Professional Documents

Culture Documents

Digital Integrated Circuits: A Design Perspective

Uploaded by

steves0118Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Integrated Circuits: A Design Perspective

Uploaded by

steves0118Copyright:

Available Formats

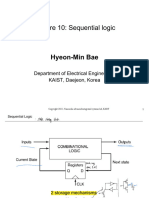

Digital Integrated

Circuits

A Design Perspective

Designing Sequential

Logic Circuits

© Digital Integrated Circuits2nd

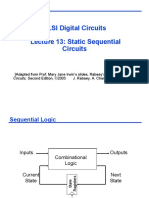

Sequential Circuits

Sequential Logic

Inputs Outputs

COMBINATIONAL

LOGIC

Current State

Next state

Registers

Q D

CLK

2 storage mechanisms

• positive feedback

• charge-based

© Digital Integrated Circuits2nd

Sequential Circuits

Naming Conventions

In our text:

a latch is level sensitive

a register is edge-triggered

There are many different naming

conventions

For instance, many books call edge-

triggered elements flip-flops

This leads to confusion however

© Digital Integrated Circuits2nd

Sequential Circuits

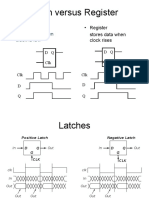

Latch versus Register

Latch Register

stores data when stores data when

clock is low clock rises

D Q D Q

Clk Clk

Clk Clk

D D

Q Q

© Digital Integrated Circuits2nd

Sequential Circuits

Latches

© Digital Integrated Circuits2nd

Sequential Circuits

Latch-Based Design

• N latch is transparent • P latch is transparent

when f = 0 when f = 1

f

N P

Logic

Latch Latch

Logic

© Digital Integrated Circuits2nd

Sequential Circuits

Timing Definitions

CLK

t Register

tsu thold D Q

D DATA CLK

STABLE t

tc - q

Q DATA

STABLE t

© Digital Integrated Circuits2nd

Sequential Circuits

Characterizing Timing

tD - Q

D Q D Q

Clk Clk

tC - Q tC - Q

Register Latch

© Digital Integrated Circuits2nd

Sequential Circuits

Maximum Clock Frequency

f

FF’s

LOGIC Also:

tcdreg + tcdlogic > thold

tp,comb

tcd: contamination delay =

minimum delay

tclk-Q + tp,comb + tsetup = T

© Digital Integrated Circuits2nd

Sequential Circuits

Positive Feedback: Bi-Stability

V o1 Vi2

1

o 1

o

V V

52

Vi

V i1 V o2

A

V i 2 = V o1

1

Vo

52 C

Vi

B

V i 1 = V o2

© Digital Integrated Circuits2nd

Sequential Circuits

Meta-Stability

Gain should be larger than 1 in the transition region

© Digital Integrated Circuits2nd

Sequential Circuits

Writing into a Static Latch

Use the clock as a decoupling signal,

that distinguishes between the transparent and opaque states

CLK

CLK

Q D D

CLK

CLK

D

CLK

Forcing the state

Converting into a MUX (can implement as NMOS-only)

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based Latches

Negative latch Positive latch

(transparent when CLK= 0) (transparent when CLK= 1)

Q 0 Q

1

D 0 D 1

CLK CLK

Q Clk Q Clk In Q Clk Q Clk In

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based Latch

CLK

CLK

CLK

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based Latch

CLK

QM

CLK

QM

CLK

CLK

NMOS only Non-overlapping clocks

© Digital Integrated Circuits2nd

Sequential Circuits

Master-Slave (Edge-Triggered)

Register

Two opposite latches trigger on edge

Also called master-slave latch pair

© Digital Integrated Circuits2nd

Sequential Circuits

Master-Slave Register

Multiplexer-based latch pair

I2 T2 I3 I5 T4 I6 Q

QM

D I1 T1 I4 T3

CLK

© Digital Integrated Circuits2nd

Sequential Circuits

Clk-Q Delay

2.5

CLK

1.5

D

tc - q(lh) tc - q(hl)

Volts Q

0.5

2 0.5

0 0.5 1 1.5 2 2.5

time, nsec

© Digital Integrated Circuits2nd

Sequential Circuits

Setup Time

© Digital Integrated Circuits2nd

Sequential Circuits

Reduced Clock Load

Master-Slave Register

CLK CLK

D T1 I1 T2 I3 Q

I2 I4

CLK CLK

© Digital Integrated Circuits2nd

Sequential Circuits

Avoiding Clock Overlap

CLK X CLK

Q

A

D

B

CLK CLK

(a) Schematic diagram

CLK

CLK

(b) Overlapping clock pairs

© Digital Integrated Circuits2nd

Sequential Circuits

Overpowering the Feedback Loop ─

Cross-Coupled Pairs

NOR-based set-reset

S R Q Q

S

Q

S Q 0 0 Q Q

1 0 1 0

R Q

0 1 0 1

Q

R 1 1 0 0

Forbidden State

© Digital Integrated Circuits2nd

Sequential Circuits

Cross-Coupled NAND

Added clock

Cross-coupled NANDs VDD

S M2 M4

Q

Q

Q

Q CLK M6 M8 CLK

R M1 M3

S M5 M7 R

This is not used in datapaths any more,

but is a basic building memory cell

© Digital Integrated Circuits2nd

Sequential Circuits

Sizing Issues

2.0 3

Q S

1.5

2 W = 0.5 m m

Q (Volts)

W = 0.6 m m

Volts

1.0

W = 0.7 m m

1

0.5 W = 0.8 m m

W = 0.9 m m

W = 1m m

0.0 0

2.0 2.5 3.0 3.5 4.0 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

W/L 5 and 6 time (ns)

(a) (b)

Output voltage dependence Transient response

on transistor width

© Digital Integrated Circuits2nd

Sequential Circuits

Storage Mechanisms

Static Dynamic (charge-based)

CLK

CLK

D Q

Q

CLK

CLK

D

CLK

© Digital Integrated Circuits2nd

Sequential Circuits

Making a Dynamic Latch Pseudo-Static

CLK

D D

CLK

© Digital Integrated Circuits2nd

Sequential Circuits

More Precise Setup Time

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Circuit before clock arrival (Setup-1 case)

CN

TG1

Inv2 Clk-Q Delay

D1 SM QM

D

Inv1

CP

TClk-Q

TSetup-1 Time

Data Clock

TSetup-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Circuit before clock arrival (Setup-1 case)

CN

TG1

Inv2 Clk-Q Delay

D1 SM QM

D

Inv1

CP

TClk-Q

TSetup-1 Time

Data Clock

TSetup-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Circuit before clock arrival (Setup-1 case)

CN

TG1

Inv2 Clk-Q Delay

D1 SM QM

D

Inv1

CP

TClk-Q

TSetup-1 Time

Data Clock

TSetup-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Circuit before clock arrival (Setup-1 case)

CN

TG1

Inv2 Clk-Q Delay

D1 SM QM

D

Inv1

TClk-Q

CP

TSetup-1 Time

Data Clock

TSetup-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Circuit before clock arrival (Setup-1 case)

CN

TG1

Inv2 Clk-Q Delay

D1 SM QM TClk-Q

D

Inv1

CP

TSetup-1 Time

Data Clock

TSetup-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Hold-1 case

CN

TG1 Clk-Q Delay

Inv2

D1 SM QM

D

Inv1

0

CP

TClk-Q

THold-1

Time

Clock Data

THold-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Hold-1 case

CN

TG1 Clk-Q Delay

Inv2

D1 SM QM

D

Inv1

0

CP

TClk-Q

THold-1

Time

Clock Data

THold-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Hold-1 case

CN

TG1 Clk-Q Delay

Inv2

D1 SM QM

D

Inv1

0

CP TClk-Q

THold-1

Time

Clock Data

THold-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Hold-1 case

CN

TG1 Clk-Q Delay

Inv2

D1 SM QM

D

Inv1 TClk-Q

0

CP

THold-1

Time

Clock Data

THold-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Setup/Hold Time Illustrations

Hold-1 case

CN

TG1 Clk-Q Delay

Inv2 TClk-Q

D1 SM QM

D

Inv1

0

CP

THold-1

Time

Clock Data

THold-1

Time

t=0

© Digital Integrated Circuits2nd

Sequential Circuits

Other Latches/Registers: C2MOS

VDD VDD

M2 M6

CLK M4 CLK M8

X

D Q

CL1 CL2

CLK M3 CLK M7

M1 M5

Master Stage Slave Stage

“Keepers” can be added to make circuit pseudo-static

© Digital Integrated Circuits2nd

Sequential Circuits

Insensitive to Clock-Overlap

VDD VDD VDD VDD

M2 M6 M2 M6

0 M4 0 M8

X X

D Q D Q

1 M3 1 M7

M1 M5 M1 M5

(a) (0-0) overlap (b) (1-1) overlap

© Digital Integrated Circuits2nd

Sequential Circuits

Pipelining

REG

REG

a a

REG

REG

REG

REG

log Out CLK log Out

CLK

REG

REG

b CLK b CLK CLK CLK

CLK CLK

Reference Pipelined

© Digital Integrated Circuits2nd

Sequential Circuits

Other Latches/Registers: TSPC

VDD VDD VDD VDD

Out

In CLK CLK In CLK CLK

Out

Positive latch Negative latch

(transparent when CLK= 1) (transparent when CLK= 0)

© Digital Integrated Circuits2nd

Sequential Circuits

Including Logic in TSPC

VDD VDD VDD VDD

In1 In2

PUN

Q Q

In CLK CLK CLK CLK

PDN In1

In2

Example: logic inside the latch

AND latch

© Digital Integrated Circuits2nd

Sequential Circuits

TSPC Register

VDD VDD VDD

CLK Q

M3 M6 M9

Y

Q

D CLK X CLK

M2 M5 M8

CLK

M1 M4 M7

© Digital Integrated Circuits2nd

Sequential Circuits

Pulse-Triggered Latches

An Alternative Approach

Ways to design an edge-triggered sequential cell:

Master-Slave Pulse-Triggered

Latches Latch

L1 L2 L

Data Data

D Q D Q D Q

Clk Clk Clk Clk

Clk

© Digital Integrated Circuits2nd

Sequential Circuits

Pulsed Latches

VDD VDD

M3 M6 VDD

CLK

Q

D CLKG CLKG MP CLKG

M2 M5

X

MN

M1 M4

(a) register (b) glitch generation

CLK

CLKG

(c) glitch clock

© Digital Integrated Circuits2nd

Sequential Circuits

Pulsed Latches

Hybrid Latch – Flip-flop (HLFF), AMD K-6 and K-7 :

CLK P1 P3

x Q

M6

M3

D P2 M5

M2

M4

M1 CLKD

© Digital Integrated Circuits2nd

Sequential Circuits

Hybrid Latch-FF Timing

© Digital Integrated Circuits2nd

Sequential Circuits

Latch-Based Pipeline

© Digital Integrated Circuits2nd

Sequential Circuits

Non-Bistable Sequential Circuits─

Schmitt Trigger

Vou t V OH

In Out

•VTC with hysteresis V OL

•Restores signal slopes

VM– VM+ Vi n

© Digital Integrated Circuits2nd

Sequential Circuits

Noise Suppression using Schmitt

Trigger

© Digital Integrated Circuits2nd

Sequential Circuits

CMOS Schmitt Trigger

VDD

M2 M4

Vin X Vout

M1 M3

Moves switching threshold

of the first inverter

© Digital Integrated Circuits2nd

Sequential Circuits

Schmitt Trigger Simulated VTC

2.5 2.5

2.0 2.0

1.5 VM1 1.5

(V)

X1.0 VM2 (V)

x1.0

k=1

V V k=3

k=2

0.5 0.5

k=4

0.0 0.0

0.0 0.5 1.0 1.5 2.0 2.5 0.0 0.5 1.0 1.5 2.0 2.5

Vin (V) Vin (V)

Voltage-transfer characteristics with hysteresis. The effect of varying the ratio of the

PMOS device M4. The width is k* 0.5m m.

© Digital Integrated Circuits2nd

Sequential Circuits

CMOS Schmitt Trigger (2)

VDD

M4

M6

M3

In Out

M2

X M5

VDD

M1

© Digital Integrated Circuits2nd

Sequential Circuits

Multivibrator Circuits

R

S

Bistable Multivibrator

flip-flop, Schmitt Trigger

T

Monostable Multivibrator

one-shot

Astable Multivibrator

oscillator

© Digital Integrated Circuits2nd

Sequential Circuits

Transition-Triggered Monostable

In

DELAY

Out

td td

© Digital Integrated Circuits2nd

Sequential Circuits

Monostable Trigger (RC-based)

VDD

In R

A B Out

(a) Trigger circuit.

C

In

B VM

(b) Waveforms.

Out

t

t1 t2

© Digital Integrated Circuits2nd

Sequential Circuits

Astable Multivibrators (Oscillators)

0 1 2 N-1

Ring Oscillator

simulated response of 5-stage oscillator

© Digital Integrated Circuits2nd

Sequential Circuits

Relaxation Oscillator

Out1

Out2

I1 I2

R C

Int

T = 2 (log3) RC

© Digital Integrated Circuits2nd

Sequential Circuits

Voltage Controller Oscillator (VCO)

Schmitt Trigger

VD D VDD

restores signal slopes

M6 M4

M2

In

M1

Iref Iref

Vcontr M3

M5 Current starved inverter

6

tpH L (nsec)

propagation delay as a function

0.0

0.5 1.5 2.5 of control voltage

V co ntr (V)

© Digital Integrated Circuits2nd

Sequential Circuits

Differential Delay Element and VCO

V o2 V o1 v3

v1

in 1 in 2

v2

v

4

V ctrl

delay cell two stage VCO

3.0

V1 V2 V3 V4

2.5

2.0

1.5

1.0

0.5

0.0

2 0.5

0.5 1.5 2.5 3.5

time (ns)

simulated waveforms of 2-stage VCO

© Digital Integrated Circuits2nd

Sequential Circuits

You might also like

- Chapter 7Document60 pagesChapter 7Lucas WeaverNo ratings yet

- Lecture 6Document31 pagesLecture 6arsalan.jawedNo ratings yet

- Designing Sequential Logic CircuitsDocument47 pagesDesigning Sequential Logic CircuitsDeepikaNo ratings yet

- Unit 3Document46 pagesUnit 3PushpalathaNo ratings yet

- 0.2 Clocks in Digital ICsDocument80 pages0.2 Clocks in Digital ICsNaftal MassingueNo ratings yet

- Chapter 7Document60 pagesChapter 7Sunil KumarNo ratings yet

- Digital Integrated CircuitsDocument60 pagesDigital Integrated CircuitsSara SaleemNo ratings yet

- Latch Versus RegisterDocument23 pagesLatch Versus RegisterSGSNo ratings yet

- Latch Versus Register: Latch Stores Data When Clock Is LowDocument23 pagesLatch Versus Register: Latch Stores Data When Clock Is LowSrikrishna JanaNo ratings yet

- Latch Versus RegisterDocument23 pagesLatch Versus Registerfly2beyondgmail.comNo ratings yet

- Static Sequential CircuitsDocument23 pagesStatic Sequential CircuitsAnubhav SinghNo ratings yet

- Chapter 10Document80 pagesChapter 10DlishaNo ratings yet

- Static Sequential XIDocument30 pagesStatic Sequential XISHOBHIT SHARMANo ratings yet

- Digital Microelectronic Circuits (: Dynamic LogicDocument38 pagesDigital Microelectronic Circuits (: Dynamic LogicPrasad BorkarNo ratings yet

- Sequential StaticDocument20 pagesSequential Staticvivek singhNo ratings yet

- Lecture7 Part3Document35 pagesLecture7 Part3aadiNo ratings yet

- Static Sequential CircuitsDocument29 pagesStatic Sequential CircuitsfneojwgfjeNo ratings yet

- L25 - Datapath Design - p1Document46 pagesL25 - Datapath Design - p1Shanawar AliNo ratings yet

- Seminar on Time Borrowing & Clock Skew TechniquesDocument18 pagesSeminar on Time Borrowing & Clock Skew TechniquesNitin Suyan PanchalNo ratings yet

- Sample and Hold Circuits P (Chapter 8)Document24 pagesSample and Hold Circuits P (Chapter 8)Anonymous JTOnHEqGVNo ratings yet

- Design of High-Speed Links: A Look at Modern VLSI Design: Vladimir StojanovićDocument53 pagesDesign of High-Speed Links: A Look at Modern VLSI Design: Vladimir StojanovićkedarkulNo ratings yet

- Clocking StrategiesDocument21 pagesClocking Strategiesswapnikasharma100% (1)

- Lecture10 SequentialDocument67 pagesLecture10 Sequential조동올No ratings yet

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDocument28 pagesA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationVinitKharkarNo ratings yet

- EE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduDocument15 pagesEE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduPhạm Đức ThuậnNo ratings yet

- 5224 wk2Document18 pages5224 wk2Nagaraj Chandrashekar SiddeshwarNo ratings yet

- Digital Integrated Circuits: IMEL7002Document47 pagesDigital Integrated Circuits: IMEL7002就爱吃饭团No ratings yet

- Converter System Modeling Via MATLAB/SimulinkDocument18 pagesConverter System Modeling Via MATLAB/SimulinkjacarmiNo ratings yet

- CD4027B CMOS Dual J-K Flip Flop: 1 Features 3 DescriptionDocument26 pagesCD4027B CMOS Dual J-K Flip Flop: 1 Features 3 DescriptionMazhar IqbalNo ratings yet

- 4740 - Lecture18 Latches and FlipflopsDocument22 pages4740 - Lecture18 Latches and Flipflopskrrish06230No ratings yet

- Digital Integrated Circuits EE 431: Fall 2015 Week 8Document28 pagesDigital Integrated Circuits EE 431: Fall 2015 Week 8Mohamed shabanaNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument34 pagesDigital Integrated Circuits: A Design PerspectiveDr. Aminul IslamNo ratings yet

- Timing DiagramDocument23 pagesTiming DiagramAnmol Gupta100% (1)

- Timing For Pipelined System: BITS PilaniDocument62 pagesTiming For Pipelined System: BITS PilaniSuvigya VijayNo ratings yet

- VLSI Design I VLSI Design I VLSI Design I VLSI Design IDocument23 pagesVLSI Design I VLSI Design I VLSI Design I VLSI Design ISaksham sangwanNo ratings yet

- D2822N ShaoxingSilicoreTechnologyDocument5 pagesD2822N ShaoxingSilicoreTechnologyandrebuhlerNo ratings yet

- 6004 Spring 1998: L10: Clocking and The Dynamic DisciplineDocument8 pages6004 Spring 1998: L10: Clocking and The Dynamic Disciplinemohammed zubairNo ratings yet

- L33 ECEN5817 Out1Document14 pagesL33 ECEN5817 Out1djyNo ratings yet

- Registers and CountersDocument47 pagesRegisters and Counterssheela lNo ratings yet

- Digital Phase Lock Loops ExplainedDocument17 pagesDigital Phase Lock Loops ExplainedMegha BadadNo ratings yet

- Lecture 4Document60 pagesLecture 4Johnjerald NicolasNo ratings yet

- Possible Ways To Add Resonant Components To The PWM Switch Cell: Classification of Resonant-Switch ConvertersDocument11 pagesPossible Ways To Add Resonant Components To The PWM Switch Cell: Classification of Resonant-Switch ConvertersdjyNo ratings yet

- Lecture 14 - Digital Circuits: Inverter Basics - Outline: - AnnouncementsDocument25 pagesLecture 14 - Digital Circuits: Inverter Basics - Outline: - Announcementsayush guptaNo ratings yet

- Introduction Logic Gates Flip Flops Registers Counters Multiplexer/ Demultiplexer Decoder/ EncoderDocument4 pagesIntroduction Logic Gates Flip Flops Registers Counters Multiplexer/ Demultiplexer Decoder/ EncoderrashmiNo ratings yet

- Lecture 2: Computer Technology & Abstractions - Last Time: Review: Don't Forget The Simple ViewDocument16 pagesLecture 2: Computer Technology & Abstractions - Last Time: Review: Don't Forget The Simple ViewFazal JadoonNo ratings yet

- Digital Integrated Circuits EE 431: Fall 2015 Week 5Document29 pagesDigital Integrated Circuits EE 431: Fall 2015 Week 5Mohamed shabanaNo ratings yet

- ELEC 335 Digital Logic Design: Dr. Mohammad Shakeel LaghariDocument30 pagesELEC 335 Digital Logic Design: Dr. Mohammad Shakeel LaghariMujaahid KhanNo ratings yet

- Advanced VLSI Design: Timing IssuesDocument88 pagesAdvanced VLSI Design: Timing IssuesSudhanshu BadolaNo ratings yet

- ECEG-4221 VLSI Design: Addis Ababa Institute of Technology (AAIT) Department of Electrical and Computer EngineeringDocument18 pagesECEG-4221 VLSI Design: Addis Ababa Institute of Technology (AAIT) Department of Electrical and Computer EngineeringNuhamin BirhanuNo ratings yet

- Metastability and Clock Domain Crossing: IN3160 IN4160Document30 pagesMetastability and Clock Domain Crossing: IN3160 IN4160kumarNo ratings yet

- Registers and Counters for Digital Logic DesignDocument42 pagesRegisters and Counters for Digital Logic DesignDayanand Gowda KrNo ratings yet

- Icl7135c - TLC7135CDocument11 pagesIcl7135c - TLC7135CCarlos PosadaNo ratings yet

- Archl FSM 04Document52 pagesArchl FSM 04Ajax KrausNo ratings yet

- 6 TimingDocument33 pages6 Timingwqy15902896758No ratings yet

- Chapter 9Document66 pagesChapter 9arsalan.jawedNo ratings yet

- Sect2-3 PDFDocument10 pagesSect2-3 PDFBlaiseNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument113 pagesDigital Integrated Circuits: A Design PerspectiveSulochana VermaNo ratings yet

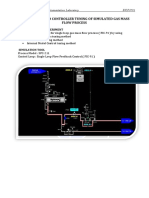

- Experiment 7: Pid Controller Tuning of Simulated Gas Mass Flow ProcessDocument6 pagesExperiment 7: Pid Controller Tuning of Simulated Gas Mass Flow ProcessPMNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogKaleb FikreNo ratings yet

- First - Robots Quote 2023-01-06Document1 pageFirst - Robots Quote 2023-01-06steves0118No ratings yet

- FLL Challenge Superpowered Awards 2022 23Document1 pageFLL Challenge Superpowered Awards 2022 23steves0118No ratings yet

- Judging Session Flowchart for Innovation Project and Robot DesignDocument1 pageJudging Session Flowchart for Innovation Project and Robot Designsteves0118No ratings yet

- RXV 673Document60 pagesRXV 673steves0118No ratings yet

- FPGA Technology: Carl LebsackDocument27 pagesFPGA Technology: Carl Lebsacksteves0118No ratings yet

- FLL Challenge Superpowered RubricsDocument3 pagesFLL Challenge Superpowered Rubricssteves0118No ratings yet

- FLL Challenge Cargo Connect Coach and Mentor Nomination Sheet 2021 FillableDocument1 pageFLL Challenge Cargo Connect Coach and Mentor Nomination Sheet 2021 Fillablesteves0118No ratings yet

- Controlling The Unit From A Web Browser (Web Control)Document3 pagesControlling The Unit From A Web Browser (Web Control)steves0118No ratings yet

- Definitive Technology SSA50 - Manual - 12309 - ReadDocument4 pagesDefinitive Technology SSA50 - Manual - 12309 - Readsteves0118No ratings yet

- English: Information About SoftwareDocument3 pagesEnglish: Information About SoftwarejpcoteNo ratings yet

- Chapter 11Document58 pagesChapter 11steves0118No ratings yet

- RXV 673 BLDocument2 pagesRXV 673 BLsteves0118No ratings yet

- Preface: X Tsx7Document58 pagesPreface: X Tsx7steves0118No ratings yet

- Moore's Law: Electronics, April 19, 1965Document106 pagesMoore's Law: Electronics, April 19, 1965steves0118No ratings yet

- Designing Combinational Logic CircuitsDocument113 pagesDesigning Combinational Logic Circuitssteves0118No ratings yet

- SZ C 611515 Us 1095-10 PDFDocument18 pagesSZ C 611515 Us 1095-10 PDFsteves0118No ratings yet

- CMOS Inverter: © Digital Integrated Circuits InverterDocument77 pagesCMOS Inverter: © Digital Integrated Circuits Invertersteves0118No ratings yet

- Moore's Law: Electronics, April 19, 1965Document117 pagesMoore's Law: Electronics, April 19, 1965steves0118No ratings yet

- OP-87160 Precautions For Use: Pin AssignmentDocument1 pageOP-87160 Precautions For Use: Pin Assignmentsteves0118No ratings yet

- Stihl Ms 150 TC Owners Instruction ManualDocument128 pagesStihl Ms 150 TC Owners Instruction ManualalexNo ratings yet

- © Digital Integrated CircuitsDocument7 pages© Digital Integrated Circuitssteves0118No ratings yet

- TSX PCX 1031-EN VaDocument1 pageTSX PCX 1031-EN Vadscj_tecNo ratings yet

- SZ C 611515 Us 1095-10 PDFDocument18 pagesSZ C 611515 Us 1095-10 PDFsteves0118No ratings yet

- Aiwa AV-X100 User ManualDocument0 pagesAiwa AV-X100 User Manualsteves0118No ratings yet

- SZ-16D CM 96124e GB WW 1055-2 PDFDocument34 pagesSZ-16D CM 96124e GB WW 1055-2 PDFsteves0118No ratings yet

- Tecumseh Model H30 35359R Parts ListDocument8 pagesTecumseh Model H30 35359R Parts Liststeves0118No ratings yet

- DCMP-lab1 HandoutDocument2 pagesDCMP-lab1 HandoutAKANSH AGRAWALNo ratings yet

- Improve timing by sizing up gates in a test circuitDocument14 pagesImprove timing by sizing up gates in a test circuit한지원No ratings yet

- Lista de Preços MM4 FS D E F Outubro 2006Document4 pagesLista de Preços MM4 FS D E F Outubro 2006Roberto CarvalhoNo ratings yet

- IC Applications and Active Filter TransformationsDocument12 pagesIC Applications and Active Filter Transformationsmsk 31No ratings yet

- Compact PlusDocument19 pagesCompact Plusfrank.garciaNo ratings yet

- Experiment Number: 10: Study of TimersDocument12 pagesExperiment Number: 10: Study of TimersBhushan RaneNo ratings yet

- Opamp Vos and Ib - SlidesDocument18 pagesOpamp Vos and Ib - SlidessridharNo ratings yet

- Mic4421 4422Document12 pagesMic4421 4422l.siqueiraNo ratings yet

- 50-555circuits (EL MEJOR)Document125 pages50-555circuits (EL MEJOR)JOSE CAMPOSNo ratings yet

- Unit - 1 D. C. Circuit: - SyllabusDocument32 pagesUnit - 1 D. C. Circuit: - SyllabusAnas AnsariNo ratings yet

- Experiment E1.07 Differential AmplifierDocument16 pagesExperiment E1.07 Differential AmplifierMohd FuadNo ratings yet

- Introduction To CMOS Circuit DesignDocument20 pagesIntroduction To CMOS Circuit DesignBharathi MuniNo ratings yet

- Anna University Examination Questions: EE6201-Circuit Theory NOV - 2015Document9 pagesAnna University Examination Questions: EE6201-Circuit Theory NOV - 2015Anonymous yO7rcec6vuNo ratings yet

- 26070-Test 18 Bit ADCs With An Ultrapure Sine Wave Oscillator PDFDocument5 pages26070-Test 18 Bit ADCs With An Ultrapure Sine Wave Oscillator PDFLuca CarboneNo ratings yet

- Tracking 3Document12 pagesTracking 3Disha GoelNo ratings yet

- Handbook of Operational Amplifier ApplicationsDocument94 pagesHandbook of Operational Amplifier Applicationshermiit89% (9)

- Unusual Filter CktsDocument46 pagesUnusual Filter Cktsraineymj100% (1)

- Diode Clamping CircuitsDocument4 pagesDiode Clamping CircuitsftafedeNo ratings yet

- Mohammed SadiqDocument2 pagesMohammed Sadiqmohammed229No ratings yet

- Root Category: # Free Space (1 Part(s) )Document1 pageRoot Category: # Free Space (1 Part(s) )MiguelNo ratings yet

- CS302 MID Term GIGA FILE PDFDocument69 pagesCS302 MID Term GIGA FILE PDFattiqueNo ratings yet

- Lab 08Document16 pagesLab 08Aleena KhalidNo ratings yet

- Logic Gates 1Document3 pagesLogic Gates 1Via Marie MesaNo ratings yet

- Transistor Configuration Comparison ChartDocument1 pageTransistor Configuration Comparison ChartKhushi SidNo ratings yet

- Question Papers: Examcode: Ece1 - 15 - B1 Version No: 1Document22 pagesQuestion Papers: Examcode: Ece1 - 15 - B1 Version No: 1sonuNo ratings yet

- Lecture 4 - Am CircuitsDocument47 pagesLecture 4 - Am Circuitsmelwin victoriaNo ratings yet

- Ta7642 PDFDocument2 pagesTa7642 PDFRobert CristobalNo ratings yet

- DSD w20dsd GtuDocument1 pageDSD w20dsd GtuSandeep kumarNo ratings yet

- Filter-Free Design Helps Class-D Audio Amplifier ImplementationsDocument6 pagesFilter-Free Design Helps Class-D Audio Amplifier ImplementationsDirson Volmir WilligNo ratings yet

- Ae Hardware PDFDocument55 pagesAe Hardware PDFIshani JhaNo ratings yet