Professional Documents

Culture Documents

Poster Przntation

Uploaded by

SakshiKoulCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Poster Przntation

Uploaded by

SakshiKoulCopyright:

Available Formats

IWPSD- 2013 GATE LEAKAGE CURRENT MODELLING IN A

FERROELECTRIC FET

Raheela Rasool, Najeeb-ud-din .

Department of Electronics & Communication Engineering

National Institute of Technology, Hazratbal

Srinagar 190 006, India

ABSTRACT

A gate leakage current model is proposed for a negative capacitance or ferroelectric FET (Fe-FET) based on Schottky and Poole-Frenkel emission.

It has been found that Poole-Frenkel current conduction mechanism takes place in ferroelectrics and the gate leakage currents in the gate stack

containing ferroelectric as dielectric can be modeled using a unified Schottky Poole-Frenkel model.

DEVICE STRUCTURE AND FRENKEL-POOLE IN FERROELECTRICS

-39.6

2.6 -38

0.5

-39.7

R(T) X 1E-4 (Cm/V)

-39.8 2.4 -39

-39.9 -40

Ln(J/E)

2.2

S(T)

-40.0

2.0 -41

-40.1

-40.2 1.8 -42

-40.3 1.6 -43

0.5 1.0 1.5 2.0 2.5 2.4 2.8 3.2 3.6 4.0

Electric Field X 1E7 (V/cm)

2.4 2.8 3.2 3.6 4.0

-1 -1

1000/T(K ) 1000/T (K )

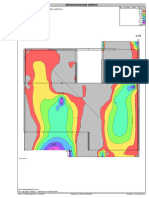

Figure 2:.Analytical plot showing current density

Figure 3: Ferroelectric FET divided by electric field versus square root of electric Figure 3: Slope R(T) versus temperature (1/T) and Intercept

filed for bulk ferroelectric material S(T ) versus temperature (1/T)

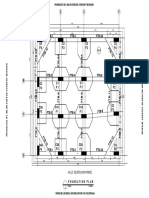

GATE stack

UNIFIED SCHOTTKY POOLE-FRENKEL MODEL

The current due to P-F mechanism in the RNL is ASSUMPTIONS

modeled and is given as:

1. A key assumption is that the dielectric

constants considered for the two

equations are the same.

2. I-V characteristics of RNL in the

proposed model is independent of

bias voltage polarity.

The leakage current for the two reverse biased 3. Characteristics of the Schottky diode

Figure 4 : Model for current conduction if junctions is modeled and is given as D1 and D2 in the proposed model is

ferroelectric Gate stack not symmetrical but instead it has

highly conductive forward and less

conductive reverse I-V characteristics.

FORWARD BIAS REVERSE BIAS

6 2.8 6

6.9890

J*10 (A/cm )

2

5 2.7 6.9889 5

J*10 (A/cm )

(A/cm )

(A/cm )

2

2

1/2

4 2.6 6.9888 4

-21

6.9887

3 2.5 3

6.9886

-18

-18

-15

2

J*10

2.4 2

J*10

6.9885

1 2.3 6.9884 1

0.5 1.0 1.5 1/22.0 2.5 0.5 1.0 1.5 2.0 2.5 0.5 1.0 1.5 2.0 2.5 0.5 1.0 1.5 1/22.0 2.5

1/2

SQRT-V(V ) SQRT_V(V1/2) SQRT V(V ) SQRT-V(V )

Figure 5: Current density (J) plotted Figure 6: Current censity (J) plotted Figure 7: Fig.10 Current density(J) Figure 8: Current density(J)

against the square root of voltage for against the square root of voltage plotted against the square root of plotted against the square root of

resistor RNL for a schottky diode D2 voltage for a schottky diode D2 voltage for resistor RNL

CONCLUSIONS

The Current conduction mechanism in Ferroelectric dielectrics has been modeled as Poole-Frenkel mechanism. Also a unified Schottky-Poole-Frenkel model has been

proposed for the gate leakage currents in the gate stack of a ferroelectric FET. The model is proposed for a simple Fe-FET consisting of a ferroelectric material in the gate

stack, directly on the silicon substrate. However, this model has some practical implications, and can be improved, if we use a thin layer of some other dielectric better

compatible with silicon in between the ferroelectric and silicon substrate. Although there is a proof of concept of negative capacitance, still there is no practical device

available till now and therefore, scope for further research in this field

REFERENCES

[1] K.Gopalakrishnan, P.B. Griffin, and J.D.Plummer,”I-MOS:A novel semiconductor device with a subthreshold slope lower than kT/q,”IEDM Tech.Dig.,2002,pp.289-292.

[2] G.F.Jiao et al,”Experimental studies of reliability issues in tunneling field effect transistors,”IEEE Electron Device Letters,vol.31,no.56,pp.396-398,may2010

[3] Chun Wing Yeung,Padilla,A.,Tsu-JaeKing Liu, Cheming Hu,”Programming characteristics of the steep turn-on/off feedback FET(FB-FET),”Symposium on VLSI Technology, vol.,no.,pp.176-

177,16-18 June 2009.

[4] S.Salahuddin and S.Datta,”Use of negative capacitance to provide voltage amplification for low power Nanoscale devices,”Nano Lett.,vol.8,no.2,pp.405-410,2008.

[5]S.M.Sze,”Physics of Semiconductor deices,”third edition, Wiley International

You might also like

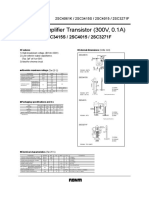

- C2911-Sanyo Semicon DeviceDocument5 pagesC2911-Sanyo Semicon DeviceCucu CatalinNo ratings yet

- Medium Power Transistor ( 80V, 0.7A) : 2SB1189 / 2SB1238Document4 pagesMedium Power Transistor ( 80V, 0.7A) : 2SB1189 / 2SB1238victory_1410No ratings yet

- 2sd2211 2sd1918 2sd1857aDocument2 pages2sd2211 2sd1918 2sd1857aOlirec Yer ZzdnarNo ratings yet

- FC4 Standard Units Pressure CurvesDocument12 pagesFC4 Standard Units Pressure CurvesTiago Karina ElisaNo ratings yet

- Load Cell Amplifier Module Model LAC 65.1Document2 pagesLoad Cell Amplifier Module Model LAC 65.1rngNo ratings yet

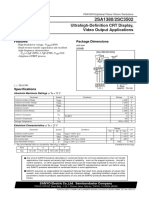

- 2SA1380/2SC3502: Ultrahigh-Definition CRT Display, Video Output ApplicationsDocument5 pages2SA1380/2SC3502: Ultrahigh-Definition CRT Display, Video Output ApplicationsdulocoNo ratings yet

- Ultrahigh-Definition Color Display Horizontal Deflection Output ApplicationsDocument4 pagesUltrahigh-Definition Color Display Horizontal Deflection Output ApplicationsManuel MartinezNo ratings yet

- D1047-Sanyo Semicon DeviceDocument4 pagesD1047-Sanyo Semicon DeviceDejan KovčićNo ratings yet

- Tranzistor 2sc4106Document4 pagesTranzistor 2sc4106BrunoNo ratings yet

- SiteDocument1 pageSiteAlvin AbilleNo ratings yet

- Correction To Interface Engineering of CoSCoON-DopDocument2 pagesCorrection To Interface Engineering of CoSCoON-DopmaczeroesNo ratings yet

- 2SC4429 PDFDocument5 pages2SC4429 PDFban4444No ratings yet

- Wcdma Radio Network Functionality: Idle Mode BehaviorDocument33 pagesWcdma Radio Network Functionality: Idle Mode Behaviormody1850No ratings yet

- LCD HD44780U (LCD-II) PC 0802-A - Pinout PDFDocument1 pageLCD HD44780U (LCD-II) PC 0802-A - Pinout PDFLodewyk KleynhansNo ratings yet

- (Dimension) - Applied Model: 43SE3KB / 43SM5KB / 43SL5KC / 43SM5KC / 43SM5KD - Unit: MM - Scale: 1/1Document1 page(Dimension) - Applied Model: 43SE3KB / 43SM5KB / 43SL5KC / 43SM5KC / 43SM5KD - Unit: MM - Scale: 1/1maximus primeNo ratings yet

- 2SD1859Document1 page2SD1859stevebow1No ratings yet

- (43SM5E W/Stand DIMENSION) - Applied Model: 43SM5E - Unit: MM - Scale: 1/1Document1 page(43SM5E W/Stand DIMENSION) - Applied Model: 43SM5E - Unit: MM - Scale: 1/1Victor González BogarinNo ratings yet

- RS-550PC/VC: Output: 5.0W 100W (Approx)Document1 pageRS-550PC/VC: Output: 5.0W 100W (Approx)Mahesa SanggadipaNo ratings yet

- 2SK2632LS: Ultrahigh-Speed Switching ApplicationsDocument4 pages2SK2632LS: Ultrahigh-Speed Switching ApplicationsHomem do CentroNo ratings yet

- 2sd1867, 2sd1980, 2sd2195 RohmDocument5 pages2sd1867, 2sd1980, 2sd2195 RohmMohammad kazem DehghaniNo ratings yet

- Datasheet CROMA AMPLIF TV Sony KV27Document1 pageDatasheet CROMA AMPLIF TV Sony KV27Javier Ventura ValenciaNo ratings yet

- Armatura Plošče 1Document4 pagesArmatura Plošče 1Milan CvetkovićNo ratings yet

- XGW IP67 LED DRIVER Catalog-2024V1Document13 pagesXGW IP67 LED DRIVER Catalog-2024V1Ciprian NeaguNo ratings yet

- MultiPodSetupWithGolf v1.0Document52 pagesMultiPodSetupWithGolf v1.0ronzo100% (1)

- FX50SMJ 2Document4 pagesFX50SMJ 2luckyz80No ratings yet

- Test Data 808nm, Conduction-Cooled Diode Laser Single BarDocument7 pagesTest Data 808nm, Conduction-Cooled Diode Laser Single BarUmar BadshahNo ratings yet

- Temperature at The Midplane of An Infi Nite Slab of Thickness 2 DDocument3 pagesTemperature at The Midplane of An Infi Nite Slab of Thickness 2 Dski097No ratings yet

- Profile 8Document1 pageProfile 8AliNo ratings yet

- Datasheet - HK k3702 3696473Document4 pagesDatasheet - HK k3702 3696473Leoned Cova OrozcoNo ratings yet

- Panasonic CGR18650C PDFDocument1 pagePanasonic CGR18650C PDFKevin Andrés Pacheco JofréNo ratings yet

- CGR18650C PanasonicDocument1 pageCGR18650C PanasonicRodolfo Becerra HernandezNo ratings yet

- 2sb1143 2sd1683Document4 pages2sb1143 2sd1683Jorge CotzomiNo ratings yet

- Self-Organization - EnglandDocument2 pagesSelf-Organization - EnglandgarcolNo ratings yet

- M 1: 305 XY Z Sector of System Group 1 Nodal Displacement in Global Z, Node Sequence Along, Loadcase 2 DSW, 1 CM 3D 20.0 MM (Min - 27.2) (Max 0)Document1 pageM 1: 305 XY Z Sector of System Group 1 Nodal Displacement in Global Z, Node Sequence Along, Loadcase 2 DSW, 1 CM 3D 20.0 MM (Min - 27.2) (Max 0)Aleksandar SiljkovicNo ratings yet

- 2sc3906k MontageDocument1 page2sc3906k MontageELDARK1No ratings yet

- Interaction Diagram - A Signle Core Wall - Aci Code / Eurocode 2Document1 pageInteraction Diagram - A Signle Core Wall - Aci Code / Eurocode 2SES DESIGNNo ratings yet

- 2sa1579 2sa1514k 2sa1038sDocument1 page2sa1579 2sa1514k 2sa1038sfmpiscoNo ratings yet

- HDM 64GS24 - 2: Dimensional DrawingDocument1 pageHDM 64GS24 - 2: Dimensional DrawingAilton SorlagNo ratings yet

- Bby 2008Document1 pageBby 2008londonmorganNo ratings yet

- High-Voltage Amplifier Transistor (120V, 50ma) : 2SC4102 / 2SC3906K / 2SC2389SDocument3 pagesHigh-Voltage Amplifier Transistor (120V, 50ma) : 2SC4102 / 2SC3906K / 2SC2389SYüksel DoğrulNo ratings yet

- A01.5 - Temporary Fencing PlanDocument1 pageA01.5 - Temporary Fencing PlanCarlos Andres Baez BaezNo ratings yet

- RTD2120LDocument37 pagesRTD2120LNeha WadyalkarNo ratings yet

- Roller AssemDocument1 pageRoller AssemMoustafa HammadNo ratings yet

- 400V/7A Switching Regulator Applications: Package Dimensions FeaturesDocument4 pages400V/7A Switching Regulator Applications: Package Dimensions FeaturesMaikol DominguezNo ratings yet

- K2043 SanyoSemiconductorCorporationDocument4 pagesK2043 SanyoSemiconductorCorporationPedro AntonioNo ratings yet

- 2SA1248/2SC3116: 160V/700mA Switching ApplicationsDocument4 pages2SA1248/2SC3116: 160V/700mA Switching ApplicationsGonzalo RojasNo ratings yet

- Ordinary Kriging in RDocument2 pagesOrdinary Kriging in RPaulo BrasilNo ratings yet

- High-Speed Switching Transistor (-60V, - 5A) : Features Dimensions (Unit: MM)Document3 pagesHigh-Speed Switching Transistor (-60V, - 5A) : Features Dimensions (Unit: MM)abmannyNo ratings yet

- S-Parameters vs. Frequency: Input Reflection Coefficient 0 Reverse Transmission, DBDocument1 pageS-Parameters vs. Frequency: Input Reflection Coefficient 0 Reverse Transmission, DBSalvador SierraNo ratings yet

- Physical and Mechanical Properties Estimation of TiHAP Functionally Graded Material Using Artificial Neural NetworkDocument7 pagesPhysical and Mechanical Properties Estimation of TiHAP Functionally Graded Material Using Artificial Neural NetworkJawad K. OleiwiNo ratings yet

- 4,042.00 MTS AREA TOTAL: Cancha # 1Document1 page4,042.00 MTS AREA TOTAL: Cancha # 1luis albertoNo ratings yet

- DatasheetDocument3 pagesDatasheetDaniel Orlando Carballo FernándezNo ratings yet

- Master Bedroom PuffDocument1 pageMaster Bedroom Puffpsyche cornNo ratings yet

- 2SA2099 / 2SC5888: High-Current Switching ApplicationsDocument5 pages2SA2099 / 2SC5888: High-Current Switching ApplicationsnguyenhieuproNo ratings yet

- 1CF43 Female Metric L - Swivel 90° Elbow (24° Cone With O-Ring) ISO 12151-2 - SWEDocument1 page1CF43 Female Metric L - Swivel 90° Elbow (24° Cone With O-Ring) ISO 12151-2 - SWEEr.Amritpal SinghNo ratings yet

- Stage 1R.1 - Location Plan For Lots 1 & 2Document1 pageStage 1R.1 - Location Plan For Lots 1 & 2hancockerNo ratings yet

- 2 SC 5297Document4 pages2 SC 5297carlosNo ratings yet

- 23LM C202V NMBDocument1 page23LM C202V NMBCairineLopesNo ratings yet

- Connection-Oriented Networks: SONET/SDH, ATM, MPLS and Optical NetworksFrom EverandConnection-Oriented Networks: SONET/SDH, ATM, MPLS and Optical NetworksNo ratings yet

- 3D Optical and Device Simulation of Surface Plasmonic Effects On Organic Solar Cells Using Silver Nano PrismsDocument5 pages3D Optical and Device Simulation of Surface Plasmonic Effects On Organic Solar Cells Using Silver Nano PrismsSakshiKoulNo ratings yet

- Introduction To Sentaurus TCADDocument47 pagesIntroduction To Sentaurus TCADSakshiKoulNo ratings yet

- Microstrip Low Pass Filter DesignDocument22 pagesMicrostrip Low Pass Filter DesignSakshiKoul100% (1)

- Design of Low Pass Filter Using Micro Strip LinesDocument14 pagesDesign of Low Pass Filter Using Micro Strip LinesSakshiKoulNo ratings yet

- Design of A "Chebyshev Low Pass Filter" at 4 GHZ: Submitted To Mr. Anil BhardwajDocument1 pageDesign of A "Chebyshev Low Pass Filter" at 4 GHZ: Submitted To Mr. Anil BhardwajSakshiKoulNo ratings yet

- Presentation On FEKO by ZUBAIRDocument14 pagesPresentation On FEKO by ZUBAIRSakshiKoulNo ratings yet

- Sunil Singh: Professional QualificationDocument3 pagesSunil Singh: Professional QualificationSakshiKoulNo ratings yet

- 34 Power Line CommunicationsDocument25 pages34 Power Line CommunicationsSakshiKoulNo ratings yet

- Radar Using Zig-Bee: Group Members: Vineet Manhas Aarif Sheikh Mehraj-Din-MirDocument10 pagesRadar Using Zig-Bee: Group Members: Vineet Manhas Aarif Sheikh Mehraj-Din-MirSakshiKoulNo ratings yet

- Physics II PU PracticlsDocument34 pagesPhysics II PU PracticlsAbhishek PadmasaleNo ratings yet

- Course Code: EEE 402 Project-II Microcontroller Based Portable Digital OscilloscopeDocument65 pagesCourse Code: EEE 402 Project-II Microcontroller Based Portable Digital OscilloscopeMohammed RaselNo ratings yet

- Electron Devices - 1Document12 pagesElectron Devices - 1rajshrimohanksNo ratings yet

- Over Voltage Protection Circuit For Automotive Load DumpDocument6 pagesOver Voltage Protection Circuit For Automotive Load Dumplennon rNo ratings yet

- Stoner Pro40 Manual-SchDocument30 pagesStoner Pro40 Manual-SchLaurin CavenderNo ratings yet

- Cmszda3v6 33vDocument3 pagesCmszda3v6 33vlalithkumartNo ratings yet

- Presentation 1Document10 pagesPresentation 1Rohit Lal MahtoNo ratings yet

- 2005priuswiring ManualDocument390 pages2005priuswiring ManualEnkhbayar Bandi100% (7)

- Data Sheet HK12PA7 ENDocument2 pagesData Sheet HK12PA7 ENkhaledNo ratings yet

- Digital Output: DevicesDocument2 pagesDigital Output: DevicesMarcial DiazNo ratings yet

- Lecture Notes On Electronics CircuitsDocument54 pagesLecture Notes On Electronics CircuitsKashif AhmedNo ratings yet

- FDN5618P 888996Document6 pagesFDN5618P 888996Alan jorgeNo ratings yet

- ENT251 Special Diodes and FETDocument39 pagesENT251 Special Diodes and FETA76 - shashank agrawalNo ratings yet

- Speed Control of DC MotorDocument31 pagesSpeed Control of DC Motorabhinav. alpheus651997No ratings yet

- SPSTR-S008020 A en PDFDocument2 pagesSPSTR-S008020 A en PDFPanda MicrowaveNo ratings yet

- Analysis of Electrical Characteristics of Solar Cell Employing Matlab/SimulinkDocument9 pagesAnalysis of Electrical Characteristics of Solar Cell Employing Matlab/SimulinkMarco Antonio Pérez FernándezNo ratings yet

- Midas Venice 160,240,320 PDFDocument46 pagesMidas Venice 160,240,320 PDFstari692002No ratings yet

- Isro SC Ec Previous Solved Papers Made EasyDocument236 pagesIsro SC Ec Previous Solved Papers Made EasyShivanshu Pandey0% (1)

- RF Chain - WikipediaDocument15 pagesRF Chain - WikipediaVasikaran PrabaharanNo ratings yet

- AO4620 Complementary Enhancement Mode Field Effect TransistorDocument13 pagesAO4620 Complementary Enhancement Mode Field Effect TransistorbobNo ratings yet

- Modified Valley-Fill For Harmonics ReductionDocument4 pagesModified Valley-Fill For Harmonics ReductionAyong HiendroNo ratings yet

- 1MRK 508 015 BenDocument20 pages1MRK 508 015 Benalaa6474794No ratings yet

- Passive Components TestDocument29 pagesPassive Components TestKesalan TerasaNo ratings yet

- h1 O03eh0 PDFDocument244 pagesh1 O03eh0 PDFedy985100% (1)

- Water Level Indicator Using Transistor: Bachelor of Technology Electronics and Communication Engineering (ECE)Document12 pagesWater Level Indicator Using Transistor: Bachelor of Technology Electronics and Communication Engineering (ECE)Srihari PuttaNo ratings yet

- Experiment 8 Current and Voltage Measurements: StructureDocument8 pagesExperiment 8 Current and Voltage Measurements: StructureGanesh DhyaniNo ratings yet

- Electronic Symbols and Actual ComponentsDocument14 pagesElectronic Symbols and Actual ComponentsVladimir Rui FortesNo ratings yet

- Lan Cable Tester (Project)Document37 pagesLan Cable Tester (Project)Sanket Gupta80% (5)

- wz3 Dioda Shotkey BarrierDocument2 pageswz3 Dioda Shotkey Barrierbengkel_ericNo ratings yet

- PC20TK: Assembling Training For Digital MultimeterDocument44 pagesPC20TK: Assembling Training For Digital MultimeterhazeypotterNo ratings yet