Professional Documents

Culture Documents

COE 202: Digital Logic Design - Sequential Circuits Part 1

Uploaded by

shabbirjamaliOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

COE 202: Digital Logic Design - Sequential Circuits Part 1

Uploaded by

shabbirjamaliCopyright:

Available Formats

COE 202: Digital Logic Design

Sequential Circuits

Part 1

Dr. Ahmad Almulhem

Email: ahmadsm AT kfupm

Phone: 860-7554

Office: 22-324

Ahmad Almulhem, KFUPM 2010

Objectives

• Sequential Circuits

• Storage Elements (Memory)

• Latches

• Flip-Flops

Ahmad Almulhem, KFUPM 2010

Combinational vs Sequential

inputs X Combinational outputs Z

Circuits

A combinational circuit:

• At any time, outputs depends only on inputs

• Changing inputs changes outputs

• No regard for previous inputs

• No memory (history)

• Time is ignored !

Ahmad Almulhem, KFUPM 2010

Combinational vs Sequential

inputs X Combinational outputs Z

Circuits

present state next state

Memory

A sequential circuit:

• A combinational circuit with feedback through memory

• The stored information at any time defines a state

• Outputs depends on inputs and previous inputs

• Previous inputs are stored as binary information into memory

• Next state depends on inputs and present state

Ahmad Almulhem, KFUPM 2010

Examples of sequential systems

Traffic light ATM Vending machine

What is common between these systems?

Ahmad Almulhem, KFUPM 2010

Combinational Adder

• 4-bit adder (ripple-carry)

• Notice how carry-out propagates

• One adder is active at a time

• 4 full adders are needed

Ahmad Almulhem, KFUPM 2010

Sequential Adder

1-bit memory and 2 4-bit memory

Only one full-adder!

4 clocks to get the output

The 1-bit memory defines the circuit state (0 or 1)

Ahmad Almulhem, KFUPM 2010

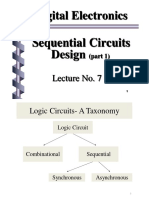

Types of Sequential Circuits

• Two types of sequential circuits:

• Synchronous: The behavior of the circuit

depends on the input signal at discrete

instances of time (also called clocked)

• Asynchronous: The behavior of the circuit

depends on the input signals at any instance

of time and the order of the inputs change

• A combinational circuit with feedback

Ahmad Almulhem, KFUPM 2010

Synchronous Sequential Circuits

inputs X Combinational outputs Z

Circuits

present state next state

Flip-Flops

clock

• Synchronous circuits employs a synchronizing signal called clock

(a periodic train of pulses; 0s and 1s)

• A clock determines when computational activities occur

• Other signals determines what changes will occur

Ahmad Almulhem, KFUPM 2010

Synchronous Sequential Circuits

inputs X Combinational outputs Z

Circuits

present state next state

Flip-Flops

clock

• The storage elements (memory) used in clocked sequential

circuits are called flip-flops

• Each flip-flop can store one bit of information 0,1

• A circuit may use many flip-flops; together they define the circuit state

• Flip-Flops (memory/state) update only with the clock

Ahmad Almulhem, KFUPM 2010

Storage Elements (Memory)

• A storage element can maintain a binary state (0,1)

indefinitely, until directed by an input signal to switch state

• Main difference between storage elements:

• Number of inputs they have

• How the inputs affect the binary state

• Two main types:

• Latches (level-sensitive)

• Flip-Flops (edge-sensitive)

• Latches are useful in asynchronous sequential circuits

• Flip-Flips are built with latches

Ahmad Almulhem, KFUPM 2010

Latches

• A latch is binary storage element

• Can store a 0 or 1

• The most basic memory

• Easy to build

• Built with gates (NORs, NANDs, NOT)

Ahmad Almulhem, KFUPM 2010

SR Latch

What does this circuit do?

Ahmad Almulhem, KFUPM 2010

SR Latch

• Two states: Set (Q = 1) and Reset (Q = 0)

• When S=R=0, Q remains the same, S=R=1 is not allowed!

• Normally, S=R=0 unless the state need to be changed (memory?)

• State of the circuit depends not only on the current inputs, but also

on the recent history of the inputs

Ahmad Almulhem, KFUPM 2010

S’ R’ Latch

How about this circuit?

Ahmad Almulhem, KFUPM 2010

S’ R’ Latch

• Similar to SR latch (complemented)

• Two states: Set (Q = 0) and Reset (Q = 1)

• When S=R=1, Q remains the same

• S=R=0 is not allowed!

Ahmad Almulhem, KFUPM 2010

SR Latch with Clock

• An SR Latch can be modified to control when it changes

• An additional input signal Clock (C)

• When C=0, the S and R inputs have no effect on the latch

• When C=1, the inputs affect the state of the latch and

possibly the output

Ahmad Almulhem, KFUPM 2010

SR Latch with Clock (cont.)

How can we eliminate the undefined state?

Ahmad Almulhem, KFUPM 2010

D Latch

S • Ensure S and R are

never equal to 1 at the

same time

• Add inverter

• Only one input (D)

R • D connects to S

• D’ connects to R

• D stands for data

• Output follows the

input when C = 1

• Transparent

• When C = 0, Q

remains the same

Ahmad Almulhem, KFUPM 2010

Graphic Symbols for Latches

clk

• A latch is designated by a rectangular block with inputs on the left and

outputs on the right

• One output designates the normal output, the other (with the bubble)

designates the complement

• For S’R’ (SR built with NANDs), bubbles added to the input

Ahmad Almulhem, KFUPM 2010

Problem with Latches

inputs X Combinational outputs Z

Circuits

Latches?

clock

Example

• What happens if Clock=1? What will be the

value of Q when Clock goes to 0? Q

D Q

• Problem: A latch is transparent; state keep

changing as long as the clock remains active

• Due to this uncertainty, latches can not be Clock C Q

reliably used as storage elements.

Ahmad Almulhem, KFUPM 2010

Flip Flops

• A flip-flop is a one bit memory similar to latches

• Solves the issue of latch transparency

• Latches are level sensitive memory element

• Active when the clock = 1 (whole duration)

• Flip-Flops are edge-triggered or edge-sensitive

memory element

• Active only at transitions; i.e. either from 0 1 or 1 0

level

positive (rising) edge negative (falling) edge

Ahmad Almulhem, KFUPM 2010

Flip Flops

clk clk

• A flip flop can be built using two latches in a master-

slave configuration

• A master latch receives external inputs

• A slave latch receives inputs from the master latch

• Depending on the clock signal, only one latch is active at

any given time

• If clk=1, the master latch is enabled and the inputs are latched

• if clk=0, the master is disabled and the slave is activated to

generate the outputs

Ahmad Almulhem, KFUPM 2010

Flip Flops

clk clk

Important Timing Considerations:

• Delay of logic gates inside the flip-flop

• Setup Time (Ts): The minimum time

during which D input must be maintained

before the clock transition occurs.

• Hold Time (Th): The minimum time

during which D input must not be

changed after the clock transition occurs.

Ahmad Almulhem, KFUPM 2010

SR Flip Flop

• Built using two latches

(Master and Slave)

• C = 1, master is active

• C = 0, slave is active

• Q is sampled at the

falling edge

• Data is entered on the

rising edge of the clock

pulse, but the output

does not reflect the

change until the falling

edge of the clock pulse.

Ahmad Almulhem, KFUPM 2010

Graphic Symbols for Flip Flops

• A Flip Flop is designated by a rectangular block with inputs on the

left and outputs on the right (similar to latches)

• The clock is designated with an arrowhead

• A bubble designates a negative-edge triggered flip flops

Ahmad Almulhem, KFUPM 2010

Other Flip Flops

JK Flip Flop

• How does it work?

• Hint: D = ?

Ahmad Almulhem, KFUPM 2010

Other Flip Flops

JK Flip Flop

• D = J Q’ + K’ Q

• J sets the flip flop (1)

• K reset the flip flop (0)

• When J = K = 1, the output is complemented

Ahmad Almulhem, KFUPM 2010

Other Flip Flops

JK Flip Flop

• D = J Q’ + K’ Q

• J sets the flip flop (1) JK Flip Flop built with SR latches

• K reset the flip flop (0)

• When J = K = 1, the output is complemented

Ahmad Almulhem, KFUPM 2010

Other Flip Flops (cont.)

T Flip Flop

• T (toggle) flip flop is a complementing flip flop

• Built with a JK or D flip flop (as shown above)

• T = 0, no change,

• T = 1, complement (toggle)

• For D-FF implementation, D = T Q

Ahmad Almulhem, KFUPM 2010

Characteristic Tables

• A characteristic table

defines the operation of a

flip flop in a tabular form

• Next state is defined in

terms of the current state

and the inputs

• Q(t) refers to current state

(before the clock arrives)

• Q(t+1) refers to next state

(after the clock arrives)

• Similar to the truth table in

combinational circuits

Ahmad Almulhem, KFUPM 2010

Characteristic Equations

• A characteristic

equation defines the

operation of a flip flop in

an algebraic form

• For D-FF

• Q(t+1) = D

• For JK-FF

• Q(t+1) = J Q’ + K’ Q

• For T-FF

• Q(t+1) = T Q

Ahmad Almulhem, KFUPM 2010

Direct Inputs

• Some flip-flops have asynchronous inputs to set/reset their states

independently of the clock.

• Preset or direct set, sets the flip-flop to 1

• Clear or direct reset, set the flip-flop to 0

• When power is turned on, a flip-flop state is unknown; Direct inputs are

useful to put in a known state

• Figure shows a positive-edge D-FF with active-low asynchronous

reset.

Ahmad Almulhem, KFUPM 2010

Flip Flops Sheet (Mano’s Textbook)

Ahmad Almulhem, KFUPM 2010

Summary

• In a sequential circuit, outputs depends on inputs and

previous inputs

• Previous inputs are stored as binary information into memory

• The stored information at any time defines a state

• Similarly, next state depends on inputs and present state

• Two types of sequential circuits: Synchronous and

Asynchronous

• Two types of Memory elements: Latches and Flip-Flops.

• Flip-flops are built with latches

• A flip-flop is described using characteristic table/equation

• Flips-flops can have direct asynchronous inputs

Ahmad Almulhem, KFUPM 2010

You might also like

- COE 202: Digital Logic Design Sequential Circuits: Dr. Ahmad AlmulhemDocument41 pagesCOE 202: Digital Logic Design Sequential Circuits: Dr. Ahmad AlmulhemFiza ShakeelNo ratings yet

- Sequential Circuits: by Dr. Nermeen TalaatDocument36 pagesSequential Circuits: by Dr. Nermeen TalaatahmedNo ratings yet

- Sequential Circuits Explained: Latches, Flip-Flops, and Their ApplicationsDocument35 pagesSequential Circuits Explained: Latches, Flip-Flops, and Their Applicationsعلوم حاسبNo ratings yet

- Sequential Circuits: Cpe 443/L Advanced Logic CircuitsDocument35 pagesSequential Circuits: Cpe 443/L Advanced Logic CircuitsKent Genzen Corpus100% (1)

- Digital Logic Design Sequential CircuitsDocument35 pagesDigital Logic Design Sequential CircuitsV Iv Ek ParekhNo ratings yet

- Flip FlopDocument35 pagesFlip Flopநட்ராஜ் நாதன்No ratings yet

- Digital Electronics Sequential Circuits Design Part 1Document14 pagesDigital Electronics Sequential Circuits Design Part 1عباس محمد عباس عبدالحسينNo ratings yet

- Combinational and SequentialCircuitsDocument40 pagesCombinational and SequentialCircuitsbrieabrhaNo ratings yet

- ch5 Flip-Flops and Related DevicesDocument95 pagesch5 Flip-Flops and Related DevicesMinh Mẫn NguyễnNo ratings yet

- Unit-Iii Sequential Logic CircuitsDocument104 pagesUnit-Iii Sequential Logic CircuitsAswin ThangarajuNo ratings yet

- FlipflopsDocument38 pagesFlipflopsajith p pNo ratings yet

- Intro to Synchronous Sequential Logic & Storage ElementsDocument49 pagesIntro to Synchronous Sequential Logic & Storage ElementsJames Francis100% (4)

- Digital - Chapter 5.sequentialDocument24 pagesDigital - Chapter 5.sequentialJenberNo ratings yet

- October 15, 2003 Flip-Flops 1Document25 pagesOctober 15, 2003 Flip-Flops 1B Dheepak BalaNo ratings yet

- Logic Design Presentation - Latches & Flip FlopsDocument16 pagesLogic Design Presentation - Latches & Flip FlopsKudzai Russell MutanhaurwaNo ratings yet

- Metastability/Overview: - Metastability of Flip-Flops (FFS) and LatchesDocument19 pagesMetastability/Overview: - Metastability of Flip-Flops (FFS) and LatchesMani KiranNo ratings yet

- Digital Circuits and Computer Architecture Chapter 2: Flip Flops, Registers, CountersDocument70 pagesDigital Circuits and Computer Architecture Chapter 2: Flip Flops, Registers, CountersCharul DeshpandeNo ratings yet

- Chapter 6 - Sequential Logics (EEEg4302) 2Document31 pagesChapter 6 - Sequential Logics (EEEg4302) 2Toli fiqeeNo ratings yet

- Module-4: Flip-Flops, Registers and CountersDocument111 pagesModule-4: Flip-Flops, Registers and CountersSanchitha GowdaNo ratings yet

- Week 07 Sequential Circuits Sec ADocument25 pagesWeek 07 Sequential Circuits Sec AMuhammad RafayNo ratings yet

- Presentation 1Document33 pagesPresentation 1Satyajit GantayatNo ratings yet

- Clocked Sequential CircuitsDocument14 pagesClocked Sequential CircuitsİBRAHİM YÜMLÜNo ratings yet

- Chapter 5Document109 pagesChapter 5Amera AdilNo ratings yet

- EE-221 Chap07 Part-01Document42 pagesEE-221 Chap07 Part-01AliNo ratings yet

- Digital Logic Circuits (Part 2) Digital Logic Circuits (Part 2)Document25 pagesDigital Logic Circuits (Part 2) Digital Logic Circuits (Part 2)maddy13rocksNo ratings yet

- Lecture 3Document13 pagesLecture 3Mohd Mujtaba AkhtarNo ratings yet

- 1up-pdf-2015Su-CS61C-L10-sk-FSMDocument47 pages1up-pdf-2015Su-CS61C-L10-sk-FSMyanagic605No ratings yet

- Flip Flop Sect 2Document31 pagesFlip Flop Sect 2Bink BonkNo ratings yet

- 1 Unit 2 Flip FlopsDocument23 pages1 Unit 2 Flip FlopsShivangi SharmaNo ratings yet

- Sequential Circuits: Types and Functions of Flip FlopsDocument16 pagesSequential Circuits: Types and Functions of Flip FlopsSonam SoniNo ratings yet

- BECE102L Digital Systems Design: Sequential CircuitsDocument115 pagesBECE102L Digital Systems Design: Sequential Circuitshitesh bonamNo ratings yet

- Flip FlopsDocument40 pagesFlip Flopszohaiba338No ratings yet

- Flip Flops and Related Devices: Instructor: Afroza SultanaDocument30 pagesFlip Flops and Related Devices: Instructor: Afroza SultanaSamina TohfaNo ratings yet

- Guide Chapter 5 Sequential CircuitsDocument99 pagesGuide Chapter 5 Sequential CircuitsSara Tilahun100% (1)

- Understanding Flip-FlopsDocument35 pagesUnderstanding Flip-FlopsKaustav MitraNo ratings yet

- Lecture #32 Registers, Counters EtcDocument21 pagesLecture #32 Registers, Counters EtcRajan GoyalNo ratings yet

- LD5 Mano Ch5Document37 pagesLD5 Mano Ch5Amr HefnyNo ratings yet

- 34 DLD Lec 34 D Latch, Flip Flop Circuit Dated 01 Jan 2021 Lecture SlidesDocument18 pages34 DLD Lec 34 D Latch, Flip Flop Circuit Dated 01 Jan 2021 Lecture SlidesEhsan MalikNo ratings yet

- Unit-IV, V VLSI DESIGNDocument91 pagesUnit-IV, V VLSI DESIGN2k20EC034 ANSHULIYERNo ratings yet

- Synchronous Sequential Logic CircuitsDocument49 pagesSynchronous Sequential Logic CircuitsDusan SimijonovicNo ratings yet

- DLD_Chapter_6 (1)Document31 pagesDLD_Chapter_6 (1)kalshkinguNo ratings yet

- Adding Binary Numbers: Half and Full AddersDocument56 pagesAdding Binary Numbers: Half and Full AdderstylerNo ratings yet

- PLCDocument46 pagesPLChazlanNo ratings yet

- Basic Sequential Components: CT101 - Computing Systems OrganizationDocument27 pagesBasic Sequential Components: CT101 - Computing Systems OrganizationRotimi OkunolaNo ratings yet

- Basic NAND S-R Latch CircuitDocument25 pagesBasic NAND S-R Latch CircuitredionxhepaNo ratings yet

- Topic 4 - Digital Logic Part 2Document44 pagesTopic 4 - Digital Logic Part 2VortexProYeoNo ratings yet

- Unit 3 VLSIDocument93 pagesUnit 3 VLSIPraba KaranNo ratings yet

- ACTIVITY PPT Exploring Sequential CircuitsDocument12 pagesACTIVITY PPT Exploring Sequential Circuitsks78874960% (1)

- Counters 123Document26 pagesCounters 123raajeevaasNo ratings yet

- CO Unit-3: Synchronous Sequential LogicDocument80 pagesCO Unit-3: Synchronous Sequential LogicMuni Koteswara Rao CHNo ratings yet

- Chapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsDocument20 pagesChapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsHamza RiazNo ratings yet

- Digital Lesson 5 Part 1Document50 pagesDigital Lesson 5 Part 1DAVIE MATIASNo ratings yet

- Logic Circuits: Fundamentals of Instrumentation and ControlDocument26 pagesLogic Circuits: Fundamentals of Instrumentation and ControlRana MohsinNo ratings yet

- Digital Logic Design: Sequential Logic FundamentalsDocument31 pagesDigital Logic Design: Sequential Logic FundamentalssfdNo ratings yet

- Chapter 5 - Sequential Circuits: Logic and Computer Design FundamentalsDocument20 pagesChapter 5 - Sequential Circuits: Logic and Computer Design FundamentalsMuhammad MuaviaNo ratings yet

- CST203 LSD M5-Ktunotes - inDocument8 pagesCST203 LSD M5-Ktunotes - incpuportNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- The University of Tokyo College of Arts and Sciences Programs in English at Komaba (PEAK)Document35 pagesThe University of Tokyo College of Arts and Sciences Programs in English at Komaba (PEAK)shabbirjamaliNo ratings yet

- Assistnt D SportDocument4 pagesAssistnt D SportshabbirjamaliNo ratings yet

- Himachal Edition HE - 03 - September - 2020 Page 6Document1 pageHimachal Edition HE - 03 - September - 2020 Page 6shabbirjamaliNo ratings yet

- Excel Multiple Choice Exam: Terms in This SetDocument6 pagesExcel Multiple Choice Exam: Terms in This SetshabbirjamaliNo ratings yet

- HT Delhi 25Document23 pagesHT Delhi 25shabbirjamaliNo ratings yet

- Discovering Computers Final Exam Flashcards - QuizletDocument20 pagesDiscovering Computers Final Exam Flashcards - QuizletshabbirjamaliNo ratings yet

- Making Short Shrift of Palaces That Stood Tall: My Unforgettable Ayodhya StoryDocument1 pageMaking Short Shrift of Palaces That Stood Tall: My Unforgettable Ayodhya StoryshabbirjamaliNo ratings yet

- Pakistan Should Be Remerged in India: 6 Will Kamala Act As Catalyst in US Politics? ADocument1 pagePakistan Should Be Remerged in India: 6 Will Kamala Act As Catalyst in US Politics? AshabbirjamaliNo ratings yet

- Precis WritingDocument7 pagesPrecis WritingJyotidesaiNo ratings yet

- Roll Number Slip: Education Testing Council (Etc)Document1 pageRoll Number Slip: Education Testing Council (Etc)shabbirjamaliNo ratings yet

- Amir 2 PDFDocument1 pageAmir 2 PDFshabbirjamaliNo ratings yet

- SIBA TESTING SERVICES FOR VARIOUS POSTS OF SINDH TEXTBOOK BOARDDocument1 pageSIBA TESTING SERVICES FOR VARIOUS POSTS OF SINDH TEXTBOOK BOARDMr. FunnyNo ratings yet

- CVDocument1 pageCVshabbirjamaliNo ratings yet

- 97 Horse MotionDocument1 page97 Horse MotionshabbirjamaliNo ratings yet

- Data Communication - CS601 Power Point Slides Lecture 01Document21 pagesData Communication - CS601 Power Point Slides Lecture 01shabbirjamali100% (1)

- C# TaskDocument16 pagesC# TaskshabbirjamaliNo ratings yet

- Solution: Letusc by YashvantkenetkarDocument16 pagesSolution: Letusc by YashvantkenetkarshabbirjamaliNo ratings yet

- Fractions PacketDocument19 pagesFractions PacketshabbirjamaliNo ratings yet

- Chap 1Document23 pagesChap 1PedyNo ratings yet

- Introduction of ComputerDocument3 pagesIntroduction of ComputershabbirjamaliNo ratings yet

- 4270 Vlan TutorialDocument21 pages4270 Vlan TutorialAsma Lata LataNo ratings yet

- Chemistry QuestionDocument27 pagesChemistry QuestionNikhil AhujaNo ratings yet

- Contact Icons Word CV TemplateDocument1 pageContact Icons Word CV TemplateshabbirjamaliNo ratings yet

- PDF Time Speed and Distance Question Bank For SSC and BANK ExamsDocument27 pagesPDF Time Speed and Distance Question Bank For SSC and BANK ExamsStudy IQ50% (4)

- Multi DisciplinaryDocument18 pagesMulti DisciplinaryshabbirjamaliNo ratings yet

- Board of Intermediate & Secondary Education Hyderabad Sindh. MarksheetDocument2 pagesBoard of Intermediate & Secondary Education Hyderabad Sindh. MarksheetshabbirjamaliNo ratings yet

- Intro To NetworkingDocument29 pagesIntro To NetworkingQueniel QuezmarNo ratings yet

- Digital Logic Design - CS302 Fall 2006 Assignment 01Document2 pagesDigital Logic Design - CS302 Fall 2006 Assignment 01shabbirjamaliNo ratings yet

- Application Sumission GuidlinesDocument4 pagesApplication Sumission GuidlinesRiaz MirNo ratings yet

- Design & Simulate BJT Amplifier CircuitDocument6 pagesDesign & Simulate BJT Amplifier CircuitBryan TokoNo ratings yet

- Digital Logic Design Combinational LogicDocument29 pagesDigital Logic Design Combinational LogicsfdNo ratings yet

- Best Practices For The Quartus Ii Timequest Timing AnalyzerDocument48 pagesBest Practices For The Quartus Ii Timequest Timing AnalyzergorskiaNo ratings yet

- Logic SynthesisDocument2 pagesLogic SynthesisSoumyarshi DasNo ratings yet

- Memory: Complete Coverage of Dram, Sram, Eprom, and Flash Memory IcsDocument2 pagesMemory: Complete Coverage of Dram, Sram, Eprom, and Flash Memory IcsLeandro MussoNo ratings yet

- Implementing Logic Gates and Code ConversionsDocument28 pagesImplementing Logic Gates and Code ConversionsayushNo ratings yet

- Syllabus PDFDocument1 pageSyllabus PDFJitha VargheseNo ratings yet

- CH 3Document25 pagesCH 3avishek aviNo ratings yet

- Semiconductor KRA101 KRA106: Technical DataDocument6 pagesSemiconductor KRA101 KRA106: Technical DataJassem Ben MeriemNo ratings yet

- Static Timing AnalysisDocument71 pagesStatic Timing Analysisapi-3762689100% (13)

- Cmos - Vlsi - Jan 2023Document2 pagesCmos - Vlsi - Jan 20231ms21ec132No ratings yet

- MITSUBISHI INTELLIGENT POWER MODULE PM50RL1B120Document9 pagesMITSUBISHI INTELLIGENT POWER MODULE PM50RL1B120MuMoMaNo ratings yet

- 18W Cascade Mod Rev 2.2 2 PDFDocument1 page18W Cascade Mod Rev 2.2 2 PDFGiovane de PedriNo ratings yet

- JSSC 2011 2143610Document10 pagesJSSC 2011 2143610Rizwan Shaik PeerlaNo ratings yet

- Cyclic Redundancy Check - CRC: CRC Solution Sequential DividerDocument12 pagesCyclic Redundancy Check - CRC: CRC Solution Sequential DividerJibran SafdarNo ratings yet

- LCA Lab Report 12Document12 pagesLCA Lab Report 12ayleeNo ratings yet

- VLSI Design-Debaprasad Das - (Ecerelatedbooks - Blogspot.in) PDFDocument669 pagesVLSI Design-Debaprasad Das - (Ecerelatedbooks - Blogspot.in) PDFTHE GAMING CHANNELNo ratings yet

- (d9ffc) Mt48lc4m32b2b5-7 ItDocument79 pages(d9ffc) Mt48lc4m32b2b5-7 ItDario Gabriel Coz RojasNo ratings yet

- 07 Schematic Diagram E (Ver2.0)Document7 pages07 Schematic Diagram E (Ver2.0)TNTRoCkZNo ratings yet

- Document 29 (No Sirve)Document5 pagesDocument 29 (No Sirve)Alejandro Antonio Nuñez BonillaNo ratings yet

- EEPROMDocument97 pagesEEPROMMoises PedrazaNo ratings yet

- Logic Gates using NAND and NORDocument9 pagesLogic Gates using NAND and NORjillaniNo ratings yet

- A11) ShortageReportDocument3,439 pagesA11) ShortageReportNhàn BeeNo ratings yet

- Chapter Seven Capacitors and InductorsDocument10 pagesChapter Seven Capacitors and InductorsVimala ElumalaiNo ratings yet

- Single Phase Energy Meter IC with Integrated OscillatorDocument7 pagesSingle Phase Energy Meter IC with Integrated OscillatorAbhishek GuptaNo ratings yet

- KL 900A CommsDocument4 pagesKL 900A CommsAhmed Abdel AzizNo ratings yet

- De Lab ComparatorDocument5 pagesDe Lab ComparatorAditya ChallaNo ratings yet

- Automatic Night Lamp Using LDRDocument12 pagesAutomatic Night Lamp Using LDRHardik PandyaNo ratings yet

- Interfacing ADC 0808 to 8051 MicrocontrollerDocument4 pagesInterfacing ADC 0808 to 8051 Microcontrollermatrixworld20No ratings yet

- 2SC5342Document4 pages2SC5342Wanderley MoreiraNo ratings yet