Professional Documents

Culture Documents

PLL Charge Pump

Uploaded by

rah0987Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PLL Charge Pump

Uploaded by

rah0987Copyright:

Available Formats

1

Charge Pump PLL

2

Outline

Charge Pump PLL

Loop Component Modeling

Loop Filter and Transfer Function

Loop Filter Design

Loop Calibration

3

Charge Pump PLL

The charge pump PLL is one of the most

popular PLL structures since 1980s

Featured with a digital phase detector and a

charge pump

Advantages

Fast lock and tracking

No false lock

Phase

Detector

Charge

Pump

Loop

Filter

VCO

N-Divider

f

i

f

o

f

o

4

Phase Detector

Gives the phase difference between the input

clock signal and VCO output signal

Different types

Nonlinear (such as Bang-Bang)

Linear (such as Hogges Phase Detector)

Linear PD output a digital signal whose duty

ratio is proportional to the phase difference

In Hogges PD, if the phase difference is

e

, the

output digital signal duty ratio is

2

e

C. Hogge, A Self-correcting clock recovery circuit, Dec, 1985

5

Typical Phase Detector and Waveform

Y. Tang, et., al., "Phase detector for PLL-based high-speed data recovery," Nov. 2002

Circuit

Structure

Output

Waveform

When locked

2

1

6

Charge Pump

Convert a digital signal into current

UP

DN

I

up

I

dn

P

I

7

Loop Filter

Low pass filter

1

st

order

2

nd

order (higher roll-off speed at high

frequency)

3

rd

order & higher

) (

1

) (

2 1 2 1

2

1

C C s C RC s

sRC

s F

I

p

V

C

C1

R

I

p

V

C

C1

R

C2

1

1

) (

sC

R s F

8

VCO

Tuning gain K

VCO

is the most important

parameter

Usually coarse tuning and fine tuning

s

K

VCO

9

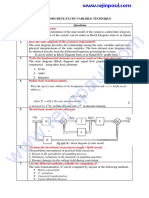

CP PLL loop modeling

Phase

Detector

Charge

Pump

Loop

Filter

VCO

f

i

f

o

f

o

i

o

10

2

nd

Loop Transfer Function

Using a 1

st

order LPF: Active PI type

Open-loop transfer function

Closed-loop transfer function

1

2

2

1

1

) (

C s

) (sRC

VCO

K

p

I

s

o

G

1

2 2

2

1

2 2

C

VCO

K

p

I

R

VCO

K

p

I

s s

C

VCO

K

p

I

R

VCO

K

p

I

s

(s)

c

G

11

3

rd

Loop Transfer Function

Using a 2

nd

order LPF

Let m=C2/C1

Open-loop transfer function

Closed-loop transfer function

) 1 (

2

1

3

1

2 2

)

2 1

(

2

2 1

3

) 1

1

(

2

) (

m s mRC s

C

VCO

K

p

I R

VCO

K

p

I

s

C C s C RC s

sRC

VCO

K

p

I

s

o

G

1

2 2

) 1 (

2

1

3

1

2 2

) (

C

VCO

K

p

I R

VCO

K

p

I

s m s mRC s

C

VCO

K

p

I R

VCO

K

p

I

s

s

c

G

12

Comparison

When m becomes 0, the 3

rd

order loop

degenerates into 2

nd

order loop

3

rd

order loop gives an extra high frequency

pole, which increases the high frequency roll-off

in jitter transfer

3

rd

order loop is widely used and can be treated

as 2

nd

order loop for simplification

Unfortunately, the 3

rd

order loop shows different

jitter transfer from the 2

nd

order loop

We focus on 3

rd

order loop

13

Simplification of 3

rd

Order Loop

Define natural frequency

n

& damping ratio

Then totally 3 loop parameters:

n

, &m

Simplified transfer function

1

2

2

C

VCO

K

p

I

n

2

2

VCO p

n

RK I

2 2 3

2

2 ) 1 (

2

2

) (

n n

n

n n

c

s s m s m

s

s G

14

LPF Design Consideration

3-dB frequency easy to control

Roll-off speed easy to meet with 2

nd

and 3

rd

order transfer function

Jitter transfer (jitter peaking)

15

Jitter peaking of 2

nd

order loop

Jitter peaking can be reduced or

eliminated by increasing the damping ratio

Eliminated when damping ratio >1

Large damping ratio leads to slow closed-

loop response

Usually suggested =5 to meet the jitter

peaking spec

16

Jitter peaking of 3

rd

order loop

Usually believed to be similar as the 2

nd

order loop

Actually quite different from the 2

nd

order

loop case

Jitter peaking always exists even with very

large

Need to be treated carefully

17

Jitter peaking is dependent on and m

m=0 (2nd loop)

jitter peaking can be

reduced or eliminated by using

large

m>0 (3rd loop)

is quite small, increasing

will decrease the jitter

peaking;

is larger than a threshold

value

m

, increasing will

increase the jitter peaking

Jitter peaking versus damping ratio and capacitance ratio

18

How to achieve the minimum jitter peaking

For given m, there exists the

minimum jitter peaking

--the minimum jitter peaking

can be viewed as a function of

m: JP(m)

The minimum jitter peaking

under a given m is achieved

only by using a proper

-- should be a function of m:

m

(m)

JP(m)

m(m)

19

Sampling effect of phase detector

The phase detector has sampling effect,

especially when its rate is not much higher

than the loop cut-off frequency

Approximate TF of phase detector :

2

1 e - 1

) (

P

-sT

P

PD

sT

s H

20

Jitter Peaking w/ PD Sampling Effect

It causes the jitter

peaking worse

when is very small, jitter

peaking decreases when

increases;

when becomes larger

than

m

, jitter peaking

increases with ;

when is larger than

m2

,

jitter peaking decreases

when is increased further

21

JP(m) and

m

(m) with sampling effect

JP(m) with sampling effect

m

(m) with sampling effect

22

Tables of JP(m) and

m

(m) for

practical design

23

Design procedures of charge pump PLLs

for jitter transfer characteristic optimization

1. Decide the maximum tolerated jitter peaking and find

capacitance ratio m using JP(m).

2. Use

m

(m) to find the optimal damping ratio value m;

3. Decide

n

according to the application, choose

reasonable K

VCO

, and calculate I

p

, R, C

1

and C

2

;

4. Use time domain simulation to verify that the expected

jitter transfer performance can be achieved

24

Design example

Target: to design a

2.5GHz CP PLL, meet

the jitter specification

Design parameters:

m=0.005 and =5.0

Simulation result: jitter

peaking is only 0.078dB

Jitter transfer characteristic of the designed PLL

25

More Discussion on Loop Transfer Function

The above discussion suggests to use

very small m to meet the jitter peaking

However, if m is too small, the effect of the

second capacitor can even be ignored

Compromise should be made between

jitter peaking and other performance

26

Charge pump PLL calibration

Purpose: make the loop transfer

characteristic meet the spec

Calibration types:

Component calibration

Loop calibration

27

Charge Pump Calibration

Purpose: minimize the mismatching

between UP and DOWN current

Method: switch small current sources

UP

DN

I

up

I

dn

UP

DN

I

up

I

dn

I

CAL

I

CAL I

CAL

I

CAL

28

Charge Pump Calibration

Procedure

Use the UP or Down current to

charge/discharge a capacitor

Compare the time difference and calculate

the calibration code

UP

DN

I

up

I

dn

Vref

Comparator

Counter

Ref CLK

R/S

29

VCO Coarse Tuning

Purpose: to speed frequency tracking

Method: make use of the coarse tuning

functionality of the VCO

When extreme high frequency range is

desired, double VCOs can be used to help

achieve fine frequency tuning resolution

30

VCO Coarse Tuning Procedure

Apply different coarse tuning voltage

(output from a low resolution coarse tuning

DAC)

Measure VCO output frequency

respectively

Compare to the reference frequency

Write the desired DAC code into register

31

Time Constant Calibration

Purpose: calibrate the loop transfer

function time constant so that the 3-dB

frequency meets the spec

Method: switch small CAL capacitors

C

CAL

C

CAL C

CAL

C

CAL

32

Time Constant Calibration Procedure

t

RC

Vref

t V

X

) (

Vref

Comparator

Counter

Ref CLK

R

Vref

R

C

Vx

RC f Counter

ref

#

33

Loop Gain Calibration

Purpose: calibrate the loop transfer gain to

the desired value

Method: switch different charge pump

output current (K

VCO

is not changeable

usually)

You might also like

- A Verilog-A Cycle-To-cycle Jitter Measurement ModulDocument4 pagesA Verilog-A Cycle-To-cycle Jitter Measurement ModulLi FeiNo ratings yet

- PLL Design ReportDocument30 pagesPLL Design Reporthasin986No ratings yet

- Pspice Lab ManualDocument30 pagesPspice Lab ManualSrinivasarao ThumatiNo ratings yet

- Seminar TopicDocument36 pagesSeminar TopicNarasing ManeNo ratings yet

- Phase Locked Loop (PLL) Vineet SahulaDocument53 pagesPhase Locked Loop (PLL) Vineet SahulaVSNo ratings yet

- Chapter1 - Integrated-Circuit Logic FamilyDocument52 pagesChapter1 - Integrated-Circuit Logic FamilyTheodore KyriakopoulosNo ratings yet

- Chap10 Phase Locked LoopsDocument26 pagesChap10 Phase Locked LoopsAlaa TobasiNo ratings yet

- Chapter - 2 Analysis and Transmission of SignalsDocument42 pagesChapter - 2 Analysis and Transmission of SignalsTemesgen MollaNo ratings yet

- Eca Lab Manual PDFDocument56 pagesEca Lab Manual PDFrppvch100% (5)

- Microwave Filter Design and Implementation TechniquesDocument53 pagesMicrowave Filter Design and Implementation TechniqueskhyatichavdaNo ratings yet

- Lab 3.5.2 Challenge Frame Relay ConfigurationDocument4 pagesLab 3.5.2 Challenge Frame Relay ConfigurationMark Zovighian0% (1)

- Sta Notes 1671631469 PDFDocument47 pagesSta Notes 1671631469 PDFAathith SaiprasadNo ratings yet

- Vlsi Lab 1Document11 pagesVlsi Lab 1Shawon karmokar JotyNo ratings yet

- Lab TutorialDocument10 pagesLab TutorialMD JamalNo ratings yet

- VLSI 100 QuestionsDocument4 pagesVLSI 100 Questionsapi-3824368No ratings yet

- PLL CircuitsDocument20 pagesPLL CircuitsNeeresh KumarNo ratings yet

- FM - PM Demodulation - The Phase Lock LoopDocument5 pagesFM - PM Demodulation - The Phase Lock LoopSunit Kumar Sharma100% (1)

- Digital Modulation Course NotesDocument11 pagesDigital Modulation Course NotesCHIM ZOE CANDAWAN CATALANNo ratings yet

- Carry Skip AdderDocument9 pagesCarry Skip AdderSimranjeet SinghNo ratings yet

- (Ebook - Electronics) - Principles of PLL - Tutorial (Kroupa 2000)Document66 pages(Ebook - Electronics) - Principles of PLL - Tutorial (Kroupa 2000)양종렬No ratings yet

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDocument5 pagesLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Implementation of Digital Lock Using VHDLDocument13 pagesImplementation of Digital Lock Using VHDLVaibhav TripathiNo ratings yet

- EE-312 Signals & Systems Course OverviewDocument3 pagesEE-312 Signals & Systems Course OverviewHamza AyazNo ratings yet

- All Digital Phase Locked Loop Design and ImplementationDocument4 pagesAll Digital Phase Locked Loop Design and ImplementationAnton SaitovNo ratings yet

- (TI) PLL Performance, Simulation 5th Edition-Dean Banerjee PDFDocument497 pages(TI) PLL Performance, Simulation 5th Edition-Dean Banerjee PDFMuresan GabrielNo ratings yet

- LAb 1Document8 pagesLAb 1nazmyNo ratings yet

- High Range-Resolution TechniquesDocument54 pagesHigh Range-Resolution TechniquesZamanundaIEEENo ratings yet

- Digitally Controlled Buck Converter: Design and ImplementationDocument12 pagesDigitally Controlled Buck Converter: Design and ImplementationaaqibNo ratings yet

- Unit 2 - CMOS Logic, Fabrication and LayoutDocument34 pagesUnit 2 - CMOS Logic, Fabrication and LayoutphillipNo ratings yet

- Experiment02 PCM-EncodingDocument13 pagesExperiment02 PCM-EncodingMary Rose P Delos SantosNo ratings yet

- Some Solution For Optical NetworkingDocument21 pagesSome Solution For Optical NetworkinglimelemonstevenNo ratings yet

- EE365 MidTerm Final Solution PDFDocument11 pagesEE365 MidTerm Final Solution PDFAfnan FarooqNo ratings yet

- UNIT 3-2marks-FET PDFDocument9 pagesUNIT 3-2marks-FET PDFpriyanka236No ratings yet

- Full-Wave RectifierDocument7 pagesFull-Wave Rectifiermohdshujaat100% (2)

- Unit 3 Tuned AmplifierDocument89 pagesUnit 3 Tuned Amplifiermohan100% (1)

- Design of Analog FIltersDocument7 pagesDesign of Analog FIltersparshuram kumarNo ratings yet

- FM Generation and DetectionDocument12 pagesFM Generation and DetectionDaniel Toublant100% (2)

- QPSKDocument12 pagesQPSKATUL SACHAN100% (1)

- Adders and MultipliersDocument59 pagesAdders and Multipliersdbanbumani_501791840No ratings yet

- Network Analysis and SynthesisDocument2 pagesNetwork Analysis and SynthesisAnonymous Zzx3FSfpNo ratings yet

- CMOS Propagation Delay LabDocument12 pagesCMOS Propagation Delay LabcoolliardNo ratings yet

- AM Generation and Detection MethodsDocument26 pagesAM Generation and Detection MethodsKalpana KoppoluNo ratings yet

- Mixed Signal Lecture PLLDocument15 pagesMixed Signal Lecture PLLsheikhdanish17No ratings yet

- Stability CMOS Ring OscillatorDocument4 pagesStability CMOS Ring OscillatorkaaashuNo ratings yet

- MIT 6.341 Lecture 20 - The Goertzel Algorithm and Chirp TransformDocument4 pagesMIT 6.341 Lecture 20 - The Goertzel Algorithm and Chirp Transformc_mc2No ratings yet

- Vcos in Ads 699Document19 pagesVcos in Ads 699Amit JhaNo ratings yet

- Advanced CMOS CircuitsDocument20 pagesAdvanced CMOS CircuitsAnonymous IXvuFdeNo ratings yet

- Digital Signal Processing QuestionsDocument2 pagesDigital Signal Processing QuestionsTalha HabibNo ratings yet

- Control Systems IMP QUESTIONSDocument8 pagesControl Systems IMP QUESTIONSHarika HarikaNo ratings yet

- Unit I - Discrete State-Variable Technique Q.No Questions: Scalar Adder IntegratorDocument184 pagesUnit I - Discrete State-Variable Technique Q.No Questions: Scalar Adder IntegratorAgatha ChristieNo ratings yet

- Gain, Phase margins, compensatorsDocument10 pagesGain, Phase margins, compensatorszakiannuarNo ratings yet

- II yr/III Sem/Mech/EEE 2 Marks With Answers Unit-VDocument5 pagesII yr/III Sem/Mech/EEE 2 Marks With Answers Unit-VanunilaNo ratings yet

- Colpitts Oscillator Using Op Amp PDFDocument2 pagesColpitts Oscillator Using Op Amp PDFStewartNo ratings yet

- QUBE-Servo DC Motor ModelingDocument5 pagesQUBE-Servo DC Motor Modelingandres guerreroNo ratings yet

- High Efficiency RF and Microwave Solid State Power AmplifiersFrom EverandHigh Efficiency RF and Microwave Solid State Power AmplifiersRating: 1 out of 5 stars1/5 (1)

- High Voltage Direct Current Transmission: Converters, Systems and DC GridsFrom EverandHigh Voltage Direct Current Transmission: Converters, Systems and DC GridsNo ratings yet

- Optimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryFrom EverandOptimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryNo ratings yet

- Synthesizer TutorialDocument26 pagesSynthesizer Tutorialrah0987No ratings yet

- L.C Oscillator Tutorial: 1 AbstractDocument18 pagesL.C Oscillator Tutorial: 1 AbstractChi PhamNo ratings yet

- Library AnalogDialogue CD Vol33n1Document76 pagesLibrary AnalogDialogue CD Vol33n1rah0987No ratings yet

- CICC09 Paper19.3 PLL Loop MeasurementDocument4 pagesCICC09 Paper19.3 PLL Loop Measurementrah0987No ratings yet

- Understanding Circles and Their PropertiesDocument4 pagesUnderstanding Circles and Their Propertiesrah0987No ratings yet

- Schober SusanDocument1 pageSchober Susanrah0987No ratings yet

- ISSCC2010!13!2 SlidesDocument23 pagesISSCC2010!13!2 Slidesrah0987No ratings yet

- Analog Electronics1Document3 pagesAnalog Electronics1rah0987No ratings yet

- CICC09 Slides19.3 PLL Loop MeasurementDocument23 pagesCICC09 Slides19.3 PLL Loop Measurementrah0987No ratings yet

- CORDICDocument32 pagesCORDICrah0987No ratings yet

- A Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam HeydariDocument4 pagesA Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam Heydarirah0987No ratings yet

- Gate Ece 1996Document5 pagesGate Ece 1996Janmejay OjhaNo ratings yet

- Thesis PLLDocument44 pagesThesis PLLrah0987No ratings yet

- Kinget Ultra Low Voltage Analog RF April 2007Document45 pagesKinget Ultra Low Voltage Analog RF April 2007rah0987No ratings yet

- Voltage Controlled Oscillator With TSPC Delay StageDocument4 pagesVoltage Controlled Oscillator With TSPC Delay Stagerah0987No ratings yet

- Gate Ece 1994Document4 pagesGate Ece 1994Janmejay OjhaNo ratings yet

- Assignment (40%) : A) Formulate The Problem As LPM B) Solve The LPM Using Simplex AlgorithmDocument5 pagesAssignment (40%) : A) Formulate The Problem As LPM B) Solve The LPM Using Simplex Algorithmet100% (1)

- Article 680 Swimming Pools, Spas, Hot Tubs, Fountains, and Similar InstallationsDocument13 pagesArticle 680 Swimming Pools, Spas, Hot Tubs, Fountains, and Similar InstallationsDocente 361 UMECITNo ratings yet

- C146-94a (2014) Standard Test Methods For Chemical Analysis of Glass SandDocument12 pagesC146-94a (2014) Standard Test Methods For Chemical Analysis of Glass SandAhmed AlzubaidiNo ratings yet

- High Current Transistor SpecsDocument5 pagesHigh Current Transistor SpecsamernasserNo ratings yet

- Noam Text ליגר טסקט םעֹנDocument20 pagesNoam Text ליגר טסקט םעֹנGemma gladeNo ratings yet

- Industrial Wire Cutting Machine: A Senior Capstone Design ProjectDocument17 pagesIndustrial Wire Cutting Machine: A Senior Capstone Design ProjectTruta IonutNo ratings yet

- Evolution of Telecommunications GenerationsDocument45 pagesEvolution of Telecommunications GenerationsSai RamNo ratings yet

- SDS WD-40 Aerosol-AsiaDocument4 pagesSDS WD-40 Aerosol-AsiazieyzzNo ratings yet

- Module 1 SIMPLE INTERESTDocument15 pagesModule 1 SIMPLE INTERESTElle Villanueva VlogNo ratings yet

- School Uniforms Argumentative EssayDocument6 pagesSchool Uniforms Argumentative Essayfllahvwhd100% (2)

- TFT-LCD TV/MONITOR SERVICE MANUALDocument54 pagesTFT-LCD TV/MONITOR SERVICE MANUALhimkoNo ratings yet

- Energies: Review of Flow-Control Devices For Wind-Turbine Performance EnhancementDocument35 pagesEnergies: Review of Flow-Control Devices For Wind-Turbine Performance Enhancementkarthikeyankv.mech DscetNo ratings yet

- Paper 2 Answer SPMDocument12 pagesPaper 2 Answer SPMSylarkNo ratings yet

- Discrete Math Assignment on Recurrence Relations, Graph Theory and Boolean AlgebraDocument6 pagesDiscrete Math Assignment on Recurrence Relations, Graph Theory and Boolean AlgebralakkajaoNo ratings yet

- Embraer ePerf Tablet App Calculates Takeoff & Landing Performance OfflineDocument8 pagesEmbraer ePerf Tablet App Calculates Takeoff & Landing Performance OfflinewilmerNo ratings yet

- Phil of DepressDocument11 pagesPhil of DepressPriyo DjatmikoNo ratings yet

- USTHB Master's Program Technical English Lesson on Reflexive Pronouns and Antenna FundamentalsDocument4 pagesUSTHB Master's Program Technical English Lesson on Reflexive Pronouns and Antenna Fundamentalsmartin23No ratings yet

- Volume 5 Issue 1Document625 pagesVolume 5 Issue 1IJAET Journal0% (1)

- Trip WireDocument19 pagesTrip Wirepinky065558100% (2)

- SurveillanceDocument17 pagesSurveillanceGaurav Khanna100% (1)

- BF 00571142Document1 pageBF 00571142Tymoteusz DziedzicNo ratings yet

- Unit 30 WorkDocument2 pagesUnit 30 WorkThanh HàNo ratings yet

- WINTER 2021 SYLLABUS All Lab Classes - Docx-2Document7 pagesWINTER 2021 SYLLABUS All Lab Classes - Docx-2Sushi M.SNo ratings yet

- Single Point Loading Working Model Specifications and Parts OverviewDocument4 pagesSingle Point Loading Working Model Specifications and Parts OverviewAnonymous CYdagI100% (1)

- Zelenbabini Darovi Ivana N Esic - CompressDocument167 pagesZelenbabini Darovi Ivana N Esic - CompressСања Р.0% (1)

- Safety Steering System Alarm Code GuideDocument43 pagesSafety Steering System Alarm Code GuideIsrael Michaud84% (19)

- Lesson Plan in Science 10 2nd QuarterDocument5 pagesLesson Plan in Science 10 2nd QuarterJenevev81% (21)

- Maintenance Procedure For Switchyard Equipment Volume-II (EHDocument39 pagesMaintenance Procedure For Switchyard Equipment Volume-II (EHbisas_rishiNo ratings yet

- Nordson EFD Ultimus I II Operating ManualDocument32 pagesNordson EFD Ultimus I II Operating ManualFernando KrauchukNo ratings yet

- Career Paralysis (PT 1) - Five Reasons Why Our Brains Get Stuck Making Career DecisionsDocument99 pagesCareer Paralysis (PT 1) - Five Reasons Why Our Brains Get Stuck Making Career DecisionsToni ErdfeldNo ratings yet