Professional Documents

Culture Documents

Sequential Digital Circuits Flip Flops Latches Edge Triggered

Uploaded by

vikramkolanu100%(2)100% found this document useful (2 votes)

76 views22 pagesdesign

Original Title

FlipFlops

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentdesign

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

100%(2)100% found this document useful (2 votes)

76 views22 pagesSequential Digital Circuits Flip Flops Latches Edge Triggered

Uploaded by

vikramkolanudesign

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 22

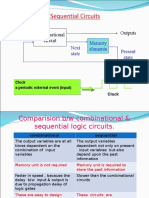

Sequential Digital Circuits

Dr. Costas Kyriacou and Dr. Konstantinos Tatas

ACOE161 - Digital Logic for Computers

- Frederick University

2

Sequential Digital Circuits

Sequential circuits are digital circuits in which the outputs

depend not only on the current inputs, but also on the previous

state of the output.

They basic sequential circuit elements can be divided in two

categories:

Level-sensitive (Latches)

High-level sensitive

Low-level sensitive

Edge-triggered (Flip-flops)

Rising (positive) edge triggered

Falling (negative) edge triggered

Dual-edge triggered

ACOE161 - Digital Logic for Computers

- Frederick University

3

The Set/Reset (SR) Latch

The Set/Reset latch is the most basic unit of sequential digital circuits. It has two

inputs (S and R) and two outputs outputs Q and Q. The two outputs must always be

complementary, i.e if Q is 0 then Q must be 1, and vice-versa. The S input sets the

Q output to a logic 1. The R input resets the Q output to a logic 0.

S

R

Q

Q

R

S

Q

Q

S R Q+

0 0

0 1

1 0

1 1

Function

S Q

R Q

Logic Symbol

Truth Table Circuit Diagram

Q

0

1

0

Q+

Q Latch

Reset

Set

1

0

0

Illegal

ACOE161 - Digital Logic for Computers

- Frederick University

4

The Gated Set/Reset (SR) Latch

To be able to control when the S and R inputs of the SR latch can be applied to the

latch and thus change the outputs, an extra input is used. This input is called the

Enable. If the Enable is 0 then the S and R inputs have no effect on the outputs of the

SR latch. If the Enable is 1 then the Gated SR latch behaves as a normal SR latch.

Logic Symbol

Truth Table

S

R

Q

Circuit Diagram

S Q

R Q Q

EN

S R EN Q+

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Truth Table

S Q

R Q

EN

S R EN Q+

0 X X

1 0 0

1 0 1

1 1 0

1 1 1

Function

Q

Q

Q

Q

Q

0

1

U

ACOE161 - Digital Logic for Computers

- Frederick University

5

SR Latch :- Example

Complete the timing diagrams for :

(a) Simple SR Latch

(b) SR Latch with Enable input.

Assume that for both cases the Q output is initially at logic zero.

Set

Reset

Q

Set

Reset

Q

Enable

(b) (a)

ACOE161 - Digital Logic for Computers

- Frederick University

6

The Data (D) Latch

A problem with the SR latch is that the S and R inputs can not be at logic 1 at the

same time. To ensure that this can not happen, the S and R inputs can by connected

through an inverter. In this case the Q output is always the same as the input, and the

latch is called the Data or D latch. The D latch is used in Registers and memory

devices.

Logic Symbol

Truth Table

D Q EN Q+

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Truth Table

D EN Q+

0 0

1 0

1 0

1 1

Function

D

Q

Circuit Diagram

Q

EN

S Q

R Q

D Q

Q

EN

Q

Q

Q

Q

0

0

1

1

ACOE161 - Digital Logic for Computers

- Frederick University

7

The JK Latch

Another way to ensure that the S and R inputs can not be at logic 1 simultaneously, is

to cross connect the Q and Q outputs with the S and R inputs through AND gates.

The latch obtained is called the JK latch. In the J and K inputs are both 1 then the Q

output will change state (Toggle) for as long as the Enable 1, thus the output will be

unstable. This problem is avoided by ensuring that the Enable is at logic 1 only for a

very short time, using edge detection circuits.

Logic Symbol

Truth Table

J K EN Q+

0 X X

1 0 0

1 0 0

1 0 1

1 0 1

1 1 0

1 1 0

1 1 1

1

X

0

1

0

1

0

1

0

1 1 1

Q

Truth Table

J EN Q+

0 X

0 1

1 0

1 1

Function

1 1

K

X

0

1

0

1

J Q

Circuit Diagram

Q

EN

S Q

R Q

J Q

Q

EN

K

K

Q

0

1

0

0

1

1

1

0

ACOE161 - Digital Logic for Computers

- Frederick University

8

Latches and Flip-Flops

Latches are also called transparent or level triggered flip flops,

because the change on the outputs will follow the changes of the

inputs as long as the Enable input is set.

Edge triggered flip flops are the flip flops that change there outputs

only at the transition of the Enable input. The enable is called the

Clock input.

ACOE161 - Digital Logic for Computers

- Frederick University

9

Edge Detection Circuits

Edge detection circuits are used to detect the transition of the Enable from logic 0 to

logic 1 (positive edge) or from logic 1 to logic 0 (negative edge). The operation of the

edge detection circuits shown below is based on the fact that there is a time delay

between the change of the input of a gate and the change at the output. This delay is

in the order of a few nanoseconds. The Enable in this case is called the Clock (CLK)

EN

EN'

EN

EN

EN'

EN

EN

EN'

EN

EN

EN'

EN

EN

Positive Edge Detection Negative Edge Detection

EN

ACOE161 - Digital Logic for Computers

- Frederick University

10

The JK Edge Triggered Flip Flop

The JK edge triggered flip flop can be obtained by inserting an edge detection circuit

at the Enable (CLK) input of a JK latch. This ensures that the outputs of the flip flop

will change only when the CLK changes (0 to 1 for +ve edge or 1 to 0 for ve edge)

Logic Symbol

Positive Edge JK Flip Flop

J CLK QN+1

X

0

0

1

Function

1

K

X

0

1

0

1

J

Q

Q

CLK

S Q

R Q

J Q

Q K

K

CLK

Logic Symbol

Negative Edge JK Flip Flop

J CLK QN+1

X

0

0

1

Function

1

K

X

0

1

0

1

J

Q

Q

CLK

S Q

R Q

J Q

Q K

K

CLK

Q

0

1

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

11

The D Edge Triggered Flip Flop

The D edge triggered flip flop can be obtained by connecting the J with the K inputs

of a JK flip through an inverter as shown below. The D edge trigger can also be

obtained by connecting the S with the R inputs of a SR edge triggered flip flop

through an inverter.

Logic Symbol

Positive Edge D Flip Flop

CLK QN+1 Function D

X

0

1

D Q

Q

CLK

CLK

D Q

Q

J Q

Q K

Logic Symbol

Negative Edge D Flip Flop

CLK QN+1 Function D

X

0

1

D Q

Q

CLK

CLK

D Q

Q

J Q

Q K

0

1

Q

0

1

Q

ACOE161 - Digital Logic for Computers

- Frederick University

12

The Toggle (T) Edge Triggered Flip Flop

The T edge triggered flip flop can be obtained by connecting the J with the K inputs

of a JK flip directly. When T is zero then both J and K are zero and the Q output does

not change. When T is one then both J and K are one and the Q output will change to

the opposite state, or toggle.

Logic Symbol

Positive Edge T Flip Flop

T Q

Q

CLK

CLK

T Q

Q

J Q

Q K

Logic Symbol

Negative Edge T Flip Flop

T Q

Q

CLK

CLK

T Q

Q

J Q

Q K

CLK QN+1 Function T

X

0

1

CLK QN+1 Function T

X

0

1

Q

Q

Q

Q

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

13

Flip Flops with asynchronous inputs (Preset and Clear)

Two extra inputs are often found on flip flops, that either clear or preset the output.

These inputs are effective at any time, thus are called asynchronous. If the Clear is at

logic 0 then the output is forced to 0, irrespective of the other normal inputs. If the

Preset is at logic 0 then the output is forced to 1, irrespective of the other normal

inputs. The preset and the clear inputs can not be 0 simultaneously. In the Preset and

Clear are both 1 then the flip flop behaves according to its normal truth table.

Positive Edge JK Flip Flop with Preset and Clear

PRESET

J Q

Q K

CLR

PR

CLEAR

CLK QN+1 Function K

X

X

X

0

1

1

J

X

X

0

0

1

X

CLR

1

0

1

1

1

0

PR

0

1

1

1

1

0

1 0

1 1

1

Q

0

1

Q

0

ACOE161 - Digital Logic for Computers

- Frederick University

14

Data (D) Latch :- Example

Complete the timing diagrams for :

(a) D Latch

(b) JK Latch

Assume that for both cases the Q output is initially at logic zero.

Enable

Data (D)

Q

J

K

Q

Enable

(b) (a)

ACOE161 - Digital Logic for Computers

- Frederick University

15

JK Edge Triggered Flip Flop :- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered JK Flip Flop

(b) Negative Edge Triggered JK Flip Flop

Assume that for both cases the Q output is initially at logic zero.

J

K

Q

CLK

(b) (a)

J

K

Q

CLK

ACOE161 - Digital Logic for Computers

- Frederick University

16

D and T Edge Triggered Flip Flops :- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered D Flip Flop

(b) Positive Edge Triggered T Flip Flop

(c) Negative Edge Triggered T Flip Flop

(d) Negative Edge Triggered D Flip Flop

(b) (a)

D

Q

CLK

D

Q

CLK

(d) (c)

T

Q

CLK

T

Q

CLK

ACOE161 - Digital Logic for Computers

- Frederick University

17

JK Flip Flop With Preset and Clear:- Example

Complete the timing diagrams for :

(a) Positive Edge Triggered JK Flip Flop

(b) Negative Edge Triggered JK Flip Flop.

Assume that for both cases the Q output is initially at logic zero.

(b) (a)

J

K

Q

CLK

CLR

PR

J

K

Q

CLK

CLR

PR

ACOE161 - Digital Logic for Computers

- Frederick University

18

Level Triggered Master Slave JK Flip Flop

A Master Slave flip flop is obtained by connecting two SR latches as shown below. This flip

flop reads the inputs when the clock is 1 and changes the output when the clock is at logic

zero.

Logic Symbol

J

K

Master

S Q

R Q

CLK

Truth Table

J K CLK Q

0 0

0 1

1 0

1 1

Function

Q

Q

S Q

R Q

Slave

J

K

CLK

Q

Q

J

K

Q

CLK

(a) Positive Master Slave JK Flip Flop

J

K

Q

CLK

(b) Negative Master Slave JK Flip Flop

ACOE161 - Digital Logic for Computers

- Frederick University

19

Edge Triggered Master Slave JK Flip Flop

A Master Slave flip flop is obtained by connecting two SR latches as shown below. This flip

flop reads the inputs when the clock is 1 and changes the output when the clock is at logic

zero.

J

K

Q

CLK

(a) Positive Master Slave JK Flip Flop

J

K

Q

CLK

(b) Negative Master Slave JK Flip Flop

Logic Symbol

J

K

Master

S Q

R Q

CLK

Truth Table

J K CLK Q

0 0

0 1

1 0

1 1

Function

Q

Q

S Q

R Q

Slave

J

K

Q

Q

ACOE161 - Digital Logic for Computers

- Frederick University

20

Sequential circuit example 1

Q

Q

SET

CLR

D

2-to-1

MUX

A0

A1

S

Clock

1 2 3 4 5 6 7 8 9 10

Clock

A0

A1

S

D

Q

ACOE161 - Digital Logic for Computers

- Frederick University

21

Sequential circuit example 2

Q

Q

SET

CLR

D

Clock

1 2 3 4 5 6 7 8 9 10

Clock

Q

Q

D

ACOE161 - Digital Logic for Computers

- Frederick University

22

Sequential circuit example 3

Q

Q

SET

CLR

D

CP

FULL ADDER

X

Y

Z

C

S

/T

CP

X

Y

Z

S

C

You might also like

- Architecture of FPGAs and CPLDS: A TutorialDocument41 pagesArchitecture of FPGAs and CPLDS: A Tutorialgongster100% (5)

- Gmat Handbook: Everything You Need To Know and Agree To When Scheduling Your GMAT ExamDocument17 pagesGmat Handbook: Everything You Need To Know and Agree To When Scheduling Your GMAT ExamGirish SeshadriNo ratings yet

- SPI I2C Interface AnDocument13 pagesSPI I2C Interface AnNivin PaulNo ratings yet

- ECE545 Lecture5 Dataflow 6Document15 pagesECE545 Lecture5 Dataflow 6Utpal DasNo ratings yet

- FPGA System Design Course OverviewDocument30 pagesFPGA System Design Course OverviewKrishna Kumar100% (1)

- ArmpptDocument168 pagesArmpptamit_k25No ratings yet

- 03 PCIe 3.0 PHY Electrical Layer Requirements FinalDocument49 pages03 PCIe 3.0 PHY Electrical Layer Requirements FinalSubhadeep DattaNo ratings yet

- Verilog Imp...Document105 pagesVerilog Imp...Arun JyothiNo ratings yet

- Cell Characterization ConceptsDocument70 pagesCell Characterization Conceptshex0x1No ratings yet

- Pal and PlaDocument10 pagesPal and PlaRahul Kumar67% (6)

- Basic Terminology in Physical Design VLSI Basics and Interview QuestionsDocument10 pagesBasic Terminology in Physical Design VLSI Basics and Interview Questionsdivya gaddeNo ratings yet

- Design of Analog FIltersDocument7 pagesDesign of Analog FIltersparshuram kumarNo ratings yet

- Image Processing Using Fpgas: ImagingDocument4 pagesImage Processing Using Fpgas: ImagingAnonymous s516rsNo ratings yet

- Experiment Sheet - FPGA Design ALLDocument38 pagesExperiment Sheet - FPGA Design ALLSidney O. EbotNo ratings yet

- CharFlo-Memory Compiler Tech Rev10.3-2010JuneDocument33 pagesCharFlo-Memory Compiler Tech Rev10.3-2010Junevikramkolanu100% (1)

- FPGA Selection for Analog Signal Conversion and Ethernet Data TransferDocument6 pagesFPGA Selection for Analog Signal Conversion and Ethernet Data TransferGurinder Pal SinghNo ratings yet

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionFrom EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNo ratings yet

- Multi Cycle PathsDocument15 pagesMulti Cycle PathsgpraveenroyNo ratings yet

- Activity 2.2.3 Universal Gates: NOR Only Logic Design: Booth A B+C DDocument7 pagesActivity 2.2.3 Universal Gates: NOR Only Logic Design: Booth A B+C DZarwa Rizvi0% (1)

- Generate VHDL Code From Matlab Code: Bookmark This PageDocument10 pagesGenerate VHDL Code From Matlab Code: Bookmark This PageAnonymous JnvCyu85No ratings yet

- VHDL PDFDocument112 pagesVHDL PDFvivek patelNo ratings yet

- ADPLL Design and Implementation On FPGADocument6 pagesADPLL Design and Implementation On FPGANavathej BangariNo ratings yet

- DSP Processor FundamentalsDocument58 pagesDSP Processor FundamentalsSayee KrishnaNo ratings yet

- Introduction To VHDLDocument88 pagesIntroduction To VHDLpusd_90No ratings yet

- Orcad PSpice DesignerDocument47 pagesOrcad PSpice DesignerAishwarya JS100% (1)

- Dijsktra ThesisDocument65 pagesDijsktra ThesisGupta AakashNo ratings yet

- Ap7202-Asic and FpgaDocument12 pagesAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENo ratings yet

- Fpga Programming Using Verilog HDL LanguageDocument89 pagesFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- Zynq 7020Document4 pagesZynq 7020NGUYỄN HOÀNG LINHNo ratings yet

- Ch04 - Multimedia Element-ImagesDocument63 pagesCh04 - Multimedia Element-Imagessu6aNo ratings yet

- Low Power VLSI DesignDocument20 pagesLow Power VLSI DesignansuharshNo ratings yet

- D.S.P/MATLAB Theory & ExperimentsDocument57 pagesD.S.P/MATLAB Theory & ExperimentsNandagopal Sivakumar50% (4)

- Design of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGADocument7 pagesDesign of VLSI Architecture For A Flexible Testbed of Artificial Neural Network For Training and Testing On FPGAInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Eric Thesis SlidesDocument43 pagesEric Thesis SlidesHumberto JuniorNo ratings yet

- CPLDDocument30 pagesCPLDNanda Ganesh Kumar KingNo ratings yet

- 2D NMR SpectrosDocument12 pages2D NMR Spectrossatheeshpharma6No ratings yet

- Gaussian Random Number Generator Using Boxmuller MethodDocument27 pagesGaussian Random Number Generator Using Boxmuller MethodAbhijeet Singh KatiyarNo ratings yet

- Decision Feedback EqualiserDocument9 pagesDecision Feedback EqualiserHari PrasathNo ratings yet

- Design and Implementation of 2 Bits BCH Error Correcting Codes Using FPGADocument7 pagesDesign and Implementation of 2 Bits BCH Error Correcting Codes Using FPGAJournal of TelecommunicationsNo ratings yet

- Master Thesis FPGADocument144 pagesMaster Thesis FPGAGaye Güngör AktürkNo ratings yet

- Tiger SHARC ProcessorDocument36 pagesTiger SHARC ProcessorChintan PatelNo ratings yet

- Product OverviewDocument9 pagesProduct OverviewUsha KrishnaNo ratings yet

- Systemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammDocument26 pagesSystemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammAamir HabibNo ratings yet

- Digital Design Through Verilog HDL Course Outcomes For LabDocument1 pageDigital Design Through Verilog HDL Course Outcomes For LabSyed AshmadNo ratings yet

- ASAP7 TutorialDocument52 pagesASAP7 TutorialAtmadeep DeyNo ratings yet

- Designing Memory Array Subsystems CH 12 PDFDocument87 pagesDesigning Memory Array Subsystems CH 12 PDFrao rehNo ratings yet

- VHDL BRAM and ROM ExamplesDocument9 pagesVHDL BRAM and ROM ExamplesGmit MandyaNo ratings yet

- Digital System Design Using Verilog December 2011Document1 pageDigital System Design Using Verilog December 2011Vinayaka HmNo ratings yet

- Data Communication FaqDocument4 pagesData Communication Faqdolon10No ratings yet

- Assignment4 PDFDocument9 pagesAssignment4 PDFlavishNo ratings yet

- Anti FuseDocument2 pagesAnti FuseRahmatullah JatoiNo ratings yet

- DDR Routing GuidelinesDocument14 pagesDDR Routing GuidelinesNarayanan MayandiNo ratings yet

- Representing Multimedia Information DigitallyDocument30 pagesRepresenting Multimedia Information DigitallyNeil LewisNo ratings yet

- SAR ADC TutorialDocument13 pagesSAR ADC Tutorialvigneshk100% (3)

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- UART Is A Asynchronous Transmission Protocol To Communicate Based On The Baud Ra TeDocument1 pageUART Is A Asynchronous Transmission Protocol To Communicate Based On The Baud Ra TevikramkolanuNo ratings yet

- Exam Notice CGLE 12-02-2016Document54 pagesExam Notice CGLE 12-02-2016Saicharan BashabathiniNo ratings yet

- CDVL Application 2015Document2 pagesCDVL Application 2015KaranGargNo ratings yet

- BCD-to-Gray Code Converter . - Example Truth TableDocument3 pagesBCD-to-Gray Code Converter . - Example Truth TableDen GuizzaganNo ratings yet

- Prepare for ECE GATE 2016Document14 pagesPrepare for ECE GATE 2016vikramkolanuNo ratings yet

- RTL Vs Technology SchematicDocument1 pageRTL Vs Technology SchematicvikramkolanuNo ratings yet

- April 2004Document15 pagesApril 2004vikramkolanuNo ratings yet

- FlipflopsDocument80 pagesFlipflopsvikramkolanuNo ratings yet

- BCD-to-Gray Code Converter . - Example Truth TableDocument3 pagesBCD-to-Gray Code Converter . - Example Truth TableDen GuizzaganNo ratings yet

- 1Document2 pages1Mahesh PandeyNo ratings yet

- Fundamentals of Computer Systems: Finite State MachinesDocument32 pagesFundamentals of Computer Systems: Finite State Machinesjp_20_20No ratings yet

- SomiDocument1 pageSomivikramkolanuNo ratings yet

- 23 TrafficLightControllerDocument3 pages23 TrafficLightControllerKishore Kumar100% (1)

- TimeDocument1 pageTimevikramkolanuNo ratings yet

- CounterDocument19 pagesCounterPayal SinghalNo ratings yet

- 001 Course OutlineDocument35 pages001 Course OutlineJubin JainNo ratings yet

- Chp8 PDFDocument15 pagesChp8 PDFRaffi SkNo ratings yet

- Yacoub-Ammar FSM CH 10Document25 pagesYacoub-Ammar FSM CH 10Anubroto MitroNo ratings yet

- Tocc DownDocument19 pagesTocc DownvikramkolanuNo ratings yet

- 6htxhqwldo /RJLF, Psohphqwdwlrq $evwudfwlrq Ri 6Wdwh (OhphqwvDocument13 pages6htxhqwldo /RJLF, Psohphqwdwlrq $evwudfwlrq Ri 6Wdwh (OhphqwvakzeNo ratings yet

- State: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedDocument8 pagesState: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedvikramkolanuNo ratings yet

- Career Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailDocument2 pagesCareer Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailvikramkolanuNo ratings yet

- UnixDocument3 pagesUnixvenitiaNo ratings yet

- One-bit counter with reset using Moore and Mealy modelsDocument4 pagesOne-bit counter with reset using Moore and Mealy modelsvikramkolanuNo ratings yet

- Working With Combinational Logic: SimplificationDocument24 pagesWorking With Combinational Logic: SimplificationMain RizwanNo ratings yet

- Dflipfop Easy Problem Marvin JavierDocument9 pagesDflipfop Easy Problem Marvin JavierAngelica FangonNo ratings yet

- Module 6Document40 pagesModule 6Mani RohithNo ratings yet

- COA - Lab Manual 2023-24 - SolutionsDocument32 pagesCOA - Lab Manual 2023-24 - SolutionsVinay AgarwalNo ratings yet

- Universal Logic Gates ExplainedDocument8 pagesUniversal Logic Gates Explainedkushagra108No ratings yet

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document5 pagesPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNo ratings yet

- LAB-4 Analysis of Universal Gates ICs With Truth Tables and Implementation of The Digital CircuitsDocument11 pagesLAB-4 Analysis of Universal Gates ICs With Truth Tables and Implementation of The Digital CircuitsNaeem AtifNo ratings yet

- Full AdderDocument4 pagesFull AdderSuleiman Abubakar AuduNo ratings yet

- Digital Fundamentals: With PLD ProgrammingDocument29 pagesDigital Fundamentals: With PLD ProgrammingNeslynNo ratings yet

- Flip FlopDocument26 pagesFlip FlopFrancesco De FlorenceNo ratings yet

- Basic Logic GatesDocument5 pagesBasic Logic GatesVasu ReddyNo ratings yet

- DcsDocument50 pagesDcskartikNo ratings yet

- Objective:: The Objectives of This Experiment WereDocument12 pagesObjective:: The Objectives of This Experiment WereRiffat GulNo ratings yet

- Ventics - Logics Exp3Document19 pagesVentics - Logics Exp3Junjun VenticNo ratings yet

- 18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofDocument8 pages18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofAniket RanjanNo ratings yet

- EED Polytechnic MSU: Experiment No.1Document7 pagesEED Polytechnic MSU: Experiment No.1Dharmistha VishwakarmaNo ratings yet

- Experiment 4Document5 pagesExperiment 4AAAAALLENNNo ratings yet

- Topalian JavaScript Math Generator by Christopher TopalianDocument25 pagesTopalian JavaScript Math Generator by Christopher TopalianCollegeOfScriptingNo ratings yet

- Experiment 1.3 Bablu KUMAR (DIGITAL)Document6 pagesExperiment 1.3 Bablu KUMAR (DIGITAL)Bablu RaazNo ratings yet

- Understand Boolean Logic of NOR Gate and NAND Gate: Syed Mohsin Ali Shah Digital Logic Design LAB Spring 2019Document10 pagesUnderstand Boolean Logic of NOR Gate and NAND Gate: Syed Mohsin Ali Shah Digital Logic Design LAB Spring 2019Muhammad SufyanNo ratings yet

- 16 Master Slave Flip FlopsDocument3 pages16 Master Slave Flip FlopsTADeNo ratings yet

- Sequential Logic CircuitsDocument34 pagesSequential Logic CircuitsRockRahilNo ratings yet

- Chapter 7 - Flip FlopsDocument12 pagesChapter 7 - Flip FlopsAmeer AzharNo ratings yet

- VLSI Design (Online Lectures) Assignment-1Document3 pagesVLSI Design (Online Lectures) Assignment-1TarushiNo ratings yet

- Nand and NOR Experiment - Docx RevisedDocument7 pagesNand and NOR Experiment - Docx Revisedjoy escandorNo ratings yet

- Flip FlopsDocument18 pagesFlip FlopsveNo ratings yet

- Logic GatesDocument20 pagesLogic GatesNor Anis SalehNo ratings yet

- Mri Airis II MRPSC Cz67ac-S13Document370 pagesMri Airis II MRPSC Cz67ac-S13Kosmic AdminNo ratings yet

- Lab Experiment-ME - 12Document7 pagesLab Experiment-ME - 12Saad khanNo ratings yet