Professional Documents

Culture Documents

Digital Design and System Implementation

Uploaded by

meet_kaur8659590 ratings0% found this document useful (0 votes)

16 views32 pagesdigial design

Original Title

26-DigitalDesign

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentdigial design

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

16 views32 pagesDigital Design and System Implementation

Uploaded by

meet_kaur865959digial design

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 32

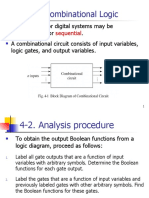

CS 150 Spring 2007 - Lec #26 Digital Design 1

Digital Design and System Implementation

Overview of Physical Implementations

CMOS devices

CMOS transistor circuit functional behavior

Basic logic gates

Transmission gates

Tri-state buffers

Flip-flops vs. latches revisited

CS 150 Spring 2007 - Lec #26 Digital Design 2

The stuff out of which we make systems

Overview of Physical Implementations

Integrated Circuits (ICs)

Combinational logic circuits, memory elements, analog interfaces

Printed Circuits (PC) boards

substrate for ICs and interconnection, distribution of CLK, Vdd, and

GND signals, heat dissipation

Power Supplies

Converts line AC voltage to regulated DC low voltage levels

Chassis (rack, card case, ...)

1-25 conductive layers

holds boards, power supply, fans, provides physical interface to user

or other systems

Connectors and Cables

CS 150 Spring 2007 - Lec #26 Digital Design 3

Integrated Circuits

Primarily Crystalline Silicon

1mm - 25mm on a side

200 - 400M effective transistors

(50 - 75M logic gates")

3 - 10 conductive layers

2007 feature size ~ 65nm = 0.065 x 10

-6

m

45nm coming on line

CMOS most common -

complementary metal oxide semiconductor

Package provides:

Spreading of chip-level signal paths to

board-level

Heat dissipation.

Ceramic or plastic with gold wires

Chip in Package

CS 150 Spring 2007 - Lec #26 Digital Design 4

Multichip Modules (MCMs)

Multiple chips directly connected to a substrate

(silicon, ceramic, plastic, fiberglass) without chip packages

Printed Circuit Boards

Fiberglass or ceramic

1-20in on a side

IC packages are

soldered down

CS 150 Spring 2007 - Lec #26 Digital Design 5

Integrated Circuits

Moores Law has fueled innovation for the last 3 decades

Number of transistors on a die doubles every 18 months.

What are the consequences of Moores law?

CS 150 Spring 2007 - Lec #26 Digital Design 6

Integrated Circuits

Uses for Digital IC technology today:

Standard microprocessors

Used in desktop PCs, and embedded applications (ex: automotive)

Simple system design (mostly software development)

Memory chips (DRAM, SRAM)

Application specific ICs (ASICs)

custom designed to match particular application

can be optimized for low-power, low-cost, high-performance

high-design cost / relatively low manufacturing cost

Field programmable logic devices (FPGAs, CPLDs)

customized to particular application after fabrication

short time to market

relatively high part cost

Standardized low-density components

still manufactured for compatibility with older system designs

CS 150 Spring 2007 - Lec #26 Digital Design 7

Cross Section

The gate acts like a capacitor. A high voltage on

the gate attracts charge into the channel. If a

voltage exists between the source and drain a

current will flow. In its simplest

approximation, the device acts like a switch.

Top View

MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

nFET

pFET

CMOS Devices

CS 150 Spring 2007 - Lec #26 Digital Design 11

Logic and Layout: NAND Gate

CS 150 Spring 2007 - Lec #26 Digital Design 12

Transmission gates are the way to build switches in CMOS

In general, both transistor types are needed:

nFET to pass zeros

pFET to pass ones

The transmission gate is bi-directional (unlike logic gates)

Does not directly connect to Vdd and GND, but can be combined with

logic gates or buffers to simplify many logic structures

Transmission Gate

CS 150 Spring 2007 - Lec #26 Digital Design 13

Pass-Transistor Multiplexer

2-to-1 multiplexer:

c = sa + sb

Switches simplify the

implementation:

s

s

b

a

c

CS 150 Spring 2007 - Lec #26 Digital Design 14

4-to-1 Pass-transistor Mux

The series connection of

pass-transistors in each

branch effectively forms the

AND of s1 and s0 (or their

complement)

20 transistors

CS 150 Spring 2007 - Lec #26 Digital Design 15

Alternative 4-to-1 Multiplexer

This version has less

delay from in to out

Care must be taken to

avoid turning on multiple

paths simultaneously

(shorting together the

inputs)

36 Transistors

CS 150 Spring 2007 - Lec #26 Digital Design 16

Example: Tally Circuit

N inputs: How many of these are asserted?

Tally

In

I1

N

Two

One

Zero

E.g., 1 input, 2 outputs: One, Zero

E.g., 2 inputs, 3 outputs: Two, One, Zero

N inputs, N+1 outputs: N, , One, Zero

CS 150 Spring 2007 - Lec #26 Digital Design 17

Example: Tally Circuit

0 1

CS 150 Spring 2007 - Lec #26 Digital Design 18

Example: Tally Circuit

CS 150 Spring 2007 - Lec #26 Digital Design 19

Example: Tally Circuit

CS 150 Spring 2007 - Lec #26 Digital Design 20

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

I1

0

1

1

0

CS 150 Spring 2007 - Lec #26 Digital Design 21

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

I1

0

1

0

CS 150 Spring 2007 - Lec #26 Digital Design 22

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

CS 150 Spring 2007 - Lec #26 Digital Design 23

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

CS 150 Spring 2007 - Lec #26 Digital Design 24

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

CS 150 Spring 2007 - Lec #26 Digital Design 25

Example: Tally Circuit

2 inputs, 3 outputs:

Two, One, Zero

CS 150 Spring 2007 - Lec #26 Digital Design 26

Example: Crossbar Switch

N inputs, N outputs, N x N control signals

Cross

Bar

Bus

i

O

u

t

i

Note: circuit like this

used inside Xilinx

switching matrix

CS 150 Spring 2007 - Lec #26 Digital Design 27

Barrel Shifter

Barrel

Shifter

Bus

Out

Shift

Bus Shift

CS 150 Spring 2007 - Lec #26 Digital Design 28

Example: Barrel Shifter

N inputs, N outputs, N control signals

Shift 0

CS 150 Spring 2007 - Lec #26 Digital Design 29

Example: Barrel Shifter

N inputs, N outputs, N control signals

Shift 1

CS 150 Spring 2007 - Lec #26 Digital Design 30

Example: Barrel Shifter

N inputs, N outputs, N control signals

Rotating

Shift 1

CS 150 Spring 2007 - Lec #26 Digital Design 33

Tri-state Based Multiplexer

Multiplexer

If s=1 then c=a else c=b

Transistor Circuit for

inverting multiplexer:

CS 150 Spring 2007 - Lec #26 Digital Design 34

D-type Edge-triggered Flip-flop

The edge of the clock is used to

sample the "D" input & send it to

"Q (positive edge triggering)

At all other times the output Q is

independent of the input D (just

stores previously sampled value)

The input must be stable for a

short time before the clock edge.

CS 150 Spring 2007 - Lec #26 Digital Design 35

Transistor-level Logic Circuits

Positive Level-sensitive latch:

Latch Transistor Level:

clk

clk

clk

clk

Positive Edge-triggered flip-

flop built from two level-

sensitive latches:

CS 150 Spring 2007 - Lec #26 Digital Design 36

State Machines in CMOS

Two Phase Non-Overlapping Clocking

Combinational

Logic

R

E

G

R

E

G

In Out

State

P1

P2

CLK

P1

P2

1/2 Register

1/2 Register

CS 150 Spring 2007 - Lec #26 Digital Design 37

Digital Design and Implementation

Summary

CMOS preferred implementation technology

Much more than simple logic gates

Transmission gate as a building block

Used to construct steering logic

Very efficient compact implementations of interconnection

and shifting functions

Simple storage building blocks

D-type flip flop behavior with cross-coupled inverters and

two phase clocking

Heart of Xilinx implementation structures

You might also like

- Digital Design and System Implementation Overview of Physical ImplementationsDocument4 pagesDigital Design and System Implementation Overview of Physical ImplementationsGuganesan PerumalNo ratings yet

- 26 DigitalDesignx2Document10 pages26 DigitalDesignx2api-3742890No ratings yet

- Fundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document29 pagesFundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- VLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Document52 pagesVLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Mohammed ElNeanaeiNo ratings yet

- Prezentare Flux ProiectareDocument31 pagesPrezentare Flux ProiectareGeorge IoNo ratings yet

- Logic Gates: Power and Other Logic FamilyDocument36 pagesLogic Gates: Power and Other Logic FamilybhawnaNo ratings yet

- sc554 2014 Lecture09Document34 pagessc554 2014 Lecture09tharindu12No ratings yet

- ADC Pipeline LectureDocument29 pagesADC Pipeline LectureInJune YeoNo ratings yet

- Implementation Implementation Technology: (PART 2)Document45 pagesImplementation Implementation Technology: (PART 2)katral-jamerson-9379No ratings yet

- References: (Used For Creation of The Presentation Material)Document35 pagesReferences: (Used For Creation of The Presentation Material)Kumar BsnspNo ratings yet

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pages4 - Bit - Carry - Propagate - Adder PDFRennze Dominic DeveraNo ratings yet

- 5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoDocument15 pages5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoRaj AryanNo ratings yet

- V3 1Document16 pagesV3 1Ridwan WkNo ratings yet

- Logic Synthesis and Verification: Course InfoDocument7 pagesLogic Synthesis and Verification: Course InfoManisha JadavNo ratings yet

- Arithmetic Blocks Low-Power Design: 18-322 Lecture 18Document18 pagesArithmetic Blocks Low-Power Design: 18-322 Lecture 18shijint89No ratings yet

- Dl3 Digital CircuitsDocument14 pagesDl3 Digital Circuitsomgcharlie12No ratings yet

- VLSI: Design FlowDocument37 pagesVLSI: Design FlowCGNo ratings yet

- Chapter 17: Low-Power Design: Keshab K. Parhi and Viktor OwallDocument34 pagesChapter 17: Low-Power Design: Keshab K. Parhi and Viktor OwallGowtham Gntupallii GNo ratings yet

- Arhitectura CalculatoarelorDocument29 pagesArhitectura CalculatoarelormiryangelNo ratings yet

- Analog To DigitalDocument46 pagesAnalog To DigitalSaleem HaddadNo ratings yet

- Electronics Hardware Questions : Answers & Follow UpsDocument12 pagesElectronics Hardware Questions : Answers & Follow UpsJayachandra MakannavarNo ratings yet

- Introduction To VLSI Circuits: Naveen Bhat, Teaching Assistant Karnatak University, DharwadDocument100 pagesIntroduction To VLSI Circuits: Naveen Bhat, Teaching Assistant Karnatak University, DharwadunchalliNo ratings yet

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pages4 - Bit - Carry - Propagate - Adder PDFAhmed GadNo ratings yet

- VHDL - 00 - Basics of Digital DesignDocument29 pagesVHDL - 00 - Basics of Digital DesignKyle GilsdorfNo ratings yet

- L01 Introduction and ICs 21336Document41 pagesL01 Introduction and ICs 21336Mohamed ElzareiNo ratings yet

- P109 113 PDFDocument5 pagesP109 113 PDFSuraj Kumar PrustyNo ratings yet

- Vlsi TechnologyDocument60 pagesVlsi TechnologyPrasad NagavaraNo ratings yet

- PCB Design& Simulation LabDocument8 pagesPCB Design& Simulation LabVikram RaoNo ratings yet

- 8.RCX - View of CMOS Inverter and Nand GateDocument6 pages8.RCX - View of CMOS Inverter and Nand GatealokjadhavNo ratings yet

- Cmos BasicDocument21 pagesCmos BasicAnkesh JaiswalNo ratings yet

- ECN 252 Lab 6 - Design of D Flip-Flop and CountersDocument2 pagesECN 252 Lab 6 - Design of D Flip-Flop and CountersRUSHIL MOTWANINo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- Aplicacion Con CCS y PIC18F14K50Document45 pagesAplicacion Con CCS y PIC18F14K50Julián MinatelNo ratings yet

- AO Module Electronics: Mark HuntenDocument24 pagesAO Module Electronics: Mark Huntensecretxd26No ratings yet

- Chapter 3: Implementation Technology: 2009 Spring CS211 Digital Systems & LabDocument35 pagesChapter 3: Implementation Technology: 2009 Spring CS211 Digital Systems & LabChriztian CriolloNo ratings yet

- Design of A BPSK Modulator With VHDLDocument13 pagesDesign of A BPSK Modulator With VHDLNung NingNo ratings yet

- Viterbi Decoder: Presentation #2: Omar Ahmad Prateek Goenka Saim Qidwai Lingyan SunDocument13 pagesViterbi Decoder: Presentation #2: Omar Ahmad Prateek Goenka Saim Qidwai Lingyan SunSteven LeNo ratings yet

- S3esk Picoblaze Dac ControlDocument15 pagesS3esk Picoblaze Dac Controlkaruneee7003No ratings yet

- Cecc enDocument10 pagesCecc enpigulusNo ratings yet

- CMOS Design With Delay ConstraintsDocument22 pagesCMOS Design With Delay ConstraintsKumar Amit VermaNo ratings yet

- Post Layout Delay Calculation Using RCXDocument6 pagesPost Layout Delay Calculation Using RCXalokjadhavNo ratings yet

- Modeling and Simulation: Raul - Ionel@etc - UptDocument14 pagesModeling and Simulation: Raul - Ionel@etc - UpthassenbbNo ratings yet

- TMS320F2812-Analogue To Digital ConverterDocument26 pagesTMS320F2812-Analogue To Digital ConverterPantech ProLabs India Pvt LtdNo ratings yet

- CMOS Logic DesignDocument35 pagesCMOS Logic DesignsomosreeNo ratings yet

- EE 367 - Logic Design: AgendaDocument6 pagesEE 367 - Logic Design: Agendadivya1587No ratings yet

- Switching Circuits & Logic DesignDocument21 pagesSwitching Circuits & Logic Design555-193614No ratings yet

- Presentation: OF Base Station System (BSS)Document30 pagesPresentation: OF Base Station System (BSS)wakeonlanNo ratings yet

- Lec1 OverviewDocument36 pagesLec1 OverviewgariyakNo ratings yet

- ECE 331 - Digital System Design: Power Dissipation and Additional Design ConstraintsDocument31 pagesECE 331 - Digital System Design: Power Dissipation and Additional Design ConstraintsgpuonlineNo ratings yet

- TI Data Converter GuideDocument16 pagesTI Data Converter GuideDavid PostonNo ratings yet

- Low Power CMOS AD ConvertersDocument53 pagesLow Power CMOS AD ConvertersguitarfridoNo ratings yet

- Lacture 6Document44 pagesLacture 6Ali KhanNo ratings yet

- Atmel 11219 SmartEnergy ATSENSE-101-301-301H Datasheet4Document55 pagesAtmel 11219 SmartEnergy ATSENSE-101-301-301H Datasheet4Ivan BabicNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsFrom EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsRating: 4.5 out of 5 stars4.5/5 (2)

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Exercise Set 2.4: The Logic of Compound StatementsDocument2 pagesExercise Set 2.4: The Logic of Compound StatementsNatia ShpetishviliNo ratings yet

- Design and Implementation of Vedic Multiplier: Akshay Savji, Shruti OzaDocument4 pagesDesign and Implementation of Vedic Multiplier: Akshay Savji, Shruti OzaMahi BodanapuNo ratings yet

- Vlsi Design NotesDocument47 pagesVlsi Design Notesbooks babuNo ratings yet

- VLSI Module-1Document119 pagesVLSI Module-1Phanindra Reddy100% (2)

- Lab 1: To Generate Layout For CMOS Inverter Circuit and Simulate It For VerificationDocument51 pagesLab 1: To Generate Layout For CMOS Inverter Circuit and Simulate It For VerificationAbdullah Al Mamun MojumderNo ratings yet

- User's Manual of RDC6445GZ Control System V1.0 PDFDocument71 pagesUser's Manual of RDC6445GZ Control System V1.0 PDFСергейNo ratings yet

- Eeeg 202Document2 pagesEeeg 202Sailesh DahalNo ratings yet

- How To Use TeSys T Custom - Logic (2020 - 07 - 16 11 - 18 - 21 UTC)Document28 pagesHow To Use TeSys T Custom - Logic (2020 - 07 - 16 11 - 18 - 21 UTC)Welton SouzaNo ratings yet

- Combinational CircuitsDocument68 pagesCombinational Circuitsavita207No ratings yet

- Logic Gates - TheoryDocument43 pagesLogic Gates - TheorySaima Salman100% (1)

- 1 Combinational Logic CircuitsDocument6 pages1 Combinational Logic CircuitsRome Empe BalNo ratings yet

- St. Mary's University: Department of Computer ScienceDocument39 pagesSt. Mary's University: Department of Computer ScienceDofdofe KokoNo ratings yet

- ThesisDocument11 pagesThesistotktoNo ratings yet

- SyllabusDocument1 pageSyllabusRajalingam BossNo ratings yet

- DLD LAB Experiment 2 14Document7 pagesDLD LAB Experiment 2 14Dinh LâmNo ratings yet

- Lab 1: Full Adder: Tor) SoftwareDocument8 pagesLab 1: Full Adder: Tor) SoftwareAnonymous 6Xed5FfNo ratings yet

- GRP Scheme of Switchgear Generator, GT and UT 35620061800R00Document136 pagesGRP Scheme of Switchgear Generator, GT and UT 35620061800R00Rukma Goud Shakkari100% (1)

- Easergy P5 External Presentation - V14Document58 pagesEasergy P5 External Presentation - V14Jefri Yan SipahutarNo ratings yet

- Digital ElectronicsDocument6 pagesDigital Electronicspravallika vysyarajuNo ratings yet

- Altivar Machine ATV320 ATV320U15M3CDocument10 pagesAltivar Machine ATV320 ATV320U15M3CMarcos ZambranoNo ratings yet

- Basic Electronics: The AtomDocument65 pagesBasic Electronics: The AtomSantosh DevadeNo ratings yet

- Lecture12 Ee620 DividersDocument32 pagesLecture12 Ee620 DividersahmedNo ratings yet

- R15 Iii-IDocument9 pagesR15 Iii-IbmkondareddyNo ratings yet

- Combination Logic CircuitsDocument21 pagesCombination Logic Circuitsamitssaksena100% (1)

- Water Level Indicator Circuit DiagramDocument7 pagesWater Level Indicator Circuit DiagramEugen Cornea100% (1)

- Study of Logic Gates: AnswersDocument5 pagesStudy of Logic Gates: AnswersPinakiRanjanSarkarNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) Bhopalकिशोरी जूNo ratings yet

- DIgital Communication AssignmentDocument2 pagesDIgital Communication AssignmentRahul ChoudharyNo ratings yet

- Nand DigitalDocument3 pagesNand Digitalt19125 t19125No ratings yet

- Sop PosDocument31 pagesSop PosMrishoNo ratings yet