Professional Documents

Culture Documents

CS1104 Lecture on Counters and Registers

Uploaded by

Kelvin YipOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CS1104 Lecture on Counters and Registers

Uploaded by

Kelvin YipCopyright:

Available Formats

CS1104 Computer Organization

http://www.comp.nus.edu.sg/~cs1104

Aaron Tan Tuck Choy

School of Computing

National University of Singapore

CS1104-13

Lecture 13: Sequential Logic:

Counters and Registers

2

Lecture 13: Sequential Logic

Counters and Registers

Counters

Introduction: Counters

Asynchronous (Ripple) Counters

Asynchronous Counters with MOD number < 2

n

Asynchronous Down Counters

Cascading Asynchronous Counters

CS1104-13

Lecture 13: Sequential Logic:

Counters and Registers

3

Lecture 13: Sequential Logic

Counters and Registers

Synchronous (Parallel) Counters

Up/Down Synchronous Counters

Designing Synchronous Counters

Decoding A Counter

Counters with Parallel Load

CS1104-13

Lecture 13: Sequential Logic:

Counters and Registers

4

Lecture 13: Sequential Logic

Counters and Registers

Registers

Introduction: Registers

Simple Registers

Registers with Parallel Load

Using Registers to implement Sequential Circuits

Shift Registers

Serial In/Serial Out Shift Registers

Serial In/Parallel Out Shift Registers

Parallel In/Serial Out Shift Registers

Parallel In/Parallel Out Shift Registers

CS1104-13

Lecture 13: Sequential Logic:

Counters and Registers

5

Lecture 13: Sequential Logic

Counters and Registers

Bidirectional Shift Registers

An Application Serial Addition

Shift Register Counters

Ring Counters

Johnson Counters

Random-Access Memory (RAM)

CS1104-13

Introduction: Counters 6

Introduction: Counters

Counters are circuits that cycle through a specified

number of states.

Two types of counters:

synchronous (parallel) counters

asynchronous (ripple) counters

Ripple counters allow some flip-flop outputs to be

used as a source of clock for other flip-flops.

Synchronous counters apply the same clock to all

flip-flops.

CS1104-13

Asynchronous (Ripple) Counters 7

Asynchronous (Ripple) Counters

Asynchronous counters: the flip-flops do not change

states at exactly the same time as they do not have a

common clock pulse.

Also known as ripple counters, as the input clock

pulse ripples through the counter cumulative

delay is a drawback.

n flip-flops a MOD (modulus) 2

n

counter. (Note: A

MOD-x counter cycles through x states.)

Output of the last flip-flop (MSB) divides the input

clock frequency by the MOD number of the counter,

hence a counter is also a frequency divider.

CS1104-13

Asynchronous (Ripple) Counters 8

Asynchronous (Ripple) Counters

Example: 2-bit ripple binary counter.

Output of one flip-flop is connected to the clock input

of the next more-significant flip-flop.

K

J

K

J

HIGH

Q

0

Q

1

Q

0

FF1

FF0

CLK C C

Timing diagram

00 01 10 11 00 ...

4 3 2 1 CLK

Q

0

Q

0

Q

1

1 1

1 1

0

0 0

0 0

0

CS1104-13

Asynchronous (Ripple) Counters 9

Asynchronous (Ripple) Counters

Example: 3-bit ripple binary counter.

K

J

K

J

Q

0

Q

1

Q

0

FF1

FF0

C C

K

J

Q

1

C

FF2

Q

2

CLK

HIGH

4 3 2 1 CLK

Q

0

Q

1

1 1

1 1

0

0 0

0 0

0

8 7 6 5

1 1 0 0

1 1 0 0

Q

2

0 0 0 0 1 1 1 1 0

Recycles back to 0

CS1104-13

Asynchronous (Ripple) Counters 10

Asynchronous (Ripple) Counters

Propagation delays in an asynchronous (ripple-

clocked) binary counter.

If the accumulated delay is greater than the clock

pulse, some counter states may be misrepresented!

4 3 2 1 CLK

Q

0

Q

1

Q

2

t

PLH

(CLK to Q

0

)

t

PHL

(CLK to Q

0

)

t

PLH

(Q

0

to

Q

1

)

t

PHL

(CLK to Q

0

)

t

PHL

(Q

0

to

Q

1

)

t

PLH

(Q

1

to

Q

2

)

CS1104-13

Asynchronous (Ripple) Counters 11

Asynchronous (Ripple) Counters

Example: 4-bit ripple binary counter (negative-edge

triggered).

K

J

K

J

Q

1

Q

0

FF1 FF0

C C

K

J

C

FF2

Q

2

CLK

HIGH

K

J

C

FF3

Q

3

CLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Q

0

Q

1

Q

2

Q

3

CS1104-13

Asynchronous Counters with

MOD number < 2^n

12

Asyn. Counters with MOD no. < 2

n

States may be skipped resulting in a truncated

sequence.

Technique: force counter to recycle before going

through all of the states in the binary sequence.

Example: Given the following circuit, determine the

counting sequence (and hence the modulus no.)

K

J Q

Q

CLK

CLR

K

J Q

Q

CLK

CLR

K

J Q

Q

CLK

CLR

C B A

B

C

All J, K

inputs

are 1

(HIGH).

CS1104-13

Asynchronous Counters with

MOD number < 2^n

13

Asyn. Counters with MOD no. < 2

n

Example (contd):

K

J Q

Q

CLK

CLR

K

J Q

Q

CLK

CLR

K

J Q

Q

CLK

CLR

C B A

B

C

All J, K

inputs

are 1

(HIGH).

A

B

1 2

C

NAND

Output

1

0

3 4 5 6 7 8 9 10 11 12

Clock

MOD-6 counter

produced by

clearing (a MOD-8

binary counter)

when count of six

(110) occurs.

CS1104-13

Asynchronous Counters with

MOD number < 2^n

14

Asyn. Counters with MOD no. < 2

n

Example (contd): Counting sequence of circuit (in

CBA order).

A

B

C

NAND

Output

1

0

1 2 3 4 5 6 7 8 9 10 11 12

Clock

111

000

001

110

101

100

010

011

Temporary

state

Counter is a MOD-6

counter.

0

0

0

1

0

0

0

1

0

1

1

0

0

0

1

1

0

1

0

0

0

1

0

0

CS1104-13

Asynchronous Counters with

MOD number < 2^n

15

Asyn. Counters with MOD no. < 2

n

Exercise: How to construct an asynchronous MOD-5

counter? MOD-7 counter? MOD-12 counter?

Question: The following is a MOD-? counter?

K

J Q

Q

CLR

C B A

C

D

E

F

All J = K = 1.

K

J Q

Q

CLR

K

J Q

Q

CLR

K

J Q

Q

CLR

K

J Q

Q

CLR

K

J Q

Q

CLR

D E F

CS1104-13

Asynchronous Counters with

MOD number < 2^n

16

Asyn. Counters with MOD no. < 2

n

Decade counters (or BCD counters) are counters

with 10 states (modulus-10) in their sequence.

They are commonly used in daily life (e.g.: utility

meters, odometers, etc.).

Design an asynchronous decade counter.

D

CLK

HIGH

K

J

C

CLR

Q

K

J

C

CLR

Q

C

K

J

C

CLR

Q

B

K

J

C

CLR

Q

A

(A.C)'

CS1104-13

Asynchronous Counters with

MOD number < 2^n

17

Asyn. Counters with MOD no. < 2

n

Asynchronous decade/BCD counter (contd).

D

C

1 2

B

NAND

output

3 4 5 6 7 8 9 10

Clock

11

A

D

CLK

HIGH

K

J

C

CLR

Q

K

J

C

CLR

Q

C

K

J

C

CLR

Q

B

K

J

C

CLR

Q

A

(A.C)'

0

0

0

0

1

0

0

0

0

1

0

0

1

1

0

0

0

0

1

0

1

0

1

0

0

1

1

0

1

1

1

0

0

0

0

1

1

0

0

1

0

0

0

0

CS1104-13

Asynchronous Down Counters 18

Asynchronous Down Counters

So far we are dealing with up counters. Down

counters, on the other hand, count downward from

a maximum value to zero, and repeat.

Example: A 3-bit binary (MOD-2

3

) down counter.

K

J

K

J

Q

1

Q

0

C

C

K

J

C

Q

2

CLK

1

Q

Q'

Q

Q'

Q

Q'

Q

Q'

3-bit binary

up counter

3-bit binary

down counter

1

K

J

K

J

Q

1

Q

0

C

C

K

J

C

Q

2

CLK

Q

Q'

Q

Q'

Q

Q'

Q

Q'

CS1104-13

Asynchronous Down Counters 19

Asynchronous Down Counters

Example: A 3-bit binary (MOD-8) down counter.

4 3 2 1 CLK

Q

0

Q

1

1 1

1 0

0

0 1

0 0

0

8 7 6 5

1 1 0 0

1 0 1 0

Q

2

1 1 0 1 1 0 0 0 0

001

000

111

010

011

100

110

101

1

K

J

K

J

Q

1

Q

0

C

C

K

J

C

Q

2

CLK

Q

Q'

Q

Q'

Q

Q'

Q

Q'

CS1104-13

Cascading Asynchronous

Counters

20

Cascading Asynchronous Counters

Larger asynchronous (ripple) counter can be

constructed by cascading smaller ripple counters.

Connect last-stage output of one counter to the

clock input of next counter so as to achieve higher-

modulus operation.

Example: A modulus-32 ripple counter constructed

from a modulus-4 counter and a modulus-8 counter.

K

J

K

J

Q

1

Q

0

C

C CLK

Q

Q'

Q

Q'

Q

Q'

K

J

K

J

Q

3

Q

2

C

C

K

J

C

Q

4

Q

Q'

Q

Q'

Q

Q'

Q

Q'

Modulus-4 counter Modulus-8 counter

CS1104-13

Cascading Asynchronous

Counters

21

Cascading Asynchronous Counters

Example: A 6-bit binary counter (counts from 0 to

63) constructed from two 3-bit counters.

3-bit

binary counter

3-bit

binary counter

Count

pulse

A

0

A

1

A

2

A

3

A

4

A

5

A

5

A

4

A

3

A

2

A

1

A

0

0 0 0 0 0 0

0 0 0 0 0 1

0 0 0 : : :

0 0 0 1 1 1

0 0 1 0 0 0

0 0 1 0 0 1

: : : : : :

CS1104-13

Cascading Asynchronous

Counters

22

Cascading Asynchronous Counters

If counter is a not a binary counter, requires

additional output.

Example: A modulus-100 counter using two decade

counters.

CLK

Decade

counter

Q

3

Q

2

Q

1

Q

0

C

CTEN

TC

1

Decade

counter

Q

3

Q

2

Q

1

Q

0

C

CTEN

TC

freq

freq/10

freq/100

TC = 1 when counter recycles to 0000

CS1104-13

Synchronous (Parallel) Counters 23

Synchronous (Parallel) Counters

Synchronous (parallel) counters: the flip-flops are

clocked at the same time by a common clock pulse.

We can design these counters using the sequential

logic design process (covered in Lecture #12).

Example: 2-bit synchronous binary counter (using T

flip-flops, or JK flip-flops with identical J,K inputs).

Present Next Flip-flop

state state inputs

A

1

A

0

A

1

+

A

0

+

TA

1

TA

0

0 0 0 1 0 1

0 1 1 0 1 1

1 0 1 1 0 1

1 1 0 0 1 1

01 00

10 11

CS1104-13

Synchronous (Parallel) Counters 24

Synchronous (Parallel) Counters

Example: 2-bit synchronous binary counter (using T

flip-flops, or JK flip-flops with identical J,K inputs).

Present Next Flip-flop

state state inputs

A

1

A

0

A

1

+

A

0

+

TA

1

TA

0

0 0 0 1 0 1

0 1 1 0 1 1

1 0 1 1 0 1

1 1 0 0 1 1

TA

1

= A

0

TA

0

= 1

1

K

J

K

J

A

1

A

0

C

C

CLK

Q

Q'

Q

Q'

Q

Q'

CS1104-13

Synchronous (Parallel) Counters 25

Synchronous (Parallel) Counters

Example: 3-bit synchronous binary counter (using T

flip-flops, or JK flip-flops with identical J, K inputs).

Present Next Flip-flop

state state inputs

A

2

A

1

A

0

A

2

+

A

1

+

A

0

+

TA

2

TA

1

TA

0

0 0 0 0 0 1 0 0 1

0 0 1 0 1 0 0 1 1

0 1 0 0 1 1 0 0 1

0 1 1 1 0 0 1 1 1

1 0 0 1 0 1 0 0 1

1 0 1 1 1 0 0 1 1

1 1 0 1 1 1 0 0 1

1 1 1 0 0 0 1 1 1

TA

2

=A

1

.A

0

A

2

A

1

A

0

1

1

TA

1

=A

0

TA

0

=1

A

2

A

1

A

0

1

1 1

1

A

2

A

1

A

0

1 1 1

1 1 1 1

1

CS1104-13

Synchronous (Parallel) Counters 26

Synchronous (Parallel) Counters

Example: 3-bit synchronous binary counter (contd).

TA

2

= A

1

.A

0

TA

1

= A

0

TA

0

= 1

1

A

2

CP

A

1

A

0

K

Q

J K

Q

J K

Q

J

CS1104-13

Synchronous (Parallel) Counters 27

Synchronous (Parallel) Counters

Note that in a binary counter, the n

th

bit (shown

underlined) is always complemented whenever

01111 10000

or 11111 00000

Hence, X

n

is complemented whenever

X

n-1

X

n-2

... X

1

X

0

= 1111.

As a result, if T flip-flops are used, then

TX

n

= X

n-1

. X

n-2

. ... . X

1

.

X

0

CS1104-13

Synchronous (Parallel) Counters 28

Synchronous (Parallel) Counters

Example: 4-bit synchronous binary counter.

TA

3

= A

2

. A

1

. A

0

TA

2

= A

1

. A

0

TA

1

= A

0

TA

0

= 1

1

K

J

K

J

A

1

A

0

C

C

CLK

Q

Q'

Q

Q'

Q

Q'

K

J

A

2

C

Q

Q'

K

J

A

3

C

Q

Q'

A

1

.A

0

A

2

.A

1

.A

0

CS1104-13

Synchronous (Parallel) Counters 29

Synchronous (Parallel) Counters

Example: Synchronous decade/BCD counter.

Clock pulse Q

3

Q

2

Q

1

Q

0

Initially 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 (recycle) 0 0 0 0

T

0

= 1

T

1

= Q

3

'.Q

0

T

2

= Q

1

.Q

0

T

3

= Q

2

.Q

1

.Q

0

+ Q

3

.Q

0

CS1104-13

Synchronous (Parallel) Counters 30

Synchronous (Parallel) Counters

Example: Synchronous decade/BCD counter

(contd).

T

0

= 1

T

1

= Q

3

'.Q

0

T

2

= Q

1

.Q

0

T

3

= Q

2

.Q

1

.Q

0

+ Q

3

.Q

0

1

Q

1

Q

0

CLK

T

C

Q

Q'

Q

Q'

Q

2

Q

3

T

C

Q

Q'

Q

Q'

T

C

Q

Q'

Q

Q'

T

C

Q

Q'

Q

Q'

CS1104-13

Up/Down Synchronous Counters 31

Up/Down Synchronous Counters

Up/down synchronous counter: a bidirectional

counter that is capable of counting either up or

down.

An input (control) line Up/Down (or simply Up)

specifies the direction of counting.

Up/Down = 1 Count upward

Up/Down = 0 Count downward

CS1104-13

Up/Down Synchronous Counters 32

Up/Down Synchronous Counters

Example: A 3-bit up/down synchronous binary

counter.

Clock pulse Up Q

2

Q

1

Q

0

Down

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

TQ

0

= 1

TQ

1

= (Q

0

.Up) + (Q

0

'.Up' )

TQ

2

= ( Q

0

.Q

1

.Up ) + (Q

0

'. Q

1

'. Up' )

Up counter

TQ

0

= 1

TQ

1

= Q

0

TQ

2

= Q

0

.Q

1

Down counter

TQ

0

= 1

TQ

1

= Q

0

TQ

2

= Q

0

.Q

1

CS1104-13

Up/Down Synchronous Counters 33

Up/Down Synchronous Counters

Example: A 3-bit up/down synchronous binary

counter (contd).

TQ

0

= 1

TQ

1

= (Q

0

.Up) + (Q

0

'.Up' )

TQ

2

= ( Q

0

.Q

1

.Up ) + (Q

0

'. Q

1

'. Up' )

1

Q

1

Q

0

CLK

T

C

Q

Q'

Q

Q'

T

C

Q

Q'

Q

Q'

T

C

Q

Q'

Q

Q'

Up

Q

2

CS1104-13

Designing Synchronous Counters 34

Designing Synchronous Counters

Covered in Lecture #12.

Example: A 3-bit Gray code

counter (using JK flip-flops).

100

000

001

101

111

110

011

010

Present Next Flip-flop

state state inputs

Q

2

Q

1

Q

0

Q

2

+

Q

1

+

Q

0

+

J Q

2

KQ

2

J Q

1

KQ

1

J Q

0

KQ

0

0 0 0 0 0 1 0 X 0 X 1 X

0 0 1 0 1 1 0 X 1 X X 0

0 1 0 1 1 0 1 X X 0 0 X

0 1 1 0 1 0 0 X X 0 X 1

1 0 0 0 0 0 X 1 0 X 0 X

1 0 1 1 0 0 X 0 0 X X 1

1 1 0 1 1 1 X 0 X 0 1 X

1 1 1 1 0 1 X 0 X 1 X 0

CS1104-13

Designing Synchronous Counters 35

Designing Synchronous Counters

3-bit Gray code counter: flip-flop inputs.

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X X X

1

J Q

2

=Q

1

.Q

0

'

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X X X

1

KQ

2

=Q

1

'.Q

0

'

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X

X X 1

J Q

1

=Q

2

'.Q

0

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X

X X

1

KQ

1

=Q

2

.Q

0

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X

X X 1

J Q

0

=Q

2

.Q

1

+ Q

2

'.Q

1

'

= (Q

2

Q

1

)'

1

0

1

00 01 11 10

Q

2

Q

1

Q

0

X X

X X 1

1

KQ

0

=Q

2

.Q

1

' + Q

2

'.Q

1

=Q

2

Q

1

CS1104-13

Designing Synchronous Counters 36

Designing Synchronous Counters

3-bit Gray code counter: logic diagram.

JQ

2

= Q

1

.Q

0

' JQ

1

= Q

2

'.Q

0

JQ

0

= (Q

2

Q

1

)'

KQ

2

= Q

1

'.Q

0

' KQ

1

= Q

2

.Q

0

KQ

0

= Q

2

Q

1

Q

1

Q

0

CLK

Q

2

J

C

Q

Q' K

J

C

Q

Q' K

J

C

Q

Q' K

Q

2

'

Q

0

'

Q

1

'

CS1104-13

Decoding A Counter 37

Decoding A Counter

Decoding a counter involves determining which state

in the sequence the counter is in.

Differentiate between active-HIGH and active-LOW

decoding.

Active-HIGH decoding: output HIGH if the counter is

in the state concerned.

Active-LOW decoding: output LOW if the counter is

in the state concerned.

CS1104-13

Decoding A Counter 38

Decoding A Counter

Example: MOD-8 ripple counter (active-HIGH

decoding).

A'

B'

C'

1 2 3 4 5 6 7 8 9

Clock

HIGH only on

count of ABC = 000

A'

B'

C

HIGH only on

count of ABC = 001

A'

B

C'

HIGH only on

count of ABC = 010

10 0

A

B

C

HIGH only on

count of ABC = 111

.

.

.

CS1104-13

Decoding A Counter 39

Decoding A Counter

Example: To detect that a MOD-8 counter is in state

0 (000) or state 1 (001).

A'

B'

1 2 3 4 5 6 7 8 9

Clock

HIGH only on

count of ABC = 000

or ABC = 001

10 0

Example: To detect that a MOD-8 counter is in the

odd states (states 1, 3, 5 or 7), simply use C.

C

1 2 3 4 5 6 7 8 9

Clock

HIGH only on count

of odd states

10 0

A'

B'

C'

A'

B'

C

CS1104-13

Counters with Parallel Load 40

Counters with Parallel Load

Counters could be augmented with parallel load

capability for the following purposes:

To start at a different state

To count a different sequence

As more sophisticated register with increment/decrement

functionality.

CS1104-13

Counters with Parallel Load 41

Counters with Parallel Load

Different ways of getting a MOD-6 counter:

Count = 1

Load = 0

CP I

4

I

3

I

2

I

1

Count = 1

Clear = 1

CP

A

4

A

3

A

2

A

1

Inputs = 0

Load

(a) Binary states 0,1,2,3,4,5.

I

4

I

3

I

2

I

1

A

4

A

3

A

2

A

1

Inputs have no effect

Clear

(b) Binary states 0,1,2,3,4,5.

I

4

I

3

I

2

I

1

Count = 1

Clear = 1

CP

A

4

A

3

A

2

A

1

0 0 1 1

Load

(d) Binary states 3,4,5,6,7,8.

I

4

I

3

I

2

I

1

Count = 1

Clear = 1

CP

A

4

A

3

A

2

A

1

1 0 1 0

Load

Carry-out

(c) Binary states 10,11,12,13,14,15.

CS1104-13

Counters with Parallel Load 42

Counters with Parallel Load

4-bit counter with

parallel load.

Clear CP Load Count Function

0 X X X Clear to 0

1 X 0 0 No change

1 1 X Load inputs

1 0 1 Next state

CS1104-13

Introduction: Registers 43

Introduction: Registers

An n-bit register has a group of n flip-flops and some

logic gates and is capable of storing n bits of

information.

The flip-flops store the information while the gates

control when and how new information is transferred

into the register.

Some functions of register:

retrieve data from register

store/load new data into register (serial or parallel)

shift the data within register (left or right)

CS1104-13

Simple Registers 44

Simple Registers

No external gates.

Example: A 4-bit register. A new 4-bit data is loaded

every clock cycle.

A

3

CP

A

1

A

0

D

Q

D

Q Q

D

A

2

D

Q

I

3

I

1

I

0

I

2

CS1104-13

Registers With Parallel Load 45

Registers With Parallel Load

Instead of loading the register at every clock pulse,

we may want to control when to load.

Loading a register: transfer new information into the

register. Requires a load control input.

Parallel loading: all bits are loaded simultaneously.

CS1104-13

Registers With Parallel Load 46

Registers With Parallel Load

A

0

CLK

D Q

Load

I

0

A

1

D Q

A

2

D Q

A

3

D Q

CLEAR

I

1

I

2

I

3

Load'.A

0

+ Load. I

0

CS1104-13

Using Registers to implement

Sequential Circuits

47

Using Registers to implement

Sequential Circuits

A sequential circuit may consist of a register

(memory) and a combinational circuit.

Register Combin-

ational

circuit

Clock

Inputs Outputs

Next-state value

The external inputs and present states of the register

determine the next states of the register and the

external outputs, through the combinational circuit.

The combinational circuit may be implemented by

any of the methods covered in MSI components and

Programmable Logic Devices.

CS1104-13

Using Registers to implement

Sequential Circuits

48

Using Registers to implement

Sequential Circuits

Example 1:

A

1

+

= S m(4,6) = A

1

.x'

A

2

+

= S m(1,2,5,6) = A

2

.x' + A

2

'.x = A

2

x

y = S m(3,7) = A

2

.x

Present Next

state Input State Output

A

1

A

2

x A

1

+

A

2

+

y

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 0 1 0

0 1 1 0 0 1

1 0 0 1 0 0

1 0 1 0 1 0

1 1 0 1 1 0

1 1 1 0 0 1

A

1

A

2

x

y

A

1

.x'

A

2

x

CS1104-13

Using Registers to implement

Sequential Circuits

49

Using Registers to implement

Sequential Circuits

Example 2: Repeat example 1, but use a ROM.

Address Outputs

1 2 3 1 2 3

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 0 1 0

0 1 1 0 0 1

1 0 0 1 0 0

1 0 1 0 1 0

1 1 0 1 1 0

1 1 1 0 0 1

ROM truth table

A

1

A

2

x y

8 x 3

ROM

CS1104-13

Shift Registers 50

Shift Registers

Another function of a register, besides storage, is to

provide for data movements.

Each stage (flip-flop) in a shift register represents

one bit of storage, and the shifting capability of a

register permits the movement of data from stage to

stage within the register, or into or out of the register

upon application of clock pulses.

CS1104-13

Shift Registers 51

Shift Registers

Basic data movement in shift registers (four bits are

used for illustration).

Data in Data out

(a) Serial in/shift right/serial out

Data in Data out

(b) Serial in/shift left/serial out

Data in

Data out

(c) Parallel in/serial out

Data out

Data in

(d) Serial in/parallel out

Data out

Data in

(e) Parallel in /

parallel out

(f) Rotate right (g) Rotate left

CS1104-13

Serial In/Serial Out Shift Registers 52

Serial In/Serial Out Shift Registers

Accepts data serially one bit at a time and also

produces output serially.

Q

0

CLK

D

C

Q

Q

1

Q

2

Q

3

Serial data

input

Serial data

output

D

C

Q D

C

Q D

C

Q

CS1104-13

Serial In/Serial Out Shift Registers 53

Serial In/Serial Out Shift Registers

Application: Serial transfer of data from one register

to another.

Shift register A Shift register B

SI SI SO SO

Clock

Shift control

CP

Wordtime

T

1

T

2

T

3

T

4

CP

Clock

Shift

control

CS1104-13

Serial In/Serial Out Shift Registers 54

Serial In/Serial Out Shift Registers

Serial-transfer example.

Timing Pulse Shift register A Shift register B Serial output of B

Initial value 1 0 1 1 0 0 1 0 0

After T

1

1 1 0 1 1 0 0 1 1

After T

2

1 1 1 0 1 1 0 0 0

After T

3

0 1 1 1 0 1 1 0 0

After T

4

1 0 1 1 1 0 1 1 1

CS1104-13

Serial In/Parallel Out Shift

Registers

55

Serial In/Parallel Out Shift Registers

Accepts data serially.

Outputs of all stages are available simultaneously.

Q

0

CLK

D

C

Q

Q

1

D

C

Q

Q

2

D

C

Q

Q

3

D

C

Q

Data input

D

C CLK

Data input

Q

0

Q

1

Q

2

Q

3

SRG 4

Logic symbol

CS1104-13

Parallel In/Serial Out Shift

Registers

56

Parallel In/Serial Out Shift Registers

Bits are entered simultaneously, but output is serial.

D

0

CLK

D

C

Q

D

1

D

C

Q

D

2

D

C

Q

D

3

D

C

Q

Data input

Q

0

Q

1

Q

2

Q

3

Serial

data

out

SHIFT/LOAD

SHIFT.Q

0

+ SHIFT'.D

1

CS1104-13

Parallel In/Serial Out Shift

Registers

57

Parallel In/Serial Out Shift Registers

Bits are entered simultaneously, but output is serial.

Logic symbol

C CLK

SHIFT/LOAD

D

0

D

1

D

2

D

3

SRG 4

Serial data out

Data in

CS1104-13

Parallel In/Parallel Out Shift

Registers

58

Parallel In/Parallel Out Shift Registers

Simultaneous input and output of all data bits.

Q

0

CLK

D

C

Q

Q

1

D

C

Q

Q

2

D

C

Q

Q

3

D

C

Q

Parallel data inputs

D

0

D

1

D

2

D

3

Parallel data outputs

CS1104-13

Bidirectional Shift Registers 59

Bidirectional Shift Registers

Data can be shifted either left or right, using a control

line RIGHT/LEFT (or simply RIGHT) to indicate the

direction.

CLK

D

C

Q D

C

Q D

C

Q D

C

Q

Q

0

Q

1

Q

2

Q

3

RIGHT/LEFT

Serial

data in

RIGHT.Q

0

+

RIGHT'.Q

2

CS1104-13

Bidirectional Shift Registers 60

Bidirectional Shift Registers

4-bit bidirectional shift register with parallel load.

CLK

I

4

I

3

I

2

I

1

Serial

input for

shift-right

D

Q

D

Q

D

Q

D

Q

Clear

4x1

MUX

s

1

s

0

3 2 1 0

4x1

MUX

3 2 1 0

4x1

MUX

3 2 1 0

4x1

MUX

3 2 1 0

A

4

A

3

A

2

A

1

Serial

input for

shift-left

Parallel inputs

Parallel outputs

CS1104-13

Bidirectional Shift Registers 61

Bidirectional Shift Registers

4-bit bidirectional shift register with parallel load.

Mode Control

s

1

s

0

Register Operation

0 0 No change

0 1 Shift right

1 0 Shift left

1 1 Parallel load

CS1104-13

An Application Serial Addition 62

An Application Serial Addition

Most operations in digital computers are done in

parallel. Serial operations are slower but require less

equipment.

A serial adder is shown below. A A + B.

FA

x

y

z

S

C

Shift-register A

Shift-right

CP

SI

Shift-register B

SI

External input

SO

SO

Q D

Clear

CS1104-13

An Application Serial Addition 63

An Application Serial Addition

A = 0100; B = 0111. A + B = 1011 is stored in A

after 4 clock pulses.

Initial:

A: 0 1 0 0

B: 0 1 1 1

Q: 0

Step 1: 0 + 1 + 0

S = 1, C = 0

A: 1 0 1 0

B: x 0 1 1

Q: 0

Step 2: 0 + 1 + 0

S = 1, C = 0

A: 1 1 0 1

B: x x 0 1

Q: 0

Step 3: 1 + 1 + 0

S = 0, C = 1

A: 0 1 1 0

B: x x x 0

Q: 1

Step 4: 0 + 0 + 1

S = 1, C = 0

A: 1 0 1 1

B: x x x x

Q: 0

CS1104-13

Shift Register Counters 64

Shift Register Counters

Shift register counter: a shift register with the serial

output connected back to the serial input.

They are classified as counters because they give a

specified sequence of states.

Two common types: the Johnson counter and the

Ring counter.

CS1104-13

Ring Counters 65

Ring Counters

One flip-flop (stage) for each state in the sequence.

The output of the last stage is connected to the D

input of the first stage.

An n-bit ring counter cycles through n states.

No decoding gates are required, as there is an output

that corresponds to every state the counter is in.

CS1104-13

Ring Counters 66

Ring Counters

Example: A 6-bit (MOD-6) ring counter.

CLK

Q

0

D Q D Q D Q D Q D Q D Q

Q

1

Q

2

Q

3

Q

4

Q

5

CLR

PRE

Clock Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

0 1 0 0 0 0 0

1 0 1 0 0 0 0

2 0 0 1 0 0 0

3 0 0 0 1 0 0

4 0 0 0 0 1 0

5 0 0 0 0 0 1

100000

010000

001000

000100

000010

000001

CS1104-13

Johnson Counters 67

Johnson Counters

The complement of the output of the last stage is

connected back to the D input of the first stage.

Also called the twisted-ring counter.

Require fewer flip-flops than ring counters but more

flip-flops than binary counters.

An n-bit Johnson counter cycles through 2n states.

Require more decoding circuitry than ring counter

but less than binary counters.

CS1104-13

Johnson Counters 68

Johnson Counters

Example: A 4-bit (MOD-8) Johnson counter.

Clock Q

0

Q

1

Q

2

Q

3

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 1 0

4 1 1 1 1

5 0 1 1 1

6 0 0 1 1

7 0 0 0 1

CLK

Q

0

D Q D Q D Q D Q

Q

1

Q

2

Q

3

'

CLR

Q'

0000

0001

0011

0111

1111

1110

1100

1000

CS1104-13

Johnson Counters 69

Johnson Counters

Decoding logic for a 4-bit Johnson counter.

Clock A B C D

Decoding

0 0 0 0 0 A'.D'

1 1 0 0 0 A.B'

2 1 1 0 0 B.C'

3 1 1 1 0 C.D'

4 1 1 1 1 A.D

5 0 1 1 1 A'.B

6 0 0 1 1 B'.C

7 0 0 0 1 C'.D

A'

D'

State 0

A

D

State 4

B

C'

State 2

C

D'

State 3

A

B'

State 1

A'

B

State 5

B'

C

State 6

C'

D

State 7

CS1104-13

Random Access Memory (RAM) 70

Random Access Memory (RAM)

A memory unit stores binary information in groups of

bits called words.

The data consists of n lines (for n-bit words). Data

input lines provide the information to be stored

(written) into the memory, while data output lines

carry the information out (read) from the memory.

The address consists of k lines which specify which

word (among the 2

k

words available) to be selected

for reading or writing.

The control lines Read and Write (usually combined

into a single control line Read/Write) specifies the

direction of transfer of the data.

CS1104-13

Random Access Memory (RAM) 71

Random Access Memory (RAM)

Block diagram of a memory unit:

Memory unit

2

k

words

n bits per word

k address lines

k

Read/Write

n

n

n data

input lines

n data

output lines

CS1104-13

Random Access Memory (RAM) 72

Random Access Memory (RAM)

Content of a 1024 x 16-bit memory:

1011010111011101

1010000110000110

0010011101110001

:

:

1110010101010010

0011111010101110

1011000110010101

Memory content

decimal

0

1

2

:

:

1021

1022

1023

0000000000

0000000001

0000000010

:

:

1111111101

1111111110

1111111111

binary

Memory address

CS1104-13

Random Access Memory (RAM) 73

Random Access Memory (RAM)

The Write operation:

Transfers the address of the desired word to the address

lines

Transfers the data bits (the word) to be stored in memory to

the data input lines

Activates the Write control line (set Read/Write to 0)

The Read operation:

Transfers the address of the desired word to the address

lines

Activates the Read control line (set Read/Write to 1)

CS1104-13

Random Access Memory (RAM) 74

Random Access Memory (RAM)

The Read/Write operation:

Memory Enable Read/Write Memory Operation

0 X None

1 0 Write to selected word

1 1 Read from selected word

Two types of RAM: Static and dynamic.

Static RAMs use flip-flops as the memory cells.

Dynamic RAMs use capacitor charges to represent data.

Though simpler in circuitry, they have to be constantly

refreshed.

CS1104-13

Random Access Memory (RAM) 75

Random Access Memory (RAM)

A single memory cell of the static RAM has the

following logic and block diagrams.

R

S

Q

Input

Select

Output

Read/Write

BC Output Input

Select

Read/Write

Logic diagram Block diagram

CS1104-13

Random Access Memory (RAM) 76

Random Access Memory (RAM)

Logic construction of a 4 x 3 RAM (with decoder and

OR gates):

CS1104-13

Random Access Memory (RAM) 77

Random Access Memory (RAM)

An array of RAM chips: memory chips are combined

to form larger memory.

A 1K x 8-bit RAM chip:

Block diagram of a 1K x 8 RAM chip

RAM 1K x 8

DATA (8)

ADRS (10)

CS

RW

Input data

Address

Chip select

Read/write

(8) Output data

8 8

10

CS1104-13

Random Access Memory (RAM) 78

Random Access Memory (RAM)

4K x 8 RAM.

1K x 8

DATA (8)

ADRS (10)

CS

RW

Read/write

(8)

Output

data

1K x 8

DATA (8)

ADRS (10)

CS

RW

(8)

1K x 8

DATA (8)

ADRS (10)

CS

RW

(8)

1K x 8

DATA (8)

ADRS (10)

CS

RW

(8)

01023

1024 2047

2048 3071

3072 4095

Input data

8 lines

0

1

2

3

2x4

decoder

Lines Lines

0 9 11 10

S

0

S

1

Address

End of segment

You might also like

- Step by Step Mixing 2nd Edition Table of ContentsDocument4 pagesStep by Step Mixing 2nd Edition Table of ContentsDevendra YadavNo ratings yet

- EE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Document19 pagesEE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanNo ratings yet

- Counters and Finite State MachinesDocument55 pagesCounters and Finite State MachinesFahim MahmudNo ratings yet

- Riello Multiplus Ups Series 100 120 ManualDocument45 pagesRiello Multiplus Ups Series 100 120 ManualJorgeErnestoCartagenaNo ratings yet

- Harmonic Filter Design PDFDocument14 pagesHarmonic Filter Design PDFserban_elNo ratings yet

- Digital Logic Design Lab ReportDocument16 pagesDigital Logic Design Lab ReportTrương Quang Tường100% (1)

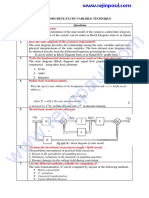

- Unit I - Discrete State-Variable Technique Q.No Questions: Scalar Adder IntegratorDocument184 pagesUnit I - Discrete State-Variable Technique Q.No Questions: Scalar Adder IntegratorAgatha ChristieNo ratings yet

- Timers, Serial, InterDocument107 pagesTimers, Serial, Inters sreehari,No ratings yet

- Counters and Registers 5Document79 pagesCounters and Registers 5Munish GargNo ratings yet

- Lesson 8 2 Asynchronous Counters11Document30 pagesLesson 8 2 Asynchronous Counters11Chris TineNo ratings yet

- Stepper MotorDocument6 pagesStepper MotorSiddharth MishraNo ratings yet

- AN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportDocument6 pagesAN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportYasin ArslanNo ratings yet

- Dac 0800 & Dac 0802 (An 1525)Document4 pagesDac 0800 & Dac 0802 (An 1525)HARICH90No ratings yet

- Put Coin and Draw PowerDocument74 pagesPut Coin and Draw PowerAjaysinh ParmarNo ratings yet

- Password Based Door LockingDocument4 pagesPassword Based Door LockingAswathi SruthiNo ratings yet

- Introduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadDocument117 pagesIntroduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadEnGr Asad Hayat BanGashNo ratings yet

- CC442 Chapter 8 Asynchronous CounterDocument19 pagesCC442 Chapter 8 Asynchronous CounterMuhamdA.BadawyNo ratings yet

- New Generation Polling Method Using RFDocument10 pagesNew Generation Polling Method Using RFEnoch IsraelNo ratings yet

- ECE 304 Microcontroller Course OverviewDocument1 pageECE 304 Microcontroller Course OverviewNishant GhoshNo ratings yet

- AT89C51Document15 pagesAT89C51vaalginNo ratings yet

- Thevenins and NortonsDocument26 pagesThevenins and NortonsKishan SinghNo ratings yet

- Chapter IIDocument37 pagesChapter IIJohn Pol Igagamao100% (1)

- IE LAB 8 HamzaDocument7 pagesIE LAB 8 HamzaHamza BilgramiNo ratings yet

- Fuzzy Logic History and ApplicationsDocument5 pagesFuzzy Logic History and ApplicationsYossry AwadNo ratings yet

- Syllabus For Fundamentals of The Embedded Systems: Programming ExamplesDocument3 pagesSyllabus For Fundamentals of The Embedded Systems: Programming ExamplesvarshaNo ratings yet

- 6.voice Integrated Speed and Direction Control For DC MotorDocument4 pages6.voice Integrated Speed and Direction Control For DC MotorRamsathayaNo ratings yet

- IoT traffic controlDocument9 pagesIoT traffic controlDesta Yakob Doda 18BML0121No ratings yet

- PL7-1 Language: Structure and functionsDocument27 pagesPL7-1 Language: Structure and functionsTalyson AlexandreNo ratings yet

- Project Report Digital Clock: Abu Dhabi UniversityDocument11 pagesProject Report Digital Clock: Abu Dhabi UniversityAbbas RajpootNo ratings yet

- Logo Applications enDocument36 pagesLogo Applications enosama mahyoubNo ratings yet

- The Silicon Laboratories C8051F020Document89 pagesThe Silicon Laboratories C8051F020hani1986yeNo ratings yet

- MNA StampDocument58 pagesMNA Stampellig1871638No ratings yet

- 8051 Vs Motorola 68HC11Document19 pages8051 Vs Motorola 68HC11zuanne83No ratings yet

- EC2252 U1 Notes PDFDocument44 pagesEC2252 U1 Notes PDFPaul ThiraviumNo ratings yet

- 8086 Microprocessor Lab 1Document7 pages8086 Microprocessor Lab 1Tyler BarneyNo ratings yet

- EC2303 2 Marks With AnswersDocument19 pagesEC2303 2 Marks With AnswersVijay Arunagiri ANo ratings yet

- PLC, SCADA & DCS Automation SystemsDocument2 pagesPLC, SCADA & DCS Automation Systemsmoney_kandan2004No ratings yet

- Ec805 Wireless Sensor NetworksDocument1 pageEc805 Wireless Sensor NetworkscalvinosimonNo ratings yet

- EC2302 DIGITAL SIGNAL PROCESSING Two Marks With Answers Vidyarthiplus (V+) Blog - A Blog For StudentsDocument41 pagesEC2302 DIGITAL SIGNAL PROCESSING Two Marks With Answers Vidyarthiplus (V+) Blog - A Blog For StudentsSiva Prasad Nandyala100% (2)

- MSDFFDocument20 pagesMSDFFShweta KumariNo ratings yet

- Digital System Design VHDL StopwatchDocument25 pagesDigital System Design VHDL StopwatchSrinivas CherukuNo ratings yet

- Put Coin and Draw PowerDocument22 pagesPut Coin and Draw PowerJINCYMOHANAN100% (1)

- DC Motor Control with PIC MCU Using L293 Driver ICDocument4 pagesDC Motor Control with PIC MCU Using L293 Driver ICifyNo ratings yet

- The Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItDocument11 pagesThe Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItsaadawarNo ratings yet

- EE-312 Signals & Systems Course OverviewDocument3 pagesEE-312 Signals & Systems Course OverviewHamza AyazNo ratings yet

- E Book On ADC ProductsDocument29 pagesE Book On ADC ProductsSudharani YellapragadaNo ratings yet

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocument43 pagesECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaNo ratings yet

- Fuzzy Gain Scheduling of PID Controllers PDFDocument7 pagesFuzzy Gain Scheduling of PID Controllers PDFMiguel ZeaNo ratings yet

- CS 8491 Computer ArchitectureDocument103 pagesCS 8491 Computer ArchitectureMUKESH KUMAR P 2019-2023 CSENo ratings yet

- Ring Counter PDFDocument6 pagesRing Counter PDFحسنين غانم خضيرNo ratings yet

- Experiment Procedure and Components ManualDocument14 pagesExperiment Procedure and Components ManualMuhammad Ali Khan AwanNo ratings yet

- Experiment No. 01 Experiment Name-ASK ModulationDocument47 pagesExperiment No. 01 Experiment Name-ASK ModulationmuskanNo ratings yet

- Hazards in Digital Logic and SwitchingDocument18 pagesHazards in Digital Logic and SwitchingAyush MukherjeeNo ratings yet

- Atmel-Code Lock With 4x4 Keypad and I2C™ LCDDocument9 pagesAtmel-Code Lock With 4x4 Keypad and I2C™ LCDkaran_vistaNo ratings yet

- Missile Detection and DestroyerDocument6 pagesMissile Detection and DestroyeranushreeNo ratings yet

- Least Mean Square Adaptive FiltersDocument502 pagesLeast Mean Square Adaptive FiltersEko WahyudeNo ratings yet

- ProjectDocument22 pagesProjectSandeep SharmaNo ratings yet

- Counters and Shift RgistersDocument59 pagesCounters and Shift RgistersrobinptNo ratings yet

- CountersDocument44 pagesCountersNaveen Kishore GattimNo ratings yet

- Consequence LogicDocument83 pagesConsequence LogicLai Yon PengNo ratings yet

- 9 Counter CircuitsDocument9 pages9 Counter CircuitsWaseem AhmadNo ratings yet

- Registers and Counters Lecture SummaryDocument24 pagesRegisters and Counters Lecture SummaryPiyooshTripathiNo ratings yet

- (Counter) Paper - 1 - 7967 - 163 PDFDocument57 pages(Counter) Paper - 1 - 7967 - 163 PDFmaprofNo ratings yet

- Universiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementDocument63 pagesUniversiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementKelvin YipNo ratings yet

- Archimedes' Approximation of Pi 1997Document4 pagesArchimedes' Approximation of Pi 1997Kelvin YipNo ratings yet

- Request of Course Offering Letter (UBML1053 Business LawDocument2 pagesRequest of Course Offering Letter (UBML1053 Business LawKelvin YipNo ratings yet

- Universiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementDocument63 pagesUniversiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementKelvin YipNo ratings yet

- List of TableDocument1 pageList of TableKelvin YipNo ratings yet

- 16413Document4 pages16413Kelvin YipNo ratings yet

- Questionnaire TemplateDocument2 pagesQuestionnaire TemplateKelvin YipNo ratings yet

- Universiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementDocument63 pagesUniversiti Tunku Abdul Rahman: Undergraduate Research Project Page 1 of 63 Faculty of Accountancy and ManagementKelvin YipNo ratings yet

- DHR FM DHR RC 003 - 20161020Document5 pagesDHR FM DHR RC 003 - 20161020Kelvin YipNo ratings yet

- Current and Kva CalculationsDocument18 pagesCurrent and Kva CalculationsKelvin YipNo ratings yet

- Online PTPTN Loan Repayment ReceiptDocument1 pageOnline PTPTN Loan Repayment ReceiptKelvin YipNo ratings yet

- AbstractDocument1 pageAbstractKelvin YipNo ratings yet

- 15 Toughest Interview Questions and Answers!: 1. Why Do You Want To Work in This Industry?Document8 pages15 Toughest Interview Questions and Answers!: 1. Why Do You Want To Work in This Industry?johnlemNo ratings yet

- TitleDocument3 pagesTitleKelvin YipNo ratings yet

- Special RelationshipsDocument5 pagesSpecial RelationshipsKelvin YipNo ratings yet

- Combined 123456Document63 pagesCombined 123456Kelvin YipNo ratings yet

- Chapter 5 Acceptance SamplingDocument45 pagesChapter 5 Acceptance SamplingKelvin YipNo ratings yet

- Chapter 1Document16 pagesChapter 1Kelvin YipNo ratings yet

- Chapter1 StatisticDocument33 pagesChapter1 StatisticKelvin YipNo ratings yet

- Chapter 5 Acceptance SamplingDocument45 pagesChapter 5 Acceptance SamplingKelvin YipNo ratings yet

- Title:To Practically Configuration and Characteristic ofDocument14 pagesTitle:To Practically Configuration and Characteristic ofKelvin YipNo ratings yet

- ConceptDocument3 pagesConceptKelvin YipNo ratings yet

- Chapter 2 Basic Quality ConceptDocument31 pagesChapter 2 Basic Quality ConceptKelvin YipNo ratings yet

- Chapter 6 To 8 Quality Compatibility ModeDocument29 pagesChapter 6 To 8 Quality Compatibility ModeKelvin YipNo ratings yet

- Chapter 5 Acceptance SamplingDocument45 pagesChapter 5 Acceptance SamplingKelvin YipNo ratings yet

- ESSAY (100 Marks) : Pages 2 of 8Document7 pagesESSAY (100 Marks) : Pages 2 of 8Iskandar IbrahimNo ratings yet

- Chapter 6 To 8 Quality Compatibility ModeDocument29 pagesChapter 6 To 8 Quality Compatibility ModeKelvin YipNo ratings yet

- Power ScrewsDocument13 pagesPower ScrewsKelvin YipNo ratings yet

- End of Cahpter 1Document2 pagesEnd of Cahpter 1Kelvin YipNo ratings yet

- GLST Project Titles BookDocument35 pagesGLST Project Titles BookKelvin YipNo ratings yet

- The History of MMDSDocument4 pagesThe History of MMDSAvril BannisterNo ratings yet

- PowerMaxExpress V17 Eng User Guide D-303974 PDFDocument38 pagesPowerMaxExpress V17 Eng User Guide D-303974 PDFSretenNo ratings yet

- Online data sheet for 3D LIDAR Sensors MRS1104C-111011 and MRS1000Document9 pagesOnline data sheet for 3D LIDAR Sensors MRS1104C-111011 and MRS1000Zaki ZamaniNo ratings yet

- EMR2 Flyer enDocument6 pagesEMR2 Flyer enEloy Cabrera100% (3)

- 11050000G2 Auxiliary Power SuppliesDocument6 pages11050000G2 Auxiliary Power Suppliestha_ansNo ratings yet

- Radar Level Sensor: Block DiagramDocument4 pagesRadar Level Sensor: Block Diagramsouma yukihiraNo ratings yet

- OP AmpsDocument13 pagesOP AmpsMy PhoneNo ratings yet

- RC Circuits: Instructor: Kazumi TolichDocument11 pagesRC Circuits: Instructor: Kazumi TolichSoji AdimulaNo ratings yet

- RF Plan Release 3.0 Release NotesDocument6 pagesRF Plan Release 3.0 Release NotesMichele PastoreNo ratings yet

- SP3-GT35 HMI - Human Machine Interface: FeaturesDocument2 pagesSP3-GT35 HMI - Human Machine Interface: FeaturesSEBATELEC SEBATELECNo ratings yet

- CDI (Capacitive Discharge Ignition) : Unit-IIDocument12 pagesCDI (Capacitive Discharge Ignition) : Unit-IIVARUN BABUNELSONNo ratings yet

- Thinvent Micro 6 Mini PC: Performance With StyleDocument2 pagesThinvent Micro 6 Mini PC: Performance With Style郑伟健No ratings yet

- Vehicle Speed Detection System Using IR PDFDocument7 pagesVehicle Speed Detection System Using IR PDFSIDHARTH MISHRANo ratings yet

- Shield Ekg Emg Rev B SchematicDocument1 pageShield Ekg Emg Rev B SchematicwidyarahmahNo ratings yet

- 2Document10 pages2Marcelo OemNo ratings yet

- Manual de Operación TensiómetroDocument6 pagesManual de Operación TensiómetroIsrael SanchezNo ratings yet

- Asdi Damanik: Personal DetailsDocument7 pagesAsdi Damanik: Personal DetailsIlham RangkutiNo ratings yet

- PT580 TETRA Portable BrochureDocument2 pagesPT580 TETRA Portable BrochureFabio LisboaNo ratings yet

- 1.1embedded System Implementation: Advanced Health Sensing Smart PillowDocument46 pages1.1embedded System Implementation: Advanced Health Sensing Smart Pillowkum1242No ratings yet

- Soundcard ScopeDocument3 pagesSoundcard ScopeJmlm JoseNo ratings yet

- Using The Grandstream GXP 1625 (Applicable For Other Models)Document2 pagesUsing The Grandstream GXP 1625 (Applicable For Other Models)Christopher NolanNo ratings yet

- Clone A Remote With ArduinoDocument10 pagesClone A Remote With Arduinodeath914No ratings yet

- Tpca8057-H Mosfet Ps3 Placa Modelo PQX 001Document9 pagesTpca8057-H Mosfet Ps3 Placa Modelo PQX 001Eisenhower Garcia LealNo ratings yet

- ECT201 - Discrimination With LV Power Circuit-Breakers 21Document1 pageECT201 - Discrimination With LV Power Circuit-Breakers 21Hany ShaltootNo ratings yet

- How To Create A LabVIEW Based Virtual Instrument For NI Multisim - National Instruments PDFDocument6 pagesHow To Create A LabVIEW Based Virtual Instrument For NI Multisim - National Instruments PDFAgus MelaskeNo ratings yet

- Models - Acdc.inductor in CircuitDocument14 pagesModels - Acdc.inductor in CircuitneomindxNo ratings yet

- M140 - HighVoltage DC Power - SuppliesDocument4 pagesM140 - HighVoltage DC Power - SuppliesAlexander PischulinNo ratings yet