Professional Documents

Culture Documents

ES Lecture2 (ARM)

Uploaded by

Rajneesh SharmaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ES Lecture2 (ARM)

Uploaded by

Rajneesh SharmaCopyright:

Available Formats

Embedded Systems

Lecture 2: ARM Processor fundamentals

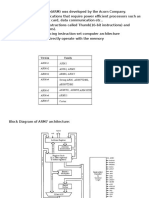

ARM core dataflow model

ARM Core data flow

Von-Neumann implementation data items and instructions share the same bus. Instruction decoder translates instructions before they are executed. Load instruction: copy data from memory to register Store instruction: copy data from register to memory There are no data processing instructions that directly manipulate data in memory. Data items are placed in the register file a storage bank made up of 32-bit registers. ARM instructions typically have two source registers Rn and Rm and one destination register Rd. ALU and MAC (Multiply-accumulate) unit takes the register values Rn and Rm from A and B buses and computes a result. Load and store instructions use the ALU to generate an address to be held in the addres register and broadcast on the Address bus. The register Rm can be alternatively pre-processed in the barrel shifter before it enters the ALU. For load and store instructions the incrementer updates the address register before the core reads or writes the next register value from or to the next sequential memory location.

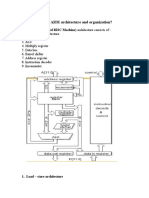

Registers

General purpose registers hold either data or an address. All registers are 32-bit in size. 18 active registers

16 data registers r0 to r15 2 process status registers

CPSR Current Program Status Register SPSR Saved Program Status Register

r13, r14, r15 have special functions

R13 stack pointer (sp) and stores the head of the stack in the current processor mode R14 link register (lr) where the core puts the return address whenever it calls a subroutine. R15 programme counter (pc) and contains the address of the next instruction to be fetched by the processor.

r13 and r14 can also be used as general purpose register as these registers are banked during a processor mode change. The registers r0 to r13 are orthogonal. Any instruction that you can apply to r0, you can equally apply to other registers. There are instructions that treat r14 and r15 in a special way.

Current Program Status Register (CPSR)

ARM core uses CPSR to monitor and control internal operations. CPSR is a dedicated 32-bit register and resides in the register file. CPSR is divided into four fields each 8-bits wide:

Flags Status Extension - reserved for future use Control reserved for future use

Control field contains processor modes, state and interrupt mask bits.

CPSR

Processor Modes

The processor mode determines which registers are active and the access rights to the CPSR register itself. Each processor mode is either privileged or nonprivileged. A privileged mode allows full read-write access to CPSR. A non-privileged mode only allows read access to the control field in the CPSR but still allows R/W access to the condition flags.

Processor Modes

Banked Registers

ARM has 37 registers in the register file Of those, 20 registers are hidden from a program at different times. These registers are called banked registers (shown as shaded region) They are available only when the processor is in a particular mode. Every processor mode except user mode can change mode by writing directly to the mode bits of the CPSR. All modes except system mode have a set of associated banked registers that are a subset of the main 16 registers. A banked register maps one-to-one onto a user mode register. If you change processor mode, a banked register from the new mode will replace an existing register. There is no spsr available in the user mode.

Banked Registers Contd ...

Changing Processor Mode

The processor mode can be changed by a program that writes directly to CPSR (the processor has to be in privileged mode) or by hardware when core responds to an exception or interrupt. Following exceptions cause a mode change:

Reset Interrupt Request Fast interrupt request Software interrupt Data abort Prefetch abort Undefined instruction

Exception and interrupt suspend the normal execution of sequential instructions and jump to a specific location.

Changing processor modes

Core changing from user mode to interrupt request mode, which happens when an interrupt request occurs due to an external device raising an interrupt to the process core. This change causes user registers r13 and r14 to be banked. The user registers are replaced with registers r13_irq and r14_irq respectively. r13_irq contains the stack pointer for the interrupt request mode. r14_irq contains the return address. The cpsr is copied to spsr_irq. To return back to the user mode, a special return instruction is used that instructs the core to restore the original cpsr from spsr_irq and bank in the user registers r13 and r14. The register spsr can only be modified in a privileged mode. There is no spsr available in the user mode. Note that cpsr is not copied into the spsr when a mode change is forced due to a program writing directly to the cpsr. The saving of cpsr only occurs when an exception or interrupt is raised.

Mode bits & Vector Table

Exception Vector Table

The exception vector table consists of designated addresses in external memory that hold information to handle an exception, an interrupt or other atypical event (e.g. reset). For example, when an interrupt request comes along, the processor will change the program counter to 0x18 and begin fetching instructions from there. One can put a branch instruction at this location so that the processor can jump to the interrupt handler located at some other location in the memory. On reset, the core jumps to address 0x0 and starts fetching instruction. We either need to provide a reset exception handler (initialization routine) or we can begin coding at this address.

State & Instruction Sets

The state of the core determines which instruction set is being executed. There are three instruction sets

ARM Thumb Jazelle

The Jazelle (J) and Thumb (T) bits in the cpsr reflect the state of the processor. Jazelle instruction set is a closed set and is not openly available.

State & Instruction Sets Contd...

Interrupt Masks & Condition Flags

Interrupt masks are used to stop specific interrupt requests from interrupting the processor. Two types of interrupt request Interrupt Request (IRQ) Fast interrupt request (FIQ) Interrupt mask bits I (7) and F (6)

Condition flags are updated by comparison and the result of ALU operation that specify S instruction suffix. Eg. If a SUBS instruction results in a zero register value, Z flag in cpsr is suffix set. Most ARM instructions can be executed conditionally on the value of the condition flags. Processors with DSP extensions, the Q bit indicates overflow or saturation that has occcured in an enhanced DSP instruction. Conditional execution controls whether or not the core will execute an instruction. Most instructions have a condition attribute which is compared with the condition flags in cpsr to determine if the instruction is to be executed. The condition attribute is post-fixed to the instruction mnemonic, which is encoded into the instruction.

You might also like

- 2 Programming Model and PipeliningDocument40 pages2 Programming Model and PipeliningHiteshNo ratings yet

- 18CS44 MODULE1 Chapter2Document38 pages18CS44 MODULE1 Chapter2Jim MoriartyNo ratings yet

- ARM 4 Part2Document9 pagesARM 4 Part2SUGYAN ANAND MAHARANANo ratings yet

- ARM7TDMI ArchitectureDocument22 pagesARM7TDMI ArchitecturemraohrishikeshNo ratings yet

- ARM ArchitectureDocument26 pagesARM ArchitectureKiran KumarNo ratings yet

- Arm NotesDocument22 pagesArm NotesShreya SatheeshNo ratings yet

- ARM7 ARCHITECTURE OVERVIEWDocument8 pagesARM7 ARCHITECTURE OVERVIEWVipin TiwariNo ratings yet

- ARM Cortex M3 RegistersDocument22 pagesARM Cortex M3 RegistersRaveendra Moodithaya100% (2)

- ARM Microcontroller Introduction and FeaturesDocument21 pagesARM Microcontroller Introduction and FeatureskalyanNo ratings yet

- ARM Processor GuideDocument65 pagesARM Processor GuideSaurabh GargNo ratings yet

- Arm 7 ArchitectureDocument22 pagesArm 7 Architecturejinto0007No ratings yet

- ARM Instruction Sets and Program: Jin-Fu Li Department of Electrical Engineering National Central UniversityDocument116 pagesARM Instruction Sets and Program: Jin-Fu Li Department of Electrical Engineering National Central UniversityRANJITHANo ratings yet

- Arm 7 ArchitectureDocument22 pagesArm 7 ArchitectureNarasimha Murthy YayavaramNo ratings yet

- Unit IV MPMCDocument22 pagesUnit IV MPMCDeepika SanalaNo ratings yet

- Unit-8 MPMCDocument22 pagesUnit-8 MPMCMani Kanta ReddyNo ratings yet

- ARM Processor Blinking LED CodeDocument8 pagesARM Processor Blinking LED CodeTejas FattewaleNo ratings yet

- ARM Processor CoreDocument34 pagesARM Processor CorevarshaksNo ratings yet

- Course Name-Microprocessor: Model Institute of Engineering & TechnologyDocument10 pagesCourse Name-Microprocessor: Model Institute of Engineering & Technologyeklavya0304No ratings yet

- Register OrganisationDocument9 pagesRegister Organisationdineshe.eceNo ratings yet

- ARM PresentationDocument51 pagesARM PresentationSumeet SauravNo ratings yet

- ARM7TDMI ProcessorDocument44 pagesARM7TDMI Processormuralik_64No ratings yet

- ARM 1vDocument31 pagesARM 1vsuntosh_14No ratings yet

- Module - 1: Salient Features of The Cortex-M3Document29 pagesModule - 1: Salient Features of The Cortex-M3Dr Ravi Kumar A.VNo ratings yet

- ARM Processor 3Document27 pagesARM Processor 3Ayan AcharyaNo ratings yet

- ARM ArchitectureDocument6 pagesARM ArchitectureCarlos AraujoNo ratings yet

- ARM (Advanced RISC Machines) : Sushma RawalDocument48 pagesARM (Advanced RISC Machines) : Sushma RawalGaurav GrimReaper Roy100% (2)

- Arm ProcessorDocument18 pagesArm ProcessorashokNo ratings yet

- The ARM Instruction Set: Advanced RISC MachinesDocument58 pagesThe ARM Instruction Set: Advanced RISC MachinesarthicseNo ratings yet

- Module 4 Topic 2 ARM Processor FundamentalsDocument64 pagesModule 4 Topic 2 ARM Processor FundamentalsDeepti ChandrasekharanNo ratings yet

- Cortex-M3/M4 Architecture Programmer’s Model OverviewDocument37 pagesCortex-M3/M4 Architecture Programmer’s Model Overviewsuhaskakade0075745No ratings yet

- Lecture 6b: MSP430 Assembly Language Tutorial: MSP430 CPUDocument64 pagesLecture 6b: MSP430 Assembly Language Tutorial: MSP430 CPUSufyan NikaninNo ratings yet

- ARM A9 Intro IntelfpgaDocument29 pagesARM A9 Intro Intelfpgakerry emiNo ratings yet

- Laboratory Manual: Embedded SystemsDocument74 pagesLaboratory Manual: Embedded SystemsVipul MistryNo ratings yet

- Arm Instruction ProgramDocument121 pagesArm Instruction ProgramErmin KatardzicNo ratings yet

- Programable PPTDocument91 pagesProgramable PPTJay PatelNo ratings yet

- 02 ARM Processor FundamentalsDocument65 pages02 ARM Processor Fundamentalsbengaltiger100% (2)

- ARM: An Advanced MicrocontrollerDocument54 pagesARM: An Advanced MicrocontrollershubhamNo ratings yet

- ARM - Advanced RISC Machines Architecture OverviewDocument60 pagesARM - Advanced RISC Machines Architecture OverviewPraveen EdulaNo ratings yet

- Two Marks-8051.docx - 1570617188187Document4 pagesTwo Marks-8051.docx - 1570617188187PraveenNo ratings yet

- Architectural Features and Block Diagram of Arm7 TdmiDocument23 pagesArchitectural Features and Block Diagram of Arm7 TdmiMrunal Kshirsagar100% (1)

- ArmDocument203 pagesArmJannathul Firdous MohamedNo ratings yet

- ARM - An Understanding and MoreDocument87 pagesARM - An Understanding and MoreSivasini Netra S ANo ratings yet

- ESRTPDocument13 pagesESRTPadvaitkaleNo ratings yet

- Acorn RISC MachineDocument6 pagesAcorn RISC Machinesolomon girmaNo ratings yet

- Arm Program ModelDocument4 pagesArm Program ModelvlkumashankardeekshithNo ratings yet

- COA Module 3 PART 1Document30 pagesCOA Module 3 PART 1Anirban BhattacharjeeNo ratings yet

- ES LabManual 2011Document74 pagesES LabManual 2011వంశీ క్రిష్ణNo ratings yet

- CortexM Registers 2Document27 pagesCortexM Registers 2Sai Mohnish MuralidharanNo ratings yet

- Cisc vs. RiscDocument53 pagesCisc vs. RiscnikitaNo ratings yet

- ARM Notes From NPTELDocument3 pagesARM Notes From NPTELAnonymous pcNdMpNE100% (1)

- DSP ArchitectureDocument50 pagesDSP ArchitectureNayan SenNo ratings yet

- ARM CORTEX M4 Memory LayoutDocument11 pagesARM CORTEX M4 Memory LayoutGurram KishoreNo ratings yet

- Chapter 2 - Architecture of ARM ProcessorDocument43 pagesChapter 2 - Architecture of ARM Processor方勤No ratings yet

- Notes Mpgl1 Chapter6Document46 pagesNotes Mpgl1 Chapter6Joshua DuffyNo ratings yet

- The Acorn RISC Machine (ARM)Document12 pagesThe Acorn RISC Machine (ARM)Vikas SinghNo ratings yet

- Arm Intro l01Document47 pagesArm Intro l01Tanishq GuptaNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Svug 2007 Abv LitterickDocument18 pagesSvug 2007 Abv LitterickRajneesh SharmaNo ratings yet

- Gate Level SimulationDocument26 pagesGate Level Simulationjit20080% (1)

- Ashutosh Sharma CVDocument3 pagesAshutosh Sharma CVRajneesh SharmaNo ratings yet

- Introduction to Verilog Fundamentals and Advanced ConceptsDocument62 pagesIntroduction to Verilog Fundamentals and Advanced ConceptsdilipbagadiNo ratings yet

- FIFODepth CalculationDocument2 pagesFIFODepth CalculationSuyog Avinash ChutkeNo ratings yet

- Lekdyuksa Osq Vuqiz KSX: (Application of Integrals)Document19 pagesLekdyuksa Osq Vuqiz KSX: (Application of Integrals)Rajneesh SharmaNo ratings yet

- Interview QuestionDocument7 pagesInterview QuestionRajneesh SharmaNo ratings yet

- F K&foeh T Kfefr: (Three Dimensional Geometry)Document42 pagesF K&foeh T Kfefr: (Three Dimensional Geometry)Rajneesh SharmaNo ratings yet

- Microprocessor Viva QuestionsDocument2 pagesMicroprocessor Viva QuestionsPrabhakar PNo ratings yet

- TMS320F2812 Digital Signal Processor (DSP) Implementation of DPWMDocument4 pagesTMS320F2812 Digital Signal Processor (DSP) Implementation of DPWMhabibsutriharjoNo ratings yet

- Closing The Gap Between Asic Custom Tools and TechniquesDocument431 pagesClosing The Gap Between Asic Custom Tools and TechniquesAnonymous ZaO7fL4t100% (3)

- EUCIP Core Syllabus Version 3.0Document38 pagesEUCIP Core Syllabus Version 3.0fabrizio5103No ratings yet

- ARM PresentationDocument51 pagesARM PresentationSumeet SauravNo ratings yet

- Micro PillsDocument33 pagesMicro PillsAmshala SrikanthNo ratings yet

- Real Time Control - InterruptsDocument39 pagesReal Time Control - InterruptsmkrishnadNo ratings yet

- 3-Course Plan - UG - EC303 DSPDocument18 pages3-Course Plan - UG - EC303 DSPAravinth RameshNo ratings yet

- Nice Assembly ProgrammingDocument140 pagesNice Assembly Programmingprakashcawasthi100% (6)

- Communicating With The MicroprocessorDocument13 pagesCommunicating With The MicroprocessorRyan John de LaraNo ratings yet

- Testing EnoughDocument17 pagesTesting EnoughRavijosanNo ratings yet

- Code OptimizationDocument49 pagesCode OptimizationShabin MuhammedNo ratings yet

- MCU - PIC24FV32KA304 - MICROCHIP - Programming SpecificationsDocument54 pagesMCU - PIC24FV32KA304 - MICROCHIP - Programming SpecificationsLudwig SchmidtNo ratings yet

- IT225: Computer Organizations: August 25, 2014 (Monday)Document12 pagesIT225: Computer Organizations: August 25, 2014 (Monday)skiloh1No ratings yet

- VIRTUALIZATION OVERVIEW: BRINGING VIRTUALIZATION TO X86Document14 pagesVIRTUALIZATION OVERVIEW: BRINGING VIRTUALIZATION TO X86Nayanthara SreenivasNo ratings yet

- Top Level View of Computer Function and InterconnectionDocument38 pagesTop Level View of Computer Function and Interconnectionhsi3No ratings yet

- NC PRGDocument9 pagesNC PRGNAGU2009No ratings yet

- 9A12301 Digital Logic Design and Computer OrganizationDocument4 pages9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNo ratings yet

- EC6504 Lecture Notes RejinpaulDocument164 pagesEC6504 Lecture Notes RejinpaulJeffreyJosanneM0% (1)

- ABB RPBA 01 Profibus DP Adapter Module Start GuideDocument5 pagesABB RPBA 01 Profibus DP Adapter Module Start GuideAn Sang0% (1)

- BuflabDocument11 pagesBuflabrasromeoNo ratings yet

- ARM 9 WEB ServerDocument36 pagesARM 9 WEB ServerNagraj TondchoreNo ratings yet

- B SCDocument56 pagesB SCRythemBansalNo ratings yet

- MSP 430 F 2011Document93 pagesMSP 430 F 2011Amarnath M DamodaranNo ratings yet

- CISC 101 NotesDocument20 pagesCISC 101 NotesRobinNo ratings yet

- ST20-GP6: Gps ProcessorDocument124 pagesST20-GP6: Gps ProcessorDenis PrivatNo ratings yet

- Smart Memories A Seminar Report: A.Rana Pratap (14761A0506)Document15 pagesSmart Memories A Seminar Report: A.Rana Pratap (14761A0506)Hari KrishNo ratings yet

- DSP CasestudyDocument23 pagesDSP CasestudyShayani BatabyalNo ratings yet

- Me2401 Mechatronics - 2 Marks With Answer PDFDocument15 pagesMe2401 Mechatronics - 2 Marks With Answer PDFSiva RamanNo ratings yet

- A Levels Computing 9691 Revision NotesDocument17 pagesA Levels Computing 9691 Revision NotesMuhammad Ahmad FarazNo ratings yet