Professional Documents

Culture Documents

Lalit Mangal SUID: 808774406: CSE 765 VLSI Testing and Verification Exam 1

Uploaded by

Lalit MangalOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lalit Mangal SUID: 808774406: CSE 765 VLSI Testing and Verification Exam 1

Uploaded by

Lalit MangalCopyright:

Available Formats

CSE 765 VLSI Testing and Verification Exam 1

Lalit Mangal SUID: 808774406

1 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

1. Depending on whether the number of inversions on a combinational feedback loop is even or odd, it can introduce either sequential behavior or oscillation into a design. Because the value stored in the loop cannot be controlled or determined during test, this can lead to an increase in test generation complexity or fault coverage loss. Because combinational feedback loops are not a recommended design practice, the best way to fix this problem is to rewrite the RTL code generating the loop. In cases where this is not possible, a combinational feedback loop, as shown in Figure a, can be fixed by using a test mode signal TM. This signal permanently disables the loop throughout the entire shift and capture operations by inserting a scan point (i_e_, a combination of control and observation points) to break the loop, as shown in Figure b.

2 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

2. Concurrent Fault Simulation.

Pattern 1

a=1, b=0 At e s/0, it is not detected since b=0 and therefore the output of good gate is same as that of the bad gate. Similarly at g S/1 not detected for the given input pattern, However it can detect g/0, e/1 faults. Pattern 2

3 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

a=0, b=1 At e which is s/0 not detected. At g which is s/1 is detected. Other detected faults a/1, f/1. Pattern 3

a=1, b=1 Faults detected are as follows: At e s/0 will be detected. Also a transition from 1 to 0 occurs at g, therefore fault at point g which is s/1 will be detected. Other faults which can be detected are a/0, f/0. 4 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

3. Critical Path Tracing

5 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

4.Untestable Fault Identification

a. Compute the static logic implications of b=0 {d=e=g=h=i=0; k=1} b. Compute the static logic implications of b=1 {b=d=e=f=1; j=z=0} c. Set of faults that are untestable when b=0. Faults unexcitable when b=0 are b/0, d/0, h/0, e/0, k/1, i/0 Faults unobservable when b=0 are c/0, c/1 Faults undetectable when b=0 are b/0, d/0, h/0, e/0, k/1, i/0, c/0, c/1 d. Set of faults that are untestable when b=1 Faults unexcitable when b=1 are b/1, e/1, d/1, f/1, g/0, z/0 Faults unobservable when b=1 are a/0, a/1, h/0, h/1, i/0, i/1, k/0, k/1 Faults undetectable when b=1 are a/0, a/1, b/1, d/1, f/1, e/1, h/1, h/o, j/0, k/0, k/1, z/0, i/0, i/1 e. The intersection of the two sets of undetectable faults computed in part c and part d are the set of undetectable faults on stem b. untestable faults= e/0, c/0, c/1, i/0, k/1, h/0, g/0

6 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

5. Consider the circuit shown and use PODEM to generate a vector for each of the following faults: a. k/1 b. k/0 c. g/1 d. g/0

7 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

6.

. The set of reachable states are as follows: 00, 01, 11 a b c 0 0 0 0 0 1 0 1 1 0 1 0

d 0 0 1 0

e 0 1 1 0

Fig. FSM State Diagram

8 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

7. The cellular automaton of length 5 is 11001, 1 refers to CA rule 150, 0 refers to CA rule 90. So, rule 90: Xi(t+1) = Xi-1(t) + Xi+1(t) Rule 150: Xi(t+1) = Xi-1(t) + Xi+1(t) + Xi(t) The generated sequence is: 11111 01000 11100 01110 10011 11110 01011 11010 00001 00011 00110 01111 11000 00100 .. due to very large sequence, I cannot give all the 31 number in the sequence, but I proved it. According to the original paper, Cellular Automata-Based Pseudo Random Number Generator is for BIST. Maximal cycle length hybrid cellular automata exist for lengths larger than 53 but must be found using computer simulation. That is true, the rule for length 53 is already very long. 1000011100101010001000001001100101110111110110010101 (length 53)

8. F(x)= 1+x+x^4 and M={10011011}, we obtain the fault free signature R={1011}. For the faulty sequence M={11111111} or M(x)=1+x+x^2+x^3+x^4+x^5+x^6+x^7, by polynomial division M(x)=q(x)f(x)+r(x), we can obtain q(x)=x+x^2+x^3, and r(x)=1+x^2+x^3. Thus the faulty signature R={1011} Since R=r, the fault, the fault is undetected. Another solution can be deduced by using error sequence E, where E=M+M={01100100} or E(x)=xf(x). Since f(x) divides E(x), this fault is undetected.

9. a. Test Time for STUMPs = Patterns * Scan Chain Length * Clock Period = 100,000 * 100 * 1000 * (1/200) = 50s b. Test Time for BILBO= Patterns * Scan Chain Length * Clock Period= 100,000 * (1/200)= 50 * 10^(-6)s c. Test Time for STUMPs = Patterns * Scan Chain Length * Clock Period = 100,000 * 100 * 1000 * (1/20) = 500s 9 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

10. March Element Type w0 r0 r1 {w1, r1} {w0, r0}

Faults Detected are SAF(Stuck At Fault), TF(Transition Fault) and some part of (A,F)Address Decoding Fault, CFin(Coupling Fault-inversion)

11. a. Number of possible single stuck-at faults circuit has= 50 b. Number of collapsed single stuck-at faults circuit has= 2*(number of primary outputs+ number of fanout stems)+total number of gate(including inverter)inputs- total number of inverters=2*(1+5)+19-0 =31 c. Test Vector to detect s/0 on k= 00111, 0 d. The three of the other faults which can be detected by the vector 00111, 0 are s/0 on j; s/0 on y; s/1 on d.

10 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

12. Logic Levelization

a. The dotted lines in the circuit represent the levelization of the given circuit. Values 2,3,4,5,6 in the components of the circuit represents the levelization in the circuit. b. Pseudo Code read(a,b c,h i); d= OR(a,b); e= D FlipFlop(c); f= AND(d,e); g= buffer(f); j= OR(g,h); j=NOT(j) k= OR(f,i); k= NOT(k); w= AND(a,j); w= NOT(w); x= AND(j,k); y= AND(b,k); y= NOT(y); z= AND(w,x,y); end

11 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

13. D Algorithm Initially we place D-bar on h. The D-frontier at this time includes{a,j}. Next we pick a D frontier to propagate the fault effect across. Suppose we pick j. Then the decision h=0 is made. At this time Dfrontier becomes w,x,y. We pick D-frontier that is closest to PO. Thus we pick w. The J frontier consists of h=D-bar. Justifying J=D-Bar is likewise straightforward setting h=0. Thus the vector consists of 00X010 detects the target fault h/1.

14. (f=0)dz/df = f(z(f=0)+z(f=1)) =f(ab) So the test vectors are {00000 00001 00010 00011 00100 00101 00110 00111} (h=1)dz/dh=h(z(h=0)+z(h=1)) =h(0+0) =0 So it is untestable (h=1)dz/dh=h(z(h=0)+z(h=1)) =h(0+0) =0 So it is untestable

15. Only one static implications for the circuits by considering direct implementation for g=0 which is f=0. No static implication for the circuit considering indirect implementation.

16. Four patterns are enough to exhaustively test each gate in the parity checker independent of n. They are as follows: (11.1), (00..0), (100..0), and (011.1).

12 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

17. SCOAP controllability and observability measures for a two-input exclusive-NOR gate is shown in the diagram below.

18. System Availability= MTBF/(MTBF+MTTR) MTBF is Mean Time Between Failure=1year MTTR is Mean Time Between Repair=? It would take 3153.6 seconds to repair a system each year if the availability of the system is 99.99%.

19. Defect Level= 1- yield^(1-fault coverage) 5.18 percentage of all parts shipped will be defective if the yield is 7% and the fault coverage is 98% for the set of test vectors used to test the parts .

20. Given, critical path delay of a circuit is 100ps and 10% margin for the clock period. Therefore, Penalty= 30 * 1/(100*(1-0.1)+30) = 25%

13 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

21. Scan Flipflops= 10,000 Combinational Vectors= 100,000 Clock Rate= 100MHz Time the Test will Take= (Scan Flipflops + Combinational Vectors)/Clock Rate = (10,000+100,000)/(100*10^6)= 1.1ms

22. The aliasing probability for a signature analyzer constructed with an n-stage linear feedback shift register (LFSR) with primitive feedback polynomial is given by ( 2^(L-n)-1)/ ((2^L)-1)

23. The essential minimum number of test pins added for scan design is two which is Scan Enable and Scan Input.

24. The complexity of a memory test sequence for an n-bit memory should be linear time.

25. For a ten-input AND gate, the minimum number of test vectors that will detect all single stuck-at faults = 11

26. A march test: is a sequence of march elements, a sequence of operations applied to every cell,in either one of two address orders: Increasing address order; from cell 0 to cell n-1 Decreasing address order; from cell n-1 to cell 0. MATS(Modified Algorithmic Test Sequence) Test contains of 3 march elements : M0, M1, M2 MATS++ { (w0) (r0, w1) (r1, w0, r0)} Faults detected are Address Decoding Fault, stuck at Fault, Transition fault and Stuck Open Fault. Test Length= 6n , where n is the number of bits of the memory array.

14 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

27.

values to abcd that would induce the largest current in the bridge are those values which makes either X or Y equal to 1. AND GATE Truthtable A b X A 0 0 0 B 0 1 0 C 1 0 0 D 1 1 1 OR GATE Truthtable a b X E 0 0 0 F 0 1 1 G 1 0 1 H 1 1 1 The sets of combination of values that will induce maximum current in the bridge are given as follows: {A,F},{A,G}, {A,H}, {B, F}, {B,G}, {B,H}, {C,F},{C,G}{C,H},{D,E}, or {E,D} {F,A},{G,A}, {H,A}, {F,B}, {G,B},{H,B}, {F,C}, {G,C}, {H,C}

15 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

28. Table below use the parallel-pattern single-fault propagation fault simulation technique to identify which test vectors can detect H/1, J/0, E/0,K/1 faults. PPSFP Input Input Input Internal Internal Internal OUTPUT Fault FaultFree P A B 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 C 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 E 1 1 1 0 1 1 1 0 1 1 1 0 0 0 0 0 1 1 1 0 H 1 0 1 0 1 1 1 1 1 0 1 0 0 0 0 0 1 0 1 0 J 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 1 0 0 0 1 K 0 1 0 0 0 0 0 0 0 1 0 1 0 0 0 0 1 1 1 1

P1 1 P2 0 P3 1 P4 0

FaultH/1

P1 1 P1 0 P3 1 P4 0

FaultJ/0

P1 1 P1 0 P3 1 P4 0

FaultE/0

P1 1 P1 0 P3 1 P4 0

FaultK/1

P1 1 P2 0 P3 1 P4 0

Note: Red color shows the faults in the above table.

16 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

29. a. Binary Counter as Exhaustive Pattern generator(EPG)

Potential Use: Binary Counter as Exhaustive Pattern generator(EPG) can be used as an exhaustive pattern generator to test a four-input combinational CUT.

b. 3-bit complete LFSR

Potential Use: It can be used as an exhaustive pattern generator to test a three-input CUT.

c. Four Stage MISR (Multiple Input Signature Register)

MISR reduces test logic by using multiple bit streams to create a signature. BILBO (built-in logic block observer) uses MISR as both PRBS generator and signature register. Potential Use: It can be used as an output response analyzer that can compact 4-bit output responses into a signature and compare it with a golden signature for the fault-free circuit either embedded onchip or stored off-chip.

17 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

30. a. Differences between Testing and Functional Verification Functional Verification: Functional Verification is the activity where design or product is tested to make sure that all the functions of the device are indeed working as stated. This activity ensures that features functions as specified. It is noted that some of the device features may or may not be visible to the user and may be internal to the design itself. However it is imperative that all the features are verified to operate correctly as specified. This verification activity usually consumes more time in the design cycle. Testing: Circuit manufacturers must thoroughly test their products before delivering them to customers. The causes of circuit failure are design errors and manufacturing defects. Design errors are caused by errors in the layout. We normally attempt to detect design errors by simulating the circuit and testing the simulation. No simulation can perfectly predict what a real circuit will do. For example, most simulations cannot predict whether or not latch up will occur. Thus, it is necessary to test a real circuit before we can be sure that all design errors have been fixed. Manufacturing defects are caused by random variations in the manufacturing process that can cause malfunctions in circuit components. These defects can occur even in circuits that have no design errors. Most modern processes have an average defect density of around 1 defect per cm2. As the chip area increases, the probability of a defective chip increases and the yield (probability of no defects) decreases. For performance reasons, we would like to have the chip as large as possible. This means that a considerable fraction of large chips will be defective and we must test each chip to be sure that it is defect free.

b. Differences between ATPG and BIST ATPG: ATPG is an electronic design automation method/technology used to find an input (or test) sequence that, when applied to a digital circuit, enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. The generated patterns are used to test semiconductor devices after manufacture, and in some cases to assist with determining the cause of failure. The effectiveness of ATPG is measured by the amount of modeled defects, or fault models, that are detected and the number of generated patterns. These metrics generally indicate test quality (higher with more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration. It is influenced by the fault model under consideration, the type of circuit under test (full scan, synchronous sequential, or asynchronous sequential), the level of abstraction used to represent the circuit under test (gate, register-transistor, switch), and the required test quality. BIST: A built-in self-test (BIST) or built-in test (BIT) is a mechanism that permits a machine to test itself. Engineers design BISTs to meet requirements such as:

high reliability lower repair cycle times

or constraints such as:

limited technician accessibility 18

March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

cost of testing during manufacture

BIST is commonplace in weapons, avionics, medical devices, automotive electronics, complex machinery of all types, unattended machinery of all types, and integrated circuits.

c. Difference between D Algorithm and PODEM Algorithm D Algorithm:Values assigned to internal nodes and PIs Decisions Choose a D from DFrontier Assign a value to justify an output Conflict -- An implied value different from assigned value Other bounding condition empty D-Frontier PODEM Algorithm: Values assigned only to PIs Decision Choose a PI and assign a value No conflicts Bounding conditions fault not excited empty D-Frontier X-path check o lookahead

d. Difference between BILBO and STUMP BILBO: Combined functionality of D flip-flop, pattern generator, response compacter, & scan chain Reset all FFs to 0 by scanning in zeros.

Example of BILBO usage is given below: 19 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

SI Scan In SO Scan Out Characteristic polynomial: 1 + x + + xn CUTs A and C: BILBO1 is MISR, BILBO2 is LFSR CUT B: BILBO1 is LFSR, BILBO2 is MISR

STUMP: Test procedure: 1. Scan in patterns from LFSR into all scan chains (200clocks) 2. Switch to normal functional mode and clock 1 x withsystem clock 3. Scan out chains into MISR (200 clocks) where test results are compacted Overlap Steps 1 & 3 Requirements: o Every system input is driven by a scan chain o Every system output is caught in a scan chain or drives another chip being sampled Architecture and example: SR1 SRn 25 full-scan chains, each 200 bits 500 chip outputs, need 25 bit MISR (not 5000 bits)

20 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

e. Difference between Standard LFSR and Modular LFSR Standard LFSR

Autocorrelation any shifted sequence same as original in 2n-1 1 bits, differs in 2n-1bits Cannot initialize to all 0s hangs If X is initial state, progresses through states X, Ts X, Ts2X, Ts3X, Matrix period: Smallest k such that Tsk= I LFSR cycle length Described by characteristic polynomial: f (x) = |Ts I X |= 1 + h1 x + h2 x2 + + hn-1 xn-1 + x

Modular LFSR:

Described by companion matrix Tm = TsT Internal XOR LFSR XOR gates in between D flip-flops Equivalent to standard External XOR LFSRWith a different state assignmentFaster usually does not matter Same amount of hardware X (t + 1) = Tm x X (t) f (x) = | Tm I X |= 1 + h1 x + h2 x2 + + hn-1 xn-1 + xn Right shift equivalent to multiplying by x, and then dividing by characteristic polynomial and storing

21 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

f. Difference Between MUX-D Scan Cell and LSSD Scan Cell MUX-D Scan Cell: In newer technologies (45nm and lesser); the Mux D cell is not used because of the combinational elements and the inherent impact on the controllability thats a major concern in semiconductor testing. In making the choice of which is better; it just depends on the technology. MUX-D is better if we can offer just one scan clock. No phase relationships to be maintained if the select signal is strobe. But, with MUX (again a combinational logic), there can be guaranteed uncertainty. LSSD Scan Cell: The LSSD cell, though offers a lesser usable slack is inherently a master-slave flop flop/ latch combination and is free from the effects of combinational logic- hence better controllability and observability. Even in terms of area and power; LSSD cell fairs better. The LSSD cell needs the proper non-overlapping phase relationship to be maintained between the scan clocks and the free running clock and between themselves; and of course the timing overhead. Apart from that, in terms of performance, this will be a better choice.

g. Difference between Logic Simulation and Fault Simulation Logic Simulation: Logic simulation is the use of a computer program to simulate the operation of a digital circuit. Logic simulation is the primary tool used for verifying the logical correctness of a hardware design. In many cases logic simulation is the first activity performed in the process of taking a hardware design from concept to realization. Modern hardware description languages are both simulatable and synthesizable. Advantages: It is a natural way for the designer to get feedback about their design. Because it is just running a program the design itself the designer interacts with it using the vocabulary and abstractions of the design. There is no layer of translation to obscure the behavior of the design. Simulation is completely general. Any hardware design can be simulated. The only limits are time and computer resources. Limitations: There is (usually) no way to know when you are done. It is not feasible to completely test, via simulation, all possible states and inputs of any non-trivial system. Simulation can take an inordinately large amount of computing resources, since typically it uses a single processor to reproduce the behavior of many (perhaps millions of) parallel hardware processes

Fault Simulation: In general, simulating a circuit in the presence of faults is known as fault simulation. The main goals of fault simulation Measuring the effectiveness of the test patterns Guiding the test pattern generator program Generating fault dictionaries Outputs of fault simulation Fault coverage - fraction (or percentage) of modeled faults detected by test vectors Set of undetected faults 22 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

The fault simulation process is illustrated below. Here the fault simulator affects the speed of overall fault simulation.

h. Difference Between Compiled Code and Event Driven Simulation Complied Code Simulation: Applicable to zero-delay combinational logic Also used for cycle-accurate synchronous sequential circuits for logic verification Efficient for highly active circuits, but inefficient for low activity circuits High-level (e.g., C language) models can be used Step 1: Levelize combinational logic and encode in a compilable programming language Step 2: Initialize internal state variables (flip-flops) Step 3: For each input vector Set primary input variables Repeat (until steady-state or max. iterations) Execute compiled code Report or save computed variables Event Driven Simulation: Only gates or modules with input events are evaluated (event means a signal change) Delays can be accurately simulated for timing verification Efficient for low-activity circuits Can be extended for fault simulation 23 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

Steps While (event list not empty) begin t = next time in the list for every event (i, t) begin update value of gate i schedule fanout gates of i in the event list if value changes are expected end end

i.

Difference between Deductive and Concurrent Fault Simulation

Deductive Fault Simulation Deductive fault simulation involves allocating a fault list to each gate. The fault list contains one entry for each fault which is detectable on the output of that gate plus one entry containing the number of faults in the list. The fault list on a gate's output can be computed from fault lists associated with its inputs. Simulating only the behavior of the fault free logic circuits. Need only one pass for each test pattern. All signal values in each faulty circuit are deduced from the fault-free circuit values and the circuit structure. For each test pattern, a deductive procedure is applied to all lines in a level order(for combinational logic) from inputs to outputs Simulating only the behavior of the fault free logic circuits. Definition: The fault list LA is defined as the set containing the name or index of every fault that produces an error on line A when the circuit is in its current logic state. Fault lists are to be propagated from PIs to the POs. List events occur when a fault list changes. Concurrent Fault Simulation Simulate only the elements which differ from the good circuit. The differences are maintained in concurrent fault lists. Each gate retains a list of fault copies each of which stores the status of a fault exhibiting difference from fault-free values. Simulation mechanism is similar to the conceptual fault simulation except that only the dynamical difference w.r.t. fault-free circuit is retained. Very versatile in circuit types and gate delays. Although theoretically all faults in a circuit can be processed in one pass, memory explosion problem restricts the fault number in each pass.

24 March 20 2012

th

CSE 765 VLSI Testing and Verification Exam 1

References

1. VLSI Test Principles and Architectures- Laung- Terng Wang Cheng- WenWu Xiaoqing Wen 2. Google 3. Wikipedia

25 March 20 2012

th

You might also like

- Phoenix Key Press Cheat Sheet GuideDocument3 pagesPhoenix Key Press Cheat Sheet GuideLalit MangalNo ratings yet

- Project Tour Guide IndiaDocument13 pagesProject Tour Guide IndiaLalit MangalNo ratings yet

- Rules of The RoadDocument17 pagesRules of The Roadupandown203No ratings yet

- SATURN-STOTRA Dashrath Brahmand Puran 0Document2 pagesSATURN-STOTRA Dashrath Brahmand Puran 0viky24No ratings yet

- GRE High Frequency WordsDocument2 pagesGRE High Frequency WordsFarhad HossainNo ratings yet

- Very GooodMOSFETDocument61 pagesVery GooodMOSFETlkmangalNo ratings yet

- 240Document6 pages240Lalit MangalNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Samsung Ue78ju7500t Chassis Uwj50 Uhd-Tv PDFDocument120 pagesSamsung Ue78ju7500t Chassis Uwj50 Uhd-Tv PDFautreraNo ratings yet

- Sensor TermoparDocument17 pagesSensor TermoparJose Trinidad Rodriguez QuirozNo ratings yet

- Ex2100e GE PDFDocument118 pagesEx2100e GE PDFFerio Arsyad100% (1)

- How To Perform A Noise Simulation in Cadence - EDA WikiDocument9 pagesHow To Perform A Noise Simulation in Cadence - EDA WikiandroidNo ratings yet

- Electrical Properties of Kevlar-Carbon Fiber Epoxy CompositesDocument7 pagesElectrical Properties of Kevlar-Carbon Fiber Epoxy CompositesJorge RomeroNo ratings yet

- A1205 Datasheet PDFDocument14 pagesA1205 Datasheet PDFAlekso GjakovskiNo ratings yet

- Vestel 11ak37 Chassis TV PDFDocument44 pagesVestel 11ak37 Chassis TV PDFbarber1No ratings yet

- Automatic Railway Gate ControllerDocument32 pagesAutomatic Railway Gate ControllerKaos Polos NakiraNo ratings yet

- 6.6kV switchgear layout and operationDocument16 pages6.6kV switchgear layout and operationraghavendran raghuNo ratings yet

- TTP223 Capacitive Touch Sensor ModuleDocument4 pagesTTP223 Capacitive Touch Sensor ModuleSarah Joy ManimtimNo ratings yet

- Isousb211 (Texas Instruments)Document40 pagesIsousb211 (Texas Instruments)Name SurnameNo ratings yet

- Literature ReviewDocument36 pagesLiterature Reviewprakush_prakush0% (1)

- Contents ListDocument27 pagesContents ListBandaru Lakshmi RaoNo ratings yet

- Bosch Semiconductors and Sensors 2011Document36 pagesBosch Semiconductors and Sensors 2011Mircea Gilca100% (1)

- Robotics With RobotCDocument6 pagesRobotics With RobotCM Madan GopalNo ratings yet

- Argus 7Document4 pagesArgus 7prabhakaran_hdecNo ratings yet

- Antenna FundamentalsDocument54 pagesAntenna FundamentalsMahmoudYasienMashhourNo ratings yet

- LG 32LF630V 32LF630V-ZA Series Service ManualDocument97 pagesLG 32LF630V 32LF630V-ZA Series Service Manualzepus89% (9)

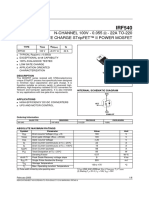

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Seimens Alternator SpecDocument6 pagesSeimens Alternator SpecAdeelNo ratings yet

- Panasonic Sa Vkx80ga, Sa Vkx80gc, Sa Vkx80gsDocument164 pagesPanasonic Sa Vkx80ga, Sa Vkx80gc, Sa Vkx80gsboroda2410100% (1)

- Company ProfileDocument30 pagesCompany ProfileYugendra RNo ratings yet

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsDocument42 pagesSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadNo ratings yet

- CO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierDocument6 pagesCO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierCJ CHNo ratings yet

- Cablemaster CM - Remote Control Programing GuideDocument2 pagesCablemaster CM - Remote Control Programing GuideGlendinning Products, LLC.No ratings yet

- TVL12 IA EPAS q4 Mod1 Inspect Installed Devices Respond Lisnang Bgo v3Document15 pagesTVL12 IA EPAS q4 Mod1 Inspect Installed Devices Respond Lisnang Bgo v3Luis MendezNo ratings yet

- 9702 p1 Current Electricity AllDocument35 pages9702 p1 Current Electricity AllMCHNo ratings yet

- 3 Sensors and TransducersDocument99 pages3 Sensors and TransducersSon Athena100% (2)

- Introduction To Nanotechnology: 1.1 Nanotechnology - Definition and ExamplesDocument15 pagesIntroduction To Nanotechnology: 1.1 Nanotechnology - Definition and ExamplesMustafaNo ratings yet

- L7 Voltage Regulator, Half Wave Rectifier S2 1617Document20 pagesL7 Voltage Regulator, Half Wave Rectifier S2 1617Bhagyalaxmi patilNo ratings yet