Professional Documents

Culture Documents

A Speed Efficient RNS To Binary Converter For The Moduli Set

Uploaded by

Journal of ComputingOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Speed Efficient RNS To Binary Converter For The Moduli Set

Uploaded by

Journal of ComputingCopyright:

Available Formats

A Speed Efcient RNS to Binary Converter for

the Moduli set {2

n

, 2

n

+ 1, 2

n

1}

Edem Kwedzo Bankas, and Kazeem Alagbe Gbolagade.

Department of Computer Science, Faculty of Mathematical Sciences,

University for Development Studies,

Navrongo, Ghana

AbstractIn this paper, we present a novel high speed reverse converter for the moduli set {2

n

, 2

n

+ 1, 2

n

1}. The proposed

converter is obtained by simplifying the traditional Chinese Remainder Theorem. Just as in other state of the art converters, the

proposed converter is purely adder-based. Our proposal is approximately twice faster than the best known equivalent state of

the art reverse converter.

Index TermsAdder-based, Chinese Remainder Theorem, High Speed, Reverse Converter.

!

1 INTRODUCTION

R

ESIDUE Number System (RNS) is a number sys-

tem which supports carry free addition, borrow

free subtraction, and single step multiplication with-

out partial products. Furthermore, RNS is capable of

supporting high speed concurrent and independent

operations. In RNS, an integer is decomposed into

a set of small integers, called residues. On these

residues, concurrent and independent arithmetic op-

erations can be performed.

Moduli selection remains one of the major

challenges of RNS. This is because the speed and the

complexity of the resulting RNS architecture depends

on the chosen moduli set. Several moduli sets, e.g.,

{2

n

, 2

n

1, 2

n

+ 1} [4], [5], [8], [9],

_

2

n

, 2

n

1, 2

n+1

1

_

[10], [11], [12],

_

2

n

, 2

n

1, 2

n1

1

_

[7] have been proposed. The

moduli set {2

n

, 2

n

+ 1, 2

n

1} is the most popular

length three moduli set [13]. Several conversion

methods have been proposed for the moduli set

{2

n

, 2

n

+ 1, 2

n

1} [5], [8]. Some of these proposed

conversion methods use special formulae, others use

either the traditional Chinese Remainder Thoerem

(CRT), or the New CRT [9]. Andraos et al, 1988

employed compact form of multiplicative inverses

to simplify the CRT [5]. Based on similar principles,

Piestrak, 1995 presented an adder based reverse

converter, which is an improvement on Andraos

et al, 1988 [8]. Another area-delay efcient reverse

converter based on New CRT was presented in

[9]. All the converters presented in [5], [8], [9] are

for the moduli set {2

n

, 2

n

+ 1, 2

n

1}. The speed,

area, and the hardware complexity of the resulting

reverse converters proposed for the moduli set

{2

n

, 2

n

+ 1, 2

n

1} can be further reduced since

the moduli set supports several interesting number

theoretic properties.

In this paper, we propose a novel high

speed RNS reverse converter for the moduli set

{2

n

, 2

n

+ 1, 2

n

1}. First, the proposed reverse

converter is based on the simplication of the

traditional CRT. We simplify further the resulting

architecture in order to achieve a reverse converter

that utilizes only Carry Save Adders (CSAs) and

Carry Propagate Adders (CPAs). Theoretically

speaking, the proposed converter is faster than the

one in [9] with a higher area cost.

The rest of the paper is organized as follows. Section

2 provides a brief background information. In Section

3, the proposed algorithm is presented. Section 4

describes the hardware realization of the proposed

algorithm and Section 5 gives a performance compari-

son with the state of the art reverse converters. Finally,

the paper is concluded in Section 6.

2 BACKGROUND

RNS is dened by a set S of k integers that are

relatively prime. This set is known as the moduli

set {m

i

}

i=1,k

, where gcd(m

i

, m

j

) = 1 for i = j.

Here, gcd(m

i

, m

j

) stands for Greatest Common Di-

visor of m

i

and m

j

. The dynamic range M, is given

by M =

k

i=1

m

i

. Any weighted number X can be

represented in RNS as X = (x

1

, x

2

, ..., x

k

), where

x

i

= |X|

mi

representing x

i

= (Xmod m

i

); 0 x

i

<

m

i

, such a representation is unique for any integer

X [0, M 1].

For general purpose RNS processors to become

a reality, effective high speed data converters are

needed to convert numbers from binary-to-residue (B-

R) or residue-to-binary (R-B) representations. A high

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 83

speed B-R converter is required at the front end of

the system as well as a high speed R-B converter at

the back end. In this paper we concentrate on R-B

converters because many operations such as scaling,

magnitude comparison, division, and sign detection

invariably need conversion from R-B representations

[6].

Given a moduli set {m

i

}

i=1,k

, the residues

(x

1

, x

2

, ..., x

k

) can be converted into the corresponding

decimal number X in two general ways: First, by the

use of the well known CRT, which is given as [9]:

X =

i=1

m

i

M

1

i

mi

x

i

M

(1)

where M =

k

i=1

m

i

, M

i

=

M

mi

and M

1

i

is the

multiplicative inverse of M

i

with respect to (w.r.t)

m

i

.

Second, the Mixed Radix Conversion (MRC),

can be used. Suppose we have a residue number

representation (x

1

, x

2

, ..., x

k

) w.r.t the moduli set

{m

i

}

i=1,k

and Mixed Radix Digits (MRDs), {a

i

}

i=1,k

,

the decimal equivalent of the residues can be

computed as follows [13]:

X = a

1

+a

2

m

1

+a

3

m

1

m

2

+... +a

n

m

1

m

2

...m

k1

(2)

Where the MRDs are given as

a

1

= x

1

a

2

=

(x

2

a

1

)

m

1

1

m2

m2

a

3

=

((x

3

a

1

)

m

1

1

m2

a

2

)

m

1

2

m3

m3

.

.

.

a

k

=

(((x

k

a

1

)

m

1

1

m

k

a

2

)

m

1

2

m

k

...

a

k1

)

m

1

k1

m

k

m

k

(3)

The MRC method is a sequential algorithm as the

values of the MRDs are dependent on preceding

calculated values with the exception of a

1

. One advan-

tage of MRC is that it makes magnitude comparison

easy to perform and does not require large modulo M

as it is the case in the traditional CRT. However, CRT

is also desirable because computation can be paral-

lelized. This explains why many interesing converters

are based on CRT.

3 PROPOSED ALGORITHM

The proposed algorithm is formulated using the fol-

lowing theorems:

Theorem 1: Given the moduli set {m

1

, m

2

, m

3

} with

m

1

= 2

n

, m

2

= 2

n

+1, and m

3

= 2

n

1, the following

hold true:

|(m

2

m

3

)

1

|

m1

= 1, (4)

|(m

1

m

3

)

1

|

m2

= 2

n1

+ 1 =

m

1

2

+ 1, (5)

|(m

1

m

2

)

1

|

m3

= 2

n1

=

m

1

2

(6)

Proof: For (4) we have |1 (m

2

m

3

)|

m1

=

1 (2

2n

1)

2

n

= 1

For (5) we have

m1

2

+ 1 (m

1

m

3

)

m2

=

(2

n1

+ 1) (2

2n

2

n

)

2

n

+1

= 1

and for (6) we have

m1

2

(m

1

m

2

)

m3

=

2

n1

(2

2n

+ 2

n

)

2

n

1

= 1.

The following important relations are used in the

proof of the subsequent theorem: Given the moduli set

{m

1

, m

2

, m

3

} with m

1

= 2

n

, m

2

= 2

n

+1, m

3

= 2

n

1,

the following hold true:

m

3

= m

1

1, (7)

m

2

= m

1

+ 1, (8)

m

2

= m

3

+ 2, (9)

m

1

m

2

= m

1

m

3

+ 2m

1

(10)

Theorem 2: The decimal equivalent of the RNS

number (x

1

, x

2

, x

3

) with respect to the moduli set

{m

1

= 2

n

, m

2

= 2

n

+ 1, m

3

= 2

n

1} is computed as

follows:

X = m

1

_

X

m

1

_

+x

1

(11)

where

_

X

m1

_

= |u

1

+u

2

+u

3

|

m2m3

, u

1

=

(

1

m1

m

2

+1)x

1

, u

2

= (

m1m2

2

1)x

2

and u

3

=

m1m2

2

x

3

Proof: The traditional CRT (1) [11] for n = 3 is

given by:

X =

M

1

M

1

1

m1

x

1

+

M

2

M

1

2

m2

x

2

+M

3

M

1

3

m3

x

3

M

(12)

substituting (4), (5), (6) in (12) and applying expres-

sions of M

1

, M

2

, and M

3

we obtain:

X =

m

2

m

3

x

1

+

m

1

m

1

m

3

x

2

2

+

m

1

m

3

x

2

+

(m

1

m

3

+ 2m

1

)(m

1

x

3

)

2

M

(13)

substituting (7), (8) and (9) into (13) and then simpli-

fying, we obtain:

X =

m

1

m

2

(x

1

+

m

3

x

2

2

+x

2

+

m

3

x

3

2

) +

m

1

m

2

x

3

m

1

m

3

x

2

2

m

1

m

3

x

3

2

2m

1

x

2

|m

1

x

3

+m

2

x

1

|

M

(14)

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 84

X =

m

1

m

2

[

m

3

2

(x

2

+x

3

) + (x

2

x

1

)] +m

1

m

2

x

3

+

m

2

x

1

m(x

3

+ 2x

2

)

(m

1

m

3

)(x

2

+x

3

)

2

M

(15)

substituting m

1

m

3

in (10) into (15) and re-arranging

we obtain:

X =

m

1

m

2

[

m

3

2

(x

2

+x

3

) +

x

2

+x

3

2

x

1

] +

|m

1

(x

2

+x

3

) m

1

(x

3

+ 2x

2

) +m

2

x

1

)|

M

(16)

further simplication gives:

X =

m

1

m

2

[

m

3

2

(x

2

+x

3

) +

x

2

+x

3

2

x

1

] +

|m

2

x

1

m

1

x

2

|

m1m2m3

(17)

replacing the expression m

2

x

1

m

1

x

2

in (17) by

m

1

(x

1

x

2

) +x

1

we obtain:

X =

m

1

m

2

[

m

3

2

(x

2

+x

3

) +

x

2

+x

3

2

x

1

] +

|m

1

(x

1

x

2

) +x

1

|

m1m2m3

(18)

Dividing both sides of the above equation by m

1

and taking the oor, we have:

_

X

m

1

_

=

m

2

[

m

3

2

(x

2

+x

3

) +

x

2

+x

3

2

x

1

] +

x

1

x

2

+

x

1

m

1

m2m3

(19)

further simplication gives:

_

X

m

1

_

=

(

1

m

1

m

2

+ 1)x

1

+ (

m

1

m

2

2

1)x

2

+

m

1

m

2

2

x

3

m2m3

(20)

Let u

1

= (

1

m1

m

2

+ 1)x

1

, u

2

= (

m1m2

2

1)x

2

and

u

3

=

m1m2

2

x

3

_

X

m

1

_

= |u

1

+u

2

+u

3

|

m2m3

(21)

We nally obtain:

X = m

1

_

X

m

1

_

+x

1

(22)

In order to reduce the hardware complexity, we use

the following properties as in [11] to simplify (22)

Property 1: The multiplication of a residue number

by 2

k

in modulo (2

p

1) is computed by k bit circular

left shifting

Property 2: A negative number in modulo (2

p

1)

is calculated by subtracting the number in question

from (2

p

1). In binary representation, the ones

complement of the number gives the result.

Let the residues (x

1

, x

2

, x

3

) have binary representa-

tion as follows:

x

1

= (x

1,n1

x

1,n2

...x

1,1

x

1,0

. .

n

) (23)

x

2

= (x

2,n

x

2,n1

...x

2,1

x

2,0

. .

n+1

) (24)

x

3

= (x

3,n1

x

3,n2

...x

3,1

x

3,0

. .

n

) (25)

Evaluating u

1

u

1

=

(

1

2

n

(2

n

+ 1) + 1)x

1

2

2n

1

. We evaluate the

four parts of u

1

separately using property 1 and

property 2 where applicable:

u

11

=

1

2

n

x

1

2

2n

1

=

n

..

00...00 . x

1,n1

...x

1,0

. .

n

(26)

u

12

= |2

n

x

1

|

2

2n

1

=

n

..

x

1,n1

x

1,n2

...x

1,1

x

1,0

11..11

. .

n

(27)

u

13

= |x

1

|

2

2n

1

=

n

..

11...11 x

1,n1

x

1,n2

...x

1,1

x

1,0

. .

n

(28)

u

14

= |x

1

|

2

2n

1

=

n

..

00...00 x

1,n1

x

1,n2

...x

1,1

x

1,0

. .

n

(29)

Therefore by adding equation (26) through to (29),

we have the value of u

1

. However, u

11

could be

ignored because it is approximately zero as the oor

function makes it negligible. Considering u

12

and

u

14

, the n leftmost bit of u

14

are zeros, and the n

rightmost bit of u

12

are ones. By adding u

12

and u

14

we obtain u

1

, where denotes OR:

u

1

=

n

..

x

1,n1

x

1,n2

...x

1,1

x

1,0

1 x

1,n1

1 x

1,n2

...1 x

1,0

. .

n

(30)

Evaluating u

2

u

2

=

(

2

2n

+2

n

2

1)x

2

2

2n

1

=

2

2n1

x

2

+ 2

n1

x

2

x

2

2

2n

1

We evaluate the three parts of u

2

separately using

property 1 and property 2 where applicable as fol-

lows:

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 85

u

21

=

2

2n1

x

2

2

2n

1

= x

2,0

n1

..

00...00 x

2,n

x

2,n1

...x

2,1

. .

n

(31)

u

22

=

2

n1

x

2

2

2n

1

=

n+1

..

x

2,n

x

2,n1

...x

2,1

x

2,0

00...00

. .

n1

(32)

u

23

= x

2

=

n1

..

11...11 x

2,n

x

2,n1

...x

2,1

x

2,0

. .

n+1

(33)

Again, by considering u

21

and u

22

, we manipulate

them using the n 1 zero bits in each to obtain u

2

u

2

= x

2,0

x

2,n

x

2,n1

...x

2,1

. .

n1

x

2,0

x

2,n

x

2,n1

...x

2,1

x

2,0

. .

n1

(34)

Evaluating u

3

u

3

=

(

2

2n

+2

n

2

)x

3

2

2n

1

=

(2

2n1

x

3

+ 2

n1

x

3

)

2

2n

1

Again we evaluate the two parts of u

3

separately as

follows:

u

31

=

2

2n1

x

3

2

2n

1

= x

3,0

n

..

00...00 x

3,n1

x

3,n2

...x

3,1

. .

n1

(35)

u

32

=

2

n1

x

3

2

2n

1

= 0

n

..

x

3,n1

...x

3,1

x

3,0

00...00

. .

n1

(36)

From the above, we manipulate u

31

and u

32

to

obtain:

u

3

=

n+1

..

x

3,0

x

3,n1

...x

3,1

x

3,0

x

3,n1

x

3,n2

...x

3,1

. .

n1

(37)

Now it is convenient to express the sum of all the

binary strings given by (27) - (37). Let

_

X

m1

_

= .

=

1

+u

13

+u

3

+u

2

+u

23

2

2n

1

(38)

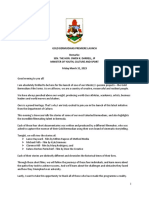

4 HARDWARE REALIZATION

The hardware structure of the proposed reverse con-

verter is based on (22) and (38). Calculation of the

operands of requires 3n inverters. Since u

13

and

u

23

both have n bits of 1s, two full adders FAs in

the Carry Save Adder (CSA) with End arround Carry

(EAC) are reduced to two half adders (HAs). The ve

2n bit numbers are summed up modulo (2

2n

1). This

requires three levels of 2n CSAs with EAC, followed

by a 2n bit Carry Propagate Adder (CPA) with a carry-

in of 1. It is important to note that, n and n 1

most signicant bits of two operands that always

have inputs equal to 1. This in anticipation will result

in a nal ones complement adder that generates an

end-around carry with the ones complement adder

reduced to a normal CPA with a constant carry-in of

1.This therefore makes the delay tCPA(2n). Since x

1

is an n-bit number, the computation of (22) requires no

additional hardware as the desired result is obtained

by concatenating x

1

with . Figure 1 below depicts

the structutre of the proposed hardware.

5 PERFORMANCE ANALYSIS

In this section, we evaluate the performance of

the proposed RNS to binary high speed converter

with the best state of the art equivalent converter

proposed in [9]. As outlined in the previous section,

we sum up ve 2n bit numbers u

1

, u

13

, u

3

, u

2

,

and u

23

modulo (2

2n

1). For this reason, three

CSAs with EAC which include 8n FAs is sufcient.

However, considering the operands, some of these

FAs can be reduced to HAs. The CSA with EAC has

an inverter level for all operands, so the inversions

in u

1

, u

13

and u

23

are executed in both CSA1 with

EAC and CSA2 with EAC. From (28), (30), and (37),

n of the FAs in CSA1 is reduced to n HAs . This

means that CSA1 with EAC consist of n FA and n

HAs. Also, since (34) has 2 bits of XNOR/OR, 2n

FAs are reduced to (2n 2) FAs in CSA2 with EAC.

Then in CSA3 with EAC, we have (n 1) bit of 1s,

reducing 2n FAs to n + 1 FAs. The 2n bit modulo

adder has an approximate complexity of 2n FA and

an approximate delay of (2n)t

FA

, where t

FA

is the

delay of one FA. Table1 presents the characteristics of

each part of the proposed reverse converter in terms

of FA and HA where the complexity of XNOR/OR

are considered as HA for simplicity sake.

Table 1. Hardware Requirement of the converter

Components Full Adder Half Adder

CSA1 n n

CSA2 2n 2 2

CSA3 n + 1 n 1

CPA 2n 0

Total 6n 1 2n + 1

The hardware architecture of the proposed reverse

converter consists of (6n 1) FAs and (2n + 1) HAs.

The delay of a CSA is the same as that of a FA, so

the proposed converter has a total delay of (3t

FA

+

t

CPA(2n)

+t

inv

). Table 2 compares the performance of

our proposal with the state of the art reverse converter

in [9]. The result of this comparison is shown in Table

2.

The data for converters presented in [14], [5], [15],

[8] and [9] given in Table 2 are obtained from [9, Table

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 86

u1 u13 u3

u23

s1 c1

s2 c2

s3 c3

u2

CSA 1 with EAC

2n bit

CPA

2n bit

CSA 2 with EAC

2n bit

CSA 3 with EAC

2n bit

1

X

Figure 1: Proposed hardware Structure

I]. In summary, it is evident from the table that the

proposed converter is faster than the converters in

[14], [5], [15], [8] and [9], while requiring higher area

cost.

6 CONCLUSIONS

In this paper, a novel high speed reverse converter for

the moduli set

{2

n

, 2

n

+ 1, 2

n

1} has been proposed. The resulting

architecture was further reduced to obtain a R-B con-

verter that utilizes only CSAs and CPA with a carry-in

of 1. The proposed converter have been demonstrated

to have high speed capability than equivalent state of

the art converters.

REFERENCES

[1] N.S. Szabo and R.I Tanaka. Residue Arithmetic and its Applications

to Computer Technology, MCGraw Hill, New York, 1967.

[2] B. Vinnakota and V.V. Bapeswara Rao. Fast Conversion Techniques

for Binary- Residue Number System, IEEE Trans. Circuit and Sys-

tems. IEEE Trans. Circuits Syst I, Vol. 41, No. 12, pp.927929. Dec,

1994.

[3] Y. Wang. Residue-to-Binary converters based on New Chinese Re-

mainder Theorems. IEEE Trans. Circuit and Systems II, pp. 197-206.

May, 2008.

[4] S. Bi., W Wang and A. Al-Khalili. Modulo Deation in (2

n

+

1, 2

n

, 2

n

1) Converters, Proc. IEEE International Symposium on

Circuits and Systems (ISCAS 2004), Vol. 2, pp. 429-432.

[5] S. Andraos and H. Ahmad A New Efcient Memoryless Residue to

Binary Converter, IEEE Trans. Circuits Syst., vol. 35, Pp. 1441-1444.

1988.

[6] P.V. Ananda Mohan. Reverse Converters for A New Moduli Set

(2

2n

1, 2

n

, 2

2n

+1), Circuits Systems Signal Processing, Vol. 26,

No. 2, pp.215227. 2007.

[7] M. Hosseinzadeh, A.S. Molahosseini and K. Navi. A Paral-

lel Implementation of the Reverse Converter for the Moduli Set

_

2

n

, 2

n

1, 2

n1

1

_

, World Academy of Science , Engineering

and Technology., Vol. 55, pp.494498. 2009.

[8] S.J. Piestrak. A High Speed Realization of a Residue to Binary Num-

ber System Converter, IEEE Transactions on Circuits and Systems

-II: Analog and Digital Signal Processing, Vol. 42 No. 10 , pp.661

663. 1995

[9] Y. Wang, X. Song, M. Aboulhamid and H. Shen. Adder Based

Residue to Binary Number Converters for (2

n

1, 2

n

, 2

n

+ 1),

IEEE Transactions on Processing, Vol. 50, pp.17721779. 2002.

[10] S. Lin, M. Sheu, and C. Wang. Efcient VLSI Design of Residue-

to-Binary Converter for the Moduli Set (2

n

, 2

n+1

1, 2

n

1),

IEICE Trans. Inf. and Syst., Vol. E91-D, No 7 pp.20502060. 2008.

[11] K.A. Gbolagade, G.R. Voicu, and S.D. Cotofana. Memoryless

RNS to Binary Converters for the (2

n+1

1, 2

n

, 2

n

1), IEEE

International Conference on Application Specic Systems, Architec-

tures, and Processors (ASAP 2010), pp.301304, Rennes, France.

2010.

[12] P.V.A. Mohan. RNS-To-Binary Converter for a New Three-Moduli

set (2

n+1

1, 2

n

, 2

n

1), IEEE Transactions on Circuits and

Systems -II, Vol. 54, No. 9 . pp. 775-779. 2007.

[13] W. Wang, M.N.S. Swamy, M.O. Ahmad, and Y. Wang A study

of the residue -to-binary converters for the three moduli sets, IEEE

Trans. Circuits Syst. I, Fundam. Theory Appl, Vol. 50, No. 2, pp.235

243. 2003.

[14] K. Ibrahim, and S. Saloum An efcient residue to binary number

converter design, IEEE Trans. Circuits Syst, Vol. 35, pp.11561158.

1988.

[15] M. Bhardwaj, A.B. Premkumah, and T. Srikanthan. Breaking

the 2n bit carry propagate barrier in residue to binary conversion

for (2

n

1, 2

n

, 2

n

+ 1) moduli set, IEEE Trans. Circuit Syst. II,

Vol. 45,pp. 998-1009. 1988

[16] K.A. Gbolagade,R. Chaves, L. Sousa, and S.D. Cotofana. An

Improved RNS Reverse Converter for (2

2n+1

1, 2

n

, 2

n

1)

moduli set, IEEE International Symposium on Circuits and Systems

(ISCAS 2010), pp.21032106, Paris, France. June, 2010.

Edem Kwedzo Bankas received the B.Ed degree in Mathematics

from the University of Education, Winneba, Ghana. He obtained

M.Ed degree in Computer Education and Technology from Ohio

University, USA. He is currently working towards the Ph.D degree.

His research is in the area of Residue Number Systems. He is a

Lecturer at the Computer Science Department of the University for

Development Studies, Navrongo, Ghana.

Kazeem Alagbe Gbolagade received his PhD in Computer Engi-

neering from the Delft University of Technology in the Netherlands.

He obtained his M.Sc and B.Sc in Computer Science from the

University of Ibadan and Ilorin, respectively, in Nigeria. Presently,

he is a senior lecturer and the Dean of Faculty of Mathematical

Sciences, University for Development Studies, Navrongo, Ghana.

He has worked as a visiting researcher at the Technical University

of Lisbon in Portugal. His research interests include Digital Logic

Design, Computer Arithmetic, Residue Number Systems, and VLSI

Design.

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 87

Table 2. Hardware Complexity Comparison

Converter FA AND/OR XOR/XNOR CLAs-2n Delay

[14] 6n - n + 1 2 2t

CPA(n)

+ 2t

CPA(2n)

+ 2t

XOR

[5] 6n 4n 2 2n 1 3t

CPA(2n)

+ 2t

XOR

+log(2n) t

AND

[15] 6n n + 3 n + 1 1 2t

FA

+t

inv

+t

CPA(2n)

+t

MUX

[8] 4n 2n 1 2n 1 2t

FA

+t

inv

+ 2t

CPA(2n)

+ 3t

MUX

[9] 2n - 1 1 t

inv

+t

MUX

+t

FA

+ 2t

CPA(2n)

proposed 6n 1 - 2n + 1 - 3t

FA

+t

CPA(2n)

+t

inv

JOURNAL OF COMPUTING, VOLUME 4, ISSUE 5, MAY 2012, ISSN 2151-9617

https://sites.google.com/site/journalofcomputing

WWW.JOURNALOFCOMPUTING.ORG 88

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Google Cloud Sales Credential 1Document7 pagesGoogle Cloud Sales Credential 1Gaurav Nanda100% (1)

- Action Plan 2019-2020 (English)Document2 pagesAction Plan 2019-2020 (English)Ian Batocabe100% (8)

- Social Work Practice and Social Welfare Policy in The United States A History (Philip R. Popple)Document393 pagesSocial Work Practice and Social Welfare Policy in The United States A History (Philip R. Popple)5819Elis RahmawatiNo ratings yet

- Idiosyncratic Dialects and Error AnalysisDocument8 pagesIdiosyncratic Dialects and Error AnalysisEdwarNo ratings yet

- Complex Event Processing - A SurveyDocument7 pagesComplex Event Processing - A SurveyJournal of ComputingNo ratings yet

- Mobile Search Engine Optimization (Mobile SEO) : Optimizing Websites For Mobile DevicesDocument5 pagesMobile Search Engine Optimization (Mobile SEO) : Optimizing Websites For Mobile DevicesJournal of ComputingNo ratings yet

- Business Process: The Model and The RealityDocument4 pagesBusiness Process: The Model and The RealityJournal of ComputingNo ratings yet

- Applying A Natural Intelligence Pattern in Cognitive RobotsDocument6 pagesApplying A Natural Intelligence Pattern in Cognitive RobotsJournal of Computing100% (1)

- A Compact Priority Based Architecture Designed and Simulated For Data Sharing Based On Reconfigurable ComputingDocument4 pagesA Compact Priority Based Architecture Designed and Simulated For Data Sharing Based On Reconfigurable ComputingJournal of ComputingNo ratings yet

- Hybrid Network Coding Peer-to-Peer Content DistributionDocument10 pagesHybrid Network Coding Peer-to-Peer Content DistributionJournal of ComputingNo ratings yet

- Exploring Leadership Role in GSD: Potential Contribution To An Overall Knowledge Management StrategyDocument7 pagesExploring Leadership Role in GSD: Potential Contribution To An Overall Knowledge Management StrategyJournal of ComputingNo ratings yet

- Product Lifecycle Management Advantages and ApproachDocument4 pagesProduct Lifecycle Management Advantages and ApproachJournal of ComputingNo ratings yet

- Using Case-Based Decision Support Systems For Accounting Choices (CBDSS) : An Experimental InvestigationDocument8 pagesUsing Case-Based Decision Support Systems For Accounting Choices (CBDSS) : An Experimental InvestigationJournal of ComputingNo ratings yet

- Image Retrival of Domain Name System Space Adjustment TechniqueDocument5 pagesImage Retrival of Domain Name System Space Adjustment TechniqueJournal of ComputingNo ratings yet

- Divide and Conquer For Convex HullDocument8 pagesDivide and Conquer For Convex HullJournal of Computing100% (1)

- Towards A Well-Secured Electronic Health Record in The Health CloudDocument5 pagesTowards A Well-Secured Electronic Health Record in The Health CloudJournal of Computing0% (1)

- Analytical Study of AHP and Fuzzy AHP TechniquesDocument4 pagesAnalytical Study of AHP and Fuzzy AHP TechniquesJournal of ComputingNo ratings yet

- Decision Support Model For Selection of Location Urban Green Public Open SpaceDocument6 pagesDecision Support Model For Selection of Location Urban Green Public Open SpaceJournal of Computing100% (1)

- Application of DSmT-ICM With Adaptive Decision Rule To Supervised Classification in Multisource Remote SensingDocument11 pagesApplication of DSmT-ICM With Adaptive Decision Rule To Supervised Classification in Multisource Remote SensingJournal of ComputingNo ratings yet

- Detection and Estimation of Multiple Far-Field Primary Users Using Sensor Array in Cognitive Radio NetworksDocument8 pagesDetection and Estimation of Multiple Far-Field Primary Users Using Sensor Array in Cognitive Radio NetworksJournal of ComputingNo ratings yet

- QoS Aware Web Services Recommendations FrameworkDocument7 pagesQoS Aware Web Services Recommendations FrameworkJournal of ComputingNo ratings yet

- Predicting Consumers Intention To Adopt M-Commerce Services: An Empirical Study in The Indian ContextDocument10 pagesPredicting Consumers Intention To Adopt M-Commerce Services: An Empirical Study in The Indian ContextJournal of ComputingNo ratings yet

- Hiding Image in Image by Five Modulus Method For Image SteganographyDocument5 pagesHiding Image in Image by Five Modulus Method For Image SteganographyJournal of Computing100% (1)

- Real-Time Markerless Square-ROI Recognition Based On Contour-Corner For Breast AugmentationDocument6 pagesReal-Time Markerless Square-ROI Recognition Based On Contour-Corner For Breast AugmentationJournal of ComputingNo ratings yet

- Secure, Robust, and High Quality DWT Domain Audio Watermarking Algorithm With Binary ImageDocument6 pagesSecure, Robust, and High Quality DWT Domain Audio Watermarking Algorithm With Binary ImageJournal of ComputingNo ratings yet

- K-Means Clustering and Affinity Clustering Based On Heterogeneous Transfer LearningDocument7 pagesK-Means Clustering and Affinity Clustering Based On Heterogeneous Transfer LearningJournal of ComputingNo ratings yet

- Impact of Facebook Usage On The Academic Grades: A Case StudyDocument5 pagesImpact of Facebook Usage On The Academic Grades: A Case StudyJournal of Computing100% (1)

- Energy Efficient Routing Protocol Using Local Mobile Agent For Large Scale WSNsDocument6 pagesEnergy Efficient Routing Protocol Using Local Mobile Agent For Large Scale WSNsJournal of ComputingNo ratings yet

- Combining Shape Moments Features For Improving The Retrieval PerformanceDocument8 pagesCombining Shape Moments Features For Improving The Retrieval PerformanceJournal of ComputingNo ratings yet

- Detection of Retinal Blood Vessel Using Kirsch AlgorithmDocument4 pagesDetection of Retinal Blood Vessel Using Kirsch AlgorithmJournal of ComputingNo ratings yet

- Impact of Software Project Uncertainties Over Effort Estimation and Their Removal by Validating Modified General Regression Neural Network ModelDocument6 pagesImpact of Software Project Uncertainties Over Effort Estimation and Their Removal by Validating Modified General Regression Neural Network ModelJournal of ComputingNo ratings yet

- When Do Refactoring Tools Fall ShortDocument8 pagesWhen Do Refactoring Tools Fall ShortJournal of ComputingNo ratings yet

- Arabic Documents Classification Using Fuzzy R.B.F Classifier With Sliding WindowDocument5 pagesArabic Documents Classification Using Fuzzy R.B.F Classifier With Sliding WindowJournal of ComputingNo ratings yet

- Prioritization of Detected Intrusion in Biometric Template Storage For Prevention Using Neuro-Fuzzy ApproachDocument9 pagesPrioritization of Detected Intrusion in Biometric Template Storage For Prevention Using Neuro-Fuzzy ApproachJournal of ComputingNo ratings yet

- Computer Vision Cover LetterDocument6 pagesComputer Vision Cover Letterpenebef0kyh3100% (2)

- Communicating in BusinessDocument9 pagesCommunicating in BusinessDrEi Shwesin HtunNo ratings yet

- Final PPT For Map SkillsDocument72 pagesFinal PPT For Map SkillsjahnavikidambiNo ratings yet

- Monitoring and Supervision Tool (M&S) For TeachersDocument3 pagesMonitoring and Supervision Tool (M&S) For TeachersJhanice Deniega EnconadoNo ratings yet

- CapstoneDocument6 pagesCapstoneJulius TenidoNo ratings yet

- How To Use The Alberta K 12 Esl Proficiency BenchmarksDocument9 pagesHow To Use The Alberta K 12 Esl Proficiency Benchmarksapi-301199075No ratings yet

- Classroom Management: Some Times It Feels Like We Are Herding CatsDocument22 pagesClassroom Management: Some Times It Feels Like We Are Herding CatsAhmad SherNo ratings yet

- Day9 Master ThesisDocument4 pagesDay9 Master Thesisvickiewesternelgin100% (2)

- Principles of EconomicsDocument20 pagesPrinciples of EconomicsRonald QuintoNo ratings yet

- Powerpoint Presentation For BarkadahanDocument27 pagesPowerpoint Presentation For BarkadahanAmaiNo ratings yet

- Project Management (PM)Document4 pagesProject Management (PM)N-aineel DesaiNo ratings yet

- International Journal of Trend in Scientific Research and Development (IJTSRD)Document8 pagesInternational Journal of Trend in Scientific Research and Development (IJTSRD)Editor IJTSRDNo ratings yet

- HBO MotivationDocument16 pagesHBO MotivationFrancis Elaine FortunNo ratings yet

- ACM SIGGRAPH Annual Report July 2020 To June 2021 Fiscal Year 2021Document48 pagesACM SIGGRAPH Annual Report July 2020 To June 2021 Fiscal Year 2021CarrieNo ratings yet

- Dalcroze LessonDocument2 pagesDalcroze Lessonapi-531830348No ratings yet

- Fifty Years of Supporting Parapsychology - The Parapsychology Foundation (1951-2001)Document27 pagesFifty Years of Supporting Parapsychology - The Parapsychology Foundation (1951-2001)Pixel PerfectNo ratings yet

- Bulgaria Lesson Plan After LTT in SpainDocument3 pagesBulgaria Lesson Plan After LTT in Spainapi-423847502No ratings yet

- SecA - Group1 - Can Nice Guys Finish FirstDocument18 pagesSecA - Group1 - Can Nice Guys Finish FirstVijay KrishnanNo ratings yet

- 11-Foundations of GMAT VerbalDocument35 pages11-Foundations of GMAT VerbalDroea Intimates100% (1)

- Lesson Plan English Year 5Document8 pagesLesson Plan English Year 5NurAiniNasirNo ratings yet

- Test 2Document7 pagesTest 2muhammad_muhammadshoaib_shoaibNo ratings yet

- Minister Darrell - Gold Bermudians RemarksDocument2 pagesMinister Darrell - Gold Bermudians RemarksBernewsAdminNo ratings yet

- Eteeap Application Form Pangasinan State UDocument1 pageEteeap Application Form Pangasinan State UMarcial Jr. MilitanteNo ratings yet

- Toptal Alternatives and Competitors To Hire DevelopersDocument18 pagesToptal Alternatives and Competitors To Hire DevelopersJansser CostaNo ratings yet

- Institute of Professional Psychology Bahria University Karachi CampusDocument16 pagesInstitute of Professional Psychology Bahria University Karachi Campusayan khwajaNo ratings yet

- Appointment Processing ChecklistDocument2 pagesAppointment Processing ChecklistGlorious El Domine100% (1)