Professional Documents

Culture Documents

Decode 5 To 32

Uploaded by

Doan Thanh Thien0 ratings0% found this document useful (0 votes)

276 views7 pagesConstruct a 5-to-32 decoder using only 2-to-4 decoders and 3-to-8 decoder. Design a 32-to-1 multiplexer using only 8-to+1 multiplexer. Use block diagram for the components.

Original Description:

Original Title

decode 5 to 32

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentConstruct a 5-to-32 decoder using only 2-to-4 decoders and 3-to-8 decoder. Design a 32-to-1 multiplexer using only 8-to+1 multiplexer. Use block diagram for the components.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

276 views7 pagesDecode 5 To 32

Uploaded by

Doan Thanh ThienConstruct a 5-to-32 decoder using only 2-to-4 decoders and 3-to-8 decoder. Design a 32-to-1 multiplexer using only 8-to+1 multiplexer. Use block diagram for the components.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 7

HOMEWORK 4 Solution

ICS 151 Digital Logic Design

Spring 2004

1. Decoder/Multiplexer combining

a. Construct a 5-to-32 decoder using only 2-to-4 decoders and 3-to-8 decoders

(with enable).

b. Design a 32-to-1 multiplexer using only 8-to-1 multiplexer.

Use block diagram for the components.

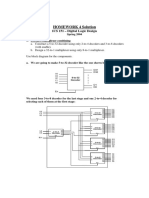

a. We are going to make 5-to-32 decoder like the one shown below:

We need four 3-to-8 decoder for the last stage and one 2-to-4 decoder for

selecting each of them at the first stage:

b. We use four 8-to-1 in the first stage and another one to select between the

output of the others:

2. Function implementation using Multiplexer

Realize the following functions:

f

1

(x,y,z) = m(0,2,3,5,7)

f

2

(x,y,z) = y+z

We need to have the minterm lists for both f1 and f2. For f1 we have it, for f2

we can reach to it by usning truth table or minterm expansion, we will use

truth table for now:

x y z f

2

0 0 0 1

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 0

1 1 1 1

So f2 = m (0, 1, 2, 3, 4, 5, 7)

a. Using only 8-to-1 multiplexer

For each of f1 and f2 we need 1 8-to-1 multiplexer:

b. Using one 3-to-8 decoder and two-input gates (INV, AND, OR, NAND, NOR, XOR)

For implementing f1and f2 using decoder we need only one decoder, because we can

share the decoder outputs.

And also because the number of 1s are more than the number of 0s for both of the

functions, its better to use INV-AND to make the functions, so:

We first derive the left diagram and then from there we will reach to the right digram

by replacing INV-ANDs with NORs.

3. Combinational Multiplier Design

Design a binary multiplier that multiplies two 4-bit unsigned binary numbers. Use

AND gates and full adder only.

Imagine that we want to multiply x3x2x1x0 by y3y2y1y0, for this multiplier we need to

make a circuit that do the multiplication like below:

x3y0 x2y0 x1y0 x0y0

x3y1 x2y1 x1y1 x0y1

x3y2 x2y2 x1y2 x0y2

x3y3 x2y3 x1y3 x0y3

P7 P6 P5 P4 P3 P2 P1 P0

All the ANDed sentences in each column should be added. So We need 16 2 input AND

gates and 12 FAs to add all the columns. So, this is the final circuit:

Module-based Design

Imagine that we have these two modules ready to use:

1) BCD adder

2) 9s complement circuit

The block diagrams for these modules are shown below: (A, B, S are all BCD digits)

BCD Adder

A[3:0] B[3:0]

S[3:0] Cout

9's complement

A[3:0]

S[3:0]

Cin

For example if A=1001 (BCD of decimal 9) and B=0101 (BCD of decimal 5) then

the outputs from BCD Adder will be C

out

=1 and S = 0100 (1 0100 is BCD of decimal

14).

And if A=0111 then the output from 9s complement will be S=0010

Now we want to use the aforementioned modules to:

Design a 4-digit BCD adder-subtractor using four BCD adders (as shown above) and

four 9s complement circuit (as shown above) and multiplexers. Your circuit has 3 set of

inputs:

1) X

3

X

2

X

1

X

0

(4-digit BCD input; for example 4896 or 0100 1000 1001 0110)

2) Y

3

Y

2

Y

1

Y

0

(4-digit BCD input; for example 1267 or 0001 0010 0110 0111)

3) M (mode input; M=0 means add and M=1 means subtract)

And it has two sets of outputs:

1) Z

3

Z

2

Z

1

Z

0

(4-digit BCD output showing the result of the add or subtract; for

example the result of the add will be 6163 or 0110 0001 0110 0011 and the

result of the subtract will be 3629 or 0011 0110 0010 1001 for the above

examples)

2) C

out

(Carry output)

Use block diagrams for each component, showing only inputs and outputs.

The design of 4-digit BCD adder/subtractor is almost the same as the design of 4 bit

adder/subtractor. In case of the adder we should just add the 4 BCD digits using the

4 BCD adders that we have. For the subtraction we need to add the first number

and the 9s complement and 1. Four 9s complements modules used for generating

the 9s complement of the 4 BCD digits and the carry in of the first stage is used to

feed the 1 that we need during the subtraction, so we can connect it to mode (M)

input.

And finally we need 4 quadruple 2-to-1 multiplexers to select between the second

variable and its 9s complement for addition and subtraction. The select line will be

connected to mode (M). Each of these quadruple 2-to-1 multiplexers is consisting of

four 2-to-1 multiplexers that have a shared select line. The final design block

diagram is given below:

You might also like

- HOMEWORK 4 Solution: ICS 151 - Digital Logic DesignDocument7 pagesHOMEWORK 4 Solution: ICS 151 - Digital Logic DesignNur Amiera SyuhadhaNo ratings yet

- Tutorial 4 - 1Document7 pagesTutorial 4 - 1YONIWO EDWARD TSEMINo ratings yet

- DLD BankDocument16 pagesDLD BankHarshad ThiteNo ratings yet

- DDL 06Document8 pagesDDL 06Anonymous KLGejaVNo ratings yet

- CH 4 ALU and Floating Point ArithmeticDocument12 pagesCH 4 ALU and Floating Point ArithmeticbokadashNo ratings yet

- Problems-Chapter-8-ConceptsDocument2 pagesProblems-Chapter-8-ConceptsNguyen Huu Duc ThoNo ratings yet

- Implement 16x1 Multiplexer Circuit in MultisimDocument51 pagesImplement 16x1 Multiplexer Circuit in MultisimVikasNo ratings yet

- 2-Bit Multiplier M B A: Don't Worry About This Question Because This Particular Method Was Not Presented in ClassDocument8 pages2-Bit Multiplier M B A: Don't Worry About This Question Because This Particular Method Was Not Presented in ClassMarlon BoucaudNo ratings yet

- DCS Assignment 1Document5 pagesDCS Assignment 1Aayush JainNo ratings yet

- UntitledDocument5 pagesUntitlediijjgwelNo ratings yet

- 7 Segment Display GuideDocument12 pages7 Segment Display Guidehieu minh TranNo ratings yet

- Chapter 3 - Encoder, DecoderDocument39 pagesChapter 3 - Encoder, Decodernizar_ayub95No ratings yet

- Digital Circuit Design and Combinational Logic CircuitsDocument6 pagesDigital Circuit Design and Combinational Logic CircuitsRizaldy Pahlevi Bin JamaluddinNo ratings yet

- Problem Set 1Document4 pagesProblem Set 1Pradyumn PaliwalNo ratings yet

- Practice Problems 1Document34 pagesPractice Problems 1akbisoi1No ratings yet

- How Adders and Decoders Work in Digital CircuitsDocument42 pagesHow Adders and Decoders Work in Digital CircuitsAhmad IzzuddinNo ratings yet

- Chapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageDocument12 pagesChapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageRahul SinghNo ratings yet

- Applications of Combinational Circuits - Edited 2020Document26 pagesApplications of Combinational Circuits - Edited 2020Matthew LewisNo ratings yet

- Chapter 3 - Combinational Logic DesignDocument36 pagesChapter 3 - Combinational Logic Designmahbub mitulNo ratings yet

- Mod 1 2Document20 pagesMod 1 2Naseef RahmanNo ratings yet

- B38DB ClassExs2sDocument33 pagesB38DB ClassExs2sNabil IshamNo ratings yet

- Digital Logic Circuit Design Combinational Logic Circuits Test QuestionsDocument12 pagesDigital Logic Circuit Design Combinational Logic Circuits Test Questionspavithra.jNo ratings yet

- Bcd to 7 SegmentDocument8 pagesBcd to 7 Segmentbalakasriram123No ratings yet

- Digital Design Assignment 40%Document2 pagesDigital Design Assignment 40%Obada Ar-ruzziNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- Logic Design / Digital Logic (Assignment 2) Due Date: 24.10.2017 (Tuesday)Document2 pagesLogic Design / Digital Logic (Assignment 2) Due Date: 24.10.2017 (Tuesday)Sabyasachi mishraNo ratings yet

- Basic Digital Logic Design Notes PDFDocument138 pagesBasic Digital Logic Design Notes PDFnandamsNo ratings yet

- Unit 3Document58 pagesUnit 3Anji ReddyNo ratings yet

- Question Bank: Ec6302 Digital ElectronicsDocument14 pagesQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNo ratings yet

- DecoderDocument6 pagesDecoderAparajitha Narayanan0% (1)

- MSI Devices 2021 L 21 - 24Document48 pagesMSI Devices 2021 L 21 - 24Nethmi LokusuriyaNo ratings yet

- CEG 2131 - Fall 2003 - FinalDocument14 pagesCEG 2131 - Fall 2003 - FinalAmin DhouibNo ratings yet

- D L C Question BankDocument11 pagesD L C Question BankLeka AmuNo ratings yet

- Digital Logic CircuitsDocument15 pagesDigital Logic CircuitsskblkoNo ratings yet

- 3 NotesDocument122 pages3 NoteschinnarrrNo ratings yet

- DLD question bankDocument5 pagesDLD question bankHarshad ThiteNo ratings yet

- Practice Problems 12Document32 pagesPractice Problems 12suduku007No ratings yet

- Prob 1. (36 Points Total, 6 Points Each) Convert The Following Signed Integers Using The FollowingDocument3 pagesProb 1. (36 Points Total, 6 Points Each) Convert The Following Signed Integers Using The FollowingJawwad QammarNo ratings yet

- NAND-ONLY LOGIC CIRCUITS REALIZATIONDocument33 pagesNAND-ONLY LOGIC CIRCUITS REALIZATIONyagnasree_sNo ratings yet

- DPCO Unit 1Document45 pagesDPCO Unit 1Laks SadeeshNo ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- Tutorial Sheet - 5Document4 pagesTutorial Sheet - 5Vidit MathurNo ratings yet

- VLSI Questions Answers r3Document79 pagesVLSI Questions Answers r3Gowtham HariNo ratings yet

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Document10 pagesDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa PadmanabhuniNo ratings yet

- Unit 2Document38 pagesUnit 2toshgangwarNo ratings yet

- K-MAP MINIMIZATIONDocument49 pagesK-MAP MINIMIZATIONPavithraNo ratings yet

- Final Old SolDocument8 pagesFinal Old SolPDF PDFNo ratings yet

- EC2203 Digital Electronics Question BankDocument16 pagesEC2203 Digital Electronics Question BankSophiaKaviNo ratings yet

- Chapter 5Document12 pagesChapter 5Sonia MadueñoNo ratings yet

- Quiz Questions For DLD LabDocument6 pagesQuiz Questions For DLD LabGerald Carson100% (1)

- DPSDDocument16 pagesDPSDDhilip PrabakaranNo ratings yet

- Labsheet 1: Problem 1: Subtractor DesignDocument4 pagesLabsheet 1: Problem 1: Subtractor Designanon_248257978No ratings yet

- EENG410/INFE410 - Microprocessors I: Fall 08/09 - Lecture Notes # 1 Outline of The LectureDocument7 pagesEENG410/INFE410 - Microprocessors I: Fall 08/09 - Lecture Notes # 1 Outline of The LectureMuzaffar KhanNo ratings yet

- Workshop Week 4 PDFDocument4 pagesWorkshop Week 4 PDFStevenRNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DFrom EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DNo ratings yet

- Digital Electronics For Engineering and Diploma CoursesFrom EverandDigital Electronics For Engineering and Diploma CoursesNo ratings yet

- Autodesk 3ds Max 2015 Essentials: Autodesk Official PressFrom EverandAutodesk 3ds Max 2015 Essentials: Autodesk Official PressRating: 1 out of 5 stars1/5 (1)

- Ozkan2004 Ultrasonic MaooDocument31 pagesOzkan2004 Ultrasonic MaooDoan Thanh ThienNo ratings yet

- C2500Document16 pagesC2500Doan Thanh ThienNo ratings yet

- Lab1: Design A MIPS 32 by 32 Register FileDocument5 pagesLab1: Design A MIPS 32 by 32 Register FileDoan Thanh ThienNo ratings yet

- Ci It TH Circuit Theory: Electronic & Communication Engineering Danang University of TechnologyDocument43 pagesCi It TH Circuit Theory: Electronic & Communication Engineering Danang University of TechnologyDoan Thanh ThienNo ratings yet

- Lab 1Document16 pagesLab 1Doan Thanh ThienNo ratings yet

- Lab 1 - EE 341Document4 pagesLab 1 - EE 341Nguyễn Văn ThiệnNo ratings yet

- Lab 1 - EE 341Document4 pagesLab 1 - EE 341Nguyễn Văn ThiệnNo ratings yet

- Lab 2: Introduction To Image Processing: 1. GoalsDocument4 pagesLab 2: Introduction To Image Processing: 1. GoalsDoan Thanh ThienNo ratings yet

- Cs6008 Human Computer Interaction L T P C 3 0 0 3Document1 pageCs6008 Human Computer Interaction L T P C 3 0 0 3Sasi RajiNo ratings yet

- Step by Step Failover ClusterDocument53 pagesStep by Step Failover ClusterAtul SharmaNo ratings yet

- CM Service Request Reject CauseDocument9 pagesCM Service Request Reject CausekanthiituNo ratings yet

- Guide On Enabling BFD & ARP DetectionsDocument26 pagesGuide On Enabling BFD & ARP DetectionssamNo ratings yet

- MyPower S3330 Series 10G Access Switch DatasheetDocument12 pagesMyPower S3330 Series 10G Access Switch DatasheetAlejandro LeyvaNo ratings yet

- Ps Virtual Web Application Firewall Admin GuideDocument622 pagesPs Virtual Web Application Firewall Admin GuideWalter BlokNo ratings yet

- Frequently Asked Questions: " (Type Subject of Faqs) " Rulefinder User GuideDocument1 pageFrequently Asked Questions: " (Type Subject of Faqs) " Rulefinder User GuidesjsshipNo ratings yet

- Combo FixDocument8 pagesCombo FixJesus Jhonny Quispe RojasNo ratings yet

- Application Form For Free / at Concession Computer EducationDocument1 pageApplication Form For Free / at Concession Computer EducationChristopher Kirk100% (1)

- Sony DVP-CX850Document84 pagesSony DVP-CX850tonipocoviNo ratings yet

- Index: TCP/IP-Controller-Readme: Setup and Operating InstructionsDocument36 pagesIndex: TCP/IP-Controller-Readme: Setup and Operating InstructionsjovanoxNo ratings yet

- Calculate Hexadecimal DHCPDocument4 pagesCalculate Hexadecimal DHCPTiago SoaresNo ratings yet

- KFSUserGuideENOG HELP SYSTEMDocument227 pagesKFSUserGuideENOG HELP SYSTEMCLEITONNo ratings yet

- Psa Modules Wiring Diagrams: Obd2 DB9Document9 pagesPsa Modules Wiring Diagrams: Obd2 DB9Ĵames-Ĕddìne BaîaNo ratings yet

- Fx2n Function Expansion Memory Hardware ManualDocument8 pagesFx2n Function Expansion Memory Hardware ManualsunhuynhNo ratings yet

- Lab01 Exercise LinuxDocument7 pagesLab01 Exercise LinuxBhupinder SharmaNo ratings yet

- Week 2.3 - The Internet & Web Zeeshan RasoolDocument41 pagesWeek 2.3 - The Internet & Web Zeeshan RasoolTati carryNo ratings yet

- QLAY2 DocumentationDocument10 pagesQLAY2 Documentationjose perezNo ratings yet

- Application - CEMTES Cambodia) Pte LTDDocument2 pagesApplication - CEMTES Cambodia) Pte LTDsuylyvarNo ratings yet

- GE PPS Getting StartedDocument62 pagesGE PPS Getting StartedLeonardPrayitnoNo ratings yet

- Introduction To Quartus II 9.1 Web EditionDocument7 pagesIntroduction To Quartus II 9.1 Web EditionlmnnregNo ratings yet

- Eng TELE-satellite 1207Document324 pagesEng TELE-satellite 1207Alexander WieseNo ratings yet

- Final Year Project ProposalDocument300 pagesFinal Year Project Proposalalim dublinNo ratings yet

- A1800 Meter - Modbus MapDocument48 pagesA1800 Meter - Modbus MaphazimeNo ratings yet

- ATC-108 User's ManualDocument0 pagesATC-108 User's ManualMaitry ShahNo ratings yet

- Rabbit RCM3750 Press ReleaseDocument1 pageRabbit RCM3750 Press ReleaseElectromateNo ratings yet

- ANX9021Document23 pagesANX9021Floricica Victor Vasile50% (2)

- DVB-T2 Digital Terrestrial Receiver User's ManualDocument21 pagesDVB-T2 Digital Terrestrial Receiver User's Manualreza sajatNo ratings yet

- Sensor Node Failure Detection Using Round Trip Delay in Wireless Sensor NetworkDocument9 pagesSensor Node Failure Detection Using Round Trip Delay in Wireless Sensor Networksurendar147No ratings yet

- CSA CompleteDocument196 pagesCSA CompleteNishant SehgalNo ratings yet