Professional Documents

Culture Documents

L&DIC

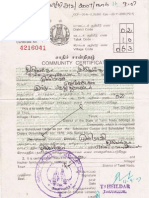

Uploaded by

Dhamo DaranOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

L&DIC

Uploaded by

Dhamo DaranCopyright:

Available Formats

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

INDEX

EXPT.NO 1 2 NAME OF THE EXPERIMENT STUDY OF BASIC DIGITAL ICS a) IMPLEMENTATION OF BOOLEAN FUNCTION b) DESIGN AND IMPLEMENTATION OF ADDER AND SUBTRACTOR USNIG BASIC GATES a) DESIGN AND IMPLEMENTATION OF CODE COVERTERS b) DESIGN AND IMPLEMENTATION OF PARITY GENERATOR AND CHECKER DESIGN AND IMPLEMENTATION OF ENCODER AND DECODER DESIGN AND IMPLEMENTATION OF MULTIPLEXER AND DEMULTIPLEXER CONSTRUCTION AND VERIFICATION OF 4-BIT RIPPLE COUNTER & MOD-10 / MOD-12 RIPPLE COUNTER DESIGN AND IMPLEMENTATION OF 3-BIT SYNCHRONOUS UP / DOWN COUNTER IMPLEMENTATION OF SHIFT REGISTER USING FLIP-FLOPS ASTABLE AND MONOSTABLE MULTIVIBRATOR USING 555 APPLICATIONS OF OP-AMP a) INVERTING AND NON-INVERTING AMPLIFIER b) DIFFERENTIATOR AND INTEGRATOR STUDY OF a) DIGITAL TO ANALOG CONVERTER b) ANALOG TO DIGITAL CONVERTER STUDY OF VCO AND PLL a) FREQUENCY MULTIPLIER USING PLL b) VOLTAGE TO FREQUENCY CHARACTERISTICS OF VCO ADDITIONAL EXPERIMENTS 98 13 14 INSTRUMENTATION AMPLIFIER 101 RC PHASE SHIFT AND WEIN BRIDGE OSCILLATOR USING OP - AMP PAGE NO 3 13 17

3 4 5

24 34 38 42

6 7 8 9

46 52 56 62 68 74 81 85 89 93

10 11

12

1

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

2-Input AND gate:

3-Input AND gate:

2

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To study about logic gates and verify their truth tables. APPARATUS REQUIRED: SL.NO 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. THOERY: Logic gates are the basic elements that make up a digital system. The gate is a digital circuit with one or more inputs, but only one output. By connecting the different gates in different ways, we can build circuits that perform arithmetic and other functions. The operation of a logic gate can be easily understood with the help of truth table. A truth table is a table that shows all the input-output possibilities of a logic circuit ie., the truth table indicates the outputs for different possibilities of the inputs. The types of gates available are the AND, OR, NOT, NAND, NOR, exclusive-OR and the exclusive-NOR. Except for the exclusive-NOR gate they are available in monolithic integrated form. COMPONENTS 2- I/P AND gate 3-I/P AND gate OR gate NOT gate 2- I/P NAND gate 3-I/P NAND gate NOR gate EX-OR gate IC Trainer Kit Patch cords SPECIFICATION IC 7408 IC7411 IC 7432 IC 7404 IC7400 IC7410 IC7402 IC7486 QUANTITY 1 1 1 1 1 1 1 1 1 Few

OR gate: 3

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

NOT gate:

AND gate: 4

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

The AND gates has two or more inputs. It performs a logical multiplication. The output is HIGH (1), when both the inputs are 1; otherwise the output from the gate is LOW (0). The output from the AND gate is written as A.B.

OR gate: The OR gates has two or more inputs. It performs a logical addition. The output is HIGH (1), if any of the inputs are 1; the output is LOW (0) if and only if all the inputs are 0. The output from the AND gate is written as A+B.

NOT gate: The NOT gate has only one input. It performs a basic logic function called inversion. The output is HIGH (1), when the input is 0; the output is LOW (0) when the input is 1. The output from the NOT gate is written as A. NAND gate: The NAND gate is a contraction of AND-NOT. It has two or more inputs. The output is HIGH (1), when any of the inputs are 0; the output is LOW (0), if and only if all the inputs are 1. The output from the AND gate is written as (A.B). It is a universal gate.

NOR gate: The NOR gate is a contraction of OR-NOT. It has two or more inputs. The output is HIGH (1), when all inputs are 0; the output is LOW (0), when any of the inputs are 1. The output from the AND gate is written as (A+B). It is a universal gate.

EX-OR gate: The EX-OR gate has two or more inputs. The output is HIGH (1), when odd number of inputs is 1. The output from the AND gate is written as (A B).

5

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

2-Input NAND gate:

3-Input NAND gate:

6

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

NOR gate:

EX-OR gate:

7

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Flip-Flops:

Flip-flops are synchronous bistable devices (has two outputs Q and Q). In this case, the term synchronous means that the output changes state only at a specified point on the triggering input called the clock (CLK), i.e., changes in the output occur in synchronization with the clock. The different types of edge-triggered flip-flops are S-R Flip-flop, J-K Flip-flop, D Flip-flop, T Flip-flop. S-R Flip-flop: The simplest type of flip-flop is the Set - Reset (SR) flip-flop. The S and R inputs of the S-R flip-flop are called synchronous inputs because data on these inputs are transferred to the flip-flop's output only on the triggering edge of the clock pulse. On the positive edge of the clock pulse, the circuit responds to the S and R inputs. J-K Flip-flop: JK means Jack Kilby, Texas Instrument (TI) Engineer, who invented IC in 1958. JK flip-flop has two inputs J (set) and K (reset). The data input J and the output Q are applied o the first AND gate and its output (JQ) is applied to the S input of SR flip-flop. Similarly, the data input K and the outputs Q are applied to the second AND gate and its output (KQ) is applied to the R input of SR flip-flop. D Flip-flop: To eliminate the undesirable condition of the indeterminate state in the RS flip-flop is to ensure that inputs S and R are never equal to 1 at the same time. This is done by D flip-flop. The D (delay) flip-flop has one input called delay input and clock pulse input. T Flip-flop: The T (Toggle) flip-flop is a modification of the JK flip-flop. It is obtained from JK flip-flop by connecting both inputs J & K together, i.e., single input. Regardless of the present state, the flip-flop complements its output when the clock pulse occurs while input T= 1.

8

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

JK Flip-flop:

(a) Logic Diagram TRUTH TABLE:

Clock 1 1 1 1 1 1 1 1

Qn 0 0 0 0 1 1 1 1

J 0 0 1 1 0 0 1 1

K 0 1 0 1 0 1 0 1

Qn+1 0 0 1 1 1 0 1 0

Truth table for JK Flip-flop

SR Flip-flop:

9

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TRUTH TABLE:

CLK 1 1 1 1 1 1 1 1

Qn 0 1 0 1 0 1 0 1

S 0 0 0 0 1 1 1 1

R 0 0 1 1 0 0 1 1

Qn+1 0 1 0 0 1 1 x x

Truth table for SR Flip-flop

D Flip-flop:

TRUTH TABLE:

Clock 1 1 1 1

Qn 0 0 1 1

D 0 1 0 1

Qn+1 0 1 0 1

10

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

T Flip-flop:

TRUTH TABLE:

Clock 1 1 1 1

Qn 0 0 1 1

T 0 1 0 1

Qn+1 0 1 1 0

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with the truth table.

RESULT: Thus the logic gates are studied and their truth tables for AND, OR, NOT, EXOR, NOR, NAND, JK FF, RS FF, D FF and T FF are verified.

11

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

DESIGN: Given, F( A, B, C, D) = m (0, 1, 2, 5, 8, 9, 10) The function, F has four input variables. Hence a 4- variable Karnaugh map is used to obtain a simplified expression for the output as shown, K-map Simplification:

From the K-map, the expression can be written as, F = BC + BD + ACD The above expression can be written as, F = C (B+ AD) + BD Now, the logic circuit for the above expression can be drawn as,

LOGIC DIAGRAM:

12

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To minimize the Boolean function using K-map and implement the logic circuit and verify the truth table of the given Boolean function. F( A, B, C, D) = m (0, 1, 2, 5, 8, 9, 10) APPARATUS REQUIRED:

SL.NO COMPONENTS SPECIFICATION QUANTITY

1. 2. 3. 4. 5. 6.

IC Trainer kit EX-OR gate NOT gate OR gate AND gate Patch cords

IC 7486 IC 7404 IC 7432 IC7408 -

1 1 1 1 1 Few

THEORY: The simplification of the functions using Boolean laws and theorems becomes complex with the increase in the number of variables and terms. The map method, first proposed by Veitch and slightly improvised by Karnaugh, provides a simple, straightforward procedure for the simplification of Boolean functions. The method is called Veitch diagram or Karnaugh map, which may be regarded as a pictorial representation of a truth table. The Karnaugh map technique provides a systematic method for simplifying and manipulation of Boolean expressions. A K-map is a diagram made up of squares, with each square representing one minterm of the function that is to be minimized. For n variables on a Karnaugh map there are 2 n numbers of squares. Each square or cell represents one of the minterms. It can be drawn directly from either minterm (sum-of-products) or maxterm (product-of-sums) Boolean expressions.

13

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TRUTH TABLE: INPUT A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 OUTPUT F = C (B+ AD) + BD 1 1 1 0 0 1 0 0 1 1 1 0 0 0 0 0

The following guidelines should be followed while choosing the preferred form for hardware implementation: 1. The implementation should have the minimum number of gates, with the gates used having the minimum number of inputs. 2. There should be a minimum number of interconnections. 3. Limitation on the driving capability of the gates should not be ignored.

14

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with their truth tables.

RESULT: Thus the given Boolean function was minimized using K-map and the circuit was implemented using basic gates.

15

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

HALF ADDER:

TRUTH TABLE:

Inputs A 0 0 1 1

K- MAP SIMPLIFICATION:

Outputs Carry (C) 0 0 0 1 Sum (S) 0 1 1 0

B 0 1 0 1

LOGIC DIAGRAM:

FULL ADDER:

TRUTH TABLE:

Inputs A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Cin 0 1 0 1 0 1 0 1 Sum (S) 0 1 1 0 1 0 0 1

Outputs Carry (C out) 0 0 0 1 0 1 1 1 16

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and construct a half adder, full adder, half subtractor and full subtractor circuits and verify their truth table using logic gates.

APPARATUS REQUIRED: SL.NO 1. 2. 3. 4. 5. 6. COMPONENTS IC Trainer kit EX-OR gate NOT gate OR gate AND gate Patch cords SPECIFICATION IC 7486 IC 7404 IC 7432 IC7408 QUANTITY 1 1 1 1 1 Few

THEORY: Half Adder: A half-adder is a combinational circuit that can be used to add two binary bits. It has two inputs that represent the two bits to be added and two outputs, with one producing the SUM output and the other producing the CARRY. The Sum can be applied using EX-OR gate, carry output can be applied using an AND gate.

Full Adder: A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of 3 inputs and 2 outputs. Two of the input variables, represent the significant bits to be added. The third input represents the carry from previous lower significant position. The logic diagram of the full adder can also be implemented with two halfadders and one OR gate. The S output from the second half adder is the exclusive -OR of Cin and the output of the first half-adder

17

DMI College of Engineering

131452-Linear and Digital Integrated Circuits. K-MAP SIMPLIFICATION:

Dept of Electronics & Communication Engg

LOGIC DIAGRAM:

Full Adder:

Full Adder using Two Half Adders:

18

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Half Subtractor: A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output. The BORROW output here specifies whether a 1 has been borrowed to perform the subtraction. The difference can be applied using EX-OR gate, borrow output can be applied using an AND gate and an inverter.

Full Subtractor: A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a 1 has already been borrowed by the previous adjacent lower minuend bit or not. As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin . There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo . The BORROW output bit tells whether the minuend bit needs to borrow a 1 from the next possible higher minuend bit.

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with their truth tables.

19

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

HALF SUBTRACTOR:

TRUTH TABLE:

Input A 0 0 1 1

K- MAP SIMPLIFICATION:

B 0 1 0 1

Output Difference (D) Borrow (Bout) 0 0 1 1 1 0 0 0

LOGIC DIAGRAM:

FULL SUBTRACTOR:

TRUTH TABLE:

Inputs A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Bin 0 1 0 1 0 1 0 1

Outputs Difference(D) Borrow(Bout) 0 0 1 1 1 1 0 1 1 0 0 0 0 0 1 1

20

DMI College of Engineering

131452-Linear and Digital Integrated Circuits. K- MAP SIMPLIFICATION:

Dept of Electronics & Communication Engg

LOGIC DIAGRAM:

Full Subtractor:

Full Subtractor with Two Half Subtractors:

21

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus half adder, full adder, half subtractor and full subtractor circuits was designed using logic gates and their truth tables were verified. 22

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

BINARY TO GRAY CODE CONVERTER: Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 B3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Binary code B2 B1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 G3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Gray code G2 G1 0 0 0 0 0 1 0 1 1 1 1 1 1 0 1 0 1 0 1 0 1 1 1 1 0 1 0 1 0 0 0 0 G0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

K- Map Simplification:

23

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implement 4-bit 1. Binary to Gray code Converter 2. Gray to Binary code Converter 3. BCD to Excess-3 code Converter 4. Excess-3 code to BCD Converter APPARATUS REQUIRED: SL.NO 1. 2. 3. 4. 5. 6. 7. THEORY: An availability of large variety of codes for the same discrete elements of information results in the use of different codes by different systems. A conversion circuit must be inserted between the two systems if each uses different codes for the same information. Thus, code converter is a circuit that makes the two systems compatible even though each uses different binary code. The bit combination assigned to binary code gray code. Since each code uses four bit to represent a decimal digit. There are four inputs and four outputs. Gray code is a non weighted code. The input variable are designed as B3 ,B2 ,B1 ,B0 and the output variables are designed as G3 ,G2 ,G1 ,G0 . From the truth table, combinational circuit is designed. The Boolean functions are obtained from K-Map for each output variable. COMPONENT IC Trainer kit EX-OR gate NOT gate OR gate 2-Input AND gate 3-Input AND gate Patch cords SPECIFICATION IC7486 IC7404 IC7432 IC7408 IC7411 QUANTITY 1 1 1 1 1 1 Few

24

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Logic Diagram:

GRAY TO BINARY CODE CONVERTER: Truth Table: G3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Gray code G2 G1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 G0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 B3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Binary code B2 B1 0 0 0 0 0 1 0 1 1 1 1 1 1 0 1 0 1 1 1 1 1 0 1 0 0 0 0 0 0 1 0 1 B0 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0

25

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

A code converter is a circuit that makes the two systems compatible even though each uses a different binary code. To convert from binary code to Excess-3 code, the input lines must supply the bit combination of elements as specified by code and the output lines generate the corresponding bit combination of code. Each one of the four maps represents one of the four outputs of the circuit as a function of the four input variables. A two-level logic diagram may be obtained directly from the Boolean expressions derived by the maps. These are various other possibilities for a logic diagram that implements this circuit. Now the OR gate whose output is C+D has been used to implement partially each of three outputs.

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with the truth tables.

26

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

K-Map Simplification:

Logic Diagram:

27

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

BCD TO EXCESS-3 CODE: Truth table: B3 0 0 0 0 0 0 0 0 1 1 BCD code B2 B1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 B0 0 1 0 1 0 1 0 1 0 1 E3 0 0 0 0 0 1 1 1 1 1 Excess-3 code E2 E1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 E0 1 0 1 0 1 0 1 0 1 0

K-Map Simplification:

28

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Logic Diagram:

29

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

EXCESS-3 TO BCD CONVERTER: Truth Table: E3 0 0 0 0 0 1 1 1 1 1 Excess-3 code E2 E1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 E0 1 0 1 0 1 0 1 0 1 0 B3 0 0 0 0 0 0 0 0 1 1 BCD code B2 B1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 B0 0 1 0 1 0 1 0 1 0 1

K-Map Simplification:

30

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Logic Diagram:

31

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus the 4-bit 1. Binary to Gray code Converter 2. Gray to Binary code Converter 3. BCD to Excess-3 code Converter 4. Excess-3 code to BCD Converter was designed and implemented.

32

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PARITY GENERATOR : Truth Table: 3-bit Message A B C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Even Parity bit (Pe ) 0 1 1 0 1 0 0 1 Odd Parity bit (Po) 1 0 0 1 0 1 1 0

Parity generator truth table for even parity & odd parity

K-map Simplification:

For Even-Parity Generator:

For Even-Parity Generator:

Logic Diagram:

33

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implement an even Parity Generator and Checker using logic gates.

APPARATUS REQUIRED:

SL.NO COMPONENT SPECIFICATION QUANTITY

1. 2. 3. 4. THEORY:

IC Trainer kit EX-OR gate NOT gate Patch cords

IC7486 IC7404 -

1 1 1 Few

Parity is a very useful tool in information processing in digital computers to indicate any presence of error in bit information. External noise and loss of signal strength causes loss of data bit information while transporting data from one device to other device, located inside the computer or externally. To indicate any occurrence of error, an extra bit is included with the message according to the total number of 1s in a set of data, which is called parity. If the extra bit is considered 0 if the total number of 1s is even and 1 for odd quantities of 1s in a set of data, then it is called even parity. On the other hand, if the extra bit is 1 for even quantities of 1s and 0 for an odd number of 1s, then it is called odd parity.

Parity Generator: A parity generator is a combination logic system to generate the parity bit at the transmitting side. The message including the parity is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator.

34

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PARITY CHECKER:

Truth Table:

4-Bit Received A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Parity Error Check (PEC) 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0

Parity checker truth table for even parity

K-map Simplification:

Logic Diagram:

4-bit even parity checker

35

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Parity Checker: The message bits with the parity bit are transmitted to their destination, where they are applied to a parity checker circuit. The circuit that checks the parity at the receiver side is called the parity checker. The parity checker circuit produces a check bit and is very similar to the parity generator circuit. If the check bit is 1, then it is assumed that the received data is incorrect. The check bit will be 0 if the received data is correct.

PROCEDURE: 1. Connections are given as per the circuit diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with the truth table.

RESULT: Thus an even and odd Parity Generator and even parity checker were designed and implemented using logic gates. 36

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

ENCODER: Logic Diagram:

Truth Table: INPUTS Y1 1 0 0 0 0 0 0 Y2 0 1 0 0 0 0 0 Y3 0 0 1 0 0 0 0 Y4 0 0 0 1 0 0 0 Y5 0 0 0 0 1 0 0 Y6 0 0 0 0 0 1 0 Y7 0 0 0 0 0 0 1 A 0 0 0 1 1 1 1 OUTPUTS B 0 1 1 0 0 1 1 C 1 0 1 0 1 0 1

37

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implementation encoder and decoder using logic gates.

APPARATUS REQUIRED:

SL.NO COMPONENT SPECIFICATION QUANTITY

1. 2. 3. 4. 5. THEORY: Encoder:

IC Trainer kit 3-I/P NAND gate NOT gate OR gate Patch cords

IC7410 IC7404 IC7432 -

1 2 1 3 Few

An encoder is a digital circuit that performs inverse operation of a decoder. An encoder has 2n input lines and n output lines. In encoder the output lines generates the binary code corresponding to the input value. In octal to binary encoder it has eight inputs, one for each octal digit and three output that generates the corresponding binary code. In encoder it is assumed that only one input has a value of one at any given time otherwise the circuit is meaningless. It has an ambiguila that when all inputs are zero the outputs are zero. The zero outputs can also be generated when D0=1.

Decoder: A decoder is a multiple output logic circuit which converts input into coded output where input and output codes are different. The input code generally has few bits than the output code. Each input code word produces a different output code word i.e., there is one to one mapping can be expressed in truth table. In block diagram of decoder circuit the encoded information is present as n input producing 2n possible outputs. The 2n output values are from 0 through out 2n -1.

38

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

DECODER: Logic Diagram ( 2-to-4- Line Decoder with Enable Input):

Truth Table: INPUTS E 1 0 0 0 0 A x 0 0 1 1 B x 0 1 0 1 D3 1 0 1 1 1 OUTPUTS D1 1 1 0 1 1 D2 1 1 1 0 1 D3 1 1 1 1 0

39

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with the truth tables.

RESULT: Thus the design and implementation of encoder and decoder using logic gates was done successfully.

40

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

4:1 MULTIPLEXER:

BLOCK DIAGRAM:

FUNCTION TABLE:

S1 0 0 1 1

S0 0 1 0 1

INPUTS, (Y) D0 = D0 S1 S0 D1 = D1 S1 S0 D2 = D2 S1 S0 D3 = D3 S1 S0

Output, Y= D 0 S1 S0 +D 1 S1 S0 + D 2 S1 S0 +D3 S1 S0

LOGIC DIAGRAM:

41

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implement multiplexer and demultiplexer using logic gates.

APPARATUS REQUIRED:

SL.NO COMPONENTS SPECIFICATION QUANTITY

1. 2. 3. 4. 5.

IC Trainer kit 3-I/P AND GATE NOT GATE OR GATE Patch cords

IC7411 IC7404 IC7432 -

1 2 1 1 Few

THEORY: Multiplexer: Multiplexer means transmitting a large number of information units over a small number of channels or lines. A digital multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally there are 2 n input line and n selection lines whose bit combination determine which input is selected. A multiplexer is also called a data selector, since it selects one of many inputs and steers the binary information to the output line.

De-multiplexer: The function of Demultiplexer is in contrast to multiplexer function. It takes information from one line and distributes it to a given number of output lines. For this reason, the demultiplexer is also known as a data distributor. Decoder can also be used as Demultiplexer.

42

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

1: 4 DEMULTIPLEXER:

BLOCK DIAGRAM:

FUNCTION TABLE:

S1 0 0 1 1

S0 0 1 0 1

INPUT, X

D0 = XS1 S0 D1 = XS1 S0 D2 = XS1 S0 D3 = XS1 S0

Output, Y= XS1 S0 +XS1 S0 + XS1 S0 +XS1 S0

LOGIC DIAGRAM:

43

DMI College of Engineering

131452-Linear and Digital Integrated Circuits. TRUTH TABLE:

Dept of Electronics & Communication Engg

INPUT S1 0 0 0 0 1 1 1 1 S0 0 0 1 1 0 0 1 1

I/P

OUTPUT D1 0 1 0 0 0 0 0 0 D0 0 0 0 1 0 0 0 0 D2 0 0 0 0 0 1 0 0 D3 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 1

In the 1:4 demultiplexer circuit, the data input line goes to all of the AND gates. The data select lines enable only one gate at a time and the data on the data input line will pass through the selected gate to the associated data output line.

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the truth table. 3. Observe the logic output and verify with the truth tables.

RESULT: Thus the multiplexer and demultiplexer was designed and implemented using logic gates. 44

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

4- BIT RIPPLE COUNTER:

Pin Diagram (JK Flip-Flop):

Logic Diagram (4-Bit Ripple Counter):

45

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To construct and verify 4 bit ripple counter, MOD-10 and MOD-12 ripple counter. APPARATUS REQUIRED: SL.NO 1. 2. 3. 4. COMPONENT IC Trainer kit JK Flip-flop NAND gate Patch cords SPECIFICATION IC7476 IC7400 QUANTITY 1 2 1 Few

THEORY: A counter is a register capable of counting number of clock pulse arriving at its clock input. Counter represents the number of clock pulse arrived. A specified sequence of states appears as counter output. This is the main difference between a register and a counter. There are two types of counter, synchronous and asynchronous. In synchronous common clock is given to all flip flop and in asynchronous, first flip flop is clocked by external pulse and then each successive flip flop is clocked by Q or Q output of pervious stage. A ripple counter is a cascaded arrangement of flip-flops where the output of one flipflop drives the clock input of the following flip-flop. The number of flip-flops in the cascaded arrangement depends upon the number of different logic states that it goes through before it repeats the sequence, a parameter known as the modulus of the counter. In a ripple counter, also called an asynchronous counter or a serial counter, the clock input is applied only to the first flip-flop, also called the input flip-flop, in the cascaded arrangement. The clock input to any subsequent flip-flop comes from the output of its immediately preceding flip-flop. For instance, the output of the first flip-flop acts as the clock input to the second flip-flop, the output of the second flip-flop feeds the clock input of the third flip-flop and so on.

46

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Truth Table: CLK 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 QA 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 QB 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 QC 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 QD 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Logic Diagram (MOD-10 Ripple Counter):

47

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

In a ripple counter, also called an asynchronous counter or a serial counter, the clock input is applied only to the first flip-flop, also called the input flip-flop, in the cascaded arrangement. The clock input to any subsequent flip-flop comes from the output of its immediately preceding flip-flop. For instance, the output of the first flip-flop acts as the clock input to the second flip-flop, the output of the second flip-flop feeds the clock input of the third flip-flop and so on. A four-bit ripple counter is implemented with negative edge-triggered J-K flip-flops wired as toggle flip-flops. The output of the first flip-flop feeds the clock input of the second, and the output of the second flip-flop feeds the clock input of the third, the output of which in turn feeds the clock input of the fourth flip-flop. The outputs of the four flip-flops are designated as Q0 (LSB flip-flop), Q 1 , Q2 and Q 3 (MSB flip-flop).

48

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Truth Table: CLK 0 1 2 3 4 5 6 7 8 9 10 QA 0 1 0 1 0 1 0 1 0 1 0 QB 0 0 1 1 0 0 1 1 0 0 0 QC 0 0 0 0 1 1 1 1 0 0 0 QD 0 0 0 0 0 0 0 0 1 1 0

Logic Diagram (MOD-12 Ripple Counter):

49

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Truth Table: CLK 0 1 2 3 4 5 6 7 8 9 10 11 12 QA 0 1 0 1 0 1 0 1 0 1 0 1 0 QB 0 0 1 1 0 0 1 1 0 0 1 1 0 QC 0 0 0 0 1 1 1 1 0 0 0 0 0 QD 0 0 0 0 0 0 0 0 1 1 1 1 0

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the logic diagram. 3. Observe the logic output and verify with the truth tables.

RESULT: Thus 4-bit ripple counter, MOD-10 and MOD-12 ripple counter was constructed and verified successfully. 50

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

3- BIT SYNCHRONOUS UP/DOWN COUNTER: State Diagram:

Truth table: Input Up/Down 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Present State QA 0 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 QB 0 1 1 0 0 1 1 0 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Next State QA+1 QB+1 QC+1 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 0 1 1 0 0 1 1 0 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 JA 1 x x x x 0 0 0 0 0 0 1 x x x x A KA x 0 0 0 1 x x x x x x x 0 0 0 1 JB 1 x x 0 1 x x 0 0 1 x x 0 1 x x B KB x 0 1 x x 0 1 x x x 0 1 x x 0 1 JC 1 x 1 x 1 x 1 x 1 x 1 x 1 x 1 x C KC x 1 x 1 x 1 x 1 x 1 x 1 x 1 x 1

51

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implement 3 bit synchronous up/down counter. APPARATUS REQUIRED:

SL.NO COMPONENT SPECIFICATION QUANTITY

1. 2. 3. 4. 5. 6. 7.

IC Trainer kit JK Flip-flop 3-I/P NAND gate NOT gate OR gate EX-OR gate Patch Cords

IC7476 IC7411 IC7404 IC7432 IC7486 -

1 2 1 1 1 1 Few

THEORY: A Counter is a register capable of counting number of clock pulse arriving at its clock input. Counter represents the number of clock pulses arrived. An up/down counter is one that is capable of progressing in increasing order or decreasing order through a certain sequence. An up/down counter is also called bi-directional counter. Usually up/down operation of the counter is controlled by up/down signal. When this signal high counter goes through up sequence and when up/down signal is low counter follows reverse sequence. The counter counts upwards when UP control are logic 1 and DOWN control is logic 0. In this case the clock input of each flip-flop other than the LSB flip-flop is fed from the normal output of the immediately preceding flip-flop. The counter counts downwards when the UP controls input are logic 0 and DOWN control is logic 1. In this case, the clock input of each flip-flop other than the LSB flip-flop is fed from the complemented output of the immediately preceding flip-flop.

52

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Excitation Table (JK Flip-Flop):

Q 0 0 1 1

K-Map Simplification:

Q t+1 0 1 0 1

J 0 1 x x

K x x 1 0

53

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Logic Diagram:

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the logic diagram. 3. Observe the logic output and verify with the truth tables.

RESULT: Thus 3- bit synchronous up/down counter was designed and implemented successfully. 54

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

SHIFT REGISTER: Pin Diagram (D-Flip-Flop):

Serial IN Serial OUT:

Logic Diagram:

55

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design and implement 1. Serial in serial Out(SISO) 2. Serial in parallel Out(SIPO) 3. Parallel in serial Out(PISO) 4. Parallel in parallel Out(PIPO)

APPARATUS REQUIRED: SL.NO 1. 2. 3. 4. COMPONENT IC Trainer kit D-Flip flop OR gate Patch cords SPECIFICATION IC7474 IC7432 QUANTITY 1 2 1 Few

THEORY: A register is capable of shifting its binary information in one or both directions is known as shift register. A logical configuration of shift register consist of a D flip flop cascaded with output of one flip flop connected to input of next flip flop. All flip flops receive common clock pulses which causes the shift in the output of the flip flop. The simplest possible shift register is one that uses only flip flop. The output of a given flip flop is connected to the input of next flip flop of the register. Each clock pulse shifts the content of register one bit position to right.

56

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Truth Table:

CLK 1 2 3 4 5 6 7 8

Serial IN 1 1 1 1 0 0 0 0

Serial OUT 0 0 0 1 1 1 1 0

Serial IN Parallel OUT:

Logic Diagram:

Truth Table:

CLK 1 2 3 4

DATA 1 0 0 1

OUTPUT Q3 1 0 0 1 Q2 0 1 0 0 Q1 0 0 1 0 Q0 0 0 0 1

57

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Parallel IN Serial OUT:

Logic Diagram:

Truth Table:

S/ L 0 1 1 1

INPUTS CLK 0 1 2 3 A 1 1 1 1 B 0 0 0 0 C 0 0 0 0 D 1 1 1 1

OUTPUT Q 1 0 0 1

58

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Parallel IN Parallel OUT:

Logic Diagram:

Truth Table: CLK D3 1 2 1 1 DATA INPUTS D2 0 0 D1 0 1 D0 1 0 Q3 1 1 OUTPUT Q2 0 0 Q1 0 1 Q0 1 0

59

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PROCEDURE: 1. Connections are given as per the logic diagram. 2. Logic inputs are given as per the logic diagram. 3. Observe the logic output and verify with the truth tables.

RESULT: Thus the design and implementation of 1. Serial in serial Out (SISO) 2. Serial in parallel Out (SIPO) 3. Parallel in serial Out (PISO) 4. Parallel in parallel Out (PIPO) was done successfully. 60

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGRAM:

CIRCUIT DIAGRAM:(ASTABLE)

TABULATION: DESIGN VALUE OBSERVED VALUE F (Hz)

Waveforms Output waveform Capacitor waveform (Capacitor voltage Vc)

Amplitude (volts)

THigh

(ms)

TLow

(ms)

T

(ms)

THigh

(ms)

TLow

(ms)

T

(ms)

F (Hz)

61

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To Design and test Astable and Monostable multivibrator using 555 timer IC. APPARATUS REQUIRED: S.NO 1. 2. 3. 4. 5. 6. 7. COMPONENTS IC 555 RESISTORS CAPACITORS SIGNAL GENERATOR CATHODE RAY OSCILLOSCOPE DUAL POWER SUPPLY CONNECTING WIRES RANGE --6.8K,470,3.3K,300,10K 0.1f, 0.01f. (0-3)MHz (0-20)MHz (0-30)V --QUANTITY 01 EACH 01 EACH01 01 01 01 FEW

THEORY:(ASTABLE) When the power supply VCC is connected, the external timing capacitor C charges towards VCC with a time constant (RA+RB) C. During this time, pin 3 is high (VCC) as Reset R=0, Set S=1 and this combination makes Q = 0 which has unclamped the timing capacitor C. When the capacitor voltage equals 2/3 VCC, the upper comparator triggers the control flip flop on that Q =1. It makes Q1 ON and capacitor C starts discharging towards ground through RB and transistor Q1 with a time constant RBC. Current also flows into Q1 through RA. Resistors RA and RB must be large enough to limit this current and prevent damage to the discharge transistor Q1. The minimum value of RA is approximately equal to VCC/0.2 where 0.2A is the maximum current through the ON transistor Q1. During the discharge of the timing capacitor C, as it reaches VCC/3, the lower comparator is triggered and at this stage S=1, R=0 which turns Q =0. Now Q =0 unclamps the external timing capacitor C. The capacitor C is thus periodically charged and discharged between 2/3 VCC and 1/3 VCC respectively. The length of time that the output remains HIGH is the time for the capacitor to charge from 1/3 VCC to 2/3 VCC.

62

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODEL GRAPH:

(a): Square wave output (b): Capacitor voltage of Square wave output

MONOSATBLE MULTIVIBRATOR:

63

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

The capacitor voltage for a low pass RC circuit subjected to a step input of VCC volts is given by VC = VCC [1- exp (-t/RC)] Total time period T = 0.69 (RA + 2 RB) C f = 1/T = 1.45/ (RA + 2RB) C MONOSATBLE MULTIVIBRATOR : A Monostable Multivibrator, often called a one-shot Multivibrator, is a pulse-generating circuit in which the duration of the pulse is determined by the RC network connected externally to the 555 timer. In a stable or stand by mode the output of the circuit is

approximately Zero or at logic-low level. When an external trigger pulse is given, the output is forced to go high ( VCC). The time for which the output remains high is determined by the external RC network connected to the timer. At the end of the timing interval, the output automatically reverts back to its logic-low stable state. The output stays low until the trigger pulse is again applied. Then the cycle repeats. The Monostable circuit has only one stable Normally the output of the Monostable

state (output low), hence the name Monostable. Multivibrator is low. DESIGN PROCEDURE: ASTABLE MULTIVIBRATOR:

Design of Astable multivibrator of operation frequency = 1 KHz & duty cycle of 25% using 555 timer IC. Given Frequency=1000Hz Duty cycle=25% D= T low/T = RB/RA+2RB*100 100RB = 25(RA+2RB) 50RB 25RA = 0 given f=1khz we know that T=1/f T=1ms T= T high + T low 0.69(RA+2RB)C = 1*10-3 0.69(RA+2RB) = 1*10-3 /C Let C=0.1F 0.69RA+1.38RB = 1*10-3 /0.1*10-6 0.69RA+1.38RB = 10 4 ------------------------------------(2) -----------------------------------(1)

64

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TABULATION: Amplitude (volts) Time period (ms)

S.No

Waveforms

1.

Input waveform

2.

Output waveform Capacitive waveform (Capacitor voltage Vc)

3.

MODEL GRAPH:

65

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Solving equation 1 & 2 we get RA=7.2K RB= 3.6K MONOSTABLE MULTIVIBRATOR:

T = 1.1RAC Assume RA = 10K C=1F T = 1.1 * 10000 * 1*10-6 = 11ms PROCEDURE: ASTABLE MULTIVIBRATOR: 1. Calculate the component values using the design procedure. 2. Connect the circuit as shown in the circuit diagram. 3. Observe and note down the output waveform. 4. Measure the frequency of oscillations and duty cycle and then compare with the given values. 5. Plot both the waveforms to the same time scale in a graph. MONOSTABLE MULTIVIBRATOR: 1. Calculate the value of R & C using design procedure. 2. Connect the circuit as shown in the circuit diagram. 3. Apply Negative triggering pulses at pin 2 of frequency 1 KHz. 4. Observe the output waveform and measure the pulse duration. 5. Theoretically calculate the pulse duration as T=1.1 RAC

RESULT: Thus the Astable and Monostable multivibrator is designed and tested using 555 timer IC

66

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGARAM:

INVERTING AMPLIFIER: CIRCUIT DIAGRAM:

TABULATION: S.No 1. 2. 3. 4. R f (K) 1K 10K 33K 100K Vin (Volts) Vout (Volts) Theoretical Gain A = -Rf / R1 Practical Gain A = V0 / Vin

67

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design the Inverting and Non-Inverting Amplifiers using Op-amp IC741 and test their performance. APPARATUS REQUIRED: S.NO 1. 2. 3. 4. 5. 6. IC 741 RESISTORS SIGNAL GENERATOR CATHODE RAY OSCILLOSCOPE DUAL POWER SUPPLY CONNECTING WIRES COMPONENTS RANGE --1K, 33K 10K, 100 K. (0-3)MHz (0-20)MHz (0-30)V --QUANTITY 01 EACH 01 EACH 02 02 01 01 FEW

THEORY: Op-amp in open-loop configuration has a very few application because of its enormous open-loop gain. Controlled gain can be can be achieved by taking a part of output signal to the input with the help of feedback. This is called as Closed-Loop Configuration. The three basic types of closed-loop amplifier configuration are: 1. Inverting amplifier. 2. Non-inverting amplifier. 3. Differential amplifier. The entire configuration can be operated with either AC or DC input. INVERTING AMPLIFIER: If the input signal is applied to the inverting terminal through an input resistance, a part of output is feedback to the inverting terminal through feedback resistance Rf and the non-inverting terminal grounded, then the configuration is said to be Inverting Amplifier. It provides 1800 phase shift or polarity reversal for the given input. The circuit closed-loop voltage gain is

Avcl Rf . R1

68

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODEL GRAPH:

NON-INVERTING AMPLIFER: CIRCUIT DIAGRAM:

TABULATION: S.No 1. 2. 3. 4. R f (K) 1K 10K 33K 100K Vin (Volts) Vout (Volts) Theoretical Gain A = 1+(R f / R1 ) Practical Gain A = V0 / Vin

69

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

NON-INVERTING AMPLIFIER: If the input signal is given to non inverting terminal & the feedback from output is connected to inverting terminal of an op-amp through a potential divider network, then it is called as Non-Inverting Amplifier Configuration. It operates in a same way as a voltage follower (unity gain buffer), except that the output voltage is potentially divided before it is fedback to the inverting input terminal. No phase shift or change in the circuit closed loop polarity occurs voltage gain is Avcl 1 PROCEDURE:

Rf R1

1. Select R1 as a constant value and choose a value of Rf. 2. Connect the circuit as per as the circuit diagram. 3. Apply the constant amplitude input voltage to the circuit. 4. Measure the output voltage amplitude for different value of Rf from CRO. 5. Calculate the practical gain for different value of Rf & compare it with theoretical gain. 6. Practical gain & theoretical gain should be approximately equal. 7. Plot the graph of the input wave versus output wave for any one practical case.

70

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODEL GRAPH:

71

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus the Inverting and Non-Inverting Amplifiers are designed and their performance was successfully tested using op-amp IC 741. 72

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGARAM:

INTEGRATOR: CIRCUIT DIAGRAM:

TABULATION: Input Amplitude (V) Time Period (ms) Amplitude (V) Output Time Period (ms)

73

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design an Integrator and Differentiator using op-amp IC 741 and to test their performance. APPARATUS REQUIRED: S.NO 1. 2. 3. 4. 5. 6. IC 741 RESISTORS CAPACITOR SIGNAL GENERATOR CATHODE RAY OSCILLOSCOPE CONNECTING WIRES COMPONENTS RANGE --1.5K 15K 0.1f, 0.01f (0-3)MHz (0-20)MHz --QUANTITY 01 02 01 Each 01 01 01 FEW

THEORY (INTEGRATOR): A circuit in which the output voltage waveform is the integral of the input voltage waveform is the integrator or integration amplifier; Such a circuit is obtained by using basic inverting amplifier configuration, if the feed back resistor Rf is replaced by a capacitor Cf. The Output voltage expression is given as

VO 1 R1C f

t

Vin dt

o

C.

The frequency of input at which the gain is 0 db is given as fb

1 2 R1C f

The point up to which the gain is constant & maximum is called as gain limiting frequency & given as fa

1 2 Rf C f

Where Rf is the feedback resistor used to correct the stability & roll-off

problems. Between fa & fb the circuit acts as an integrator and it is similar to a LPF. Integrator is most commonly used in analog computers, A/D converter & signal wave shaping circuits.

74

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODELGRAPH:

DIFFERENTIATOR: CIRCUIT DIAGRAM:

75

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

THEORY- (DIFFERENTIATOR): A differentiator or differentiation amplifier is a circuit which performs the mathematical operation of differentiation; that is, the output waveform is the derivative of the input waveform. The differentiator may be constructed from the basic inverting amplifier if an input resistor R1 is replaced by capacitor C1. The differentiation is very useful to find the rate at which a signal varies with time. For maintaining the stability of differentiator, a series resistor R1 is connected with input capacitor C1. the circuit will provide differentiation function but only over a limited frequency range & over this range differentiator tend to oscillate (or) poor stability results. The expression for output voltage is Vo PROCEDURE: INTEGRATOR: 1. From the given frequency fa & fb, the values of Rf, Cf, R1 & Rcomp are calculated as given in the design procedure. 2. Connect the circuit as shown in the circuit diagram. 3. Apply the sinusoidal input as the constant amplitude to the inverting terminal of opamp. 4. Gradually increase the frequency & observe the output amplitude. 5. Calculate the gain with respect to frequency & plot its graph. DIFFERENTIATOR:

R f C1 dVin dt

1. Select fa equal to the highest frequency of the input signal to be differentiated. Calculate the component values of C 1 & Rf. 2. Choose fb = 10fa & calculate the values of R1 & Cf, so that R1 C1 =Rf Cf. 3. Connect the components as shown in the circuit diagram. 4. Apply a sinusoidal & square wave input to the inverting terminal of op-amp through R1 C1. 5. Observe the shape of the output signal for the given input in CRO. 6. Note down the reading and plot the graph of input versus output wave for both cases.

76

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TABULATION: Input Amplitude (V) Time Period (ms) Amplitude (V) Output Time Period (ms)

MODEL GRAPH:

77

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

DESIGN PROCEDURE-(INTEGRATOR):

Design of integrator to integrate at cut-off frequency 100Hz. Take fa =

1 2 Rf C f

= 100Hz. Always take C f < 1f and Let Cf = 0.1f Rf =

1 2 C f fa

Rf = 15.9K Rf = 15K Take fb =

1 = 1KHz. 2 R1C f

R1 =

1 = 1.59K. 2 fbC f

R1 1.5K

Rcomp = R1 // Rf =

R1 R f R1 Rf

R1, Assume RL = 10K

Rcomp = 1.5K

78

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

DESIGN PROCEDURE-(DIFFERENTIATOR):

Design an op-amp differentiator that will differentiate an input signal with fmax = 100HZ Select fa = fmax = 100 HZ = 1 / 2RFC1 Let C1 = 0.1F Then RF = 1 / 2(102 )(10-7 ) = 15.9K Now choose fb = 10fa = 1 / 2R1 C1 Therefore, R1 = 1 / 2(103 )(10-7 ) = 1.59K Since RFCF = R1 C1 We get, CF = (1.59*103 *10-7 ) / 15.9*103 = 0.01F

RESULT: Thus an Integrator and Differentiator using op-amp are designed and their performance was successfully tested using op-amp IC 741.

79

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGRAM:

CIRCUIT DIAGRAM:

80

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design a 4-bit R-2R ladder type DAC. APPARATUS REQUIRED: SL.NO 1 2 3 4 5 ITEMS IC 741 Voltmeter Dual Power Supply Resistor Bread Board RANGE (0-15)V (0-30)V 22K, 11K QUANTITY 1 1 1 7,3 1

THEORY: In R-2R ladder network only two values of resistors are required. Consider 4 bit DAC, where switch position d1,d2,d3,d4 corresponding to binary words. PROCEDURE: 1. 2. 3. 4. Connections are made as per the circuit diagram. The inputs are given through b0,b1,b2,b3. The inputs are given from (0-15)V and observe the outputs in voltmeter. The graph is drawn.

81

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TABULATION: Equivalent Binary Decimal b3 b2 b1 b0 Practical Voltage (V) Theoretical Voltage (V)

MODEL GRAPH:

82

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus digital to analog converter was constructed.

83

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

BASIC CIRCUIT OF A FLASH TYPE A/D CONVERTER:

84

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design an analog to digital converter and to study their performance characteristics. APPARATUS REQUIRED: SL.NO 1 2 3 4 5 ITEMS IC 741 LED Dual Power Supply Resistor Bread Board RANGE (0-30)V 10K QUANTITY 8 3 1 7 1

THEORY: The flash type analog to digital converter is considered. It is the fastest ADC. The circuit consists of a resistive divider network, eight op-amp comparators and an eight line to three line encoder. Since all the resistors are of equal value, the voltage levels available at the nodes are equally divided between the reference voltage Vr and the ground. The purpose of the circuit compares the analog input voltage Va with each of the node voltages. PROCEDURE: 1. The circuit connections are made as per the circuit diagram. 2. The analog input voltage, Va is varied and the corresponding digital output is obtained. 3. The graph is thus drawn.

85

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Voltage Input Va >Vd Va < Vd Va = Vd

Logic Output X=1 X=0 Previous Value

TRUTH TABLE FOR A FLASH TYPE A/D CONVERTER:

Input Voltage (Va) 0 to VR/8 VR/8 to VR/4 VR/4 to 3VR/8 3VR/8 to VR/2 VR/2 to 5VR/8 5VR/8 to 3VR/4 3VR/4 to 7VR/8 7VR/8 to VR

X7 0 0 0 0 0 0 0 1

X6 0 0 0 0 0 0 1 1

X5 0 0 0 0 0 1 1 1

X4 0 0 0 0 1 1 1 1

X3 0 0 0 1 1 1 1 1

X2 X1 X0 0 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Y2 0 0 0 0 1 1 1 1

Y1 0 0 1 1 0 0 1 1

Y0 0 1 0 1 0 1 0 1

86

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus an analog to digital converter is studied. 87

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM:

NE 565 PLL connection diagram

DESIGN PROCEDURE:If C= 0.01F and the frequency of input trigger signal is 2KHz, output pulse width of 555 in Monostable mode is given by 1.1RAC = 1.2T =1.2/f RA= 1.2/(1.1Cf)=54.5K fIN=fOUT /N Under locked conditions, fOUT = NfIN = 2fIN = 4KHz

88

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: To design & test the characteristics of PLL and to construct and test frequency multiplier using PLL IC565. APPARATUS REQUIRED: S.NO 1 2 3 IC 565 IC 555 RESISTORS COMPONENT VALUE ----12K,6.8K 0.01F 4 CAPACITORS 0.001f, 10f, 10f 5 6 7 8 DRB DUAL POWER SUPPLY CATHODE RAY OSCILLOSCOPE CONNECTING WIRES (0-10)M (0 -30)V (0 20MHz) --EACH 01 01 02 01 FEW QUANTITY 01 01 EACH 01

89

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PLL as Frequency Multiplier

(a): Input (b): PLL output under locked conditions without 555 (c): Output at pin4 of 565 with 555 connected in the feedback

90

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

Theory: The frequency divider is inserted between the VCO and the phase comparator of PLL. Since the output of the divider is locked to the input frequency fIN, the VCO is actually running at a multiple of the input frequency .The desired amount of multiplication can be obtained by selecting a proper divide by N network ,where N is an integer. To obtain the output frequency fOUT =2fIN, N = 2 is chosen. One must determine the input frequency range and then adjust the free running frequency fOUT of the VCO by means of R1 and C1 so that the output frequency of the divider is midway within the predetermined input frequency range. The output of the VCO now should be 2fIN . The output of the VCO should be adjusted by varying potentiometer R1 . A small capacitor is connected between pin7 and pin8 to eliminate possible oscillations. Also, capacitor C 2 should be large enough to stabilize the VCO frequency. SAMPLE READINGS: PARAMETER Amplitude (Vp-p ) Frequency (KHz) INPUT OUTPUT

PROCEDURE:1. The circuit is connected as per the circuit diagram. 2. Apply a square wave input to the pin2 of the 565 3. Observe the output at pin4 of 565 under locked condition. 4. Give the output of 565 to the pin2 of 555 IC. 5. Observe the output of 555 at pin3. 6. Now give the output of 555 as feedback to the pin5 of the 565. 7. Observe the frequency of output signal fo at pin4 of 565 IC. 8. Plot the waveforms in graph.

RESULT: Thus the PLL characteristics are designed and tested and Frequency multiplier using IC 565 is constructed and tested.

91

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM:

Fig1: Voltage Controlled Oscillator DESIGN: 1. Maximum deviation time period =T. 2. fmin = 1/T. where fmin can be obtained from the FM wave 3. Maximum deviation, f= fo - fmin 4. Modulation index = f/fm 5. Band width BW = 2(+1) fm = 2 (f+fm) 6. Free running frequency,fo = 2(VCC -Vc) / R1 C1 VCC

92

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

AIM: i) To observe the applications of VCO-IC 566 ii) To generate the frequency modulated wave by using IC 566 APPARATUS REQUIRED: S.No Equipment/Component Name 1 2 IC 566 Resistors 10K 1.5K 3 Capacitors 0.1 F 100 pF 4 5 6 Regulated power supply Cathode Ray Oscilloscope Function Generator 0-30 V, 1 A 0-20 MHz 0.1-1 MHz Specifications/Value Quantity 1 2 1 1 1 1 1 1

THEORY: The VCO is a free running Multivibrator and operates at a set frequency fo called free running frequency. resistor. This frequency is determined by an external timing capacitor and an external It can also be shifted to either side by applying a d.c control voltage vc to an The frequency deviation is directly proportional to the dc

appropriate terminal of the IC.

control voltage and hence it is called a voltage controlled oscillator or, in short, VCO. The output frequency of the VCO can be changed either by R1 , C1 or the voltage VC at the modulating input terminal (pin 5). The voltage VC can be varied by connecting a R1 R2 circuit. The components R1 and C1 are first selected so that VCO output frequency lies in the centre of the operating frequency range. Now the modulating input voltage is usually varied from 0.75 VCC which can produce a frequency variation of about 10 to 1.

93

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

WAVEFORMS:

Fig 2 (a): Input wave of VCO (b): Output of VCO at pin3 (c): Output of VCO at pin4 SAMPLE READINGS: VCC=+12V; R1 =R3 =10K; R2 =1.5K; fm=1KHz Free running frequency, fo = 26.1KHz fmin = 8.33KHz f= 17.77 KHz = f/fm = 17.77 Band width BW 36 KHz

94

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PROCEDURE: 1. The circuit is connected as per the circuit diagram shown in Fig1. 2. Observe the modulating signal on CRO and measure the amplitude and frequency of the signal. 3. Without giving modulating signal, take output at pin 4, we get the carrier wave. 4. Measure the maximum frequency deviation of each step and evaluate the modulating Index. mf = = f/fm

RESULT: Frequency modulated waveforms are observed and modulation Index, B.W required for FM is calculated for different amplitudes of the message signal.

95

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

ADDITIONAL EXPERIMENTS

96

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGARAM:

CIRCUIT DIAGRAM:

TABULATION: THEORITICAL Vo = (R f/R1 )(1+2R 2 /R G) (V1 -V2 ) (Volts) PRACTICAL VO (Volts)

S.No

V1 (Volts)

V2 (Volts)

1. 2.

97

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

INSTRUMENTATION AMPLIFIER

EXP.NO: 13 AIM: To construct an instrumentation amplifier using op-amp IC741. APPARATUS REQUIRED: S.NO 1. 2. 3. 4. 5. IC 741 RESISTORS DUAL POWER SUPPLY DIGITAL MULTIMETER CONNECTING WIRES COMPONENTS RANGE --1K. (0-30)V ----QUANTITY 03 07 02 01 FEW

THEORY: An instrumentation amplifier is the intermediate stage of a instrumentation system. The signal source of the instrumentation amplifier is the output of the transducer. Many transducers output do not have the ability or sufficient strength to drive the next following stages. Therefore, instrumentation amplifiers are used to amplify the low-level output signal of the transducer so that it can drive the following stages such as indicator or displays. The major requirements of a instrumentation amplifier are precise, low-level signal amplification where low-noise, low thermal and time drifts, high input resistance & accurate closed-loop gain, low power consumption, high CMRR & high slew rate for superior performance.

98

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PROCEDURE: 1. Select the entire resistor with same value of resistance R. Let RG be the gain varying resistor with different values of resistance for simplicity let RG, be a constant value. 2. Connect the circuit as shown in the circuit diagram. 3. Give the input V1 & v2 to the non-inverting terminals of first & second op-amp respectively. 4. By varying the value of V1 and V2 note the output voltage Vo .

RESULT: Thus an instrumentation amplifier was constructed tested using op-amp IC 741.

99

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

PIN DIAGARAM:

RC PHASE SHIFT OSCILLATOR:CIRCUIT DIAGRAM:-

TABULATION:. OBSERVED OUTPUT WAVEFORM Amplitude Time period Frequency (volts) (ms) (Hz)

Design Frequency (Hz)

100

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RC PHASE SHIFT AND WIEN BRIDGE OSCILLATOR USING OP-AMP

EXP.NO: 14 AIM: To design RC Phase Shift and Wien Bridge Oscillator using op-amp IC 741 and to test its performance. APPARATUS REQUIRED: S.NO 1. 2. 3. 4. 5. 6. 7. IC 741 RESISTORS CAPACITORS POT DUAL POWER SUPPLY CATHODE RAY OSCILLOSCOPE CONNECTING WIRES COMPONENTS RANGE --1.5K 15K 0.1f 1M,47K (0-30)V (0-20)MHz --QUANTITY 01 03 02 03 EACH 01 01 01 FEW

THEORY:(RC PHASE SHIFT OSCILLATOR) RC phase shift oscillator produces 360 of phase shift in two parts. Firstly, each and every RC pair in the feedback network produces 60 phase shift and totally there were three pairs, thus producing 180 Phase shift and secondly, the feedback input is given to the inverting terminal of op-amp to produce another 180 phase shift and a total phase shift of 360. The frequency of oscillation is given by f0 =

2 1 6 RC

; If an inverting amplifier is used,

the gain must be atleast equal to 29 to ensure the oscillations with constant amplitude that is,

AV

< 1. Otherwise the oscillation will die out.

THEORY :(WIEN BRIDGE) A bridge circuit with two components connected in series and parallel combination is used to archived the required of phase shift of 00. When the bridge is balanced the phase shift of 00 is achieved and the feedback signal is connected to the positive terminal; of Op-amp. So the Op-amp is acting as a non-inverting amplifier and the feedback network do not provide any phase shift. 101

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODEL GRAPH:

Vout

OUTPUT

Time (ms)

WIEN BRIDGE OSCILLATOR:CIRCUIT DIAGRAM:-

102

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

TABULATION: OBSERVED OUTPUT WAVEFORM Amplitude Time period Frequency (volts) (ms) (Hz)

Design Frequency (Hz)

The major drawback of wien bridge oscillator is difficulty in balancing the bridge circuit. This occurs because of drift in component values due to external and internal disturbances. The frequency of oscillation is given as f0 =

1 . 2 RC

PROCEDURE- (RC PHASE SHIFT): 1. Select the given frequency of oscillation f0 = 400Hz. 2. Assume either R or C to find out the other using formula f0 = . 2 6 RC 3. The gain is selected such that Rf / R1 = 29K. Assume Rf or R1 to find the other. 4. Connect the circuit as per as the circuit diagram. 5. Measure the amplitude frequency of the output signal plot the graph. WEIN BRIDGE OSCILLATOR: 1. Select the given frequency of oscillation f0 = 1 KHz. 2. Assume either R or C to find out the other using formula value of other components as given in design procedure. 3. Connect the circuit as per as the circuit diagram. 4. Measure the amplitude and frequency of the output signal to plot the graph.

1 . Also determine the 2 RC

103

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

MODEL GRAPH:

Vout

OUTPUT

Time (ms)

DESIGN : RC PHASE SHIFT OSCILLATOR: Design a RC phase shift oscillator to oscillate at 400Hz. 1. Select fo = 400Hz. 2. Assume C = 0.1f & determine R from fo. fo =

1 2 6 RC

=R=

1 2 6 f oc

= 1.6K Use (1.5K)

3. To prevent the loading of amp because it is necessary that R1>>10R. Therefore R1=10R=15K. 4. At this frequency the gain must be atleast 29 (i.e)Rf / R1 =29. Therefore Rf = 29R1. Rf = 29 (15K) = 435K.(Use 1M Pot)

WEIN BRIDGE OSCILLATROR: (i) (ii) (iii) Select frequency f0 = 1KHz. 1 Use f0 = , A = 1+(Rf / R1 ) = 3. To find R & Rf. 2 RC Therefore Rf = 2R1 & assume C = 0.1f & find R from 1 R= = 1.59K. 2 f oC Assume R1 = 10R & find Rf from Rf = 2R1 Therefore R1 = 15K Rf = 30 (Use 47K Pot)

(iv)

104

DMI College of Engineering

131452-Linear and Digital Integrated Circuits.

Dept of Electronics & Communication Engg

RESULT: Thus RC Phase Shift and Wien Bridge Oscillator were designed and tested using op-amp IC 741. 105

DMI College of Engineering

You might also like

- Theoretical Frame Work of Performance AppraisalDocument54 pagesTheoretical Frame Work of Performance AppraisalDhamo Daran100% (2)

- Program and OutputDocument38 pagesProgram and OutputDhamo DaranNo ratings yet

- CirDocument1 pageCirDhamo DaranNo ratings yet

- Lab 1 6 PDFDocument14 pagesLab 1 6 PDFDhamo DaranNo ratings yet

- Di'Ii: E) IgiiieeriiigDocument49 pagesDi'Ii: E) IgiiieeriiigDhamo DaranNo ratings yet

- Bmi AssignmentsDocument5 pagesBmi AssignmentsDhamo DaranNo ratings yet

- Di (I RQ: Capc"O"Document15 pagesDi (I RQ: Capc"O"Dhamo DaranNo ratings yet

- Wireless Power Transmission: Click To Edit Master Subtitle StyleDocument39 pagesWireless Power Transmission: Click To Edit Master Subtitle StyleDhamo DaranNo ratings yet

- PhotographyDocument5 pagesPhotographyDhamo DaranNo ratings yet

- EE2252 Unit 1Document25 pagesEE2252 Unit 1amsk24_24No ratings yet

- Data Structures and Algorithms Lab EeeDocument71 pagesData Structures and Algorithms Lab EeeDhamo DaranNo ratings yet

- Dhamu - All Progromes Batch-1Document60 pagesDhamu - All Progromes Batch-1Dhamo DaranNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- ECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Document23 pagesECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Phoebe MensahNo ratings yet

- Active and Passive FiltersDocument11 pagesActive and Passive FiltersHemanshu DasNo ratings yet

- Norton's Theorem Simplifies CircuitsDocument3 pagesNorton's Theorem Simplifies CircuitsPankaj Dhariwal PipliNo ratings yet

- Measurements & Electronic Instruments Laboratory Experiment ManualDocument3 pagesMeasurements & Electronic Instruments Laboratory Experiment Manualfirst lastNo ratings yet

- ELEC 2147 Electrical Energy Technology: AC Circuit IIDocument25 pagesELEC 2147 Electrical Energy Technology: AC Circuit IIKa Hei Ernest HoNo ratings yet

- Digital Circuits - Understanding Multiplexers and DemultiplexersDocument13 pagesDigital Circuits - Understanding Multiplexers and Demultiplexerstareq omarNo ratings yet

- 555 Timer PinoutDocument1 page555 Timer PinoutframirezbNo ratings yet

- Self-Oscillating Half-Bridge Driver Preliminary Data SheetDocument9 pagesSelf-Oscillating Half-Bridge Driver Preliminary Data Sheetamijoski6051No ratings yet

- Bfu590G Ism 433 MHZ Pa Design: Rev. 1 - 16 June 2014 Application NoteDocument23 pagesBfu590G Ism 433 MHZ Pa Design: Rev. 1 - 16 June 2014 Application NoteAero RanjithNo ratings yet

- Ap89042 VoiceDocument19 pagesAp89042 VoicevizordNo ratings yet

- 3.4-TESTER DE PULSOS DIGITALES 1-0-PULSOS Fabricado Con NANDDocument2 pages3.4-TESTER DE PULSOS DIGITALES 1-0-PULSOS Fabricado Con NANDDavid molinaNo ratings yet

- LM324 Comparador de Voltaje Nte987Document3 pagesLM324 Comparador de Voltaje Nte987criman45No ratings yet

- Logic Inverter ExperimentDocument6 pagesLogic Inverter Experimentxoxoxoxox11No ratings yet

- VHDL CODES AND DIGITAL CIRCUITSDocument4 pagesVHDL CODES AND DIGITAL CIRCUITSSiva GuruNo ratings yet

- 7 Segment Led Based Spi Display Using 74hc595Document2 pages7 Segment Led Based Spi Display Using 74hc595Emin KültürelNo ratings yet

- Moore's Law Transistor Growth and Dennard ScalingDocument14 pagesMoore's Law Transistor Growth and Dennard Scalingshreyas nNo ratings yet

- Chapter 8 - Voltage RegulatorDocument18 pagesChapter 8 - Voltage RegulatorMuhammad AliNo ratings yet

- Tea5570 Philips Data SheetDocument19 pagesTea5570 Philips Data Sheetarizona976No ratings yet

- Design and Implementation of 8 Bit Barrel Shifter Using 2:1 Multiplexer in VerilogDocument4 pagesDesign and Implementation of 8 Bit Barrel Shifter Using 2:1 Multiplexer in VerilogEraj MasoodNo ratings yet

- Chapter 6Document46 pagesChapter 6uchihaitachi1394100% (1)

- Lab Report 04Document4 pagesLab Report 04Mehmood Khan Marwat100% (1)

- Astable & Monostable Multivibrator CircuitsDocument4 pagesAstable & Monostable Multivibrator CircuitsJiva 1107No ratings yet

- Analogue Report Common Emitter AmplifierDocument5 pagesAnalogue Report Common Emitter Amplifierfedley sikoliaNo ratings yet

- Kirchhoff's Law & Millman's TheoremDocument18 pagesKirchhoff's Law & Millman's Theoremjankarlo123100% (1)

- LED Temperature Thermometer ProjectDocument3 pagesLED Temperature Thermometer Projectbhk_bdbhatt4424100% (3)

- Hartley OscillatorDocument3 pagesHartley OscillatorJunaid AleemNo ratings yet

- Timing DocumentationDocument14 pagesTiming DocumentationÆshok IncreĐible KingNo ratings yet

- Sequential Circuits: Output Is DependentDocument66 pagesSequential Circuits: Output Is DependentSiddharth SharmaNo ratings yet

- EEE Job PreparationDocument12 pagesEEE Job Preparationpinare2193No ratings yet