Professional Documents

Culture Documents

M 011

Uploaded by

ChellakaruppasamyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

M 011

Uploaded by

ChellakaruppasamyCopyright:

Available Formats

M 011

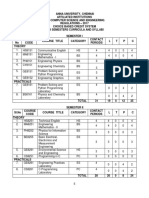

MODEL PAPER B.E. DEGREE EXAMINATION. Fourth Semester Electronics and Communication Engineering EC 244 LINEAR INTEGRATED CIRCUITS Time : Three hours Answer ALL questions. PART A (10 2 = 20 marks) 1. With reference to an OP AMP, define supply voltage rejection ratio. 2. In response to a square wave input, the output of an OP AMP changed from 3V to +3V over a time interval of 0.25 s. Determine the slew rate of the OP AMP. 3. State the important features of an instrumentation amplifier. 4. Using an OP AMP, draw the circuit diagram of a phase shift oscillator. 5. What is a two quadrant multiplier? 6. With reference to a PLL, define Pull in Time. 7. The basic step of a 9 bit DAC is 103 mV. If 000000000 represents 0V, what is the output for an input of 101101111? 8. Why does the dual slope ADC provide excellent noise rejection of AC signals whose periods are integral multiples of the integration time? 9. Using a 555, draw the circuit diagram of an astable multivibrator. Maximum : 100 marks

10.State the limitations of linear voltage regulators. PART B (5 16 = 80 marks) 11.Draw the circuit diagram of a symmetrical emitter coupled difference amplifier and derive an expression for the difference mode gain Ad and the common mode gain Ac. 12.(a) Design a fourth order Butterworth low pass filter having a upper cutoff frequency of 1 KHz. Or (b) Design a square wave oscillator for f0 = 1 KHz using 741 OP AMP and a DC supply voltage of 12 V. Draw the basic block diagram of a 566 VCO and derive an expression for the VCO output frequency. Or (b) Using neat sketches, explain how a PLL can be used as (i) a frequency translator and (ii) a AM demodulation. Draw and explain the functional diagram of the successive approximation A/D converter. Or (b) A dual slope ADC uses a 16 bit counter and a 4 MHZ clock rate. The maximum input voltage is +10 V. The maximum integrator output voltage should be 8V when the counter has cycled through zn counts. The capacitor used in the integrator is 0.1 F . Find the value of the resistor R of the integrator. If the analog signal is +4.129 V, find the corresponding binary number. (i) Draw a neat sketch showing the noise voltage and noise current characteristics of the OP27/37 op. amp.

13.(a)

14.(a)

15.(a) (ii)

Show that the figures of merit in op amp noise performance are the white noise floors enw and i nw and the corner frequencies fce and fci . Or

(b)

Write short notes on : (i) (ii) Power op amps. Fiber optic ICs.

(iii) Optocouplers. 2

M 011

You might also like

- Install NotesIF Not WorkingIF Not WorkingIF Not WorkingIF Not WorkingDocument2 pagesInstall NotesIF Not WorkingIF Not WorkingIF Not WorkingIF Not WorkingChellakaruppasamyNo ratings yet

- Install, Start, Log in With A Fake Account, and Start The Trial Version. Close The Program and Apply The CrackDocument1 pageInstall, Start, Log in With A Fake Account, and Start The Trial Version. Close The Program and Apply The CrackChellakaruppasamyNo ratings yet

- Quotation For 640kg Boiler Automatic PlantDocument2 pagesQuotation For 640kg Boiler Automatic PlantChellakaruppasamyNo ratings yet

- Template For First Investor PitchDocument14 pagesTemplate For First Investor PitchChellakaruppasamyNo ratings yet

- Locus Exim Proposal - 2.TPDDocument14 pagesLocus Exim Proposal - 2.TPDChellakaruppasamyNo ratings yet

- Vajarahalli Volume I Technical Bid PDFDocument123 pagesVajarahalli Volume I Technical Bid PDFChellakaruppasamyNo ratings yet

- World Cashew Nuts - Market Report. Analysis and Forecast To 2025Document37 pagesWorld Cashew Nuts - Market Report. Analysis and Forecast To 2025ChellakaruppasamyNo ratings yet

- Cse Syllabus First YearDocument15 pagesCse Syllabus First Year1balamanianNo ratings yet

- No Load and Load Test On A DC Shunt GeneratorDocument3 pagesNo Load and Load Test On A DC Shunt GeneratorHazoorAhmadNo ratings yet

- BSNL Recruitment for JTO Posts via GATE 2017 ScoreDocument1 pageBSNL Recruitment for JTO Posts via GATE 2017 ScoreChellakaruppasamyNo ratings yet

- Term and ConditionsDocument4 pagesTerm and ConditionsMahendran MaheNo ratings yet

- Payment receipt for Tamilnadu electricity bill from December 2016Document1 pagePayment receipt for Tamilnadu electricity bill from December 2016ChellakaruppasamyNo ratings yet

- Kaju Summit - e BrochureDocument3 pagesKaju Summit - e BrochureChellakaruppasamyNo ratings yet

- Districtwise CollegesDocument7 pagesDistrictwise CollegesChellakaruppasamyNo ratings yet

- Bank lease for office spaceDocument5 pagesBank lease for office spaceRamesh BabuNo ratings yet

- CarWale - EMI ScheduleDocument2 pagesCarWale - EMI ScheduleChellakaruppasamyNo ratings yet

- Tirunelveli IPODocument6 pagesTirunelveli IPOChellakaruppasamyNo ratings yet

- 23Document70 pages23ChellakaruppasamyNo ratings yet

- CH 4Document5 pagesCH 4ChellakaruppasamyNo ratings yet

- KAJU SUMMIT Registration FormDocument4 pagesKAJU SUMMIT Registration FormChellakaruppasamyNo ratings yet

- Manual-CSMDocument23 pagesManual-CSMChellakaruppasamyNo ratings yet

- Components of Project Report: Part-IDocument5 pagesComponents of Project Report: Part-IVayu PuthraNo ratings yet

- N Approved Documen ProcessingDocument1 pageN Approved Documen ProcessingChellakaruppasamyNo ratings yet

- CH 4Document5 pagesCH 4ChellakaruppasamyNo ratings yet

- கை ரேகை பலன்கள் PDFDocument1 pageகை ரேகை பலன்கள் PDFChellakaruppasamyNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentChellakaruppasamyNo ratings yet

- ReferenceDocument2 pagesReferenceChellakaruppasamyNo ratings yet

- Cashew ProcessingDocument4 pagesCashew ProcessingDg CharpeNo ratings yet

- Needs Scheme GoDocument13 pagesNeeds Scheme GoKhalif Ahamed UsmanNo ratings yet

- Student Payment Guide - 0809Document2 pagesStudent Payment Guide - 0809ChellakaruppasamyNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Rm0038 Reference Manual: Stm32L100Xx, Stm32L151Xx, Stm32L152Xx and Stm32L162Xx Advanced Arm-Based 32-Bit McusDocument859 pagesRm0038 Reference Manual: Stm32L100Xx, Stm32L151Xx, Stm32L152Xx and Stm32L162Xx Advanced Arm-Based 32-Bit McusGANGISETTI SATYA KRISHNA,Mtech2021 Vel Tech, ChennaiNo ratings yet

- Logic Circuits Midterm ReviewerDocument38 pagesLogic Circuits Midterm ReviewerHector Ledesma IIINo ratings yet

- Lab Exercise Design of Active FiltersDocument3 pagesLab Exercise Design of Active Filtersmrana_56100% (2)

- Lec - A-03 - Introduction To Digital Logic and Boolean Algebra 1920Document112 pagesLec - A-03 - Introduction To Digital Logic and Boolean Algebra 1920hbfagfjafasebaNo ratings yet

- Automatic Hand Dryer: May Lwin Thant Khine Myint Mon, Khin Thandar TunDocument4 pagesAutomatic Hand Dryer: May Lwin Thant Khine Myint Mon, Khin Thandar TunSamuel OlusanyaNo ratings yet

- FENDER SR 6520-8520PD-11x17Document12 pagesFENDER SR 6520-8520PD-11x17Vital Juan LuisNo ratings yet

- Digital Logic Circuit Design Combinational Logic Circuits Test QuestionsDocument12 pagesDigital Logic Circuit Design Combinational Logic Circuits Test Questionspavithra.jNo ratings yet

- Lect 4 BJT AC Analysis (Common Emitter Amplifier ACDocument13 pagesLect 4 BJT AC Analysis (Common Emitter Amplifier ACTan Chiang LiNo ratings yet

- UGN3055 DatasheetDocument8 pagesUGN3055 DatasheetMiguel Angel ReyesNo ratings yet

- 4-Phase Adiabatic Logic Design VHDLDocument24 pages4-Phase Adiabatic Logic Design VHDLLakshmi Sri K VNo ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument7 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetjoeNo ratings yet

- Capacitance Adapter For Multimeter: (Document Subtitle)Document11 pagesCapacitance Adapter For Multimeter: (Document Subtitle)Kashif Hassan100% (1)

- 10 ways to fix SETUP and HOLD violationsDocument6 pages10 ways to fix SETUP and HOLD violationsAbhi AggarwalNo ratings yet

- Yaesu FT 2900R Service ManualDocument0 pagesYaesu FT 2900R Service ManualRobert/YG2AKRNo ratings yet

- Eet202/3 Digital Electronics Ii Tutorial 4Document13 pagesEet202/3 Digital Electronics Ii Tutorial 4HaroonRashidNo ratings yet

- 74 HCT 148Document11 pages74 HCT 148Merényi OszkárNo ratings yet

- 8-Channel, High Throughput, 24-Bit Sigma-Delta ADC: Data SheetDocument32 pages8-Channel, High Throughput, 24-Bit Sigma-Delta ADC: Data SheetPravin RautNo ratings yet

- FPGA DS 02056 3 9 MachXO2 Family Data SheetDocument122 pagesFPGA DS 02056 3 9 MachXO2 Family Data Sheetthe hoangNo ratings yet

- PCOMDocument8 pagesPCOMShreejith NairNo ratings yet

- Lab Report 10 - The Inductive DC-DC Converter: 1 Luiz Augusto Frazatto Fernandes 2 Yasmim de SouzaDocument3 pagesLab Report 10 - The Inductive DC-DC Converter: 1 Luiz Augusto Frazatto Fernandes 2 Yasmim de SouzaYasmim de SouzaNo ratings yet

- MOSFET Amplifier BasicsDocument18 pagesMOSFET Amplifier BasicsHarsha BalamNo ratings yet

- PIC18F2423Document392 pagesPIC18F2423Thanh Minh HaNo ratings yet

- Non-Isolated Buck Offline LED Driver Description FeaturesDocument2 pagesNon-Isolated Buck Offline LED Driver Description FeaturesAlberto100% (1)

- Basic Vlsi Design ContentsDocument6 pagesBasic Vlsi Design ContentsrdnanduNo ratings yet

- 16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortDocument28 pages16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortParth VijayNo ratings yet

- SN74LS14NDocument4 pagesSN74LS14Nanon_386717813No ratings yet

- Datasheet DC MotorDocument9 pagesDatasheet DC MotorKosala KapukotuwaNo ratings yet

- CTR201Document2 pagesCTR201Vicente RezabalaNo ratings yet

- FPGADocument20 pagesFPGANanda Ganesh Kumar KingNo ratings yet

- Biodata Sonification DiapjDocument1 pageBiodata Sonification DiapjGandhi WasuvitchayagitNo ratings yet