Professional Documents

Culture Documents

Digital Electronics and Computer Organization

Uploaded by

Sai Prajwal SavanamOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics and Computer Organization

Uploaded by

Sai Prajwal SavanamCopyright:

Available Formats

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI, HYDERABAD CAMPUS INSTRUCTION DIVISION, FIRST SEMESTER 2011-12 COURSE HANDOUT

(PART-II)

Date: 02/08/2010 In addition to Part I (General Handout for all the courses appended to the time table), this portion gives further specific details regarding the course. Course No. Course Title Instructor-in-charge Team of Instructors (i) For Lecture (ii) For Tutorial (ii) For Practical Course Description CS C391/EEE C391/ECE C391 Digital Electronics and Computer Organization P.S.SAIKRISHNA PS SaiKrishna, Prof. Moorthy Muthukrishnan Madhuri Bayya,T Haripriya, V.Srihari, Subha Madha, Saikrishna PS M.Subha, P.S.Saikrishna, V.Srihari, Anantha saradhi This course covers the topics on logic circuits and minimization, Combinational and sequential logic circuits, Programmable Logic devices, State table and state diagrams, Digital ICs, Arithmetic operations and algorithms, Introduction to Computer organization, Algorithmic State Machines The objective of the course is to impart knowledge of the basic tools for the design of digital circuits and to provide methods and procedures suitable for a variety of digital design applications. The course also introduces fundamental concepts of computer organization. The course also provides laboratory practice using MSI devices.

Scope and Objective

Text Books. : T1: M.Moris Mano and Michael D. Ciletti Digital Design, PHI, 4th Edition, 2007 T2: G Raghurama, , TSB Sudharshan Introduction to Computer Organization. EDD notes 2007 T3: G Raghurama, S & Others Experiments in Digital Electronics, EDD notes 2007.

Reference Books: R1: Donald D. Givonne ., Digital Principles and Design TMH, 2003 Course Plan. Lect. Learning Objectives No. 1 Introduction to Digital Systems and Characteristics of Digital ICs.

Topics to be covered Digital Systems, Digital ICs

Reference to Text Book 1.1; 1.9; 2.3, 10.1,2

2.

3-5 6

Boolean algebra and logic gates, Codes number systems Simplification of Boolean functions Simulation and synthesis basics Combinational Logic, Arithmetic circuits Sequential Logic Digital Integrated Circuits MSI Components Simulation of Combinational Logic Functions. Memory and PLDs Clocked Sequential Circuits Simulation of Sequential Logic Functions. Registers & Counters Analysis of arithmetic units Modular approach for CPU Design Design of Digital Systems Design of Asynchronous Circuits. Memory Organization

Boolean functions Canonical forms, number systems and codes K-Maps (4,5 variables), QM Method Hardware Description Language Adders, Subtracters Multipliers Flip-Flops & Characteristic tables, Latches. TTL, MOS Logic families and their characteristics Comparators, Decoders, Encoders, MUXs, DEMUXs HDL for Combinational Logic RAM, ROM, PLA, PAL Analysis of clocked sequential circuits, state diagram and reduction HDL for Sequential Logic

1.2-7, 2.4-2.9

3.1 to 3.8 3.11

7-9

4.1 - 4-7

10-11 12-14 15-16 17

5.1 to 5.4 10.3, 10.5, 10.7 to 10.10 4.8 to 4.11 4.12

18-20 21-22

7.2, 7.5 to 7.7 5.5, 5.7

23

5.6

24-25 26-27 28-31 32-34 35-37 38-40

Shift registers, Synchronous & Asynchronous counters Multiplication & Division algorithms RTL, HDL description Algorithmic State Machines Asynchronous Sequential Logic Memory Hierarchy & different types of memories

6.1 to 6.5 T2: Appendix A 8.1,8.2, 8.4 to 8.8 R1. Chapter 8 9.1 9.4 T2: Ch 6

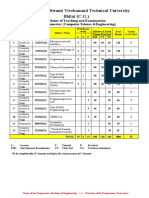

Evaluation Scheme: Component Test 1

Duration Maximum Marks 50 mins 40

Date & Time 05/09 11.00 11.50 AM 3/10 11.00 11.50 AM

Remarks CB

Test 2

50 mins

40

OB

Quiz

50 mins

40

Comprehensive Examination Practicals: Regularity, Lab reports Lab test & Viva

3 Hrs

100 40

7/11 11.00 11.50 AM 07/12 AN To be announced

CB

CB To be announced

40

To be announced

(b) Practicals (From T3.) S.No.

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12.

Name of experiment

FAMILIARIZATION OF BENCH EQUIPMENTS IMPLEMENTATION OF BOOLEAN FUNCTIONS USING LOGIC GATES OPERATION OF 4-BIT COUNTER ADDERS AND SUBTRACTORS BCD ADDER DECODERS, MULTIPLEXERS AND DEMULTIPLEXERS LATCHES & FLIP-FLOPS COMPARATORS & ARITHMETIC LOGIC UNIT COUNTERS SHIFT REGISTERS SEQUENTIAL CIRCUITS MEMORIES AND FPGAS

Surprise Quiz: The Surprise quizzes will be conducted in the tutorial class. There will be no make-up for the same. Make-up Policy: There will no make-ups unless for genuine reasons. Prior permission is to be taken. Chamber Consultation Hour: To be announced in class Notices: All notices will be displayed on the LTC and EEE/ECE notice boards.

Instructor-in-charge,

CS C391/EEE C391/ECE C391

You might also like

- Digital Design EEE F215 HandoutDocument3 pagesDigital Design EEE F215 HandoutHarshilGargNo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Handout 2016 PDFDocument4 pagesHandout 2016 PDFShubham RohilaNo ratings yet

- Models and Analysis for Distributed SystemsFrom EverandModels and Analysis for Distributed SystemsSerge HaddadNo ratings yet

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- CMSC 130 SyllabusDocument2 pagesCMSC 130 SyllabusamamNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- DDDocument3 pagesDDJAY JANAK MANEKNo ratings yet

- De Teaching Plan-13Document3 pagesDe Teaching Plan-13toshgangwarNo ratings yet

- Bits PilaniDocument3 pagesBits PilaniasdmddamcNo ratings yet

- Sem 3Document15 pagesSem 3arpita sarkarNo ratings yet

- BE Syllabus Chandigarh UniversityDocument114 pagesBE Syllabus Chandigarh Universitykashishbhatia50% (2)

- Applicable From The Academic Session 2020-2021Document15 pagesApplicable From The Academic Session 2020-2021Subhashree BasuNo ratings yet

- 4) Demp - Wase & WimsDocument8 pages4) Demp - Wase & WimsRashmitha RavichandranNo ratings yet

- Lec - A-01 - Number Systems and CodesDocument97 pagesLec - A-01 - Number Systems and Codescys96No ratings yet

- 3.1 Operating Systems (Os) : (Common With Information Technology)Document16 pages3.1 Operating Systems (Os) : (Common With Information Technology)Gurbhej PannuNo ratings yet

- Total Lecture Classes Available: 39 Total Tutorial Classes Available: 00Document6 pagesTotal Lecture Classes Available: 39 Total Tutorial Classes Available: 00Julie RichardsonNo ratings yet

- National Institute of Technology Calicut: Department of Computer EngineeringDocument45 pagesNational Institute of Technology Calicut: Department of Computer EngineeringmayankNo ratings yet

- B. Tech. (CSE) 2 Year/ 3 Semester Course Structure and Syllabus For 2019 - 20Document38 pagesB. Tech. (CSE) 2 Year/ 3 Semester Course Structure and Syllabus For 2019 - 20Adhara MukherjeeNo ratings yet

- BEE4413 Digital Signal ProcessingDocument3 pagesBEE4413 Digital Signal Processingdinie90No ratings yet

- Digital Design: Cs/Eee/Ece /instr F215Document34 pagesDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNINo ratings yet

- Panjab University, Chandigarh: Syllabi of First Year Courses in B.E. (Computer Science and Engineering)Document32 pagesPanjab University, Chandigarh: Syllabi of First Year Courses in B.E. (Computer Science and Engineering)Anonymous t97R3yqNo ratings yet

- Wolaita Sodo University: College of EngineeringDocument3 pagesWolaita Sodo University: College of Engineeringnandakishore.nallaNo ratings yet

- Course Outline Logic Circuits and Switching TheoryDocument2 pagesCourse Outline Logic Circuits and Switching TheorySravan KumarNo ratings yet

- Final CSE V Semester New SyllabusDocument13 pagesFinal CSE V Semester New Syllabussaurabh303No ratings yet

- B.tech 5th Sem ECE FinalDocument13 pagesB.tech 5th Sem ECE FinalamanahmedaecNo ratings yet

- ECE CSESyllabusDocument42 pagesECE CSESyllabusVivekNo ratings yet

- Ece103 Digital-logic-Design Eth 1.10 Ac29Document2 pagesEce103 Digital-logic-Design Eth 1.10 Ac29netgalaxy2010No ratings yet

- EC2101 SyllabusDocument2 pagesEC2101 SyllabusabhisheknkarNo ratings yet

- 7.CS6201 - DPSDDocument160 pages7.CS6201 - DPSDNitinchandra HegadeNo ratings yet

- BcasndtDocument38 pagesBcasndtPrakash DabhadeNo ratings yet

- (Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Computer Science & EngineeringDocument17 pages(Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Computer Science & EngineeringSoumyaratna DebnathNo ratings yet

- Lesson Plan: R.V. College of Engineering, BangaloreDocument14 pagesLesson Plan: R.V. College of Engineering, BangaloreVeena Divya KrishnappaNo ratings yet

- Iit KGP Cse SyllabusDocument47 pagesIit KGP Cse SyllabussayakjuNo ratings yet

- SCHEME (2013-2014) B.E .CSE 3Rd Semester S.No Subject Code Subject Name Hours Per Week Marks CreditsDocument78 pagesSCHEME (2013-2014) B.E .CSE 3Rd Semester S.No Subject Code Subject Name Hours Per Week Marks Creditsmanish0202No ratings yet

- Btech Syllabus Copy2 LatestDocument152 pagesBtech Syllabus Copy2 LatestShivam VishwakarmaNo ratings yet

- DEMPDocument294 pagesDEMPLALLINo ratings yet

- Attachment Circular 2023081115025923 Ic 001Document9 pagesAttachment Circular 2023081115025923 Ic 001shivam.cs667No ratings yet

- (Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Computer Science & EngineeringDocument17 pages(Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Computer Science & EngineeringWater VapourNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument4 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaNo ratings yet

- (Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Information TechnologyDocument17 pages(Applicable From The Academic Session 2018-2019) : Syllabus For B. Tech in Information Technologyamit phadikarNo ratings yet

- B.Sc. (H) Computer Science 3-Year Full Time Programme: Rules, Regulations and Courses ContentsDocument20 pagesB.Sc. (H) Computer Science 3-Year Full Time Programme: Rules, Regulations and Courses ContentspasyanteeNo ratings yet

- INSTRUCTION SET OF 8086: Data Transfer and ArithmeticDocument18 pagesINSTRUCTION SET OF 8086: Data Transfer and ArithmeticMallik KglNo ratings yet

- FMTC0302 - Lesson Plan COADocument8 pagesFMTC0302 - Lesson Plan COAdarshankumar999No ratings yet

- Lecture PlanDocument1 pageLecture Planlaviniaandronicus9No ratings yet

- R18B Tech CSE (SoftwareEngineering) IIYearSyllabus1Document34 pagesR18B Tech CSE (SoftwareEngineering) IIYearSyllabus1David JesusNo ratings yet

- 2nd SemDocument18 pages2nd SemSuman Raj SharmaNo ratings yet

- VIT CSE BTech Course PlanDocument76 pagesVIT CSE BTech Course PlanApoorv Krishak50% (2)

- CS 4th Semester SyllabusDocument13 pagesCS 4th Semester SyllabusManish KumarNo ratings yet

- CseDocument71 pagesCseDileep ShuklaNo ratings yet

- Course: Core Paper VII - : HPHCR3072T & HPHCR3072PDocument3 pagesCourse: Core Paper VII - : HPHCR3072T & HPHCR3072PAdhara MukherjeeNo ratings yet

- PTU B.tech CSE 5th Sem SyllabusDocument84 pagesPTU B.tech CSE 5th Sem SyllabusJasmine SinghNo ratings yet

- Instructor-in-Charge: (Section - 1)Document70 pagesInstructor-in-Charge: (Section - 1)ravi3192No ratings yet

- 2020 BTech Syllabus Part IDocument24 pages2020 BTech Syllabus Part IVivekNo ratings yet

- Department of Computer Science & Engineering: National Institute of Technology, Hamirpur (HP) - 177005Document61 pagesDepartment of Computer Science & Engineering: National Institute of Technology, Hamirpur (HP) - 177005ankesh45No ratings yet

- Diploma III Year (COMPUTER EGG.) : 2012-2013 SubjectsDocument22 pagesDiploma III Year (COMPUTER EGG.) : 2012-2013 SubjectsVijay GarsaNo ratings yet

- Scheme Syllabi of B.tech - 2nd Year ITDocument35 pagesScheme Syllabi of B.tech - 2nd Year ITTanisha 12B2 9No ratings yet

- Playstation (Console) : Manufacturer Product Family Type Generation Retail Availability PlaystationDocument22 pagesPlaystation (Console) : Manufacturer Product Family Type Generation Retail Availability Playstationro_venancioNo ratings yet

- Decision Making and LoopingDocument13 pagesDecision Making and LoopingVinothini100% (1)

- MSI RTX3070 V390 PG142-B00 Rev 1.0Document54 pagesMSI RTX3070 V390 PG142-B00 Rev 1.0fremerc93No ratings yet

- ATU-100 Mini User Manual EngDocument12 pagesATU-100 Mini User Manual EngFlorin Nicola100% (1)

- ABB Industrial Drives: ACS850, Drive Modules, 1 To 600 HP / 1.1 To 500 KWDocument24 pagesABB Industrial Drives: ACS850, Drive Modules, 1 To 600 HP / 1.1 To 500 KWMohan ShanmugamNo ratings yet

- App AssignmentDocument8 pagesApp AssignmentacasNo ratings yet

- Game CrashDocument38 pagesGame Crashkristopher GuerreroNo ratings yet

- Use of Social MediaDocument61 pagesUse of Social MediaBaba HeadquaterNo ratings yet

- Et200sp Ai 4xi 2 4 Wire ST Manual en-US en-USDocument30 pagesEt200sp Ai 4xi 2 4 Wire ST Manual en-US en-USNicolas Rodríguez NietoNo ratings yet

- 14 BergegrDocument38 pages14 BergegrJohnyLampNo ratings yet

- Understanding Time Delay Relay FunctionsDocument6 pagesUnderstanding Time Delay Relay FunctionsAndrew BullNo ratings yet

- LiteWave Switch DatasheetDocument3 pagesLiteWave Switch Datasheetpaul esparagozaNo ratings yet

- Quotation: Administrative Details Your ReferencesDocument3 pagesQuotation: Administrative Details Your ReferencesMichelangelo VetrugnoNo ratings yet

- Networking Devices and Networking Topologies PDFDocument25 pagesNetworking Devices and Networking Topologies PDFAli AlwesabiNo ratings yet

- Capacitive Discharge Ignition: Application NoteDocument9 pagesCapacitive Discharge Ignition: Application NoteEnesNo ratings yet

- 10-100kVA ATLAS3000 USER MANUAL-UpdatedDocument37 pages10-100kVA ATLAS3000 USER MANUAL-UpdatedAlwyn GeorgeNo ratings yet

- QuotationDocument1 pageQuotationRavendran KrishnanNo ratings yet

- A Simplified SVPWM Control Strategy For PV InverterDocument5 pagesA Simplified SVPWM Control Strategy For PV InverterRodovarNo ratings yet

- Camilamoreira It ResumeDocument1 pageCamilamoreira It Resumeapi-301890226No ratings yet

- Panasonic Plasma FHD TV S & ST Series Technical Guide 2013Document111 pagesPanasonic Plasma FHD TV S & ST Series Technical Guide 2013edsel72100% (3)

- Microservices and Containerization 1663200052Document55 pagesMicroservices and Containerization 1663200052Henry MarkinaNo ratings yet

- OSI Reference ModelDocument12 pagesOSI Reference ModelpavalbharathiNo ratings yet

- Online Ups: ME-1000-FTU ME-2000-FTU ME-3000-FTU ME-6000-FTUDocument2 pagesOnline Ups: ME-1000-FTU ME-2000-FTU ME-3000-FTU ME-6000-FTUtrdNo ratings yet

- Start: Soldering - Solderen - Soudage - Löten - Soldadura - Lödning - Juottami Nen - Saldatura - SoldaDocument1 pageStart: Soldering - Solderen - Soudage - Löten - Soldadura - Lödning - Juottami Nen - Saldatura - SoldaGABRIEL MNo ratings yet

- Sales Force Apex Language ReferenceDocument520 pagesSales Force Apex Language ReferenceCharan TejaNo ratings yet

- Block Diagram of Digital ComputerDocument12 pagesBlock Diagram of Digital ComputerpunithNo ratings yet

- AT25SF128A 85C Data Sheet RevD 03-19-2019Document56 pagesAT25SF128A 85C Data Sheet RevD 03-19-2019Hans ClarinNo ratings yet

- Datasheet Cisco GS7000Document7 pagesDatasheet Cisco GS7000jorwyonNo ratings yet

- Info Tech Summary of Lesson 1 Grade 10Document2 pagesInfo Tech Summary of Lesson 1 Grade 10Kenya LevyNo ratings yet

- L. D. College of Engineering Lab Manual: System Software (3160715)Document53 pagesL. D. College of Engineering Lab Manual: System Software (3160715)Suraj MulchandaniNo ratings yet