Professional Documents

Culture Documents

A System Design For UHF RFID Reader

Uploaded by

30f4011Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A System Design For UHF RFID Reader

Uploaded by

30f4011Copyright:

Available Formats

A System Design for UHF RFID Reader

Chen Ying

College of Communication

Hangzhou Dianzi University

Hangzhou, China

chenyinghziee@yahoo.com.cn

Zhang Fu-hong

College of Communication

Hangzhou Dianzi University

Hangzhou, China

fuhong@vip.sina.com

AbstractThis paper introduces a system design for RFID reader.

The RFID reader is compatible with EPC Class-1, Generation-2

Standard, operating at the 915MHz band. The UHF RFID reader

includes RF analog front end (AFE), the base band design and

clock control. The RFID RF AFE contains transmitting circuit

receiving circuitfrequency synthesize, circulator, etc. The base

band contains the FPGA chip, 100M hardware resources of

network supporting, DDR SDRAM, FLASH, A/D, D/A, etc. The

FPGA chip inseted NiosII soft core. This architecture is an

advantage for implementing various kinds of RFID standards by

changing the soft of NiosII core in FPGA, and efficiently reduces

the design and development time and cost.

Keywords-RFID reader;RF AFE; base band; NioU;

I. INTRODUCTION

Radio frequency identification (RFID) is a non-contact

technology that means to automatically identify people and

objects on the basis of radio waves. In recent years, RFID has

received much attention as it has rapidly expending with

applications such as the building access control, toll collection,

vehicle parking access control, animal tracking, inventory

management and so on.

Several frequency ranges are used in RFID technology,

such as LF (125KHz, 135 KHz), HF(13.56 MHz),

UHF(860~960 MHz), and microwave(2.4 GHz). UHF band is

used worldwide for its long read range and low manufacturing

cost in the distribution field.

RFID systems consist of three components: an antenna, a

reader and a tag. This paper presents a system design for UHF

RFID reader which is compatible with EPC Class-1,

Generation-2 Standard, operating at the 915MHz band.

II. UHF RFID PROTOCOL OVERVIEW

EPC Radio-frequency Identification Protocols Class 1

Generation 2 UHF RFID Protocol for Communication at 860

MHz 960 MHz, in short EPC C1G2, is the standard protocol

developed by EPCglobal for RFID devices. This protocol

outlines the air interfaces and commands between an RFID

reader and an RFID tag.

This protocol defines the physical and logical requirements

for a passive-backscatter, Interrogator-talks-first (ITF), radio-

frequency identification (RFID) system operating in the 860

MHz 960 MHz frequency range. The system comprises

Interrogators, also known as Readers, and Tags, also known as

Labels. An reader transmits information to a Tag by

modulating an RF signal in the 860 MHz 960 MHz frequency

range. The Tag receives both information and operating energy

from this RF signal. Tags are passive, meaning that they

receive all of their operating energy from the readers RF

waveform. An reader receives information from a Tag by

transmitting a continuous-wave (CW) RF signal to the Tag; the

Tag responds by modulating the reflection coefficient of its

antenna, thereby backscattering an information signal to the

reader. The system is ITF, meaning that a Tag modulates its

antenna reflection coefficient with an information signal only

after being directed to do so by an reader. Readers and Tags are

not required to talk simultaneously; rather, communications are

half-duplex, meaning that readers talk and Tags listen, or vice

versa. An reader sends information to one or more Tags by

modulating an RF carrier using double-sideband amplitude

shift keying (DSB-ASK), single-sideband amplitude shift

keying (SSB-ASK) or phase-reversal amplitude shift keying

(PR-ASK) using a pulse-interval encoding (PIE) format. An

reader receives information from a Tag by transmitting an

unmodulated RF carrier and listening for a backscattered reply.

Tags communicate information by backscatter-modulating the

amplitude and/or phase of the RF carrier. The encoding format,

selected in response to reader commands, is either FM0 or

Miller-modulated sub-carrier.

III. DESIGN IMPLEMENTATION

The figure 1 shows the block diagram of the UHF RFID

reader. The UHF RFID reader consist of RF analog front end

(AFE), the base band and clock control.

Figure 1. Block diagram of the RFID reader.

==================

978-1-4244-2251-7/08/$25.00 2008 IEEE

?008 !!th Tlll Tutuut`ouu' Couu ou Commuu`ut`ou Thuo'o_) lod`u_:

30!

A. AFE design

The RFID RF AFE contains transmitting circuit,receiving

circuit frequency synthesize, circulator, etc. The block

diagram of the RFID reader AFE is shown in figure 2. The

circulator, which determines the performance of the reader

system. The signal transmitting to the tag and receiving from

the tag use one antenna, at same frequency and at same time.

Because the transmitting signal need to activate the tags in

distance, transmitter power is far greater than receiver power.

Because of the same antenna, it will leakage transmitting

signal to the receiving path, so that all devices in receiving

circuit will unable to work. We need a good performance

circulator to make transceivers isolation. Because the receiver

power is 0dBm and the transmitter power is 30dBm. we have

chosen the circulator which have 30dBm isolation.

Transmitting circuit received 70M IF signals from base band,

and LC filter filtering the 70M IF signals quantization noise

and spurious. Then these 70M IF signals enter mixer

frequency to UHF signals. These UHF signals including

various stray such as mirror image frequency signals, local

oscillator leakage signals need to RF filter filtering. And then,

these signals need to arrive at 30dBm power by the power

amplifier. Finally, these signals can go out by the circulator

and the antenna. Receiving circuit receive backscatter signals

from tag, these backscatter signals mingled on the continuous

launching carrier wave. These signals are divided into I and Q

subchains. Then these signals pass the low noise amplifier to

amplify, pass filter to filtering. Finally, these signals enter

mixer frequency to 70M IF signals. Unlike an HF transponder,

in UHF transponder the mixed frequency signal cannot be

extracted directly from the carrier. The mixed frequency signal

is created by frequency synthesize.

S

Figure 2. Block diagram of the RFID reader AFE.

The realization of RF AFE contains HYH504BZ

circulator, MAMXSS0011 mixer, DF915S25A and

LB070DS16 filters, RF5110 RF power amplifier, ATF54143

low noise amplifier. Figure 3 is a photograph of reader RF AFE.

Figure 3. The photograph of RF AFE.

B. Baseband design

The block diagram of the reader base band is shown in

figure 4. The base band contains the FPGA chip which inserts

the NIOS II soft core system to carry on protocol processor,

100M hardware resources of network supporting, DDR

SDRAM, FLASH, A/D, D/A, etc. The main task of the base

band section is to treat the communication protocol. The reader

is compatible with EPC Class-1, Generation-2 Standard. The

standard defines the protocol for a UHF passive backscatter

RFID system, featuring the following capabilities. An reader

sends information to one or more tags by modulating an RF

carrier using double-sideband amplitude shift keying (DSB-

ASK), single-sideband amplitude shift keying (SSB-ASK) or

phase-reversal amplitude shift keying (PR-ASK) using a pulse-

interval encoding (PIE) format. Tags receive their operating

energy from this same modulated RF carrier. A reader receives

information from a tag by transmitting an unmodulated RF

carrier and listening for a backscattered reply. Tags

communicate information by backscatter-modulating the

amplitude and/or phase of the RF carrier. The encoding format,

selected in response to reader commands, is either FM0 or

Miller-modulated sub-carrier. The communications link

between readers and tags is half-duplex, meaning that tags shall

not be required to demodulate reader commands while

backscattering. A tag shall not respond using full-duplex

communications to a mandatory or optional command. An

reader manages tag populations using three basic operations: a)

Select. The operation of choosing a tag population for

inventory and access. A select command may be applied

successively to select a particular tag population based on user-

specified criteria. This operation is analogous to selecting

records from a database. b) Inventory. The operation of

identifying tags. A reader begins an inventory round by

transmitting a Query command in one of four sessions. One or

more tags may reply. The reader detects a single tag reply and

requests the PC, EPC, and CRC-16 from the tag. Inventory

comprises multiple commands. An inventory round operates in

one and only one session at a time. c) Access. The operation of

communicating with (reading from and/or writing to) a tag. An

individual tag must be uniquely identified prior to access.

Access comprises multiple commands, some of which employ

?008 !!th Tlll Tutuut`ouu' Couu ou Commuu`ut`ou Thuo'o_) lod`u_:

30?

one-time-pad based cover-coding of the R=>T

link.

NIOS II

PC

Ethernet

PHY&MAC

JTAG

DDR SDRAM

Memory

FLASH Memory

Button

,

LED

modulator

demodulator

A

D

D

A

Rx

Tx

clock

Figure 4. Block diagram of the RFID reader baseband.

The architecture is not only good for being implemented in

EPC C1G2 protocol, but also for other RFID standards.

Depending on their different logic function, the base band is

divided into several modules. The A/D changes the 70M IF Rx

signal into digital signal. The Rx signal is demodulate and

decoder by the demodulate and decoder module. The Tx signal,

which is performed by modulated and encoder with the PIE, is

modulate and coder by the modulate and coder module. The

DA changes digital signal into the 70M analog Tx signal. The

control unit, which use the NiosII soft core inserted in FPGA,

performs all commands and controls. This architecture is an

advantage for implementing various kinds of RFID standards

by changing the soft of NiosII core. The module of DDR

SDRAM, FLASH implement the control of the memory. The

ethernet module performs commands and controls with PC.

The realization of base band contains AD9248, DA5674,

Cyclone EP2C35F672I FPGA, MT46V16M16TG DDR

SDRAM and S29GL256N FLASH .Figure 5 is a photograph of

an assenmbled testing PCB of base band.

Figure 5. The photograph of base band.

C. Clock design

The clock module produces 1 group 55MHz clock, which

actuates by the electric circuit in the base band module. The

clock divide into 5 groups, which uses to make the ADC

sampling clock (1 group), the PLL clock in FPGA works (3

groups), as well as disposition chip clock (1group). Moreover,

the clock produces 1 group 220MHz clock, which takes the

DAC sampling clock. In this clock module, we select the

55MHz clock as ADC and the FPGA clock, which facilitates

the synchronous processing in ADC and the FPGA logarithm.

Moreover the DAC uses 4 time of interpolation filters, after

interpolates filter, the data rate become 220MHz from 55MHz,

therefore the sampling frequency of DAC is 220MHz.

IV. EXPERIMENTAL RESULTS

We divided into three parts to verify the results of this reader:

The waveform of transmitting signal from reader, the

waveform of backscatter signal from tag and the signal quality

indicators. Signals launching from antenna to tags acquisition

by the spectrum analyzer show in figure 6. These signals use

PIE coding, signal power at 30dBm, and low signal power

4.4dBm. When the distance is 1.5m between antenna and tag,

the tag was activated. Information by backscatter-modulating

the amplitude and phase of the RF carrier acquisition by the

spectrum analyzer show in figure 7.

Figure 6. Waveform of transmitting signal from reader .

Figure 7. Waveform of backscatter signal from tag.

The tag backscatter signal quality indicators show in figure

8. The backscatter signal modulation depth is 15.859%, the

duty cycle is 49.041%, rise times are 1.713us, fall times are

3.8934us, receiving link frequency is 64.20 kHz, which is

compatible with the EPC Class-1, Generation-2 Standard.

?008 !!th Tlll Tutuut`ouu' Couu ou Commuu`ut`ou Thuo'o_) lod`u_:

303

Figure 8. Backscatter signal quality indicators.

V. CONCLUSIONS

In this paper, we presents a system design for UHF RFID

reader. The UHF RFID reader is compatible with EPC Class-1,

Generation-2 Standard, operating at the 915MHz band. The

UHF RFID reader includes RF AFE, the base band and clock

control. The base band, which inserted the NiosII soft core in

FPGA, performs all commands and controls. This NIOSII

based baseband structure is an advantage for implementing

various kinds of RFID standards, and efficiently reduces the

design and development time and cost.

REFERENCES

[1] EPCglobal, EPC radio-frequency identity protocols class-1 generation-2

UHF RFID protocol for communications at 860 MHz - 960 MHz version

1.0.9, EPCglobal Standard Specification, 2004.

[2] F.Zhou, C.Chen, D.Jin, C.Huang, and H.Min, Evaluating and optimizing

power consumption of anticollision protocols for applications in RFID

systems, InProc.ISLPED,2004.

[3] C. Chatmon, T.vanLe, and M.Burmester, Secure anonymous RFID

authentication protocols, Technical Report TR060112, Florida State

University, Department of Computer Science, Tallahassee, Florida,

USA,2006.

[4] Chen Linying, Hou Chunping,Mao Luhong , Wu Shunhua, Xu Zhenmei,

and Wang Zhenxing, A Verification Development Platform forPassive

UHF RFID Reader, Chiese Journal of Emiconductors, Beijing, 2007,

pp.1696-1700.

[5] A. K. Jones, R. Hoare, D. Kusic, J. Fazekas, andJ. Foster. An fpga-based

vliw processor with custom hardware execution, In ACM International

Symposium on Field-Programmable Gate Arrays (FPGA),2005.

[6] ZHANG Ting; XIONG Zhang, etc, Design of Networked Radio

Frequency Identification System Based on Control Area Network,

Microelectronics & Computer, 2007,pp.151-155.

?008 !!th Tlll Tutuut`ouu' Couu ou Commuu`ut`ou Thuo'o_) lod`u_:

30+

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Frenzel Self Test Chapter 9Document6 pagesFrenzel Self Test Chapter 9Aileen May Santillan HerreraNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Ece-306: Antennas and Wave Propagation: Dr. Usha Kiran KDocument24 pagesEce-306: Antennas and Wave Propagation: Dr. Usha Kiran KRanjith KumarNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

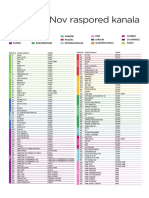

- Eutelsat 16A (16.0°E) - TV: Spisak Evropskih SatelitaDocument5 pagesEutelsat 16A (16.0°E) - TV: Spisak Evropskih SatelitaIgor IgorcicNo ratings yet

- Satellite Radio Full ReportDocument24 pagesSatellite Radio Full ReportAbanikant SahuNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- R13 ReceiverDocument2 pagesR13 ReceiverTigmasu SubhadarshyNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Am QuizDocument41 pagesAm QuizER_GIRRAJNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- FM Transmitter Project 2km CHAPTER 1Document3 pagesFM Transmitter Project 2km CHAPTER 1Jubril Akinwande80% (5)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Ec6004 Satellite Communication r2013Document2 pagesEc6004 Satellite Communication r2013Anonymous JnvCyu85No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- FM Broadcast StandardsDocument31 pagesFM Broadcast StandardsSean NatividadNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- CT Complete Notes (m1-m5)Document179 pagesCT Complete Notes (m1-m5)Rishabh NiketaNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- TruNet AR-1500 AR Data SheetDocument2 pagesTruNet AR-1500 AR Data Sheet김현선No ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- uSDX88s Handheld Shortwave Radio Assembly Instructions V2.3Document46 pagesuSDX88s Handheld Shortwave Radio Assembly Instructions V2.3Costin100% (1)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Reduce Code CongestionDocument5 pagesReduce Code CongestionNazmul HoqNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- ANNEX 10 - Aeronautical Telecomunications (Volume V)Document48 pagesANNEX 10 - Aeronautical Telecomunications (Volume V)Syahid MachedaNo ratings yet

- Total TV Raspored Kanla JulDocument2 pagesTotal TV Raspored Kanla JulДеан ВеселиновићNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Taarak MehtaDocument1 pageTaarak MehtaKneerdipNo ratings yet

- HTX 202Document5 pagesHTX 202bds2PSUNo ratings yet

- SCV Recommended PackDocument22 pagesSCV Recommended PackCHANDRAMOULI KRISHAMOORTHYNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Underground CommunicationDocument13 pagesUnderground CommunicationShivani Ekant YadavNo ratings yet

- LTE Advanced Poster enDocument1 pageLTE Advanced Poster enKlaus Simpson100% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Yaesu Fc757at Instruction ManualDocument28 pagesYaesu Fc757at Instruction ManualAudio TecnologiaNo ratings yet

- Samsung La32r71bd-32' LCD TVDocument38 pagesSamsung La32r71bd-32' LCD TVMark CoatesNo ratings yet

- Ieee 521-2002Document10 pagesIeee 521-2002Dante P. ChNo ratings yet

- FractalAntenna UADDocument2 pagesFractalAntenna UADMax PowerNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Audio-Technica Atw A49 SpecsheetDocument2 pagesAudio-Technica Atw A49 SpecsheetAnte NekicNo ratings yet

- Handling EpirbDocument14 pagesHandling EpirbAjay SinghNo ratings yet

- Reserch Proposal On: Performance Analysis and Optimization of MIMO System On Wireless NetworkDocument7 pagesReserch Proposal On: Performance Analysis and Optimization of MIMO System On Wireless NetworkSameer TrapasiyaNo ratings yet

- Two Way Radio CommunicationsDocument2 pagesTwo Way Radio Communicationsabross36No ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- DTH Services in IndiaDocument28 pagesDTH Services in IndiaNidhi Deopura Parke100% (1)

- Television TransmitterDocument2 pagesTelevision TransmitterLight CloudNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)