Professional Documents

Culture Documents

TP Liaisons Serie

Uploaded by

Imane SaharOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TP Liaisons Serie

Uploaded by

Imane SaharCopyright:

Available Formats

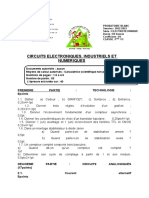

TP

Dure : 6h00

TSTI2 anne 2010/2011

SIMULATION Les registres dcalage Liaisons srie

EMETTEUR EMETTEUR D7 D0 1 0 0 1 1 1 0 1 D7 D0 D7 1 0 1 1 1 0 0 1

horloge

REGISTRE A REGISTRE A DECALAGE DECALAGE

REGISTRE A REGISTRE A DECALAGE DECALAGE

horloge D0

1 0 0 1 1 1 0 1 D7 RECEPTEUR RECEPTEUR D0

Prrequis : -

fiche "les liaisons sries"

Objectifs : -

compteur registre dcalage les liaisons sries asynchrones

simulation avec le logiciel PROTEUS-ISIS

SECTION STI

ELECTRONIQUE

La premire partie du TP porte sur le compteur 74ls161. Vous verrez dans la seconde partie l'tude des registres dcalage puis l'utilisation d'un registre dcalage dans une liaison srie asynchrone. Pour ce TP vous rdigerez un compte-rendu dans lequel vous collerez les chronogrammes des feuilles rponses.

CTR DIV16

1. RAPPEL SUR LE COMPTEUR Soit le compteur 74LS161 : 1.1 En utilisant sa documentation constructeur (rseau), donner le rle et le niveau ou front actif de chaque entre et de la sortie RCO. 1.2 Complter les chronogrammes 1 de la feuille rponse. 1.3 Saisir le schma sous PROTEUS ISIS. Saisir les stimuli et vrifier vos chronogrammes.

CLR (1) LOAD (9) ENT (10) ENP (7) CLK (2)

CT=0 M1 M2 G3 G4 C5/2,3,4+

3CT=15

(15)

RCO

A (3) B (4) C (5) D (6)

1,5D

[1] [2] [3] [4] 74LS161

(14)

QA QB QC QD

(13)

(12)

(11)

2. La liaison srie

2.1 Dans une transmission srie, quel est le rle des registres dcalage ? 2.2 Quels sont les deux types de registres dcalage utiliser dans le cas dune liaison srie ?

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 2/7

3. Le registre dcalage 74ls166 La documentation du circuit est sur le rseau (utilisez le site STI2). Les noms des broches varient dun constructeur lautre, soyez vigilants ! Aidez vous des n de broches. 3.1 3.2 3.3 3.4 Quel est le type de ce registre ? Quel type de bascules compose ce circuit ? Complter sur la feuille rponse la table de vrit du registre. Complter les chronogrammes n2 de la feuille rponse. Fates contrler par le professeur. Mettre en vidence ( couleurs ) sur le chronogramme de Q le mot srie de sortie. 3.5 Saisir sous PROTEUS le schma ci-dessous. Vrifier vos chronogrammes en simulant le composant. Conclure.

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 3/7

4. LIAISON SERIE : convertisseur parallle / srie La structure ci-dessous permet de convertir un mot // sur 8 bits en un mot srie en ajoutant un bit de START et un ou deux bits de STOP.

4.1 Rappeler le rle du bit START et du bit STOP dans une liaison srie asynchrone ? On donne les chronogrammes de CLK, LD , S0, et READY .

CLK

K

LD S0

Start D0 D1 D2 D3 D4 D5 D6 D7 stop stop start D0 D1

READY

14 15 0 1 2 3 4 5 6 7 8 9 10 10 10 10 10 14 15 0 1

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 4/7

4.2 Justifier le fait que la valeur dcimale 10, sur les sorties Q 3 Q0 du compteur, permette le blocage du compteur. Faire un schma. On considre le RESET inactif dans les questions suivantes. 4.3 READY = 0L. La conversion commence par une impulsion ngative sur lentre LD du circuit. Que se passet-il pour le compteur ? Quelle est alors la valeur en Q3 Q2 Q1 Q0 ? (binaire puis dcimale). 4.4 LD repasse au niveau haut. Que se passe-t-il pour le compteur au front actif suivant de CLK ? quelle est la valeur dcimale de sortie ? 4.5 Donner alors l'tat de RCO (broche 15 du compteur). 4.6 En dduire l'tat de S0. En vous aidant de la trame RS232, quoi correspond ce premier bit ? 4.7 Quelle incidence sur le registre a eu le passage 0L de LD ? 4.8 Au front actif suivant sur CLK, quel est ltat des sorties du compteur ? A quoi est gal S0 ? 4.9 Que fait le registre chacun des coups d'horloge suivants ? En dduire le mot srie qui apparat en S0. 4.10Que se passe-t-il lorsque les sorties du compteur retrouvent la valeur dcimale 8 ? Quel tat prend la sortie S0 ? Justifier par un schma. A quoi correspond cet tat ? 4.11Complter les chronogrammes n3 de la feuille rponse. 4.12Copier le fichier schma serie232_eleve.dsn du rpertoire v:\commun_elec\tsti2\TP\liaisons serie\ sous votre compte. diter les stimuli. 4.13Lancer la simulation. Imprimer les traces. Mettre en vidence sur le chronogramme de S0 le mot srie. Changer de code dentre, vrifier que lon retrouve bien ce code en sortie.

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 5/7

FEUILLE RPONSE (dcouper et coller dans votre compte-rendu) chronogrammes n1 - rponse la question 1.2

tableau de fonctionnement du registre 74ls166 question 3.3 On considre CLEAR = 1L.

SHIFT/LOAD CLOCK CLOCK INHIBIT

schma interne (noter les tats logiques)

fonctionnement

analyser le fonctionnement (tat de la sortie QA) pour les deux tats possibles de la DATA (A)

conclure sur le rle de CLOCK INHIBIT

Que recopie la sortie de la premire bascule sur les fronts actifs de CLOCK ? Que recopie la sortie des autres bascules ? En dduire le rle de l'entre SERIAL INPUT

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 6/7

chronogrammes n2 - rponse la question 3.4

chronogrammes n3 - rponse la question 4.11

TP LES LIAISONS SRIE

{\tp liaisons serie.odt} - page 7/7

You might also like

- Application Des Multiplexeurs Et Des DemultiplexeursDocument8 pagesApplication Des Multiplexeurs Et Des DemultiplexeursSaid EchNo ratings yet

- Registre Decalage ExercicesDocument5 pagesRegistre Decalage ExercicesexamsamediNo ratings yet

- Cahier TPDocument20 pagesCahier TPMortimer MeunierNo ratings yet

- Lisez SimulateurDocument5 pagesLisez SimulateurAmir DridiNo ratings yet

- Un Tableau ÉlectroniqueDocument26 pagesUn Tableau ÉlectroniqueManel Ouled AhmedNo ratings yet

- Les Compteurs ISISDocument10 pagesLes Compteurs ISISDiego MezaNo ratings yet

- LAB 2-SiemensDocument13 pagesLAB 2-Siemenssido bNo ratings yet

- TP Fpga Cyclone2Document3 pagesTP Fpga Cyclone2red-allNo ratings yet

- Architecture Ordinateurs 8086 ElmokhtariDocument63 pagesArchitecture Ordinateurs 8086 ElmokhtariZakaria HaitoutNo ratings yet

- CIRCUITS ELECTRONIQUES Industriel Et Numeriques Probatoire Blanc 2022-2023Document5 pagesCIRCUITS ELECTRONIQUES Industriel Et Numeriques Probatoire Blanc 2022-2023Prince JardelNo ratings yet

- TP3 4 Applications A Base de Circuit NE555Document9 pagesTP3 4 Applications A Base de Circuit NE555hajjiNo ratings yet

- TDu CDocument49 pagesTDu CnawzatNo ratings yet

- Annexe 1Document18 pagesAnnexe 1Yahya GharbiNo ratings yet

- tp1 - AfficheurDocument8 pagestp1 - AfficheurAmadou SARRNo ratings yet

- VhdlexDocument10 pagesVhdlexSoukaina NJNo ratings yet

- TP1feux Doc 1Document10 pagesTP1feux Doc 1Ahmed TriguiNo ratings yet

- Compteur Synchrone - 2011 - 2012Document8 pagesCompteur Synchrone - 2011 - 2012Elmokh Lassaad100% (1)

- Examen Rattrapage Architectures Avancées Sur SoC 2019Document6 pagesExamen Rattrapage Architectures Avancées Sur SoC 2019Dhafer MezghaniNo ratings yet

- Registre A DecalageDocument3 pagesRegistre A Decalagerachid223No ratings yet

- TP ElecII GM2 PDFDocument21 pagesTP ElecII GM2 PDFyoussef MoujanniNo ratings yet

- TP3 Electr NumériqueDocument7 pagesTP3 Electr NumériqueYoucef BoukhalfaNo ratings yet

- Devoir de Synthèse N°3 2006 2007 (Soudani Sami)Document3 pagesDevoir de Synthèse N°3 2006 2007 (Soudani Sami)Med Aymen Bensalem100% (2)

- TD N3 VHDLDocument20 pagesTD N3 VHDLHanane AIT SAIDNo ratings yet

- Regulation de Temperature D'un FourDocument6 pagesRegulation de Temperature D'un FourbalfsahiNo ratings yet

- Unité3Document19 pagesUnité3Emilio del RioNo ratings yet

- Compteurs Et AfficheursDocument2 pagesCompteurs Et Afficheursaminialaouimj100% (1)

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaNo ratings yet

- SI STE Corrigé Session Normale 2011Document7 pagesSI STE Corrigé Session Normale 2011El Idrissi HajarNo ratings yet

- Technique CDocument8 pagesTechnique CMahdi NjehNo ratings yet

- Série 19 4ST NR 2024 CompteursDocument4 pagesSérie 19 4ST NR 2024 CompteursAbdelbasset ZaiechNo ratings yet

- TP 1 Asservissement Et RégulationDocument9 pagesTP 1 Asservissement Et Régulationhoussemouazaa2003No ratings yet

- 01 Langage A ContactsDocument32 pages01 Langage A Contactsboss.12812No ratings yet

- 1tronconneuse AutomatiqueDocument40 pages1tronconneuse Automatique2ste3100% (1)

- Travaux Pratiques Electronique Numérique - 2015-2016 PDFDocument16 pagesTravaux Pratiques Electronique Numérique - 2015-2016 PDFMed Tag33% (3)

- Correction Rattrapage 2013Document10 pagesCorrection Rattrapage 2013abir cherifNo ratings yet

- Sujet TP Simulation EPI2 2016 - 2017 - v3Document10 pagesSujet TP Simulation EPI2 2016 - 2017 - v3Abdelkarim RamNo ratings yet

- Microprocessor Course Part 2Document15 pagesMicroprocessor Course Part 2Salah-Eddine NasmiNo ratings yet

- Moteur Pas - À-Pas Chapitre 2Document7 pagesMoteur Pas - À-Pas Chapitre 2Adel Haddad HauntedNo ratings yet

- 3 Compteur Synchrone 2011 2012Document8 pages3 Compteur Synchrone 2011 2012Mohamed EL MASSOUDINo ratings yet

- Devoir Surveillé Autom2 2022Document8 pagesDevoir Surveillé Autom2 2022Aftaab H. RaheemanNo ratings yet

- Bac 2015Document14 pagesBac 2015Junior JuniorNo ratings yet

- Devoir de Contrôle - Technologie Fonctions Universelles Climatiseur D'une Voiture - 2ème Sciences (2014-2015) MR Tarek PDFDocument4 pagesDevoir de Contrôle - Technologie Fonctions Universelles Climatiseur D'une Voiture - 2ème Sciences (2014-2015) MR Tarek PDFchida OussamaNo ratings yet

- Theme2 BenkacemDocument11 pagesTheme2 BenkacemMehdi BKNo ratings yet

- Exam 2020Document7 pagesExam 2020Mamadou Korka KantéNo ratings yet

- Lab 1Document9 pagesLab 1Wissem BachaNo ratings yet

- Rapport HFDocument48 pagesRapport HFMichel Massamba FayeNo ratings yet

- Chap 3 Synthese Des Systemes CombinatoiresDocument11 pagesChap 3 Synthese Des Systemes CombinatoiresKycelle MbouzekoNo ratings yet

- Travaux Diriges 2Document9 pagesTravaux Diriges 2mohcen50% (2)

- Step7 5Document28 pagesStep7 5Imane Benidder50% (2)

- Corrigé Bac Pro MEI 2019Document10 pagesCorrigé Bac Pro MEI 2019HakobyanNo ratings yet

- E2 Metro Corrige CopieDocument10 pagesE2 Metro Corrige CopieSmith FrankNo ratings yet

- BasculeDocument10 pagesBasculeWiz TraceNo ratings yet

- Exam SessNormal 21-02-2012 CompressedDocument3 pagesExam SessNormal 21-02-2012 CompressedMoha MansouriNo ratings yet

- U42 AutomatismesDocument13 pagesU42 AutomatismesTriki Bilel100% (1)

- Fiche de TD SIE GE3Document6 pagesFiche de TD SIE GE3sigha josueNo ratings yet

- Poly TexturesDocument14 pagesPoly TexturesImane SaharNo ratings yet

- Panneau/Bloc RJ 45 Pour LCS Catégorie 6Document6 pagesPanneau/Bloc RJ 45 Pour LCS Catégorie 6Imane SaharNo ratings yet

- UMTSDocument32 pagesUMTSBilel BenatiaNo ratings yet

- Registre A DecalageDocument3 pagesRegistre A Decalagerachid223No ratings yet

- (B) SignauxSystemesDocument10 pages(B) SignauxSystemesImane SaharNo ratings yet

- Structure Generale D'un Micro-OrdinateurDocument4 pagesStructure Generale D'un Micro-OrdinateurImane SaharNo ratings yet

- Electronique Pratique N°259Document6 pagesElectronique Pratique N°259Imane Sahar100% (1)

- Fonctions Mono-Ligne Fonctions Mono-Ligne: Objectifs ObjectifsDocument15 pagesFonctions Mono-Ligne Fonctions Mono-Ligne: Objectifs Objectifsazer aqNo ratings yet

- 3sc Les Fonctions PrédéfiniesDocument1 page3sc Les Fonctions PrédéfiniesAyoub AcresNo ratings yet

- Gérer Les Commandes - Prêt Pour L'expédition - Seller Center333Document4 pagesGérer Les Commandes - Prêt Pour L'expédition - Seller Center333TOP OFFICENo ratings yet

- Chaines PythonDocument1 pageChaines PythonazeerazerNo ratings yet

- Level 5 - CCM501 - Pratiquer Les Techniques D'expression Orale Et ÉcriteDocument17 pagesLevel 5 - CCM501 - Pratiquer Les Techniques D'expression Orale Et ÉcriteFortin Fils ErcilienNo ratings yet

- stb-comm-ECURCP EPCURCP Ind CDocument35 pagesstb-comm-ECURCP EPCURCP Ind ClatNo ratings yet

- SM1 Poly HaouamDocument72 pagesSM1 Poly HaouamKheir eddine DaouadiNo ratings yet

- Electronique Numerique Ge FSTDocument79 pagesElectronique Numerique Ge FSTEric TsayimNo ratings yet

- Représentation Des Nombres Réels - Eduardo SanchezDocument11 pagesReprésentation Des Nombres Réels - Eduardo SanchezPalmface MedNo ratings yet

- Chapitre 1 Systèmes de NumérationsDocument18 pagesChapitre 1 Systèmes de Numérationssouha SNo ratings yet

- Cours Emi Micro 2020 (Microp CHP 1,2,3)Document15 pagesCours Emi Micro 2020 (Microp CHP 1,2,3)Youssef El AjraouiNo ratings yet

- Je Joue Avec Les LettresDocument27 pagesJe Joue Avec Les LettresRémi LacosteNo ratings yet

- Rib CelineDocument1 pageRib CelineZLATAN IBRANo ratings yet

- Ieee 754Document7 pagesIeee 754Karim AmaneNo ratings yet

- BinaireDocument4 pagesBinairegael thomNo ratings yet

- TP 32.1 Codeur Binaire Naturel - 7 Segments - Afficheur - CorrigéDocument4 pagesTP 32.1 Codeur Binaire Naturel - 7 Segments - Afficheur - CorrigénadNo ratings yet

- TP - Code de Hamming H: Master Ice - M1Document1 pageTP - Code de Hamming H: Master Ice - M1Christian VadilloNo ratings yet

- Info I (Partie II)Document75 pagesInfo I (Partie II)RuSe NOirNo ratings yet

- TD NSI Premiere Representation Donnees Types Valeurs BaseDocument6 pagesTD NSI Premiere Representation Donnees Types Valeurs Basemulk omarNo ratings yet

- Table Des Caractères Unicode - U07C0 - Wikipédia PDFDocument31 pagesTable Des Caractères Unicode - U07C0 - Wikipédia PDFJj BishwekaNo ratings yet

- ExtraitDocument8 pagesExtraitsimao_sabrosa7794No ratings yet

- CodeDocument2 pagesCodesiamo0% (1)

- CCNA1 Lab 1 2 8 FRDocument4 pagesCCNA1 Lab 1 2 8 FRghaniNo ratings yet

- BNP RibDocument1 pageBNP RibRimo HortonNo ratings yet

- Codages Manchester - Différentiel - RZ - NRZDocument6 pagesCodages Manchester - Différentiel - RZ - NRZFAROUKNo ratings yet

- Typo La Ponctuation PDFDocument3 pagesTypo La Ponctuation PDFTabac NoirNo ratings yet

- Fractions, Nombres Relatifs Et Décimaux: MathsDocument9 pagesFractions, Nombres Relatifs Et Décimaux: Mathsjadrueueyzai82737No ratings yet

- Devoir N 1 38Document1 pageDevoir N 1 38scooorpion kidNo ratings yet

- TD 6 CN - L3 TélécomDocument8 pagesTD 6 CN - L3 TélécomHouda SenoussiNo ratings yet

- Combinaison de TouchesDocument2 pagesCombinaison de TouchesSweet-manNo ratings yet