Professional Documents

Culture Documents

Field Effect Transistor (FET)

Uploaded by

Chalez ZengeretsiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Field Effect Transistor (FET)

Uploaded by

Chalez ZengeretsiCopyright:

Available Formats

Electronics Laboratory

Experiment No.12 Field Effect Transistor (FET)

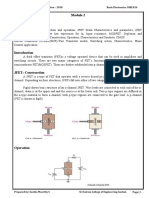

OBJECT: To investigate the FET characteristics . APPARATUS: 1-D.C power supply . 2-Oscilloscope ,A.V.Ometer . 3-FET, Resistors 1k and 200k. THEORY The acronym FET stands for field effect transistor. It is a three-terminal unipolar solidstate device in which current is controlled by an electric field as is done in vacuum tubes. Broadly speaking, there are two types of FETs : (a) junction field effect transistor (JFET) (b) metal-oxide semiconductor FET (MOSFET) It is also called insulated-gate FET (IGFET). It may be further subdivided into : (i) depletion-enhancement MOSFET i.e. DEMOSFET (ii) enhancement-only MOSFET i.e. E-only MOSFET Both of these can be either P-channel or N-channel devices. The FET family tree is shown below :

As shown in Fig.1, it can be fabricated with either an N-channel or P-channel though Nchannel is generally preferred. For fabricating an N-channel JFET, first a narrow bar of Ntype semiconductor material is taken and then two P-type junctions are diffused on opposite sides of its middle part [Fig.1 (a)]. These junctions form two P-N diodes or gates and the area between these gates is called channel. The two P-regions are internally connected and a single

Electronics Laboratory lead is brought out which is called gate terminal. Ohmic contacts (direct electrical connections) are made at the two ends of the bar-one lead is called source terminal S and the other drain terminal D. When potential difference is established between drain and source, current flows along the length of the bar through the channel located between the two Pregions. The current consists of only majority carriers which, in the present case, are electrons. P-channel JFET is similar in construction except that it uses P-type bar and two Ntype junctions. The majority carriers are holes which flow through the channel located between the two N-regions or gates. Following FET notation is worth remembering: 1. Source. It is the terminal through which majority carriers enter the bar. Since carriers come from it, it is called the source. 2. Drain. It is the terminal through which majority carriers leave the bar i.e. they are drained out from this terminal. The drain to source voltage VDS drives the drain current ID. 3. Gate. These are two internally-connected heavily-doped impurity regions which form two P-N junctions. The gate-source voltage VGS reverse biases the gates. 4. Channel. It is the space between two gates through which majority carriers pass from source-to-drain when VDS is applied. Schematic symbols for N-channel and P-channel JFET are shown in Fig.1 (c). It must be kept in mind that gate arrow always points to N-type material.

Fig. 1 FET construction

Electronics Laboratory

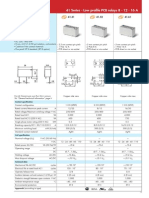

Static Characteristics of a JFET We will consider the following two characteristics: (i) drain characteristic: It gives relation between ID and VDS for different values of VGS (which is called running variable). (ii) transfer characteristic: It gives relation between ID and VGS for different values of VDS. We will analyze these characteristics for an N-channel JFET connected in the common-source mode as shown in Fig. 2. We will first consider the drain characteristic when VGS= 0 and then when VGS has any negative value upto VGS(off).

Fig. 2 JFET Drain Characteristic With VGS = 0 Such a characteristic is shown in Fig. 3. It can be subdivided into following four regions : 1. Ohmic Region OA: This part of the characteristic is linear indicating that for low values of VDS, current varies directly with voltage following Ohm's Law. It means that JFET behaves like an ordinary resistor till point A (called knee) is reached. 2. Curve AB In this region, ID increases at reverse square-law rate upto point B which is called pinch-off point. This progressive decrease in the rate of increase of ID is caused by the square law increase in the depletion region at each gate upto point B where the two regions are closest without touching each other.

Fig. 3

Electronics Laboratory 3. Pinch-off Region BC: It is also known as saturation region or amplified region. Here, JFET operates as a constant-current device because ID is relatively independent of VDS. It is due to the fact that as VDS increases, channel resistance also increases proportionally thereby keeping ID practically constant at IDSS. It should also be noted that the reverse bias required by the gate-channel junction is supplied entirely by the voltage drop across the channel resistance due to flow of IDSS and none by external bias because VGS = 0. 4. Breakdown Region: If VDS is increased beyond its value corresponding to point C (called avalanche breakdown voltage), JFET enters the breakdown region where ID increases to an excessive value. This happens because the reverse-biased gate-channel P-N junction undergoes avalanche breakdown when small changes in VDS produce very large changes in ID. It is interesting to note that increasing values of VDS make a JFET behave first as a resistor (ohmic region), then as a constant-current source (pinch-off region) and finally, as a constantvoltage source (breakdown region). Procedure : 1- Connect the circuit as shown in fig 4. 2- Let VDS =(0,0.5,1,1.5,2,2.5,3,4,5 )v measure ID. 3- Repeat step 3 for VGS =(0.5,1,1.5,2,2.5,3,3.5,4,4.5) V.

1k 200k

Fig. 4

REQUIREMENTS : 1- Draw (drain characteristics ) between ID & VDS for different values of VGS. 2- Draw ID with VGS & find gm . DISCUSSION: 1-comment on your results. 2-compar between the transistor &FET . 3-what are the kind of FET .

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Astable Multivibrator Using TransistorsDocument24 pagesAstable Multivibrator Using TransistorsChalez ZengeretsiNo ratings yet

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesFrom EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesRating: 4.5 out of 5 stars4.5/5 (7)

- An 101 Fet IntroDocument5 pagesAn 101 Fet IntrotarpinoNo ratings yet

- Unit - Vi Field Effect TransistorDocument16 pagesUnit - Vi Field Effect TransistorBhavaniPrasadNo ratings yet

- What Is A Slot TechnicianDocument4 pagesWhat Is A Slot TechnicianChalez ZengeretsiNo ratings yet

- RAM Clear Casino Tech GeminiDocument4 pagesRAM Clear Casino Tech GeminiChalez ZengeretsiNo ratings yet

- Advanced Electrical Workshop Contents and Electrical Technology FundamentalsDocument205 pagesAdvanced Electrical Workshop Contents and Electrical Technology FundamentalsLucian IftemieNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Power System ProblemDocument10 pagesPower System ProblemDanylle Lajera DiazNo ratings yet

- CB#1 Journeyman examDocument57 pagesCB#1 Journeyman examEarl Jenn AbellaNo ratings yet

- Mx341 Avr Newage StamfordDocument4 pagesMx341 Avr Newage Stamfordabuzer1981No ratings yet

- R8017G MBCHDocument52 pagesR8017G MBCHmjbriceno@gmail.com100% (1)

- Edc 4 UnitDocument26 pagesEdc 4 UnitAnonymous 6Ts3r7dwNo ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- Unit I - FETDocument19 pagesUnit I - FETJadhav BhagavatNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- Edc - Unit 5Document37 pagesEdc - Unit 5GANGADHARA SAIPRASANNANo ratings yet

- Chapter ForDocument17 pagesChapter Forbelacheweshetu222No ratings yet

- JFET and MOSFET CharacteristicsDocument56 pagesJFET and MOSFET CharacteristicsHarry Chandhu100% (1)

- Unit 3 Field Effect Transistor JfetDocument21 pagesUnit 3 Field Effect Transistor Jfetrakesh hudedNo ratings yet

- EDC Unit 6 FETDocument30 pagesEDC Unit 6 FETmuralitmpsNo ratings yet

- The Basic Structure: Field Effect TransistorDocument10 pagesThe Basic Structure: Field Effect TransistormokhaladNo ratings yet

- Field Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterDocument8 pagesField Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterAkhilesh PandeNo ratings yet

- Module-2 Fets:: Importance of Fets (Motivation)Document22 pagesModule-2 Fets:: Importance of Fets (Motivation)rajuNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- Electronics Hons C3 FET Field Effect TransistorDocument21 pagesElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaNo ratings yet

- Fet MosfetDocument20 pagesFet MosfetnupurnehaNo ratings yet

- Unit 5 - Electronic Devices - WWW - Rgpvnotes.inDocument17 pagesUnit 5 - Electronic Devices - WWW - Rgpvnotes.inprakharNo ratings yet

- Akhil Bee.Document33 pagesAkhil Bee.yashNo ratings yet

- FET/MOSFET Characteristics: ObjectiveDocument13 pagesFET/MOSFET Characteristics: ObjectiveZeeshan RafiqNo ratings yet

- Field Effect Transistors ExplainedDocument15 pagesField Effect Transistors ExplainedGizachew BalchaNo ratings yet

- Observations: Experimental ValuesDocument7 pagesObservations: Experimental ValuesShibeshwar MandalNo ratings yet

- PH3007 Logic Families L 29 - 31Document33 pagesPH3007 Logic Families L 29 - 31Nethmi LokusuriyaNo ratings yet

- Semiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheDocument10 pagesSemiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheShoumil SachanNo ratings yet

- JFET Characteristics Lab GuideDocument22 pagesJFET Characteristics Lab GuideAnsar AnsarNo ratings yet

- Lecture 06Document21 pagesLecture 06Atika Mustari SamiNo ratings yet

- Field Effect Transistor NotesDocument21 pagesField Effect Transistor NotessaraswatnidhiNo ratings yet

- Ece-Research Work 1Document10 pagesEce-Research Work 1Peale ObiedoNo ratings yet

- Unit IIIDocument20 pagesUnit IIIionightbotNo ratings yet

- Field Effect TransistorsDocument4 pagesField Effect TransistorsdwaswaNo ratings yet

- MODULE 1 - FET - WatermarkDocument16 pagesMODULE 1 - FET - WatermarkAnupama MohananNo ratings yet

- Jfet MosfetDocument25 pagesJfet Mosfethrishabhraj710No ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- Module 4 FET MOSFETDocument23 pagesModule 4 FET MOSFETsenthilnathanNo ratings yet

- Field Effect Transistors (FET) : Comparison Between BJT and FETDocument9 pagesField Effect Transistors (FET) : Comparison Between BJT and FETpranavraikar1No ratings yet

- Regulation – 2018 Basic Electronics Module 2 FET and SCR CharacteristicsDocument12 pagesRegulation – 2018 Basic Electronics Module 2 FET and SCR CharacteristicsDaisyQueenNo ratings yet

- Field Effect TransistorDocument12 pagesField Effect TransistorYashu BhargavNo ratings yet

- ECE 027 - Module 5 Field Effect TransistorDocument102 pagesECE 027 - Module 5 Field Effect TransistorMiyuki NakiriNo ratings yet

- CH 63 PDFDocument26 pagesCH 63 PDFJawad Ul Hassan ShahNo ratings yet

- JFET CharacteristicsDocument7 pagesJFET CharacteristicsKRSTNo ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- Field Effect TransistorsDocument59 pagesField Effect TransistorsRan QuitNo ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Chapter 8: Field Effect Transistors: A. Introduction To FetsDocument10 pagesChapter 8: Field Effect Transistors: A. Introduction To FetsBmanNo ratings yet

- Lecture 8Document14 pagesLecture 8Altaher Bushra AdamNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- BE 4 UnitDocument15 pagesBE 4 Unit08sunnyjaganNo ratings yet

- Bipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)Document5 pagesBipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)sgmdhussainNo ratings yet

- AEC Lab ManualDocument75 pagesAEC Lab Manualphalanetra100% (1)

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Final MosfetDocument33 pagesFinal MosfetabdallaNo ratings yet

- Lecture-1: Notes by Dr. Prem Pal SinghDocument28 pagesLecture-1: Notes by Dr. Prem Pal SinghPrempalSinghNo ratings yet

- Field Effect Transisters (FET)Document22 pagesField Effect Transisters (FET)Raja PosupoNo ratings yet

- Mosfet Notes 1Document9 pagesMosfet Notes 1Anil SaiNo ratings yet

- Chapter5 FET PDFDocument12 pagesChapter5 FET PDFJ VikasNo ratings yet

- As A Highly Skilled Electronics TechnicianDocument2 pagesAs A Highly Skilled Electronics TechnicianChalez ZengeretsiNo ratings yet

- NR - Part Details QuantityDocument1 pageNR - Part Details QuantityChalez ZengeretsiNo ratings yet

- Slot TrainingDocument17 pagesSlot TrainingChalez ZengeretsiNo ratings yet

- Touchscreen Integration and Troubleshooting GuideDocument20 pagesTouchscreen Integration and Troubleshooting GuideChalez ZengeretsiNo ratings yet

- Slot TrainingDocument17 pagesSlot TrainingChalez ZengeretsiNo ratings yet

- L4 LESSON PLAN PLCDocument2 pagesL4 LESSON PLAN PLCChalez ZengeretsiNo ratings yet

- MK7 - Common Faults1Document2 pagesMK7 - Common Faults1Chalez ZengeretsiNo ratings yet

- TechFest 18 Technical TrainingDocument3 pagesTechFest 18 Technical TrainingChalez ZengeretsiNo ratings yet

- MT7 Software Suite: March 07Document14 pagesMT7 Software Suite: March 07Chalez ZengeretsiNo ratings yet

- MemoDocument6 pagesMemoChalez Zengeretsi100% (1)

- Learning Objectives:: Topic 1.2.2 - System Simplification Using Boolean AlgebraDocument52 pagesLearning Objectives:: Topic 1.2.2 - System Simplification Using Boolean AlgebraChalez ZengeretsiNo ratings yet

- L4 Ecde QPDocument4 pagesL4 Ecde QPChalez ZengeretsiNo ratings yet

- Cap PDFDocument82 pagesCap PDFChalez ZengeretsiNo ratings yet

- Binary Codes: Advantag Es of Binary CodeDocument3 pagesBinary Codes: Advantag Es of Binary CodeKamalendu Kumar DasNo ratings yet

- Test 2Document3 pagesTest 2Chalez ZengeretsiNo ratings yet

- Markers Report For TestsDocument5 pagesMarkers Report For TestsChalez ZengeretsiNo ratings yet

- EIC L4 ISAT Electronic ComponentsDocument4 pagesEIC L4 ISAT Electronic ComponentsChalez ZengeretsiNo ratings yet

- NMMU Faculty of Engineering Prospectus 2016Document171 pagesNMMU Faculty of Engineering Prospectus 2016Chalez ZengeretsiNo ratings yet

- Flowchart, Algoruthm and Pseudo Codes in C++Document6 pagesFlowchart, Algoruthm and Pseudo Codes in C++MAveRicK135100% (4)

- Motor Forward and Reverse Direction Control Using A PLCDocument5 pagesMotor Forward and Reverse Direction Control Using A PLCChalez ZengeretsiNo ratings yet

- Eic Icass Materila - RFQDocument10 pagesEic Icass Materila - RFQChalez ZengeretsiNo ratings yet

- Year Planner 2016 NCVDocument3 pagesYear Planner 2016 NCVChalez ZengeretsiNo ratings yet

- Supervisory Management N4 - Module 1Document8 pagesSupervisory Management N4 - Module 1Chalez Zengeretsi100% (7)

- Report 191: Eastcape Midlands CollegeDocument2 pagesReport 191: Eastcape Midlands CollegeChalez ZengeretsiNo ratings yet

- L4 Test CatDocument5 pagesL4 Test CatChalez ZengeretsiNo ratings yet

- ISAT L3 - Electrical Systems & Construction 2011-13Document13 pagesISAT L3 - Electrical Systems & Construction 2011-13Chalez ZengeretsiNo ratings yet

- L4 Test 1 2015Document4 pagesL4 Test 1 2015Chalez ZengeretsiNo ratings yet

- Reply The ReportDocument30 pagesReply The ReporthggNo ratings yet

- RM 1599 Nett RM 2499 RM 980 Nett RM 1738: Desktop PC Package SystemDocument1 pageRM 1599 Nett RM 2499 RM 980 Nett RM 1738: Desktop PC Package SystemKhay SaadNo ratings yet

- Analog Circuits - WWW - Rgpvnotes.inDocument60 pagesAnalog Circuits - WWW - Rgpvnotes.inMANSI50% (2)

- Three transistor operating modes and amplifier efficiency lectureDocument149 pagesThree transistor operating modes and amplifier efficiency lectureganadim9795No ratings yet

- P2DDocument8 pagesP2DBruno NascimentoNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument113 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- APX-C Preliminary Datasheet - V1Document4 pagesAPX-C Preliminary Datasheet - V1Diego ZABALA0% (1)

- BC847 Series: 1. Product ProfileDocument17 pagesBC847 Series: 1. Product ProfileEletrohelp EletrodomésticosNo ratings yet

- Finder 16A 12V DC Relay Datasheet.Document10 pagesFinder 16A 12V DC Relay Datasheet.velizarkoNo ratings yet

- E&M Question BankDocument18 pagesE&M Question BankEzhilya VenkatNo ratings yet

- EE102 Electronic Engineering II: BJT Differential Pair Circuit AnalysisDocument11 pagesEE102 Electronic Engineering II: BJT Differential Pair Circuit Analysis211164 211164No ratings yet

- Realization of TMD Circuits Inverter, and Operational AmplifierDocument6 pagesRealization of TMD Circuits Inverter, and Operational AmplifierInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Wireless Control For Industrial Instruments and Home Appliences at UhfDocument4 pagesWireless Control For Industrial Instruments and Home Appliences at UhfNahush Bapat100% (1)

- Using SIGA-CC2A With Supervised SpeakersDocument3 pagesUsing SIGA-CC2A With Supervised SpeakersRaviNo ratings yet

- Droplet Ejection Performance of A Monolithic Thermal Inkjet Print HeadDocument9 pagesDroplet Ejection Performance of A Monolithic Thermal Inkjet Print HeadTiffany RusNo ratings yet

- ECE ExperimentDocument13 pagesECE Experimentasm98090% (1)

- Inclusion Complex Formation of Cyclodextrin and PolyanilineDocument4 pagesInclusion Complex Formation of Cyclodextrin and PolyanilineElbahi DjaalabNo ratings yet

- Explain About Push Pull Amplifier PDFDocument2 pagesExplain About Push Pull Amplifier PDFBraxton0% (1)

- MDD1903 PDFDocument4 pagesMDD1903 PDFWings Techno ServicesNo ratings yet

- Line-Commutated Converters: Manual With Solutions For Teachers SH5007-3A 2nd Edition Author: Prof. SchauerDocument122 pagesLine-Commutated Converters: Manual With Solutions For Teachers SH5007-3A 2nd Edition Author: Prof. SchauerjohnizNo ratings yet

- High-power CD player service manualDocument70 pagesHigh-power CD player service manualGiovanni Carrillo VillegasNo ratings yet

- L6 Rectifier, PIVDocument25 pagesL6 Rectifier, PIVkaloy33No ratings yet

- SN74LVC07Document23 pagesSN74LVC07abcdNo ratings yet

- LG 42pq70br-TaDocument29 pagesLG 42pq70br-TaGordon Elder100% (1)

- Det01cfc High Speed Detector IngaasDocument20 pagesDet01cfc High Speed Detector Ingaasnithin_v90No ratings yet