Professional Documents

Culture Documents

Vikas Maheshwari

Uploaded by

maheshwari_vikas1982Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vikas Maheshwari

Uploaded by

maheshwari_vikas1982Copyright:

Available Formats

Estimation of Delay, Power, and Bandwidth for On-Chip

VLSI Global Interconnects

Vikas Maheshwari

M.Tech-Final Year (Microelectronics & VLSI)

(08/ECE/455 )

Under the supervisions of

Dr. Ashis Kumar Mal Mr. Rajib Kar

Asst. Professor, ECE Deptt Asst. Professor, ECE Deptt

N.I.T. Durgapur N.I.T. Durgapur

Content

I ntroducti on

Moment Matchi ng and Model Order Reducti on

I nterconnect Models

Di stri buted RC Tree Model

Di stri buted RLC Tree Model

Di stri buted RLCG Tree Model

Conclusi on

Future Prospects

Publi cati ons

References

Introduction

Interconnection is a medium through which

signal propagates from point A to reach other points,

such as B and C.

In the nanotechnology age, as ultra deep sub-micron effects

continue to wreak havoc on the integrity of the signal, so efficient

and accurate computation of interconnect parameters has become

critical.

Due to the large number and complex nature of on-chip

interconnects, the accurate estimation of the propagation delay in

the interconnects is very important for the design of high speed

VLSI systems.

This work presents the analysis and parameters estimation of RC,

RLC and RLCG interconnects. Topics covered in this work

include on-chip interconnect delay , bandwidth, crosstalk and

power modeling for different interconnect models.

Moment Matching

Moments of the impulse response are widely used for interconnect

delay analysis, from the explicit Elmore delay expression, to

moment matching methods which creates reduced order trans-

impedance and transfer function approximations.

If more moments are required for an accurate approximation,

moment matching or other order reduction schemes can be used to

generate reduced-order dominant pole/zero approximations for the

interconnect transfer, admittance, and impedance functions.

Consider the simple RC ladder circuit shown in Figure 1 We can

express the transfer function of this circuit as

Figure 1 Simple RC ladder Circuit

m

m

n

n

s b s b s b

s a s a s a a

s Vin

s Vout

s H

+ + + +

+ + + +

= =

........ .......... .......... 1

...... .......... ..........

) (

) (

) (

2

2 1

2

2 1 0

where m>n

Expanding this equation about s = 0 we can rewrite the transfer function

as a series in powers of s :

where the coefficients, m

j

s are known as circuit moments and can be

shown as

It is straightforward to show that the first few central moments can be

expressed in terms of circuit moments as follows

.. .......... .......... .......... .......... ) (

3

3

2

2 1 0

+ + + + = s m s m s m m s H

( )

}

=

0

) (

!

1

dt t h t

q

m

q

q

q

+ =

=

=

= =

1

0

2

1

0

2 1

3 3

0

2

1

2 2

1

0 0

2

6

6

2

0

1

m

m

m

m m

m

m

m

m

m

0

is the area under the curve.

2

is variance of the distribution

3

is a measure of the skew ness

(1)

(2)

(3)

The aim of MOR is to perform the simulation and analysis on the

reduced system instead of the original one in order to increase

computational efficiency.

MOR is the technique that approximates the original large scale system

with a smaller scale system without introducing much degradation of

accuracy in both frequency and time domains.

Fig.2 demonstrates the general mechanism of MOR in a single-input

single-output where r<<n such that the transfer function of the reduced-

order system is approximated to that of the original one, i.e.,

Model Or der Reduction

) (

) ( s G s G ~

) r order ( system reduced the of Function Transfer

s b

.......... .......... s a s a 1

s b

....... .......... .......... s b

s b

) s ( G

) n order ( system original the of Function Transfer

s b .......... .......... s a s a 1

s b ....... .......... .......... s b s b b

) s ( G

1 s

1 r

2

2 1

1 r

1 n

2

2 1 0

1 r

1 r

2

2 1

1 n

1 n

2

2 1 0

+ + + +

+ + +

=

+ + + +

+ + +

=

Figure 2: MOR approximates the large scale original system of order n with a smaller scale

system of order r.

I nter connect Models

On-chip global interconnect lines are modeled in three types as discussed

bellow

Distributed RC Interconnect Model

Distributed RLC Interconnect Model

Distributed RLCG Transmission line Interconnect Model

Distributed RC interconnect models are of three types L, T, as shown

in figure 3.

L-Type T-Type -Type

Distr ibuted RC Tr ee Model

On-chip VLSI interconnect is most often modelled by RC tree. The RC

model is easy to compute, but relatively inaccurate. Figure 4 shows a

typical RC tree.

Figure 4 An Interconnect and its electrical model

For a uniform structure with a rectangle cross-section the resistance is

given by

|

.

|

\

|

=

w

l

R R

S

t

R

S

=

Where

p, l, t, and w are the resistivity, length,

thickness, and width of the wire

For capacitance extraction many different techniques can be employed.

Depending on the desired accuracy, these methods can vary from using

very simple 2-D analytical models to employing 3-D electrostatic field

solvers.

The simplest curve-fitting based model approximates the per-unit-length

capacitance as

One conservative estimate for the number of lumped segments (N)

required to model a URC, based on the maximum signal frequency of

interest, is obtained by solving

(

(

|

.

|

\

|

+

|

.

|

\

|

=

222 . 0

8 . 2 15 . 1

h

t

h

w

C

w C C C

1 0

+ =

( )

(

|

.

|

\

|

s

N

N

RC

N

f

2

1 2

cos 1

2

2

max

(4)

(5)

(6)

(4)

(5)

Venue: N.I.T. Durgapur, W.B.

RC Delay Model Based on Gamma

Distribution

Elmore assumed and therefore approximated the median (the

desired delay) by the mean of the impulse response.

The main idea behind our Delay metrics is to match the mean and

variance of the impulse response to those of Gamma distribution.

The Gamma distribution is a two parameter continuous distribution. It

is well suited to match the impulse response of the generalized RC

network since both are unimodel and have non-negative skewness.

The PDF of Gamma distribution is shown in the following figure-5.

1

m k =

Figure 5 The Gamma Distribution Function

The probability density function of gamma distribution g

, n

(t), is a

function of one variable t and two parameters and n

Gammas cumulative distribution function [CDF] as a function of t is

given by

CDF must satisfy the following conditions

Calculation of Parameters of the Gamma Distribution Function

Mean and Variance of the Gamma function is given by

0 ,

) (

) (

1

,

>

I

=

t

n

e t

t g

t n n

n

0 , ) (

0

1

> = I

}

x dy e y x

y x

Where

0 , 1 ) ( > =

t e t h

t

0 ) ( , 1 ) ( 1 ) ( 0

0

= = s s

t F Lim t F Lim and t F

t t

1

m

n

=

( )

2

2

1

2

2m m

n

=

(7)

(8)

(9)

From (8) and (9),

Calculation of Median (50 % Delay) of the Gamma Distribution Function

Median of Gamma function is given by

Mode=3*Median-2* Mean

From (3.27) and (3.28),

2

2

1

2

1

2

2

1

1

2

2 m m

m

n and

m m

m

=

(10)

( )

=

(

=

(

=

+

=

3

1

3 /

1

3

3 / 2

1

3

2

n n

n n Mean Mode

Median

(11)

+ =

|

|

.

|

\

|

=

1

2

1

1

2

2

1

1

3

2

3

4

- %) (50 Delay or,

3

2

m

m

m

m

m m

m Median

(12)

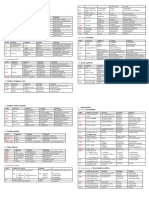

Experimental Set-Up

We have implemented the proposed delay estimation method using

Gamma Distribution and applied it to widely used actual interconnect RC

networks as shown in Figure6. For each RC network source we put a

driver, where the driver is a voltage source followed by a resister.

We compare the delays obtained from SPICE with those found using our

proposed model. The results for the 50% delay are summarized in Table

1.

(2) (4)

(5)

(6)

(7)

(1) (3)

60 ohm

1.2pF

1pF

60 ohm

1.2pF

60 ohm

1pF

60 ohm

1pF

60 ohm 60 ohm

1pF

+

-

Vin

0.5pF

80 ohm

Figure 6 An RC Tree Example

Experimental Result

0.451 0.452 7

0.373 0.375 6

0.923 0.919 5

0.828 0.845 4

0.697 0.700 3

0.493 0.477 2

0.234 0.196 1

Proposed Model (ns) SPICE (ns) Node

Table 1 Comparison of the 50% delays between SPICE and the Proposed

Delay Metric (time in ns).

Distr ibuted RLC Tr ee Model

Importance of On-Chip Inductance

With advanced technology trends, on-chip inductance effects, such

as delay increase, overshoot, and inductive crosstalk, can no longer

be ignored. Inductance effects have become increasingly significant

because:

As the clock frequency increases and the rise time decreases,

electrical signals comprise more and more high frequency

components, making the inductance effect more significant.

With the increase of chip size, it is fairly typical that many wires are

long and run in parallel, which increases the inductive crosstalk.

Due to the lack of highly conductive ground planes on the chips, the

mutual coupling between the wires cover very long ranges and

decrease very slowly with the increase of spacing.

Effect of Inductance

A key aspect of RLC delay estimation is first controlling the damping,

then approximating the delay. Excessive settling time increases delay in

some sense, both under-damping and over-damping adversely impact

delay. This is evidenced by the responses in Figure 7(b) for the series

terminated RLC line in Figure 7(a).

Figure 7 (a) A source terminated RLC Transmission Line. (b) Response of the RLC

system as R

S4

>R

S3

>R

S2

>R

S1

.

Power-Estimation using Model

Order Reduction Technique

We consider a distributed RLC line as shown in Figure 8

Suppose that it is excited by a step input. Then, the Laplace transform of

v(x, t) for a distributed RLC line of infinite length is given by

Fig 8 A distributed RLC Interconnect

B A s x V s x V

in out

. ). , ( ) , ( =

tr

R

s

l

r

s

Z

s

l

r

s Z

A

+

+

+

=

) (

/ ) (

0

0

Where

) (

l

r

s s lc x

e B

+

=

For the step input the output equation is (by taking Rtr=r)

The current equation in the time domain is given by

By applying Laplace transform on both side of

) (

) (

/ ) (

) , (

l

r

s s lc x

out

e

r

s

l

r

s

c

l

s

s

l

r

s

c

l

s x V

+

|

|

|

|

.

|

\

|

+

+

+

=

x

t x v

r

t x I

c

c

=

) , ( 1

) , (

( )

s r

s

)

l

r

s (

lc rs

e )

l

r

s ( lc

))

l

r

s ( s ( lc e

r

s

)

l

r

s (

c

l

s

s / )

l

r

s (

c

l

r

1

) s , x ( I

2

)

l

r

s ( s lc x -

)

l

r

s ( s lc x

+

+

+

=

+

|

|

|

|

.

|

\

|

+

+

+

=

+

+

By equating the denominator term to zero, we get the pole of I(x, s) as

The pole P

2

is in the left half of the s-plane, so we can write

The residue of I(x, s) at pole P

2

is given by

Thus the energy dissipation at the arbitrary position is given by

2

2 1

0

cr l

r

P and P

= =

2

2

) 2 (

2 2

2

2

) ) 2 ( (

) 2 (

) , (

cr l

cr l c r

x

e

cr l c r

cr l c

p x I

+

=

2

2

2

2 2

) , ( ) ( lim

cr l

rc r

x

p s

e rc s x I p s r

= =

2

2

2

2

2

cr l

rc ) cr l 2 ( c r

x

2 2

2

3 2

cr l

) cr l 2 ( c r

x

2 2 2

2

cr l

rc r

x

2

2

e

) ) cr l 2 ( c r (

) cr l 2 ( c

c r

e

) ) cr l 2 ( c r )( cr l (

) cr l 2 ( c

e . rc r

) p , x ( I residue r ) x ( E

|

.

|

\

|

+

+

=

+

=

=

The obtained expression for the distribution of energy dissipation can be

plotted as an exponential form as shown in the Figure-9.

We have implemented the proposed power estimation method using

Model Order Reduction technique and applied it to widely used actual

interconnect RLC networks as shown in Figure-10.

Fig 9 The Distribution of Energy Dissipation for a distributed RLC Interconnect

Table-2 gives the comparative result of the energy dissipation computed

using SPICE and our method.

9.57X10

5

10

6

8.8X10

5

10

6

9.35X10

4

10

5

8.5X10

4

10

5

9.25X10

3

10

4

8.6X10

3

10

4

9.2X10

2

10

3

8X10

2

10

3

795 8X10

2

700 8X10

2

590 6X10

2

575 6X10

2

85 10

2

75 100

10 10 10 19

8 8 8 8

1 1 1 1

0.2 0.2 0.2 0.2

Our Model (J) SPICE Model (J) Our Model (J) SPICE Model (J)

No of Nodes=1500 No of Nodes=1000

Table-2 Comparison of the energy distribution for randomly generated RLC circuit

Figure-11 & Figure-12 show the graphical representation of the result for

the circuit with 1000 and 1500 nodes respectively.

Fig-11. Comparison of the energy distribution

for randomly generated RLC circuit with

1000 nodes

Fig-12. Comparison of the energy distribution

for randomly generated RLC circuit with

1500 nodes

Distributed RLCG Tree Model

In case of very high frequency as in Giga scale (GHz), no longer can

interconnects be treated as mere delays or lumped RC networks. The

most common simulation model for interconnects is the distributed

RLC and RLCG model.

In this case, the commonly and generally well-accepted Elmore delay

calculation becomes inapplicable to RLC and RLCG interconnect

networks due to their non-monotonic characteristics induced by

inductances.

Interconnect lines may be coupled to study the effects of mutual

inductive and capacitive coupling.

Our model considers both lossless components (i.e. L, C) and lossy

components (i.e. R, G). The SPICE simulation justifies the accuracy

of our proposed approach.

Transmission Line Model

An infinitesimal unit length of the transmission line looks like the circuit

as shown in Figure 13. The parameters are defined as R, L, C and G is

Series resistance, Series inductance, Shunt capacitance and Shunt

conductance per unit length.

The following is a simple rule of thumb which can be used to determine

when to use transmission line models.

Fig 13. RLCG parameters for

a segment of a transmission

line.

{ }

{ }

{ } elling lumped

v

l

elling lumped or line on transmissi either

v

l

v

l

elling line on transmissi

v

l

fall rise

fall rise

fall rise

mod 5 ) (

mod 5 ) ( 5 . 2

mod 5 . 2 ) (

|

.

|

\

|

>

|

.

|

\

|

< < |

.

|

\

|

|

.

|

\

|

<

Crosstalk

Crosstalk is undesired energy imparted to a transmission line due to

signals in adjacent lines. The crosstalk noise between two shielded

interconnects can produce a peak noise of 15% of V

DD

in a 0.18 um

CMOS technology. In the complicated multilayered interconnect system,

signal coupling and delay strongly affect circuit performances .

Major impacts of cross talk are:

(I) Crosstalk induces delays, which change the signal propagation time,

and thus may lead to setup or hold time failures.

(II) Crosstalk induces glitches, which may cause voltage spikes on wire,

resulting in false logic behaviour. Crosstalk affects mutual inductance as

well as inter-wire capacitance.

(III) crosstalk will induce noise onto other lines, which may further

degrade the signal integrity and reduce noise margins

(IV) crosstalk will change the performance of the transmission lines in a

bus by modifying the effective characteristic impedance and propagation

velocity .

Difference Model Approximation

The time-domain difference approximation procedure should be

employed only if transient characteristics are available .

It can directly handle lines with arbitrary frequency-dependent

parameters or lines characterized by data measured in frequency-domain

For a single RLCG line, the analytical expressions are obtained for the

transient characteristics and limiting values for all the modules of the

system and device models.

The difference approximation procedure involves an approximation of

the dynamic part of the system transfer function, with the complex rational

part of the transient characteristic with the real exponential series.

Modeling of Bandwidth Using

Difference Model Approximation

We first consider the interconnect system consisting of single uniform line

and ground as shown in Figure 14, and assume the length of the line is d.

The electrical parameters of each section are R

X

, L

X

, C

X

and G

X

,

respectively, where R, L, C and G are per-unit length resistance,

inductance, capacitance and conductance of the line.

Fig. 14 Equivalent circuit of each uniform section

Using Kirchoffs Law, we can write

Simplifying the above two equations and applying Laplace

transformation, we get

Differentiating equations (3) and (4) with respect to x, and after

simplifying we get,

) , (

) , (

) , ( ) , ( t x x v

dt

t x di

L R t x i t x v

x x

A + + + =

A A

) , (

) , (

) , ( ) , ( t x x i

dt

t x x dv

c t x x v G t x i

x x

A + +

A +

+ A + =

A A

) ( ) (

) (

x I sL R

x

x V

+ =

c

c

) ( ) (

) (

x V sC G

x

x I

+ =

c

c

) (

) (

2

2

2

x V

x

x V

P =

c

c

) (

) (

2

2

2

x I

x

x I

P =

c

c

(1)

(2)

(3)

(4)

(5)

(6)

The general solution of equation (5) is given by

Where A

1

and A

2

are the constants determined by the boundary

conditions. From equations (5) and (7 )

Assuming at x=d, the termination voltage and current are V (d) =V2 and

I (d) =I2, respectively, then we get,

From equation (9) and (10) we get

x x

e A e A x V

P P

+ =

2 1

) (

(7)

| | ) ( ) (

2 1

x I sL R e A e A

x

x x

+ = +

c

c

P P

| |

x x

e A e A

Z

x I

P P

=

2 1

0

1

) (

(8)

d d

e A e A V

P P

+ =

2 1 2

] [

1

2 1

0

2

d d

e A e A

Z

I

P P

=

| |

d

e Z I V A

P

+ =

0 2 2 1

2

1

| |

d

e Z I V A

P

=

0 2 2 2

2

1

(9)

(10)

Substituting these values of A1 and A2 in equation (7)

Similarly we calculate for I (x) as

Let at x=0, V(x) =V

1

and I(x) =I

1

then from equation (9) and (11), we can

write

So we can write ABCD matrix from equation (13) and (14)

| | | |

(

+

+

=

P P ) ( 0 2 2 ) ( 0 2 2

2 2

) (

d x x d

e

Z I V

e

Z I V

x V

| | | |

(

+

=

P P ) ( 0 2 2 ) ( 0 2 2

0

2 2

1

) (

d x x d

e

Z I V

e

Z I V

Z

x I

(11)

(12)

2 0 2 1

) sinh( ) cosh( I d Z V d V P + P =

2 2

0

1

) cosh( ) sinh(

1

I d V d

Z

I P + P =

(13)

(14)

(

(

(

(

P P

P P

=

(

2

2

0

0

1

1

) cosh( ) sinh(

1

) sinh( ) cosh(

I

V

d d

Z

d Z d

I

V

(15)

From equation (15), we can write the equation for the transfer function of

the system

After simplification, we get from equation (16)

Substitute s=j in equation (17) and after simplification

Apply modulus on both side and equate to ,we get

) cosh(

1

) (

) (

) (

1

2

d s V

s V

s H

P

= =

(16)

) )( (

1

) (

) (

) (

1

2

C

G

s

L

R

s

s V

s V

s H

+ +

= =

(17)

|

.

|

\

|

+ +

=

C

G

L

R

j

CL

RG

j H

2

1

) (

2

2

2

2

1

2

1

|

.

|

\

|

+ + |

.

|

\

|

=

C

G

L

R

CL

RG

(18)

(19)

2

1

After simplification, we get 3-dB bandwidth in Hz and is given as,

The above equation (20) is our proposed closed form bandwidth

expression taking crosstalk noise voltage into consideration for distributed

RLCG interconnects line.

In Table 3, results are summarized for the 10mm length of interconnect at

different operating frequencies when the values of source resistant R

S

and

load capacitance C

L

are kept constant .

2

8

2

1

2 2

2

2 2

3

|

|

.

|

\

|

|

.

|

\

|

+ |

.

|

\

|

+

|

|

.

|

\

|

|

.

|

\

|

|

.

|

\

|

=

C

G

L

R

C

G

L

R

f

db

(20)

3.97 3 2.4 2.7 1.2 20

3.64 2.25 2.4 2.7 1.2 15

3.27 1.5 2.4 2.7 1.2 10

BW (GHz) G (mS) C (pF) L (nH) R (K) Frequency (GHz)

Table-3 Bandwidth for different values Operating Frequencies

Conclusion

The first part of the proposed work discussed about an efficient and

accurate interconnect delay metric based on Gamma function for

high speed VLSI RC global interconnects.

In the second part of the proposed work, a brief analytical model is

presented for calculating the delay and power for the RLC

interconnects.

The last part of the work proposed a distributed RLCG

transmission line model of interconnects using difference model

approach.

Future Prospects

Future integrated circuits design will be driven by interconnect

performance, not transistors performance.

New interconnect technologies, such as copper and low-

temperature interconnect, may introduce new problems.

Alternative solutions such as on-chip optical interconnects have

been proposed in order to avoid the problems associated with

global on-chip wires altogether.

Publications

Rajib Kar, Vikas Maheshwari, A.K. Mal, A.K. Bhattacharjee, Delay Analysis for

On-Chip VLSI Interconnect using Gamma Distribution Function, International

Journal of Computer Application (IJCA). Vol. 1, No. 3, Article 11, pp. 77-80, 2010,

Foundation of Computer Science (FCA) Press

Rajib Kar, Vikas Maheshwari, A.K. Mal, A.K. Bhattacharjee, A Model for Slew

Evaluation for On-Chip RC Interconnects using Gamma Distribution Function,

International Journal of Computer Application (IJCA).Vol. 1, No. 10, Article 13, pp.

88-93. 2010, Foundation of Computer Science (FCA) Press.

Rajib Kar, Vikas Maheshwari, Md. Maqbool, A.K.Mal, A.K.Bhattacharjee , An

Explicit Model of Delay and Slew Metric for On-Chip VLSI RC Interconnects for

Ramp Inputs using Gamma Distribution Function, International Journal of Recent

Trends in Engineering, Academy Publisher, Finland. Vol. Issue. pp

Rajib Kar, Md. Maqbool, Vikas Maheshwari, A.K. Mal, A.K. Bhattacharjee, Power-

Estimation for On-Chip VLSI Distributed RLC Global Interconnect Using Model

Order Reduction Technique, International Journal of Computer Application (IJCA).

Vol. 1, No.14. pp. 96-101, 2010. Foundation of Computer Science (FCA) Press

Rajib Kar, Vikas Maheshwari, Md. Maqbool, A.K.Mal, A.K.Bhattacharjee, A Closed

Form Modelling of cross-talk for Distributed RLCG On-Chip Interconnects Using

Difference Model Approach, International Journal on Communication Technology

(IJCT), India

Rajib Kar, V. Maheshwari, Md. Maqbool, A.K.Mal, A.K.Bhattacharjee, An Explicit

Coupling Aware Delay Model for Distributed On-Chip RLCG Interconnects Using

Difference Model Approach, International Journal of Embedded Systems and

Computer Engineering, Vol. 2 Issue.1.pp.39-42, Serial Publications, India

Rajib Kar, Vikas Maheshwari, Md. Maqbool, Sangeeta Mandal , A.K.Mal,

A.K.Bhattacharjee , Closed Form Bandwidth Expression for Distributed On-Chip

RLCG Interconnects, IEEE International Conference on Advances in Computer

Engineering (ACE 2010), pp. June 20-21, 2010 , Bangalore, INDIA

Rajib Kar, V. Maheshwari, Aman Choudhary, Abhishek Singh, Ashis K. Mal, A. K.

Bhattacharjee, Coupling Aware Power Estimation for Distributed On-Chip RLCG

Interconnects Using Difference Model Approach, 2nd IEEE International Conference

on Computing, Communication and Networking Technologies (ICCCN 2010), 29th -

31st July, 2010 Karur, India.

Acknowledgement

I would like to express my heartily thank to my project supervisers

Dr. Ashis Kumar Mal and Prof. Rajib Kar who are the Professors

of Electronics & Communication Engineering Department N.I.T.

Durgapur, for their precious guidance & effectual care.

I want to express my deep gratitude to Dr. S.K. Dattta, Professor &

former Head, Electronics & Communication Engineering Department,

N.I.T. Durgapur, for his support, guidance and kindness throughout

my M.Tech Degree.

Refer ences

Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits Analysis and Design,

TMH Publication,2008

Intel website, http://www.intel/research/silicon/mooreslaw.htm, Sept. 2010

C. Bermond, B. Flechet, A. Fracy, V. Arnal, J. Torres, G LeCarval, G. Angenieux, and R. Salik.

Impact of Dielectrics and Metals Properties on Electrical Performances of Advanced On-Chip

Interconnect, Proceedings of the International Interconnect Technology Conference, 2002, p. 161-

163

T. Kikkawa, Current and Future Low-K Dielectrics for Cu Interconnects, Proceedings of

International Electron Devices Meeting, 2000, p. 253-256.

L. Peters, Pursuing the Perfect Low-K Dielectric, Semiconductor International, September

1998, p. 64-74. 98 Bibliography

C. Cregut, G. Le Carval, J. Chilo. Low-K Dielectrics Influence on Crosstalk: Electromagnetic

Analysis and Characterization, Proceedings of the International Interconnect Technology

Conference, 1998, p. 59-61.

R. Donaton, F. Iacopi, M Baklanov, D. Shamiryan, B. Coenegrachts, H. Struyf, M. Lepage, M

Meuris, M. Van Hove, W. Gray, H. Meynen, D. DeRoest, S. Vanhaelemeersch, K. Maex, Physical

and Electrical Characterization of Silsesquioxane-Based Ultra-Low k Dielectric Films, Proceedings

of the International Interconnect Technology Conference, 2000, p. 93-95.

S. Jang, Y. Chen, T. Chou, S. Lee, C. Chen, T. Tseng, B. Chen, S. Chang, C, Yu, and M. Liang.

Advanced Cu/Low-k (k=2.2) Multilevel Interconnect for 0.10/0.07 mm Generation, Symposium on

VLSI Technology Proceedings, 2002, p. 17-18.

M. Anders, N. Rai, R. Krishnamurthy, S. Borkar. A Transition-Encoded Dynamic Bus

Technique for High-Performance Interconnects, Symposium on VLSI Circuits Proceedings, 2002, p.

16-17.

L. T. Pillage. Coping with RC(L) interconnect design headaches. Proceedings of the IEEE/ACM

International Conference on Computer- Aided Design, pp. 246-253, September 1995.

Y. I. Ismail, E. G. Friedman, and J. L. Neves. Figures of merit to characterize the importance of on-chip

inductance. Proceedings of the IEEE/ACM Design Automation Conference, pp. 560-565, June 1998.

F. R. Awwad, and M. Nekili. Regeneration techniques for RLC VLSI interconnects. Proceedings of the

International Conference on Microelectronics, Morocco, pp. 209-212, Oct. 2001.

A. Deutsch et al. When are transmission-line effects important for on-chip interconnections?. IEEE Trans.

Microwave Theory Tech., vol. 45, pp. 1836-1846, Oct. 1997.

A.Deutsch, Electrical characteristics of interconnects for high performance system, IEEE Proceedings,

86(2): 315-355, feb.1998.

IBM Journal of Research and Development, Vol. 39, No. 4, 1995, cover photo.

G. Kron, Equivalent circuit for the field equations of Maxwell, Proc. IRE, vol. 32, no.289,1944.

Saihua Lin, Huazhong Yang, A novel d/n RLCG transmission line model considering complex RC(L)

loads, submitted to IEEE Trans. Computer-Aided Design of Integr.Circuits Syst.,2006

Richard Chang , Near Speed-of-Light On-Chip Electrical Interconnects Ph.D. Dissertation , Stanford

University, November 2002

E. Chiprout, and M.S. Nakhla, Asymptotic Waveform Evaluation, Kluwer Academics Publishers, 1994

L.T. Pillage, R.A. Rohrer, and C. Visweswariah, Electronic circuit and System Simulation Methods,

McGraw-Hill, 1995.

W. C. Elmore, The Transient Response of Damped Linear Networks with Particular Regard to Wideband

Amplifiers, J. Applied Physics, vol. 19, no. 1, Jan. 1948. Pagees :55 63 R. Kay and

L.Pilggi,PRIMO:Probability interpretation of Moments for delay Calculation, Proc. ACM/IEEE Design

Automation conf.,june 1998. Pages: 463 - 468

R. Gupta, B. Tutuianu and L. Pileggi, The Elmore Delay as Bound for RC Trees Generalized input

Signals, IEEE Trans. Computer-Aided Design, vol. 16, no. 1, January 1997. Pagees :95 104

Celik Mustafa, Lawrence Pileggi, Alten Odabasioglu, IC Interconnect Analysis, Kluwer Academic

Publishers, 2002

Pillage L.T and Rohrer R.A, Asymptotic Waveform Evaluation for timing analysis, IEEE Transactions on

Computer-Aided Design, Vol. CAD-9, No. 4, pp. 352 - 366, April 1990

Rubinstein, P. Penfield, Jr., and M. A. Horowitz, Signal delay in RC tree networks, IEEE Trans. on

Computer Aided Design, vol. 2, pp. 202-211, 1983.

Chandramouli V. Kashyap, Charles J. Alpert, Frank Liu, and Anirudh Devgan, PERI: A Technique for

Extending Delay and Slew Metrics to Ramp Inputs International Symposium on Physical Design archive

Proceedings of the 2003 ,Pages: 24 - 31

Alpert, C.J., A. Devgan and C.V. Kashyap, RC delay metric for performance optimization, IEEE Trans.

Computer-Aided Design, vol. 20, No. 5, pp. 571-582, May 2001

Lin, T., E. Acar and L. Pileggi, H-gamma: An RC delay metric based on Gamma distribution

approximation of the homogeneous response, Proc. IEEE/ACM Intl. Conf. Computer- Aided Design, 1998

Weisstein, E., Eric Weissteins World of Mathematics, http:// mathworld.wolfram.com, Wolfram Research

Gupta, R., B. Tutuianu and L.T. Pileggi, The Elmore delay as a bound for RC trees with generalized input

signals, IEEE Trans. Computer-Aided Design, vol. 16, No. 1, pp. 95-104, January 1997

Elmore, W.C, The transient response of damped linear network with particular regard to wideband

amplifiers, Journal of Applied Physics, vol. 9, pp. 55-63, 1948

Gupta, R., B. Tutuianu and L.T. Pileggi, The Elmore delay as a bound for RC trees with generalized input

signals, IEEE Trans. Computer-Aided Design, vol. 16, No. 1, pp. 95-104, January 1997

R.Kay and L.Pileggi, PRIMO: Probability Interpretation of Moments for Delay Calculation, IEEWACM

Design Automation Conference, 1998, pp. 463-468.

T. Lin, E. Acar, and L. Pileggi, h-gamma: An RC Delay Metric Based on a Gamma Distribution

Approximation to the Homogeneous Response, IEEE/ACM International Conference on Computer-Aided

Design, 1998, pp. 19-25.

C. Chu and M. Horowitz, Charge-Sharing Models for Switch Level Simulation, Trans. on CAD, Volume 6,

Issue 6 June, 1987.

Harald Cramer. Mathematical Methods of Statistics. Princeton University Press, 1946.

R.Kay and L.Pileggi, PRIMO: Probability Interpretation of Moments for Delay Calculation, IEEWACM

Design Automation Conference, 1998, pp. 463-468.

H. L MacGillivray, The Mean, Median, Mode Inequality and Skewness for a Class of Densities,

Australian J. of Statistics, vol. 23 no. 2, 1981.

H. J. Larson, Introduction to Probability Theory and Statistical Inference, 3rd ed., John Wiley & Sons

pub., 1982.

Bakoglu, H. B., Circuits, Interconnects, and Packaging for VLSI. Addison-Wesley Publishing Company,

1990.

Kar, R.; A.K. Mal, A. K. Bhattacharjee, An Accurate Slew Metric for on-chip VLSI Interconnect using

Weibull Distribution Function ACM ICAC3 2009. 601-604 January 2009.

R. Kar, V. Maheshwari, Ashis K. Mal, A.K. Bhattacharjee, Delay Analysis on-chip VLSI Interconnect using

Gamma Distribution Function, International Journal of Computer Applications Volume 1 No. 3, pp. 77-80,

2010. R.Kar, A. Chattaraj, A.Chandra, A.K.Mal, A.K.Bhattacharjee, Delay Estimation for On-Chip VLSI

Interconnect using Weibull Distribution Function, IEEE Region 10 Colloquium and the Third ICIIS , pp- ,

2008

Charles J. Alpert, Frank Liu, Chandramouli Kashyap, and Anirudh Devgan. Delay and Slew Metrics Using

the Lognormal Distribution. DAC 2003, pp. 382-385.

Chandramouli V. Kashyap, Charles J. Alpert, Frank Liu, and Anirudh Devgan, PERI: A Technique for

Extending Delay and Slew Metrics to Ramp Inputs Proceedings of the 8th ACM/IEEE international

workshop on Timing issues in the specification and synthesis of digital systems 2002, pp. 57 62.

Rajib Kar, Ashish K. Mal, Anup K. Bhattacharjee An Accurate Slew Metric for on-chip VLSI

Interconnect using Weibull Distribution Function, International Conference on Advances in Computing,

Communication and Control (ICAC309), pp-601-604, 2009.

L. T. Pillage and R. A. Rohrer, Asymptotic Waveform Evaluation for Timing Analysis, Tran. on CAD,

Volume 9, Issue 4, 1990. pp. 331- 349

Chandramouli V. Kashyap, Charles J. Alpert, Frank Liu, and Anirudh Devgan, Closed Form Expressions for

Extending Step Delay and Slew Metrics to Ramp Inputs, International Symposium on Physical Design archive

Proceedings of the 2003 ,Pages: 24 - 31

N. N. Rao, Elements of Engineering Electromagnetics. Englewood Cliffs, NJ: Prentice-Hall, 1991

A.Deutsch, Electrical characteristics of interconnects for high performance system, IEEE Proceedings,

86(2): 315-355, feb.1998.

B. Krauter and L.T. Pileggi, Generating Sparsh Partial Inductance Matrices with Gauranteed Stability,

Proceeding of the IEEE Proceeding of the international Conference on Computer- Aided Design, pp. 45-52,

1995.

M. Beattie, B. Krauter, L. Alatan, and L. Pileggi, Equipotential Shells for Efficient Inductance Extracion,

IEEE transactions on Computer Aded design of Integrated circuits and Systems, Vol. 20, No.1, pp-70-79,

January 2001

M. beattie, S. Gupta, and L. Pileggi, Hierarchical Interconnect Circuit Models, Proceeding of the

IEEE/ACM design Automation Conference,pp. 215-221, November 2000.

A. Devgan, H. Ji, and W. Dai, How to Efficiently Capture On-Chip Inductance Effects: Introducing a New

circuit Elemecnt K, Proceeding of the IEEE/ACm Design Automation conference, pp. 150-155, November

2000.

Y. Gao and D.F. Wong, Optimal Shape Function for a Bi-directional Wire under Elmore Delay Model,

ICCAD, pp.622-627, 1997

Davis J.A and Meindl J.D, Compact distributed RLC interconnect modelsPart I: Single line transient, time

delay and overshoot expressions, IEEE Trans. Electron Devices, vol. 47, pp. 20682077, Nov.2000.

Shin Youngsoo, Sakurai T, Estimation of power distribution in VLSI interconnects,. Low Power Electronics

and Design, International Symposium on, 2001. On page(s): 370-375

Davis J.A and Meindl J.D, Compact distributed RLC interconnect modelsPart II: Single line transient,

time delay and overshoot expressions, IEEE Trans. Electron Devices, vol. 47, pp. 20682077, Nov.2000

L. Gal, On-chip crosstalk-the new signal integrity challenge, IEEE Custom Integrated Circuits

Conference, pp.251-254, 1995.

Semiconductor Industry Association, National Technology Roadmap for semiconductors, 1997.

Shien-Yang Wu, Boon-Khim Liew, K.L. Young, C.H.Yu, and S.C, Analysis of Interconnect Delay for

0.18m Technology and Beyond, IEEE International Conference Interconnect Technology, May 1999, pp.

68 70.

Deutsch, A., et al, When are Transmission-line effects important for on-chip interconnections?, IEEE

Transactions on MTT, vol.45 no.10. Oct. 1997, pp .1836-1847.

X. Qi, B. Kleveland, Z. Yu, S. S.Wong, R. W. Dutton, and T. Young, On-chip inductance modeling of

VLSI interconnects, in 2000 IEEE Int. Solid-State Circuits Conf. Dig. Techn. Papers, 2000, pp. 17273

Y. I. Ismail, E. G. Friedman and J. L. Neves, Equivalent Elmore delay for RLC trees Proceedings of the

36th ACM/IEEE conference on Design automation conference, 1999 pp. 715 - 720

[L. T. Pillage and R. A. Rohrer, Asymptotic Waveform Evaluation for timing analysis, IEEE Transactions

on Computer-Aided Design, Vol. CAD-9, No. 4, pp. 352 - 366, April 1990

J. Zhang and E. G. Friedman, Effect of Shield Insertion on Reducing Crosstalk Noise between Coupled

Interconnects, Proceeding of the IEEE International Symposium on Circuit and Systems, Vol. 2, pp. 529-532,

May 2004.

Y. Massoud, J. Kawa, D. MacMillen, J. White, Modeling and Analysis of Differential Signaling for

Minimizing Inductive Cross-Talk, IEEE/ACM DAC 2001, June 18-22, 2001, Las Vegas, Nevada, USA.

K. Lee, C. Nordquist, and J. Abraham, Test Generation for Crosstalk Effects in VLSI Circuits". IEEE

International Symposium on Circuits and Systems, Vol. 4, pp. 628-631, 1996.

Clayton R.Paul, Keith W.Whites, Syed A. Nasar Reading Introduction to Electromagnetic Fields" McGraw

Hill 1998

Clayton R.Paul, Keith W.Whites, Syed A. Nasar Reading Introduction to Electromagnetic Fields" McGraw

Hill 1998

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Music GcseDocument45 pagesMusic GcseAimee DohertyNo ratings yet

- Zarlino-On The ModesDocument150 pagesZarlino-On The ModesPartituraDireccion100% (1)

- Dynamic model of manipulatorsDocument20 pagesDynamic model of manipulatorsbalkyderNo ratings yet

- THKDocument1,901 pagesTHKapi-26356646No ratings yet

- Drager Fabius Gs Technical Service ManualDocument350 pagesDrager Fabius Gs Technical Service ManualLeonardo Chirinos100% (3)

- SDH TechnologyDocument26 pagesSDH TechnologyJayesh SinghalNo ratings yet

- Solomons Organic Chemistry Solution Manual - Chapter 3Document12 pagesSolomons Organic Chemistry Solution Manual - Chapter 3Imanghh25% (4)

- Create an access point for non-RouterOS laptop clientsDocument8 pagesCreate an access point for non-RouterOS laptop clientsGorgeus WaffleNo ratings yet

- Apriori AlgorithmDocument13 pagesApriori AlgorithmKiran JoshiNo ratings yet

- PDS - GulfSea Hydraulic AW Series-1Document2 pagesPDS - GulfSea Hydraulic AW Series-1Zaini YaakubNo ratings yet

- Serial Port InterfacingDocument5 pagesSerial Port Interfacingyampire100% (1)

- HI-8592, HI-8593, HI-8594: Single-Rail ARINC 429 Differential Line DriverDocument14 pagesHI-8592, HI-8593, HI-8594: Single-Rail ARINC 429 Differential Line DriversameeppaiNo ratings yet

- Ex - No: 4 Integrator and Differentiator Using Fpaa DateDocument4 pagesEx - No: 4 Integrator and Differentiator Using Fpaa DatechandraprabhaNo ratings yet

- Regeln Map 2Document2 pagesRegeln Map 2bruno.wetzelNo ratings yet

- Self Report QuestionnaireDocument6 pagesSelf Report QuestionnaireMustafa AL ShlashNo ratings yet

- Sem 2Document128 pagesSem 2Agustin A.No ratings yet

- 8086 Instruction SetDocument66 pages8086 Instruction SetRaj KumarNo ratings yet

- UG WeibullDocument776 pagesUG WeibullCharles GuzmanNo ratings yet

- Affixation (Landscape)Document4 pagesAffixation (Landscape)difafalahudinNo ratings yet

- Geophysical Report Megnatic SurveyDocument29 pagesGeophysical Report Megnatic SurveyShahzad KhanNo ratings yet

- DS Ac0801 GBDocument20 pagesDS Ac0801 GBHossein Jalali MoghaddamNo ratings yet

- Sensors 22 09378 v2Document13 pagesSensors 22 09378 v2FahdNo ratings yet

- Enzyme Inhibition and ToxicityDocument12 pagesEnzyme Inhibition and ToxicityDaniel OmolewaNo ratings yet

- Recomended Volume of Chain Locker PDFDocument1 pageRecomended Volume of Chain Locker PDFMayank DixitNo ratings yet

- Introduction To Curve FittingDocument10 pagesIntroduction To Curve FittingscjofyWFawlroa2r06YFVabfbajNo ratings yet

- Lsantos - Reflecting Writing For Optimization ProjectDocument2 pagesLsantos - Reflecting Writing For Optimization Projectapi-341418797No ratings yet

- Hydrogen and Its Compound.1Document10 pagesHydrogen and Its Compound.1abhishekNo ratings yet

- Geotehnical Engg. - AEE - CRPQsDocument48 pagesGeotehnical Engg. - AEE - CRPQsSureshKonamNo ratings yet

- Low-Complexity Iterative Detection For Large-Scale Multiuser MIMO-OFDM Systems Using Approximate Message PassingDocument14 pagesLow-Complexity Iterative Detection For Large-Scale Multiuser MIMO-OFDM Systems Using Approximate Message PassingNitin KumarNo ratings yet

- CI SetDocument18 pagesCI Setতন্ময় ঢালি Tanmay DhaliNo ratings yet