Professional Documents

Culture Documents

Embedded Systems 220 Control Unit Design Notes: PC: PC + 1 PC: PC PC: Operand PC: PC + Operand

Uploaded by

Mahesh JangidOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Embedded Systems 220 Control Unit Design Notes: PC: PC + 1 PC: PC PC: Operand PC: PC + Operand

Uploaded by

Mahesh JangidCopyright:

Available Formats

Embedded Systems 220 Control Unit Design Notes The von Neumann architecture is the design of a CPU that

consists of an arithmetic logic unit, a control unit, memory, and input and output devices. The innovation in this design is the idea to have the control unit decode instructions from memory, rather than follow some fixed pattern. The control unit is just like the ALU, with the exception that its accumulator (the program counter) controls the flow of the program. You should design your control unit using the same basic idea that you use for the ALU. That is, you should determine which functional modules you need, and connect these to a multiplexer. The only difference is that unlike the ALU, you cannot just use the opcode for the multiplexer input. Rather, you will need to implement some instruction decoding logic. As an example, we shall be designing a control unit for the following set of instructions. 00 xx 01 vv 02 vv 03 vv 04 aa 05 dd 06 aa 07 dd Halt the CPU (pc := pc). Load an immediate value into the accumulator (acc := vv). Add an immediate value to the accumulator (acc := acc + vv). Subtract an immediate value from the accumulator (acc := acc vv). Branch to the specified address (pc := aa). Branch by the specified distance (pc := pc + dd). If the accumulator is zero, branch to the specified address (pc := aa). If the accumulator is zero, branch by the specified distance (pc := pc + dd).

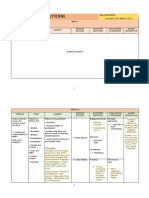

The first step is to examine these instructions and produce a complete list of arithmetic operations that can be performed on the program counter. Do not forget to include pc := pc + 1 for those instructions that do not branch anywhere. In fact, your design will be simpler if this if the first arithmetic operation in your list. 00 01 10 11 pc := pc + 1 pc := pc pc := operand pc := pc + operand

You should number each operation. Use binary numbers. Following the typical design of an ALU, you should design your CU by building the above four functional blocks and then wiring them into a multiplexer according to the numbers you gave them. You should not treat aa and dd as being something separate. They should be connected to a register containing the operand of the instruction.

Jason Foo [foo-jr@ee.uwa.edu.au]

Page 1 of 3

The next step is to design the logic that generates the two-bit input to the multiplexer. This part of the circuit is called the instruction decoder. We shall refer to the multiplexer inputs as y1 and y0. The instruction decoder should be designed by constructing a truth table. The inputs should be the opcode (x2x1x0) and any condition codes. In this circuit, there is only one condition code, which is the =0 condition (x3). The outputs are y1y0. There are two output bits, so you will be generating two Boolean functions. You could construct the truth table entirely in binary and reduce it using Karnaugh maps or the Quine-McCluskey algorithm. However, RETRO provides nice decoder blocks (the =c blocks), so we shall be writing decimal numbers into our truth table. x3 x x x x x x 0 1 0 1 x2x1x0 0 1 2 3 4 5 6 6 7 7 y1y0 01 00 00 00 10 11 00 10 00 11

The xs in the table are dont care states. To generate the above table, you need to go through each opcode, and decide which of your four PC operations applies. You only need to consider condition codes for opcodes that are dependent upon the condition. You should construct the logic for y1 and y0 separately. They are two separate Boolean functions. The resulting circuit is shown below.

Jason Foo [foo-jr@ee.uwa.edu.au]

Page 2 of 3

Most CPUs address memory in bytes. However, instructions are often larger than a single byte. In our example, the instructions are two bytes long. The control unit needs to be able to step from the first byte to the next, as well as perform branching. A signal from the timing signal generator indicates whether we are stepping or branching. We need to use a one-bit multiplexer for this switch.

Two parts of the control unit are yet to be designed. The first part is the need for two registers to fetch instructions. These registers have not been shown here. The second part is the timing signal generation. There is no straightforward approach to designing the timing signals. Rather, you should try to understand what needs to happen during each clock cycle, and how the timing signals control this. For most CPUs, in each clock cycle, you need to: 1. 2. 3. 4. 5. 6. 7. Load the opcode register (Brunls diagrams call this CODE). Increment the program counter. Load the operand register (Brunls diagrams call this ADDRESS). Wait for effective address calculations to fall through to the address bus. Wait for calculation results to fall through to the data bus. If the instruction writes to a register, then load that register. If the instruction writes to memory, then perform the memory write. Increment/branch the program counter.

There are two types of timing signal. Some are square hat pulses, that clock risingedge triggered components, such as registers. Others are high or low for extended periods of time. These switch multiplexers, and are high for the exact period of time necessary for other signals to clock rising-edge triggered components. You need to look at the timing diagram in the lecture notes, and think about it until you understand what each signal is doing. Think about it in terms of what happens in what order during a clock cycle. You need to do this on your own to understand it.

Jason Foo [foo-jr@ee.uwa.edu.au]

Page 3 of 3

You might also like

- Understanding Controversial Tattoos and SymbolsDocument40 pagesUnderstanding Controversial Tattoos and Symbolsbubu100% (2)

- Peter L. McLaren - Schooling As A Ritual Performance - Towards A Political Economy of Educational Symbols and Gestures-Routledge & Kegan Paul (1986) PDFDocument336 pagesPeter L. McLaren - Schooling As A Ritual Performance - Towards A Political Economy of Educational Symbols and Gestures-Routledge & Kegan Paul (1986) PDFMariano ChervinNo ratings yet

- Datastage Interview QuestionsDocument18 pagesDatastage Interview QuestionsGanesh Kumar100% (1)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Generic Sen StrategiesDocument5 pagesGeneric Sen Strategiesapi-264819644No ratings yet

- 2022 2023 Courseoutline Architectural Analysis and CriticismDocument8 pages2022 2023 Courseoutline Architectural Analysis and CriticismNancy Al-Assaf, PhDNo ratings yet

- Norveski - OsnovaDocument3 pagesNorveski - OsnovaTina Tinche GluscevicNo ratings yet

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 pagesUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaNo ratings yet

- Re-Entry-Plan-SEAMEO-2 HHHHHDocument2 pagesRe-Entry-Plan-SEAMEO-2 HHHHHALMA DIZON100% (2)

- Q.1) A) - Explain (1) ALU: DefinitionDocument16 pagesQ.1) A) - Explain (1) ALU: DefinitionAmee PandyaNo ratings yet

- Introduction To Computer ArchitectureDocument23 pagesIntroduction To Computer ArchitectureLwanga Charles Chas100% (1)

- IT225: Computer Organizations: August 25, 2014 (Monday)Document12 pagesIT225: Computer Organizations: August 25, 2014 (Monday)skiloh1No ratings yet

- lab1_specDocument6 pageslab1_spec星期三的配音是對的No ratings yet

- Cpu DesignDocument11 pagesCpu DesignnatyNo ratings yet

- Computer Architecture: Processor StructureDocument6 pagesComputer Architecture: Processor StructureEiEiPustaNo ratings yet

- Ladder Logic For PIC and AVRDocument9 pagesLadder Logic For PIC and AVRCarlos Cesar MaiaNo ratings yet

- Arithmetic Logic Unit: From Wikipedia, The Free EncyclopediaDocument5 pagesArithmetic Logic Unit: From Wikipedia, The Free Encyclopediahotboy7245No ratings yet

- Coa MidDocument7 pagesCoa Midmulugetahiluf995No ratings yet

- Architecture 2020Document10 pagesArchitecture 2020honey arguellesNo ratings yet

- Unit-1 CoaDocument26 pagesUnit-1 CoaArun KrishNo ratings yet

- Lab Project: Shift-and-Add Multiplication Circuit With StorageDocument5 pagesLab Project: Shift-and-Add Multiplication Circuit With StoragesneophNo ratings yet

- Mcs 012 PDFDocument397 pagesMcs 012 PDFIshan TiwariNo ratings yet

- Lab1 15Document5 pagesLab1 15Eng:ehab AlmkhlafiNo ratings yet

- Software Stage EDocument19 pagesSoftware Stage ETim TaylorNo ratings yet

- Arithmetic Logic Unit (ALU)Document11 pagesArithmetic Logic Unit (ALU)Ryan MaulanaNo ratings yet

- 3 Bit Down CounterDocument6 pages3 Bit Down CounterMustafa IqbalNo ratings yet

- Lectures Section 3 ModifiedDocument73 pagesLectures Section 3 ModifiedcoventryUkNo ratings yet

- Arithmetic UnitDocument5 pagesArithmetic UnitpatrickNo ratings yet

- Efficient 16-bit Parallel Multiplier DesignDocument62 pagesEfficient 16-bit Parallel Multiplier Designsenthilvl80% (5)

- EE 222 Assignment No 1Document17 pagesEE 222 Assignment No 1Ahmed Razi UllahNo ratings yet

- DSPACE Procedure With MPPT ExampleDocument21 pagesDSPACE Procedure With MPPT ExampleSri SriNo ratings yet

- Calculator: Jump To Navigation Jump To SearchDocument12 pagesCalculator: Jump To Navigation Jump To SearchDexterNo ratings yet

- D 32-CPU: Esign of A Bit Single CycleDocument11 pagesD 32-CPU: Esign of A Bit Single CycleAritra GuptaNo ratings yet

- Milestone 2-UpdatedDocument13 pagesMilestone 2-UpdatedHưng Nguyễn ThànhNo ratings yet

- ArchitectureDocument112 pagesArchitectureKrishnaveni DhulipalaNo ratings yet

- MCS-012 Block 1Document103 pagesMCS-012 Block 1Abhishek VeerkarNo ratings yet

- ECE486 Lab ManualDocument106 pagesECE486 Lab ManualDR ARINDAM SENNo ratings yet

- Tutorial ProjectDocument16 pagesTutorial ProjectMuhammadNizarArifansyahNo ratings yet

- Lecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsDocument5 pagesLecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsrinobiNo ratings yet

- Hardwired ControlDocument6 pagesHardwired Controlapi-19967001No ratings yet

- Milestone2 Ee3043Document14 pagesMilestone2 Ee3043teoNo ratings yet

- Arithmetic Logic UnitDocument11 pagesArithmetic Logic UnitPrasanna Kumar VotarikariNo ratings yet

- Labsheet 1: Problem 1: Subtractor DesignDocument4 pagesLabsheet 1: Problem 1: Subtractor Designanon_248257978No ratings yet

- ECN 252 Lab 9 Design Using VHDLDocument1 pageECN 252 Lab 9 Design Using VHDLGajananNo ratings yet

- Ch01 Basic Concepts and Computer EvolutionDocument36 pagesCh01 Basic Concepts and Computer EvolutionMark ShanNo ratings yet

- Ladder Logic For PIC and AVRDocument6 pagesLadder Logic For PIC and AVRTomás Totaro100% (1)

- Digital Calulator Using 89C52 Micro ControllerDocument8 pagesDigital Calulator Using 89C52 Micro Controllerchachunasayan75% (4)

- Computer Architecture 2 MarksDocument32 pagesComputer Architecture 2 MarksArchanavgs0% (1)

- Lab IV Lecture 2: Step 1 Review Introduce Step 2 Course Web PageDocument38 pagesLab IV Lecture 2: Step 1 Review Introduce Step 2 Course Web PageKulanthaivelu RamaswamyNo ratings yet

- DP 2 SolDocument14 pagesDP 2 Solchanuka469No ratings yet

- Lecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsDocument5 pagesLecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsTaqi ShahNo ratings yet

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDocument10 pagesCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNo ratings yet

- Calculator Guide: History, Design & UsesDocument8 pagesCalculator Guide: History, Design & UsesJef PerezNo ratings yet

- 1.4.1 CPU ArchitectureDocument11 pages1.4.1 CPU ArchitectureAbbas HaiderNo ratings yet

- Lab 6Document7 pagesLab 6Koteswara Rao VaddempudiNo ratings yet

- DLD Second Assignment (15-FEB-17)Document16 pagesDLD Second Assignment (15-FEB-17)Adil aliNo ratings yet

- Computer Architecture: CPU, Memory and Stored ProgramsDocument53 pagesComputer Architecture: CPU, Memory and Stored Programsdrusilla bagaboNo ratings yet

- Ec6232 Lab-ManualDocument74 pagesEc6232 Lab-ManualSuyash MishraNo ratings yet

- ATMEGA8 Expt 1Document2 pagesATMEGA8 Expt 1कुलदीप पुरोहितNo ratings yet

- 4-Bit AluDocument45 pages4-Bit AluAllam Rajkumar0% (1)

- Exp - 08 Flight86Document6 pagesExp - 08 Flight86Muhammad SaqibNo ratings yet

- Lab 7e Preliminary Design and Layout of An Embedded SystemDocument2 pagesLab 7e Preliminary Design and Layout of An Embedded Systemiky77No ratings yet

- ECE448 S12 In-Class MidtermDocument3 pagesECE448 S12 In-Class Midtermbilalhabib2001No ratings yet

- Mentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingDocument22 pagesMentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingHairil HanifNo ratings yet

- Glosario InglésDocument10 pagesGlosario InglésLorena MonroyNo ratings yet

- Lab 7 UART DesignDocument6 pagesLab 7 UART Designaditya220No ratings yet

- List of PublicationsDocument1 pageList of PublicationsMahesh JangidNo ratings yet

- IJEECS NumeralDocument6 pagesIJEECS NumeralMahesh JangidNo ratings yet

- PaperDocument1 pagePaperMahesh JangidNo ratings yet

- All HHHH 100Document7 pagesAll HHHH 100Mahesh JangidNo ratings yet

- 00777823Document4 pages00777823Mahesh JangidNo ratings yet

- A Novel Approach: Recognition of Devanagari Handwritten NumeralsDocument6 pagesA Novel Approach: Recognition of Devanagari Handwritten NumeralsMahesh JangidNo ratings yet

- CPP QuestionsDocument8 pagesCPP Questionsjagdish750No ratings yet

- PXC 3872224Document8 pagesPXC 3872224Mahesh JangidNo ratings yet

- Ddos AttackDocument10 pagesDdos AttackMahesh JangidNo ratings yet

- Acd 10Document1 pageAcd 10Mahesh JangidNo ratings yet

- CMRT09 Fabrizio Et AlDocument6 pagesCMRT09 Fabrizio Et AlMahesh JangidNo ratings yet

- Tales From The Rabbi's Desk - Volume TwoDocument11 pagesTales From The Rabbi's Desk - Volume Twojohn parkerNo ratings yet

- UNIT 10 - LESSON 2 - PART 2 - GrammarDocument4 pagesUNIT 10 - LESSON 2 - PART 2 - Grammarponyo100% (1)

- Namespace: "Application.H" "Staticfunctions.H"Document6 pagesNamespace: "Application.H" "Staticfunctions.H"iDenisNo ratings yet

- Phases of Reading Development ProjectDocument13 pagesPhases of Reading Development Projectapi-609310518No ratings yet

- RWS - Action PlanDocument88 pagesRWS - Action Planvimar fabonanNo ratings yet

- Activity 1 ADC To DACDocument14 pagesActivity 1 ADC To DACMarvin ColumbinoNo ratings yet

- IMD StationsDocument15 pagesIMD Stationschinna rajaNo ratings yet

- NBA QP FORMAT - Cycle Test 01 - III Yr - EHOSDocument6 pagesNBA QP FORMAT - Cycle Test 01 - III Yr - EHOSskarthikpriyaNo ratings yet

- Peta Okupasi Nasional Dalam Rangka Kualifikasi Nasional Indonesia Pada Area Fungsi Teknologi Informasi Dan Komunikasi Ver.03-301019Document1 pagePeta Okupasi Nasional Dalam Rangka Kualifikasi Nasional Indonesia Pada Area Fungsi Teknologi Informasi Dan Komunikasi Ver.03-301019abufaruqiNo ratings yet

- Assignmwent 3 ENGV 311 2024Document15 pagesAssignmwent 3 ENGV 311 2024phagamisonkog02No ratings yet

- Degree of ComparisonDocument2 pagesDegree of ComparisonDella futvyNo ratings yet

- Bread of SaltDocument2 pagesBread of SaltLadyAnn Petilla BarbosaNo ratings yet

- Weekly Home Learning Plans for English 2Document5 pagesWeekly Home Learning Plans for English 2Racquel Joy HMNo ratings yet

- Linux-Insides Interrupts Linux-Interrupts Part 4Document4 pagesLinux-Insides Interrupts Linux-Interrupts Part 4Avinash PalNo ratings yet

- UML Activity DiagramDocument13 pagesUML Activity DiagramMuqaddas RasheedNo ratings yet

- Final Exam Portfolio for Language Assessment CourseDocument2 pagesFinal Exam Portfolio for Language Assessment CourseFalikh FadilaNo ratings yet

- LNS 2016 1 216Document39 pagesLNS 2016 1 216Fitri KhalisNo ratings yet

- Adobe Flash Player 10.1 Read MeDocument3 pagesAdobe Flash Player 10.1 Read MemickemusicNo ratings yet

- Songs of Ourselves Volume 1 SampleDocument32 pagesSongs of Ourselves Volume 1 SampleMridini SivakumarNo ratings yet

- String Function of PHPDocument36 pagesString Function of PHPvadgamabhavinNo ratings yet

- XQueryDocument123 pagesXQuerygauti viruNo ratings yet

- CSCI Software Engineering 1 Group Assignment 5 Testing DocumentationDocument6 pagesCSCI Software Engineering 1 Group Assignment 5 Testing DocumentationsushanthkuNo ratings yet

- Radiant International School, Patna: Split-Up Syllabus For Session 2019-2020Document4 pagesRadiant International School, Patna: Split-Up Syllabus For Session 2019-2020KelNo ratings yet