Professional Documents

Culture Documents

A Beam-Forming Transmit ASIC For Driving Ultrasonic Arrays: John V. Hat®eld, Kwet Seng Chai

Uploaded by

toloiceOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Beam-Forming Transmit ASIC For Driving Ultrasonic Arrays: John V. Hat®eld, Kwet Seng Chai

Uploaded by

toloiceCopyright:

Available Formats

Sensors and Actuators A 92 (2001) 273279

A beam-forming transmit ASIC for driving ultrasonic arrays

John V. Hateld*, Kwet Seng Chai

Department Electrical Engineering and Electronics, UMIST, P.O. Box 88, Manchester M60 1QD, UK Accepted 19 December 2000

Abstract This paper describes the design of a programmable eight-channel application specic integrated circuit (ASIC) for driving ultrasonic array transducers. The ASIC is capable of generating variable delay lengths of up to 65 ms in steps of 1 ns. Integrated on the same chip is an array of eight high-voltage pulser circuits (up to 100 V). The output pulse width can also be set to match the transducer operating frequency. A minimum width of 20 ns is possible and the rise and fall times are typically 5 and 7 ns. It can also be programmed to give bursts of up to 16 repetitions to facilitate Doppler imaging. # 2001 Elsevier Science B.V. All rights reserved.

Keywords: ASIC; Ultrasonic; Beam-steering; Programmable; Pulser

1. Introduction The use of arrays of ultrasonic transducers is widespread in medical ultrasonic imaging. In general, these are 1D arrays of piezo ceramic composite materials, although PVDF arrays have been reported [1]. By electrically exciting the array elements in a pre-determined order, it is possible to electronically steer a focused beam of ultrasonic energy for imaging purposes [2]. Recent years have seen the emergence of 2D arrays that facilitate 3D ultrasound imaging [3]. Although in the main, these are sparse arrays, the trend is for the number of array elements that have to be driven to continuously increase. The implication is that the wire bundle that connects the transducer array to the control unit becomes ever more unwieldy. A solution to this problem is to mount as much of the control electronics, both transmit and receive as possible at the array itself. This paper describes an eight-channel prototype transmit beam-forming IC that can be mounted directly on the transducer head. 2. Overview of the new IC The transmit electronics play a crucial role in determining the ring sequence of the transducer array and consequently the steering and focusing of the ultrasonic beam. This task requires electronics capable of generating delays of variable

Corresponding author. Tel.: 44-161-200-4724; fax: 44-161-200-8946. E-mail address: j.hatfield@umist.ac.uk (J.V. Hatfield).

*

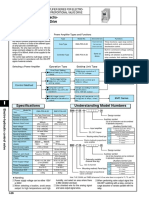

length and producing high-voltage output pulses to excite the ultrasonic transducer. A programmable prototype transmit electronics integrated circuit has, therefore, been designed. The prototype IC has eight independent channels, each of which is programmable with delays of up to 65 ms in steps of 1 ns. Also, integrated on the same chip is an array of eight high-voltage pulsers each capable of 100 V output. The high-voltage output pulse width can be shortened down to 20 ns duration. The HV output can also be congured to produce up to 16 repetitive pulses for Doppler imaging. A block diagram of the complete system is shown in Fig. 1. The coarse timer is a 10 bit synchronous counter. The ne timer is essentially a delay locked loop (DLL) used to subdivide a master clock into 64 multiple-phase clocks. These two blocks are common to eight channels of identical timing circuits. The device is programmed by writing delay values into the rst-in-rst-out (FIFO) buffers (one per course timing channel and one per ne timing channel). Each course timing channel has a digital comparator to compare the programmed time with the running coarse counter. When these values match a signal pulse, one clock cycle wide is triggered at the comparator output. This provides an enabling window for the ne timer. A programmed 64:1 multiplexer (one per channel) then selects the appropriate output from the DLL which is passed through to the high-voltage module. Hence, a resultant output of variable delay lengths can be programmed. The output is shaped before triggering the high-voltage pulser. It can be stretched to match the operating frequency of an ultrasonic transducer. It can also be repeated to generate a tone burst for Doppler imaging.

0924-4247/01/$ see front matter # 2001 Elsevier Science B.V. All rights reserved. PII: S 0 9 2 4 - 4 2 4 7 ( 0 1 ) 0 0 5 8 3 - 0

274

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

Fig. 1. Block diagram of the complete transmit IC.

It is worth noting that the ne timing circuitry may not always be necessary. For centre frequencies less than 5 MHz, it is unlikely that any delays less than 10 ns would be required. In this case, a single coarse counter clocked at 100 MHz would be adequate. However, such a solution does have implications in terms of power consumption. For high frequency, high-resolution arrays, particularly PVDF arrays timing resolutions in the nanosecond region are required. 3. Fine timing block The central component of the ne timing circuitry is a DLL which is used to interpolate between successive periods

of a reference clock [4]. Fig. 2 shows the basic block diagram of the DLL. A reference clock is delayed through a variable delay line until it is synchronised with the next period of the reference clock. A feedback loop constantly adjusts the delay so that the phase difference between the two clocks remains zero. 3.1. Delay elements The variable delay line is made up of a series of 64 delay elements. A single delay element is shown in Fig. 3 and comprises of a current starved inverter and a normal inverter. By limiting the current owing in transistors M1 and M2, the switching speed can be varied. Weak transistors M3 and M4

Fig. 2. Block diagram of delay locked loop.

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

275

and VCTRL-n, hence a 15.625 MHz master clock is required to make the feedback exactly 1 clock cycle behind the reference. 3.2. Phase detection There are potential problems in maintaining the integrity of a pulse passing along a delay line [5]. The rise and fall times created may not be equal due to the intrinsic differences between p- and n-transistors. In extreme cases, the pulse in the delay chain may simply ``disappear''. To make the design robust to process, temperature and supply variations, both the p- and n-type current-sources of Fig. 3 are provided with separate control voltage (VCTRL-n and VCTRLp). A pre-charge circuit is used for this [6]. It works by producing a pulse of duration equal to the phase difference between the two misaligned clock signals. The pulse can be used to drive a charge pump circuit to produce the control voltage. Two complimentary pre-charge circuits are needed to detect the phase difference at both edges. Fig. 4 illustrates a positive edge detector. A low at IN1 turns on transistor M1, switches off transistor M3 and precharges node X to logic 1. Transistor M6 is switched on but there is no dc path to ground since transistor M5 is off. As transistor M4 is also off, node Y may fall into unpredictable state. However, the presence of the ``weak'' transistor M7 pulls node Y towards VDD. Hence the output remains at logic 0. Signal IN1 switching high before IN2 will switch on transistor M5 to momentarily complete a dc path to ground. Node Y will be pulled towards ground and the output becomes logic 1. When IN2 catches up with IN1, node X is quickly dropped to ground when both transistors M2 and M3 are turned on. This immediately turns on transistor M4, pulling node Y back to VDD and hence, the output falls

Fig. 3. Current starved inverter delay element.

have their gates permanently tied to ground and VDD, respectively. They ensure that the delay element will still operate, by providing a minimum current, even if transistors M5 and M6 are completely switched off. Transistor M5 is a current source, controlled by a voltage VCTRL-p, which supplies current to transistor M1 hence varying the rise time of the output. Similarly, the control voltage VCTRL-n varies the current owing into transistor M6, hence adjusting the fall time of the output. The output inverter is an ordinary inverter sized to drive an identical load down the delay chain. The output from the last delay element is the loop feedback which is compared with the reference. Each delay interval is adjusted to be 1 ns apart by controlling VCTRL-p

Fig. 4. The positive edge detector circuit.

276

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

Fig. 5. The negative edge detector circuit.

towards ground. The same explanation can be extended to the negative phase detector of Fig. 5. 3.3. Charge pump The dc control voltages (VCTRL-n and VCTRL-p) are stored on capacitors. There values are established, and constantly refreshed by charge pumps. The easiest way to implement such a circuit is to allow active pulses from the phase detectors to turn on and off a switch so that current pulses can charge or discharge the voltage on the capacitor. The schematic is shown in Fig. 6. Two positive phase detectors (Fig. 4) can be connected as shown in Fig. 6 to produce two regulating signals denoted UP and DOWN. These pulsating signals can control the voltage level VCTRL-n on the capacitor C by a charge pump

circuit made up of transistors M1, M2 and two identical current sources IPUMP. When CLKFB is trailing CLKREF, the UP signal pulsates and periodically closes the switch M1 to allow IPUMP to supply charge to the capacitor C. This causes VCTRL-n to rise. Conversely, when CLKFB is leading CLKREF, the DOWN signal pulsates and switches on M2 to discharge the capacitor C through the second IPUMP. This causes VCTRL-n to fall. Similarly two negative phase detector can be connected in the same manner to form a charge pump to produce VCTRL-p. It can then be used to control the gate voltage of the p-type current source of the delay element. 3.4. Generating trigger pulse The concept of generating the trigger is now discussed. Assume that the circuit allows a predetermined coarse time

Fig. 6. The charge pump circuit.

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

277

(stored in a FIFO latch) to be compared with the running 10bit counter. When both values match, say at count N, a low signal one clock cycle wide is triggered at the comparator output. This signal is used as an enabling window to lter the ne clock. Suppose the ne time was pre-selected at `m' nanoseconds, that is the mth clock from the DLL, using a 64:1 multiplexer. It would appear that it is only necessary to logical `OR', the lter window with the mth clock to generate the nal delay (in this case, we are looking for active low pulses). However, in the event that m is chosen to be more than half the clock period, a simple logical OR of the mth clock and the comparator output will generally produce a double pulse. This is because the actual pulse to be ltered has rippled along the delay chain, partially past the lter window. What is generated at the output consists of part of the actual pulse and part of the unwanted previous pulse. To prevent this happening extra logic has to be provided to delay the lter window by half a clock cycle in these cases. 4. Pulse control block The pulse control block allows for the programmability of the chip's output. It is possible to vary the width of the output pulse to match the transducer's operating frequency. This is achieved by controlling the charging current to a capacitor in a one-shot (monostable) circuit. The charging current is controlled by means of a programmable current-source. The time constant of the one-shot circuit is then determined solely by the ratio of its capacitor value (in this case 1 pF) to the controlled current and is, therefore, linear. The current source is programmed by means of an on-chip, 8-bit DAC. The minimum programmable pulse width is 20 ns. It is also useful to be able to generate a multiple-pulse output which, in conjunction with appropriate ltering, can be used for Doppler imaging. The programmable circuit which performs this operation is shown in Fig. 7. Here three

Fig. 8. Waveforms that illustrate the programming of three output pulses.

one-shot circuits form a closed loop, which can be broken by a 4-bit counter (therefore, maximum of 16 pulses). Without the counter, the loop can go into innite oscillation once triggered. The purpose of this counter is to count the number of output pulses and send an inhibit signal to terminate the oscillation. An example which produces three output pulses is shown in Fig. 8. Upon reset, the counter settles to zero. The falling edge of an external trigger activates the one-shot, which in turn, triggers the second and third one-shots in the feedback loop. The output from the third one-shot causes the rst oneshot to trigger again. By this time the counter has been clocked once, which increments its output count by one. The ring continues until the counter registers a three at its output which breaks the feedback loop by asserting a permanent low to the NAND gate. Finally, these pulses can be used to trigger the high-voltage pulser at the next stage. 5. High-voltage output stage This chip integrates the high-voltage pulsing circuits along with the 5 V CMOS digital circuits. The technology is provided by the Alcatel Mietec Intelligent Interface Technology (I2T) which permits the co-integration of CMOS, bipolars (BiCMOS) and DMOS technologies. The

Fig. 7. Block diagram of the programmable pulse count generator.

278

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

Fig. 10. Schematic of the BiCMOS pulser drive circuit.

Fig. 9. High-voltage pulser circuit.

pulser, shown in Fig. 9 is congured as a source-follower. Co-integrated DMOS transistors are used as they can sustain the 100 V needed to drive the array elements. The output must remain at ground during the idle state for safety reasons. The output pushpull transistors are sized (RDSon < 20 O) to drive a maximum load of 200 O/20 pF. Two large protection diodes are added at the output to withstand any high-voltage surge [7]. Two complementary signals, Vx and Vy, are required to drive the pulser. Vx is normally high while Vy is normally low. A transition of Vy to VDD (5 V) causes the gate of HV3 to surge towards ground. The amount of voltage displacement is determined by the ratio of transistor HV1 to transistor HV2. Hence they can be sized to give maximum gate-source voltage allowed by the process design rule, that is Vgs less than 12 V. The effect is that transistor HV3 switches on and raises its output towards HVVDD. Transistor HV5 is a source-follower so that the output, Vout, follows suit. At the same moment, Vx is low, turning off both transistors HV4 and HV6. When Vx and Vy switches back to high and low, respectively, the output falls to ground. The weak diode WD1 has the effect of pulling the gate of transistor HV3 to HVVDD, thus, turning it completely off to minimise idle power consumption. The complementary driving signals Vx and Vy, are generated by the BiCMOS driving circuit of Fig. 10 whose input, Vin, is provided by the pulse control block. It is very convenient to use the BiCMOS technology available as part of the I2T for this purpose. The transistors HV2, HV4 and HV6 (Fig. 9) are fairly large and demand generous amounts of current to charge their capacitive gates if they are to turn on quickly. Bipolar transistors are used to do just that. A full swing output (05 V) is also important to provide maximum drive and bipolars alone will not achieve this, hence the attraction of a BiCMOS solution. Referring to Fig. 10, transistor M1 drives the base of transistor Q1. The two output BJTs, Q1 and Q2, provide

speed and driving capability. Transistor M4, when turned on, allows a low resistance path to discharge the output (Vx) towards ground. Transistors M2 and M5 provide a discharge path to the base of Q1 and Q2. A problem usually associated with BJTs is the loss of one diode drop (VBE) at the output when the transistors are turned on. Transistors M3 and M5 act as active shunt resistors to pulls the output to VDD and GND, hence a full-swing output can be achieved. The common drain of transistors M6 and M7 serves as a feedback path to switch transistors M3 and M5. This path also provides a complementary output (Vy). The source of M3 can be connected directly to the supply instead to the base of Q1 (reference) which has the benet of sourcing extra current to the output (Vx). The operation is as follows. A logic low at the input causes transistor M1 to turn on, which in turn, provides a base current to switch transistor Q1 on. These actions pull the output Vx towards VDD. The feedback, senses Vx rising toward the supply, will immediately go low at its output. This causes M3 to turn on and provide a resistive path to pull the output Vx to VDD. When the input changes to logic high, transistor M1 goes off and transistors M2 and M4 turn on. BJT Q1 goes off since its base is now tied to ground through transistor M2. Transistor M3, which is still momentarily on, pulls the base of Q2 towards the supply through transistor M4. Transistor Q2, temporarily turned on and quickly discharges the output Vx towards ground. This is sensed by the feedback network and causes Vy to go high, which in turn, switches on transistor M5. Now transistor Q2 stops working, the output Vx is returned to ground through transistors M4 and M5. 6. Floorplanning for the ASIC The oorplanning and layout as shown in the photomicrograph of Fig. 11, was performed using the Cadence Block Ensemble and Cell Ensemble. The 5 V digital circuits occupy the top half of the silicon. Eight identical timing

J.V. Hatfield, K.S. Chai / Sensors and Actuators A 92 (2001) 273279

279

high-voltage pulser circuits (up to 100 V). The output pulse width can be squeezed down to 20 ns and it can also be programmed to give up to a 16 repetitive pulse burst. References

[1] J.V. Hatfield, N.R. Scales, A.D. Armitage, P.J. Hicks, Q.X. Chen, P.A. Payne, An integrated multi-element array transducer for ultrasound imaging, Sens. Actuators A 41 (13) (1994) 167173. [2] O.T. Von Ramm, S.W. Smith, Beam steering with linear arrays, IEEE Trans. Biomed. Eng. (BME) 30 (8) (1983) 438452. [3] T.R. Nelson, D.H. Pretorius, Three-dimensional ultrasound imaging, Ultrasound Med. Biol. 24 (9) (1998) 12431270. [4] A. Rothermel, F. Dell'ova, Analogue phase measuring circuit for digital CMOS ICs, IEEE J. Solid State Circuits. 28 (7) (1993) 853 856. [5] N.R. Scales, P.J. Hicks, A.D. Armitage, P.A. Payne, Q.X. Chen, J.V. Hatfield, A programmable multi-channel CMOS pulser chip to drive ultrasonic array transducers, IEEE J. Solid State Circuits 29 (8) (1994) 992994. [6] H. Notani, H. Kondon, Y. Matsuda, A 622 MHz CMOS phase-locked loop with precharge type phase frequency detector, in: Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, USA, 1418 June 1994, pp. 129130. [7] G. Thomas, G. Troussel, F. Vialettes, High-voltage technology offers new solutions for interface integrated circuits, IEEE. Trans. Electron. Devices 33 (1986) 20162024.

Fig. 11. Photomicrograph of fabricated chip (approximately 6:5 mm 6:5 mm).

channels occupy the rst row of the chip. The second row has a shielded (from digital switching) analogue current source. It has a separate pair of supply and ground rails to minimise noise pick-up. The DLL is in the middle as equal distribution of parasitic capacitance is important. The 10 bit counter sits on the far right. The BiCMOS drivers occupy the third row and there is a guard ring to trap switching noise. Finally, the pulsers lay along the bottom of the chip. There is also a guarding shield surrounding them to trap unwanted surges in the substrate. The high-voltage IO peripherals (metal pads) take up the bottom side of the chip while the 5 V IO peripherals occupy the rest of the perimeter of the chip. The total die size, including the IO peripherals is about 6:5 mm 6:5 mm. Each pulser takes up about 2 mm 0:5 mm of space. The chip is mounted in a 84-pin JLCC package. 7. Conclusion A new eight-channel prototype transmit electronics ASIC for ultrasonic imaging systems has been designed. The IC is capable of generating variable delay length up to 65 ms in steps of 1 ns. Integrated on the same chip is an array of eight

Biographies

John V. Hatfield received the BSc degree in physics from the University of Leeds, Leeds, UK, in 1973 and the MSc degree from the University of Manchester, Institute of Science and Technology (UMIST), Manchester, UK, in 1984. He received the PhD degree from the same university in 1988 for his researches into position-sensitive particle detectors. Currently, he is a reader in the Department of Electrical Engineering and Electronics at UMIST. His research interests are in the field of integrated sensors and transducers and he has published more than 70 papers in this area. Kwet Seng Chai was awarded the BE degree in electronic engineering by the University of Manchester Institute of Science and Technology in 1995. He was awarded an MPhil degree in the following year for a current-mode analogue IC design project on a charged particle detecting integrated circuit. He was then employed as a research assistant working on an EU funded project for the development of 2D ultrasonic arrays. He was awarded the PhD for this work, by UMIST, in the year 2000. Currently, he is employed as an IC design engineer by Analog Devices in the UK.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Ultra-Low Power Phase-Locked LoopDocument4 pagesUltra-Low Power Phase-Locked Loophawking1122No ratings yet

- 11 Chapter03 PDFDocument13 pages11 Chapter03 PDFAtulNo ratings yet

- 60W Flyback TIDocument16 pages60W Flyback TIe_magazin3821No ratings yet

- Switching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Document17 pagesSwitching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Burlacu AndreiNo ratings yet

- An Improved Single Phase Full Bridge Inverter Using Sequential Triggering For Achieving Zero Voltage Without InductorDocument9 pagesAn Improved Single Phase Full Bridge Inverter Using Sequential Triggering For Achieving Zero Voltage Without InductorAl MtdrsNo ratings yet

- Interpretation Spectre SCDocument13 pagesInterpretation Spectre SCFrederic DelmarcheNo ratings yet

- High Voltage Power Supply For Electro-Optics Applications: IJRRAS 3Document5 pagesHigh Voltage Power Supply For Electro-Optics Applications: IJRRAS 3mishithNo ratings yet

- Low Cost' Three Phase To Single Phase Matrix ConverterDocument6 pagesLow Cost' Three Phase To Single Phase Matrix ConverterRaghu RamNo ratings yet

- Astable CircuitsDocument9 pagesAstable CircuitsRavindranath ShrivastavaNo ratings yet

- Qs & As Class I+IIDocument9 pagesQs & As Class I+IIphyoNo ratings yet

- Electronic Instrument atDocument8 pagesElectronic Instrument atkushalchandel0% (1)

- D Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various ProtectionsDocument6 pagesD Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various Protectionsঅর্ণব কোলেNo ratings yet

- UC3845 Technical ExplanationDocument15 pagesUC3845 Technical ExplanationankurmalviyaNo ratings yet

- Pulse Oximetry CircuitDocument19 pagesPulse Oximetry Circuitنواف الجهنيNo ratings yet

- Lic Reports FinalDocument11 pagesLic Reports FinalE L Sai BalajiNo ratings yet

- Digitally Controlled Oscillator ReportDocument18 pagesDigitally Controlled Oscillator ReportVinidhra ShivakumarNo ratings yet

- Research Article: A Four Quadrature Signals' Generator With Precise Phase AdjustmentDocument7 pagesResearch Article: A Four Quadrature Signals' Generator With Precise Phase Adjustmentaamir.nedian4139No ratings yet

- A Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterDocument4 pagesA Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterEldhose VargheseNo ratings yet

- U-93 Application NOTE A New Integrated Circuit For Current Mode ControlDocument9 pagesU-93 Application NOTE A New Integrated Circuit For Current Mode ControlpramodNo ratings yet

- A Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam HeydariDocument4 pagesA Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam Heydarirah0987No ratings yet

- Ultrasonic Distance MeterDocument5 pagesUltrasonic Distance MeterMahesh Jadhav100% (2)

- Ultrasonic Distance MeterDocument11 pagesUltrasonic Distance MeterHafiz Murtaza100% (3)

- Electrical - Ijeeer - Wavelet Modulated Z-SourceDocument10 pagesElectrical - Ijeeer - Wavelet Modulated Z-SourceTJPRC PublicationsNo ratings yet

- Modeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorDocument6 pagesModeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorLelosPinelos123No ratings yet

- (IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MDocument4 pages(IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MInternational Journal of Engineering and TechniquesNo ratings yet

- Current Controlled OscillatorDocument4 pagesCurrent Controlled OscillatorajaynkotiNo ratings yet

- Types Pyts & Pytc Switched Distance RelaysDocument14 pagesTypes Pyts & Pytc Switched Distance Relayssgshekar30100% (1)

- Slua 143Document15 pagesSlua 143Tonia KataNo ratings yet

- Aplicacion Uc3842Document15 pagesAplicacion Uc3842Gian Mejia100% (1)

- AppNote03 Uc3842Document14 pagesAppNote03 Uc3842Heriberto Flores AmpieNo ratings yet

- Zero Flux CTDocument2 pagesZero Flux CTsajedarefinNo ratings yet

- Ultrasonic TransducerDocument5 pagesUltrasonic TransducerRishabhKarn100% (3)

- Ec 4112: Analog Communication Laboratory List of Experiments: Compulsory ExperimentsDocument68 pagesEc 4112: Analog Communication Laboratory List of Experiments: Compulsory ExperimentsArchit SrivastavaNo ratings yet

- H09344448 PDFDocument5 pagesH09344448 PDFslimabidNo ratings yet

- Powe Efficient PLLDocument12 pagesPowe Efficient PLLjayalakshmisnairNo ratings yet

- Crystal Oscillator Time BaseDocument4 pagesCrystal Oscillator Time BaseOliverQueen773sNo ratings yet

- 555 Timer As Mono Stable Multi VibratorDocument8 pages555 Timer As Mono Stable Multi VibratorchrisgeclayNo ratings yet

- 00225647Document5 pages00225647thavaselvanNo ratings yet

- EC2307-New Digital Communication Lab Manual Odd 2011Document53 pagesEC2307-New Digital Communication Lab Manual Odd 2011chenthiltrNo ratings yet

- Pim Control Method of Multiple Inverters: MaclevDocument6 pagesPim Control Method of Multiple Inverters: Maclevalpe_huandvNo ratings yet

- I, and I, and Zref Separately We Measured Changes of AboutDocument5 pagesI, and I, and Zref Separately We Measured Changes of AboutBodhayan PrasadNo ratings yet

- Electronic & Telecommunication Engineering: Department ofDocument30 pagesElectronic & Telecommunication Engineering: Department ofANIRUDDHA PAULNo ratings yet

- Uc3842 Provides Low-Cost Current-Mode Control: Application NoteDocument16 pagesUc3842 Provides Low-Cost Current-Mode Control: Application NoteLeonardo Ortiz100% (1)

- A Norton Model of A Distribution Network For Harmonic EvaluationDocument7 pagesA Norton Model of A Distribution Network For Harmonic Evaluationbubo28No ratings yet

- MS Project ReportDocument11 pagesMS Project ReportArnab Jyoti BaruahNo ratings yet

- V An Innovative Magnetic Field Sweep Unit: of of of ofDocument20 pagesV An Innovative Magnetic Field Sweep Unit: of of of ofBerthaFloresNo ratings yet

- 2 Ask, PSK, FSKDocument15 pages2 Ask, PSK, FSKI AM A PROGRAMMERNo ratings yet

- Bhwna Unit 5Document9 pagesBhwna Unit 5Pradeep KumarNo ratings yet

- Design of A Under Voltage Lock Out Circuit With Bandgap StructureDocument4 pagesDesign of A Under Voltage Lock Out Circuit With Bandgap Structured_niku100% (1)

- Design A Clap SwitchDocument15 pagesDesign A Clap Switchbalvendra03No ratings yet

- Abstract: Ultra-Low Power Phase Locked LoopsDocument4 pagesAbstract: Ultra-Low Power Phase Locked LoopsRizwan Shaik PeerlaNo ratings yet

- Implementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerDocument6 pagesImplementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerAlonso CoradoNo ratings yet

- A Novel Spread-Spectrum Clock Generator For Suppressing Conducted EMI in Switching Power SupplyDocument6 pagesA Novel Spread-Spectrum Clock Generator For Suppressing Conducted EMI in Switching Power Supplyyanuar1976No ratings yet

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocument12 pagesDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNo ratings yet

- Rogowski Coil Transient Performance and Atp Simulation For Aplications in Protective RelaysDocument6 pagesRogowski Coil Transient Performance and Atp Simulation For Aplications in Protective RelaysJose Alberto RodriguezNo ratings yet

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsFrom EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Corripio, Armando B.-Tuning of Industrial Control Systems-IsA (2001)Document253 pagesCorripio, Armando B.-Tuning of Industrial Control Systems-IsA (2001)wa_moreira100% (1)

- LinearFeedbackShiftRegister PDFDocument1 pageLinearFeedbackShiftRegister PDFSai KiranNo ratings yet

- S7300DS - GS - e SIMATIC S7 Distributed Safety PDFDocument42 pagesS7300DS - GS - e SIMATIC S7 Distributed Safety PDFknightfelix12No ratings yet

- Introduction To The Fundamentals of Control System ECEDocument68 pagesIntroduction To The Fundamentals of Control System ECEEdward FernandezNo ratings yet

- Barriers of Communication: Wrong Choice of MediumDocument11 pagesBarriers of Communication: Wrong Choice of MediumArnavNo ratings yet

- Massive Manual EnglishDocument115 pagesMassive Manual Englishscaricone71No ratings yet

- 1.full Portion SM PDFDocument109 pages1.full Portion SM PDFAditya GoleNo ratings yet

- UHU Servo Controller 300 enDocument13 pagesUHU Servo Controller 300 enZoltán NémetNo ratings yet

- Oscillators Simplified - Delton T HornDocument258 pagesOscillators Simplified - Delton T HornrobertlivingstoneNo ratings yet

- 09-Wien Bridge Oscillator Using OpAmp PDFDocument4 pages09-Wien Bridge Oscillator Using OpAmp PDFVishesh Kumar SinghNo ratings yet

- Tu 05Document23 pagesTu 05Yang ElvisQUNo ratings yet

- SST Owner's Guide Rev 2Document14 pagesSST Owner's Guide Rev 2wolfen667No ratings yet

- 6.design A Wien Bridge Oscillator Using OpDocument5 pages6.design A Wien Bridge Oscillator Using OpSudeep NayakNo ratings yet

- New Air Servo System XT777 ChileDocument32 pagesNew Air Servo System XT777 Chilepaputo27No ratings yet

- The Vehicle Steer by Wire Control System by Implementing PID ControllerDocument5 pagesThe Vehicle Steer by Wire Control System by Implementing PID ControllerdashNo ratings yet

- BRH 4WRE (E) - Re29061 - 2005-10Document20 pagesBRH 4WRE (E) - Re29061 - 2005-10Moutaz IsmailNo ratings yet

- 10862028-Man 01 Final, User Manual PDFDocument517 pages10862028-Man 01 Final, User Manual PDFesteban monterrosa lopez100% (1)

- H1000e I Ema-Emc PDFDocument4 pagesH1000e I Ema-Emc PDFNguyen Van ChungNo ratings yet

- Replika XT Manual EnglishDocument48 pagesReplika XT Manual EnglishpampaboyNo ratings yet

- Load Positioning and Minimization of Load Oscillations in Rotary CranesDocument13 pagesLoad Positioning and Minimization of Load Oscillations in Rotary CranesAnonymous LFgO4WbIDNo ratings yet

- GoldSim Volume1Document427 pagesGoldSim Volume1juba1200No ratings yet

- QP Job Log 222674Document65 pagesQP Job Log 222674LUISA FERNANDA JIMENEZ BELTRANNo ratings yet

- HVDC PowerDocument70 pagesHVDC PowerHibba HareemNo ratings yet

- Char-Lynn Product Guide.58220426 - OrbitrolDocument40 pagesChar-Lynn Product Guide.58220426 - OrbitrolorlandolanchipaNo ratings yet

- INDRAMAT Manuals 2065 PDFDocument346 pagesINDRAMAT Manuals 2065 PDFHoracio BritezNo ratings yet

- Ecodrive Drive Controller DKC02.1: RexrothDocument60 pagesEcodrive Drive Controller DKC02.1: RexrothWilliam PachecoNo ratings yet

- Control SystemDocument15 pagesControl SystemRaktim Kumar SinghNo ratings yet

- Technical Data: VAV Universal ActuatorsDocument8 pagesTechnical Data: VAV Universal ActuatorsCTHNo ratings yet

- Control System Question BankDocument23 pagesControl System Question Bankdr mbaluNo ratings yet

- Operations Manual: HFG2.0 Gas Fuel Metering ValveDocument38 pagesOperations Manual: HFG2.0 Gas Fuel Metering ValveAurisNo ratings yet