Professional Documents

Culture Documents

Solutions

Uploaded by

jabir_ibmOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Solutions

Uploaded by

jabir_ibmCopyright:

Available Formats

Introduction to

Linear Circuit Analysis

and Modelling

From DC to RF

Solutions Manual

Luis Moura

Izzat Darwazeh

Contents

1 Elementary electrical circuit analysis 3

2 Complex numbers: An introduction 35

3 Frequency domain electrical signal and circuit analysis 37

4 Natural and forced responses circuit analysis 60

5 Electrical two-port network analysis 78

6 Basic electronic amplier building blocks 119

7 RF circuit analysis techniques 141

8 Noise in electronic circuits 175

2

Chapter 1

Elementary electrical circuit analysis

Solution of problem 1.1

The current owing through the capacitor is given by:

i(t) = C

d v(t)

dt

= 10

6

2 1000 cos(2 100 t +/4) A

= 6.3 cos(2 100 t +/4) mA

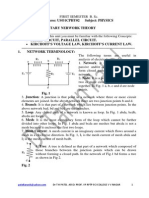

Figure 1.1 shows the waveforms for the voltage across and the current through the capacitor.

i(t)

(V)

v(t)

(mA)

5

10

5 10

15 20

t (ms)

10

5

5

10

0

0

5

10

Voltage

Current

Figure 1.1: Waveforms for the voltage across and the current through the capacitor.

1. Elementary electrical circuit analysis 4

Solution of problem 1.2

The voltage across the terminals of the inductor is given by:

v(t) = L

d i(t)

dt

= 3 10

3

2 5000 20 10

3

sin(2 5000 t) V

= 1.9 sin(2 5000 t) V

Figure 1.2 shows the waveforms for the voltage across and the current through the inductor.

i(t)

(mA)

t (ms)

10

0

0

1

2

v(t)

(V)

0.5

20

10

20

1

2

Voltage

Current

Figure 1.2: Waveforms for the voltage across and the current through the inductor.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 5

Solution of problem 1.3

The calculations of the voltages across and the currents through each circuit elements are effected

applying the Nodal analysis. This method can be outlined as follows:

1. First, we indicate the voltages at each node. These voltages indicate the potential difference

between the node being considered and a reference node which can be chosen arbitrarily. This

node is traditionally called node zero (0) or the ground terminal and is often chosen as the

node with the highest number of attached electrical elements. This is illustrated in gure 1.3 a)

+ +

V

A

V

B

R

1

+ +

V

A V

B

(V

A

)

(V

B

)

0

+

+ +

(V

A

)

(V

B

)

V

A

V

B

0

a)

0

d)

c)

b)

V

A

(V

B

)

R

1

I

R1

I

R1

=

V

A

V

B

R

1

R

1

V

R1

= V

A

V

B

V

A

V

B

V

R1

= V

A

V

B

V

R1

= V

A

+ (V

B

)

Figure 1.3: Application of the Nodal analysis method. a) Indication of the voltage is the nodes A

and B b) Indication of the current I

R

1

c) I

R

1

= (V

A

V

B

)/R. d) Adding vectors.

2. Then, we consider, in an arbitrary manner, the current direction in each branch, as indicated

in gure 1.3 b).

3. The current that ows through each resistance can be expressed, according to Ohms law, as

the ratio of the voltage across that resistance and the resistance value;

I

R

1

=

V

A

V

B

R

1

(1.1)

Note that the similarity between the way we express the voltage across the resistance, as

V

A

V

B

, and the calculation of the sum (or subtraction) of vectors shown in gure 1.3 d).

4. Finally, we apply the current voltage law to each node

1

We apply now the Nodal analysis method to solve the circuits of the problem 1.3 where the voltages

at each node and the directions of the currents have been chosen as indicated in gure 1.4.

1

As its name suggests the Nodal analysis method is based on the application of the current voltage law to each node of

the circuit. However, the calculation of some circuits may require the application of the voltage law.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 6

+

R

1

V

1

R

3

R

2

0

I

R3

I

R1

I

R2

V

A

V

B

+

+

R

1

R

2

R

3

V

1

V

2

R

4

V

A

V

B V

C

V

D

0

I

R1

I

R2

I

R3

I

R4

R

1

I

1

I

2

V

A

0

I

R1

+

V

1

+

V

2

R

2

V

A

V

B

V

C I

R2

0

R

1

I

R1

+

R

2

V

1

R

4

R

1

R

3

V

A

V

B

V

C

0

I

R1

I

R2

I

R3

I

R4

+

R

2

R

4

V

1

R

3

0

V

A

V

B

V

C

R

1

I

R1

I

R3

I

R2

I

R4

I

1

f)

e)

d)

a)

c)

b)

Figure 1.4: Circuits of problem 1.3.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 7

Circuit a): Applying the current law we can write:

I

R

1

= I

1

+I

2

= 0.7 A

The voltage across R

1

is V

A

which is obtained applying Ohms law:

V

A

= I

R

1

R

1

= 70 V

Circuit b): For this circuit we can write the following set of eqns:

_

_

I

R

1

= I

R

2

V

A

V

C

= V

1

V

B

= V

2

(1.2)

which can be rewritten as follows:

_

_

V

B

V

A

R

1

=

V

C

R

2

V

A

V

C

= V

1

V

B

= V

2

(1.3)

Solving this set of eqns in order to obtain V

A

, V

B

and V

C

we can write:

V

A

=

R

2

V

2

+R

1

V

1

R

1

+R

2

= 2.63 V

V

B

= V

2

= 3 V

V

C

= R

2

V

2

V

1

R

1

+R

2

= 0.63 V

The current I

R

1

is equal to I

R

2

= 3.7 mA.

Circuit c): For this circuit we can write

_

_

I

R

1

=

V

A

R

1

V

A

= V

1

I

R

2

= I

R

3

(1.4)

that is,

_

_

I

R

1

=

V

1

R

1

V

1

V

B

R

2

=

V

B

R

3

(1.5)

Solving to obtain V

B

we get

V

B

= V

1

R

3

R

2

+R

3

= 1.1 V

The voltage across R

2

is V

A

V

B

= 0.9 V. The currents through the resistances are:

I

R

1

= 4 mA

I

R

2

= I

R

3

= 7.5 mA

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 8

Circuit d): For this circuit we write the following set of eqns:

_

_

I

R

1

+I

R

2

+I

R

3

= 0

I

R

4

= I

R

3

V

B

V

A

= V

1

V

B

V

C

= V

2

(1.6)

This set of eqns can be written as:

_

_

V

A

R

1

+

V

B

R

2

+

V

D

R

3

= 0

V

C

V

D

R

4

=

V

D

R

3

V

B

V

A

= V

1

V

B

V

C

= V

2

(1.7)

Solving to obtain V

A

, V

B

, V

C

and V

D

we get:

V

A

= R

1

R

2

V

2

V

1

(R

2

+R

3

+R

4

)

R

2

(R

1

+R

3

+R

4

) +R

1

(R

3

+R

4

)

= 29.3 mV

V

B

= R

2

R

1

V

2

+V

1

(R

3

+R

4

)

R

2

(R

1

+R

3

+R

4

) +R

1

(R

3

+R

4

)

= 1.97 V

V

C

=

V

1

R

2

(R

3

+R

4

) V

2

(R

2

R

3

+R

2

R

4

+R

1

+R

3

+R

1

R

4

)

R

2

(R

1

R

3

+R

4

) +R

1

(R

3

+R

4

)

= 1.03 V

V

D

= R

3

(R

1

+R

2

)V

2

R

2

V

1

R

2

(R

1

+R

3

+R

4

) +R

1

(R

3

+R

4

)

= 0.46 V

Circuit e): For this circuit we write

_

_

_

I

R

4

= I

R

1

+I

R

3

I

R

2

= I

R

3

V

A

= V

1

(1.8)

or

_

_

V

C

R

4

=

V

1

V

C

R

1

+

V

B

V

C

R

3

V

1

V

B

R

2

=

V

B

V

C

R

3

(1.9)

Solving to obtain V

B

and V

C

:

V

B

= V

1

R

1

R

3

+R

4

(R

1

+R

2

+R

3

)

R

1

(R

2

+R

3

+R

4

) +R

4

(R

2

+R

3

)

= 1.8 V

V

C

= V

1

R

4

(R

1

+R

2

+R

3

)

R

1

(R

2

+R

3

+R

4

) +R

4

(R

2

+R

3

)

= 1.33 V

Circuit f): For this circuit we write the following set of eqns:

_

_

_

I

1

= I

R

1

+I

R

3

I

1

= I

R

2

+I

R

4

V

1

= V

A

V

C

(1.10)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 9

that is

_

_

I

1

=

V

B

V

A

R

1

+

V

B

V

C

R

3

I

1

=

V

A

R

2

+

V

C

R

4

V

1

= V

A

V

C

(1.11)

Solving to obtain V

A

, V

B

and V

C

we get

V

A

= R

2

V

1

+R

4

I

1

R

2

+R

4

= 8.75 V

V

B

= V

1

R

2

R

3

R

1

R

4

(R

2

+R

4

)(R

1

+R

3

)

+I

1

_

R

1

R

3

R

1

+R

3

+

R

2

R

4

R

2

+R

4

_

= 14.46 V

V

C

= R

4

R

2

I

1

V

1

R

2

+R

4

= 6.75 V

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 10

Solution of problem 1.4

We consider N resistances connected in series and driven by a DC voltage source V as shown in

gure 1.5. For this circuit we can write:

+

V

+ + +

V

R2

V

RN

R

2

R

N R

1

V

R1

I

Figure 1.5: N resistances connected in series.

V = V

R

1

+V

R

2

+. . . +V

R

N

= I (R

1

+R

2

+. . . +R

N

)

= I R

eq

that is

R

eq

= R

1

+R

2

+. . . +R

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 11

Solution of problem 1.5

We consider N resistances connected in parallel and driven by a DC voltage source V as shown in

gure 1.6. For this circuit we can write:

+

V

I

I

R2

I

R1

R

1

(G

1

)

R

2

(G

N

) (G

2

)

R

N

I

RN

Figure 1.6: N resistances connected in parallel.

I = I

R

1

+I

R

2

+. . . +I

R

N

= V (G

1

+G

2

+. . . +G

N

)

= V G

eq

that is

G

eq

= G

1

+G

2

+. . . +G

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 12

Solution of problem 1.6

Circuit a): The equivalent resistance between points A and B is given by the parallel combi-

nation of the three resistance, that is:

R

eq

= (R

1

[[R

2

)[[R

3

Let R

1,2

be the resistance resulting from the parallel combination of R

1

and R

2

;

R

1,2

=

R

1

R

2

R

1

+R

2

= 22.2

R

eq

can be calculated as follows:

R

eq

=

R

1,2

R

3

R

1,2

+R

3

= 16.2

The equivalent conductance is G

eq

= R

1

eq

= 61.7 mS.

Circuit b): Since the three resistances are connected in series we can write

R

eq

= R

1

+R

2

+R

3

= 210

The equivalent conductance is G

eq

= R

1

eq

= 4.8 mS

Circuit c): The resistance R

1

is connected in series with R

2

;

R

1,2

= R

1

+R

2

= 400

R

1,2

is connected in parallel with R

3

:

R

1,2,3

=

R

1,2

R

3

R

1,2

+R

3

= 114.3

R

1,2,3

is connected in series with R

4

, that is

R

eq

= R

1,2,3

+R

4

= 384.3

The equivalent conductance is G

eq

= R

1

eq

= 2.6 mS.

Circuit d): The resistance R

1

is connected in series with R

2

and R

3

is connected in series with

R

4

;

R

1,2

= R

1

+R

2

= 150

R

3,4

= R

3

+R

4

= 150

The equivalent resistance results from the parallel combination of R

1,2

with R

5

and with R

3,4

R

eq

= R

1,2

[[R

5

[[R

3,4

= 42.9

The equivalent conductance is G

eq

= R

1

eq

= 23.3 mS.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 13

+

R

3

R

5

R

2

R

4

0

I

R2

I

R5

I

R4

I

R3

V

Z

V

Y

I

R1

R

1

I

t

V

t

V

X

A

B

Figure 1.7: Circuit of problem 2 e).

Circuit e) For this circuit we cannot identify any combination of resistances which share the

same voltage across their terminals or share the same current. This means that there are no

parallel nor series connections. In order to determine the equivalent resistance we have to

apply a test voltage source V

t

to the circuit between points A and B as shown in gure 1.7.

This source supplies a current I

t

to the circuit. By evaluating V

t

/I

t

we calculate the equivalent

resistance:

R

eq

=

V

t

I

t

(1.12)

We apply the Nodal analysis method to evaluate V

t

/I

t

. For the circuit of gure 1.7 we can

write

_

_

I

t

= I

R

1

+I

R

4

I

t

= I

R

5

+I

R

3

I

R

1

= I

R

5

+I

R

2

V

X

= V

t

(1.13)

that is,

_

_

I

t

=

V

t

V

Y

R

1

+

V

t

V

Z

R

4

I

t

=

V

Y

R

5

+

V

Z

R

3

V

t

V

Y

R

1

=

V

Y

R

5

+

V

Y

V

Z

R

2

(1.14)

Solving in order to obtain V

t

we obtain:

V

t

= I

t

R

5

R

3

(R

1

+R

2

+R

4

) +R

1

R

4

(R

2

+R

3

+R

5

) +R

2

(R

4

R

5

+R

1

R

3

)

R

2

(R

1

+R

3

+R

4

+R

5

) + (R

3

+R

5

)(R

1

+R

4

)

If we divide both terms of last eqn by I

t

we obtain the desired equivalent resistance;

V

t

I

t

=

R

5

R

3

(R

1

+R

2

+R

4

) +R

1

R

4

(R

2

+R

3

+R

5

) +R

2

(R

4

R

5

+R

1

R

3

)

R

2

(R

1

+R

3

+R

4

+R

5

) + (R

3

+R

5

)(R

1

+R

4

)

= 83.5

The equivalent conductance is G

eq

= R

1

eq

= 12.0 mS.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 14

Solution of problem 1.7

We consider N capacitances connected in series and driven by a voltage source v(t) as shown in

gure 1.8. For this circuit we can write:

+

+ + +

v(t)

i(t)

v

C1

(t) v

C2

(t) v

CN

(t)

C

1

C

2

C

N

Figure 1.8: N capacitances connected in series.

v(t) = v

C

1

(t) +v

C

2

(t) +. . . +v

C

N

(t)

=

_

1

C

1

+

1

C

2

+. . . +

1

C

N

__

t

0

i(t)dt

=

1

C

eq

_

t

0

i(t)dt

that is

1

C

eq

=

1

C

1

+

1

C

2

+. . . +

1

C

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 15

Solution of problem 1.8

We consider N capacitances connected in parallel and driven by a voltage source v(t) as shown in

gure 1.9. For this circuit we can write:

+

i(t)

v(t)

i

CN

(t) i

C2

(t) i

C1

(t)

C

1

C

2

C

N

Figure 1.9: N capacitances connected in parallel.

i(t) = i

C

1

(t) +i

C

2

(t) +. . . +i

C

N

(t)

= (C

1

+C

2

+. . . +C

N

)

d v(t)

dt

= C

eq

d v(t)

dt

that is

C

eq

= C

1

+C

2

+. . . +C

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 16

Solution of problem 1.9

Circuit a): All capacitors are connected in series:

1

C

eq

=

1

C

1

+

1

C

2

+

1

C

3

Solving, we obtain:

C

eq

= 0.67 F

Circuit b): Now, all capacitors are connected in parallel:

C

eq

= C

1

+C

2

+C

3

= 11 F

Circuit c): C

1

is connected in parallel with C

2

. The capacitance resulting from this combina-

tion is connected in series with C

3

;

C

eq

=

(C

1

+C

2

)C

3

(C

1

+C

2

) +C

3

= 3 F

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 17

Solution of problem 1.10

We consider N inductances connected in series and driven by a voltage source v(t) as shown in

gure 1.10. For this circuit we can write:

+

+ + +

v(t)

i(t) L

1

L

2

L

N

v

L1

(t)

v

L2

(t) v

LN

(t)

Figure 1.10: N inductances connected in series.

v(t) = v

L

1

(t) +v

L

2

(t) +. . . +v

L

N

(t)

= (L

1

+L

2

+. . . +L

N

)

d i(t)

dt

= L

eq

d i(t)

dt

that is

L

eq

= L

1

+L

2

+. . . +L

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 18

Solution of problem 1.11

We consider N inductances connected in parallel and driven by a voltage source v(t) as shown in

gure 1.11. For this circuit we can write:

+

i

L1

(t)

L

1

i(t)

v(t)

i

LN

(t) i

L2

(t)

L

2 L

N

Figure 1.11: N inductances connected in parallel.

i(t) = i

L

1

(t) +i

L

2

(t) +. . . +i

L

N

(t)

=

_

1

L

1

+

1

L

2

+. . . +

1

L

N

__

t

0

v(t) dt

=

1

L

eq

_

t

0

v(t) dt

that is

1

L

eq

=

1

L

1

+

1

L

2

+. . . +

1

L

N

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 19

Solution of problem 1.12

Circuit a): The inductance L

2

is connected in series with L

3

and L

5

is connected in parallel

with L

6

. Hence, we can write:

L

2,3

= L

2

+L

3

= 11 mH

L

5,6

=

L

5

L

6

L

5

+L

6

= 5.74 mH

The circuit of gure 1.12 a) can be simplied as shown in gure 1.12 b). From the circuit of

A

L

1

L

2,3

B

L

4,5,6

A

L

1

L

2,3

L

5,6

L

4

B

A

L

1

L

2,3,4,5,6

B

A

L

1

L

4

L

5

L

6

1 mH 7 mH

6 mH

4 mH

12 mH

11 mH

L

2

L

3

a)

b)

c)

d)

Figure 1.12: Circuits of problem 1.12 a)

gure 1.12 b) we can observe that L

4

is connected in series with L

5,6

;

L

4,5,6

= L

4

+L

5,6

= 11.74 mH

From gure 1.12 c) we see that L

4,5,6

is connected in parallel with L

2,3

;

L

2,3,4,5,6

=

L

4,5,6

L

2,3

L

4,5,6

+L

2,3

= 5.68 mH

From gure 1.12 d) we see that the equivalent inductance is given by the series combination

of L

1

with L

2,3,4,5,6

, that is:

L

eq

= L

1

+L

2,3,4,5,6

= 6.68 mH

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 20

Circuit b): L

2

is connected in parallel with L

3

. The resulting inductance is connected in series

with L

1

and L

4

;

L

eq

= L

1

+

L

2

L

3

L

2

+L

3

+L

4

= 25.26 mH

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 21

Solution of problem 1.13

Circuit a): Using the expression for the resistive current divider we can obtain the current

through R

o

as follows:

I

o

= 0.1

R

1

[[R

2

R

o

+ (R

1

[[R

2

)

= 23.4 mA

and the voltage across R

o

is 1.4 Volt.

Circuit b): Using the expression for the resistive voltage divider we can obtain the voltage

across R

o

as follows:

V

o

= 3

R

o

R

o

+R

1

+R

2

= 0.4 V

and the current through R

o

is 10 mA.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 22

Solution of problem 1.14

We use the Nodal Analysis method to analyse the circuits of gure 1.13.

Circuit a): For this circuit we observe that the voltage across R

1

is the voltage supplied by V

s

,

that is, 5 V. Hence we have:

I

R

1

=

V

s

R

1

= 73.5 mA

Note that the current that ows through the short-circuit is I

sc

= I

R

1

+I

s

= 273.5 mA.

Circuit b): For the circuit of gure 1.13 b) we can write the following set of eqns:

_

_

_

I

s

= I

R

1

+I

R

3

+I

R

5

I

s

= I

R

2

+I

R

4

+I

R

5

I

R

1

= I

R

2

(1.15)

that is

_

_

I

s

=

V

A

V

B

R

1

+

V

A

V

C

R

3

+

V

A

R

5

I

s

=

V

B

R

2

+

V

C

R

4

+

V

A

R

5

V

A

V

B

R

1

=

V

B

R

2

(1.16)

Solving in order to obtain V

A

, V

B

and V

C

we get:

V

A

= I

s

R

5

(R

3

+R

4

)(R

2

+R

1

)

R

5

(R

1

+R

2

+R

3

+R

4

) + (R

4

+R

3

)(R

1

+R

2

)

= 30 V

V

B

= I

s

R

5

R

2

(R

3

+R

4

)

R

5

(R

1

+R

2

+R

3

+R

4

) + (R

4

+R

3

)(R

1

+R

2

)

= 14 V

V

C

= I

s

R

5

R

4

(R

2

+R

1

)

R

5

(R

1

+R

2

+R

3

+R

4

) + (R

4

+R

3

)(R

1

+R

2

)

= 18 V

V

R

1

is equal to (V

A

V

B

) = 16 V and I

R

1

= 200 mA.

Circuit c): For this circuit we can write:

_

_

V

C

V

D

= V

s

I

3

+I

2

+I

4

+I

6

= I

s

I

1

+I

s

= I

5

I

5

= I

4

+I

6

(1.17)

that is

_

_

V

C

V

D

= V

s

V

D

R

3

+

V

C

R

2

+

V

B

R

4

+

V

B

R

6

= I

s

V

C

V

A

R

1

+I

s

=

V

A

V

B

R

5

V

A

V

B

R

5

=

V

B

R

4

+

V

B

R

6

(1.18)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 23

+

0.2 A

c)

R

1

R

2

R

3

R

4

R

4

R

1

R

3

R

5

R

6

R

2

V

A

a)

b)

V

B

V

B

V

C

V

C

V

D 0

0

V

s

V

s

I

s

R

1

I

R

1

I

s

R

5

I

R

1

I

R

2

I

R

3

I

R

4

I

R

5

I

R

2

I

R

4

I

sc

I

R

5

V

A

I

R

1

I

R

3

0

I

R

6

Figure 1.13: Circuits of problem 1.14.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 24

Since R

4

is connected in parallel with R

6

the last set of eqns can be written as

_

_

V

C

V

D

= V

s

V

D

R

3

+

V

C

R

2

+

V

B

R

4,6

= I

s

V

C

V

A

R

1

+I

s

=

V

A

V

B

R

5

V

A

V

B

R

5

=

V

B

R

4,6

(1.19)

where R

4,6

= R

4

[[R

6

= 21.7 . Solving in order to obtain V

A

, V

B

, V

C

and V

D

we get

V

A

=

R

4

(R

4,6

+R

5

)[I

s

(R

3

R

1

+R

2

R

1

+R

3

R

2

) +R

2

V

s

]

(R

3

R

4

+R

2

R

4

)(R

4,6

+R

5

+R

1

) +R

3

R

2

(R

4,6

+R

4

)

= 6.95 V

V

B

=

R

4

R

4,6

[I

s

(R

3

R

1

+R

2

R

1

+R

3

R

2

) +R

2

V

s

]

(R

3

R

4

+R

2

R

4

)(R

4,6

+R

5

+R

1

) +R

3

R

2

(R

4,6

+R

4

)

= 2.71 V

V

C

=

R

2

[V

s

R

4

(R

4,6

+R

5

+R

1

) +I

s

R

3

(R

4

R

4,6

+R

4

R

5

R

1

R

4,6

)]

(R

3

R

4

+R

2

R

4

)(R

4,6

+R

5

+R

1

) +R

3

R

2

(R

4,6

+R

4

)

= 7.33 V

V

D

=

R

3

I

s

R

2

[R

4

(R

4,6

+R

5

) R

1

R

4,6

]

(R

3

R

4

+R

2

R

4

)(R

4,6

+R

5

+R

1

) +R

3

R

2

(R

4,6

+R

4

)

R

3

V

s

[R

4

(R

4,6

+R

5

+R

1

) +R

2

(R

4,6

+R

4

)]

(R

3

R

4

+R

2

R

4

)(R

4,6

+R

5

+R

1

) +R

3

R

2

(R

4,6

+R

4

)

= 2.67 V

V

R

1

is equal to V

C

V

A

= 0.37 V and I

R

1

= 24.8 mA.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 25

Solution of problem 1.15

Th evenin equivalent circuits between points A and B (see gure 1.14).

+

V

Th

R

Th

A

B

Figure 1.14: Th evenin equivalent circuit between points A and B.

Circuit b): The Th evenin voltage, V

Th

, is the voltage between points A and B obtained in the

previous problem:

V

Th

= V

A

= 30 V

The Th evenin resistance, R

Th

is determined by calculating the equivalent resistance between

the points A and B (after substituting the current source by an open-circuit). Figure 1.15

shows the equivalent circuit for the calculation of R

Th

. From this gure we can write:

A

R

1

R

2

R

3

R

4

R

5

B

R

Th

Figure 1.15: Equivalent circuit for the calculation of R

Th

.

R

Th

= (R

1

+R

2

)[[(R

3

+R

4

)[[R

5

= 42.9

Circuit c): The Th evenin voltage, V

Th

, is the voltage between points A and B obtained in the

previous problem:

V

Th

= V

A

V

B

= 4.24 V

The Th evenin resistance, R

Th

is determined by calculating the equivalent resistance between

the points A and B (after substituting the current source by an open-circuit and the voltage

source by a short-circuit). Figure 1.16 shows the equivalent circuit for the calculation of R

Th

.

From this gure we can write:

R

Th

= R

5

[[[(R2[[R

3

) + (R

4

[[R

6

) +R

1

]

= 19.4

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 26

R

5

R

2

A

B

R

Th

R

4

R

6

R

1

R

3

Figure 1.16: Equivalent circuit for the calculation of R

Th

.

Solution of problem 1.16

Norton equivalent circuits between points A and B (see gure 1.17).

I

Nt

R

Nt

A

B

Figure 1.17: Norton equivalent circuit.

Circuit b): The Norton current can be determined as follows:

I

Nt

=

V

Th

R

Th

= 699.3 mA

and the Norton resistance is equal to R

Nt

= R

Th

= 42.9 .

Circuit c): The Norton current can be determined as follows:

I

Nt

=

V

Th

R

Th

= 219.1 mA

and R

Nt

= R

Th

= 19.4 .

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 27

Solution of problem 1.17

We use the Nodal analysis method to solve the circuits of gure 1.18.

Circuit a): For this circuit we can write the following set of equations:

_

_

I

s

+I +I

R

2

= 0

I

R

2

= A

i

I

I =

V

A

R

1

I

R

3

= A

i

I

(1.20)

that is

_

_

I

s

+I +

V

B

V

A

R

2

= 0

V

B

V

A

R

2

= A

i

I

I =

V

A

R

1

V

C

R

3

= A

i

I

(1.21)

Solving in order to obtain V

A

, V

B

and V

C

we get:

V

A

=

R

1

I

s

1 +A

i

= 1.73 V

V

B

=

I

s

(R

1

A

i

R

2

)

1 +A

i

= 8.65 V

V

C

=

I

s

A

i

R

3

1 +A

i

= 16.15 V

The voltage across R

3

is V

C

. Thus, I

R

3

= 230.7 mA.

Circuit b): We observe that V = V

B

. Hence we can write:

_

_

V

C

R

3

= G

m

V

V = V

s

R

2

R

2

+R

1

(1.22)

that is,

V

C

= R

3

G

m

V

s

R

2

R

2

+R

1

= 32.1 V

The voltage across R

3

is V

C

. Thus, I

R

3

= 321 mA.

Circuit c): For this circuit we can write

_

_

I

R

1

= I

R

2

+I

R

4

V

B

V

C

= A

v

V

B

I

R

1

= I

R

2

+I

R

3

(1.23)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 28

+

R

2 A

i

I

I

R

1

a)

I

s

0

V

A V

B

V

C

R

3

I

R

2

I

R

3

I

R

3

I

R

1

I

R

2

I

R

4

I

R

3

I

R

3

I

R

1

+

+

+

R

3

R

1 A

v

V

V

c)

R

2

R

4

0

V

B

V

C

+

R

2

R

3

G

m

V

V

b)

R

1

V

s

V

0

V

B V

C

+

R

2 R

3

+

I

R

m

I

R

1

0

d)

V

B

V

A

V

C

V

D

V

s

V

s

V

s

V

s

I

s

V

D

Figure 1.18: Circuits of problem 1.17.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 29

that is

_

_

V

s

V

B

R

1

=

V

B

R

2

+

V

D

R

4

V

B

V

C

= A

v

V

B

V

s

V

B

R

1

=

V

B

R

2

+

V

C

V

D

R

3

(1.24)

Solving to obtain V

B

, V

C

and V

D

we have:

V

B

=

V

s

R

2

(R

3

+R

4

)

R

3

(R

2

+R

1

) +R

1

R

2

(1 A

v

) +R

4

(R

1

+R

2

)

= 0.56 V

V

C

=

V

s

R

2

(R

3

+R

4

)(A

v

1)

R

3

(R

2

+R

1

) +R

1

R

2

(1 A

v

) +R

4

(R

1

+R

2

)

= 5.08 V

V

D

=

R

4

V

s

R

2

(A

v

1)

R

3

(R

2

+R

1

) +R

1

R

2

(1 A

v

) +R

4

(R

1

+R

2

)

= 4.32 V

The voltage across R

3

is (V

C

V

D

) = 0.76 V and I

R

3

= 76 mA.

Circuit d): For this circuit we write:

_

_

V

B

V

C

= R

m

V

B

R

2

V

D

= V

s

V

A

R

1

+

V

C

V

D

R

3

=

V

B

R

2

V

A

R

1

= I

s

(1.25)

Solving to obtain V

A

, V

B

, V

C

and V

D

we get:

V

A

= I

s

R

1

= 23.4 V

V

B

=

R

2

(I

s

R

3

V

s

)

R

2

+R

m

+R

3

= 4.6 V

V

C

=

(I

s

R

3

V

s

)(R

2

+R

m

)

R

2

+R

m

+R

3

= 14.8 V

V

D

= V

s

= 10 V

The voltage across R

3

is V

C

V

D

= 4.8 V and I

R

3

= 66.7 mA.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 30

Solution of problem 1.18

We apply the Superposition theorem to the circuits of gure 1.19 to nd the current owing through

R

2

(I

R

2

).

+

+

+

R1

R2

R3

R4 R5

a)

Gm V

+

V

R1

R2

R3

R4

R5

b)

Vs1

Vs2

Is

Is

Vs

Figure 1.19: Circuits of problem 1.18.

1. Circuit a)

V

s1

: Figure 1.20 shows the equivalent circuit for the calculation of the contribution from

V

s1

to the current I

R

2

. The current source I

s

has been replaced by an open-circuit and

the voltage source V

s2

has been replaced by a short-circuit. From this circuit we can

write:

I

R

2

=

V

s1

R

1

+R

2

= 40.5 mA

I

s

: Figure 1.21 shows the equivalent circuit for the calculation of the contribution from

I

s

to the current I

R

2

. Both voltage sources were replaced by short-circuits. From this

gure we observe that R

1

and R

2

form a resistive current divider. Hence we have:

I

R

2

=

R

1

R

1

+R

2

I

s

= 64.9 mA

V

s2

: Figure 1.22 shows the equivalent circuit for the calculation of the contribution from

V

s2

to the current I

R

2

. The current source I

s

was replaced by an open-circuit and the

voltage source V

s1

was replaced by a short-circuit. We observe that there is no closed

electrical path between R

2

and V

s2

. Hence the contribution fromV

s2

to the current I

R

2

is

zero.The current that ows through R

2

(sum of all contributions) is I

R

2

= 40.5+64.9 =

105.4 mA.

2. Circuit b)

V

s1

: Figure 1.23 shows the equivalent circuit for the calculation of the contribution from

V

s

to the current I

R

2

. The current source I

s

was replaced by an open-circuit. For this

circuit we can write:

_

_

I

R

1

= I

R

2

I

R

2

+G

m

V = I

R

4

I

R

4

= I

R

5

V = V

C

V

D

(1.26)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 31

+

R

1

R

2

V

s1

I

R2

Figure 1.20: Equivalent circuit for the calculation of the contribution from V

s1

to the current I

R

2

.

R

2

R

3

R

4 R

5

I

s

R

1

Figure 1.21: Equivalent circuit for the calculation of the contribution from I

s

to the current I

R

2

.

that is

_

_

V

s

V

B

R

1

=

V

B

V

C

R

2

V

B

V

C

R

2

+G

m

(V

C

V

D

) =

V

C

V

D

R

4

V

C

V

D

R

4

=

V

D

R

5

(1.27)

Solving, we obtain:

V

B

= V

s

R

5

+R

4

G

m

R

2

R

4

+R

2

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

= 1.79 V

V

C

= V

s

R

5

+R

4

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

(1.28)

= 0.08 V

V

D

= V

s

R

5

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

= 0.03 V

and

I

R

2

=

V

B

V

C

R

2

= 20.8 mA

I

s

: Figure 1.24 shows the equivalent circuit for the calculation of the contribution from

I

s

to the current I

R

2

. The voltage source V

s

was replaced by a short-circuit. For this

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 32

+

R

2

R

5

R

1

I

R2

R

4

V

s2

Figure 1.22: Equivalent circuit for the calculation of the contribution from V

s2

to the current I

R

2

.

+

G

m

V

+

V

R

1

R

2

R

5

V

B

V

C

V

D

I

R5

I

R4

I

R2

I

R1

R

4

0

V

s

Figure 1.23: Equivalent circuit for the calculation of the contribution from V

s

to the current I

R

2

.

circuit we write:

_

_

I

s

= I

R

3

I

s

= I

R

1

+I

R

2

I

R

2

+G

m

V = I

R

4

V = (V

C

V

D

)

I

R

4

= I

R

5

+I

s

(1.29)

that is

_

_

I

s

=

V

A

V

B

R

3

I

s

=

V

B

R

1

+

V

B

V

C

R

2

V

B

V

C

R

2

+G

m

(V

C

V

D

) =

V

C

V

D

R

4

V

C

V

D

R

4

=

V

D

R

5

+I

s

(1.30)

Solving in order to obtain V

A

, V

B

, V

C

and V

D

we get:

V

A

= I

s

(G

m

R

4

1)(R

3

R

2

+R

3

R

1

+R

1

R

2

)

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

I

s

R

3

(R

5

+R

4

) +R

1

R

4

(1 +G

m

R

5

)

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

= 1.3 V

V

B

= I

s

R

1

R

5

G

m

R

4

+R

4

G

m

R

2

R

4

+R

2

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 33

G

m

V

+

V

R

3

R

1

R

2

I

s

0

V

A

V

B

V

C

V

D

I

R5

R

5

R

4

I

R4

I

R3

I

R2

I

R1

Figure 1.24: Equivalent circuit for the calculation of the contribution from I

s

to I

R

2

.

= 0.3 V

V

C

= I

s

R

2

R

5

+R

2

R

5

G

m

R

4

+R

5

G

m

R

4

R

1

+R

4

R

1

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

= 5.96 V

V

D

= I

s

R

5

R

2

+G

m

R

2

R

4

+R

1

G

m

R

4

R

4

G

m

R

2

R

4

R

2

R

5

R

4

+R

1

G

m

R

4

R

1

= 5.81 V

and the current owing through R

2

is:

I

R

2

=

V

B

V

C

R

2

= 69.6 mA

The total current (the sum of all the contributions) is 90.4 mA.

3. Circuit c)

V

s

: Figure 1.25 a) shows the equivalent circuit for the calculation of the contribution

from V

s

to V

R

2

. From this gure we observe that the voltage across R

2

is:

V

R

2

= A

v

V

C

+V

s

= (1 A

v

) V

s

= 90 V

Note that V

C

= V

s

. I

R

2

= 0.45A.

I

r

: Figure 1.25 b) shows the equivalent circuit for the calculation of the contribution

from I

r

to V

R

2

. Note that V

C

is zero. Hence, the voltage-controlled voltage source is

now effectively a short-circuit and the voltage-controlled current source is now an open-

circuit. From this gure we observe that the voltage across R

2

is zero.

The overall voltage across R

2

is 90 V and the overall current through R

2

is 0.45 A.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

1. Elementary electrical circuit analysis 34

+

V

C

R

1

+

V

s

G

m

V

C

A

v

V

C

+

a)

b)

+

R

2

V

R2

+

V

R2

I

r

+

V

C

= 0

R

2

I

R2

Figure 1.25: a) Equivalent circuit for the calculation of the contribution fromV

s

to V

R

2

b) Equivalent

circuit for the calculation of the contribution from I

r

to V

R

2

.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

Chapter 2

Complex numbers: An introduction

Solution of problem 2.1

Axis

Real

Axis

Imaginary

2

4

4

3

2.5

z

1

z

2

z

3

z

4

Figure 2.1: Representation of the complex numbers of problem 1.

Solution of problem 2.2

1. 2

2. j 2

3. 11.25 +j 2.5

4. 0.3562 +j 0.3836

5. (1.25, 0.9)

6. (2.2, 5.1)

7. (4, 15.5)

8. (1.1746, 0.4483)

Solution of problem 2.3

2. Complex numbers: An introduction 36

1. z = 3/2 +j

127/2 or z = 3/2 j

127/2

2. z = 1/4 +

21/4 or z = 1/4

21/4

3. z = 1/4 +j 1/4

39 or z = 1/4 j 1/4

39

4. z = 3

5. z =

7/4 +j

65/4 or z =

7/4 j

65/4

Solution of problem 2.4

1. 1.414 0.785 (rad)

2. 1.732 2.186 (rad)

3. 2.022 0.149 (rad)

4. 3.162 2.562 (rad)

Solution of problem 2.5

1. 0.5

2. 0.75 j 1.3

3. j 0.5

4. j 0.5

Solution of problem 2.6

1. 2

2. 8

3. 13.753 +j 9.992

4. 0.072 +j 0.222

5. 4.511 +j 8.142

6. 0.45 j 0.279

Solution of problem 2.7

1. z = 1 or z = 1

2. z =

2/2(1 +j) or z =

2/2(1 j)

3. z = 2

1/6

exp(j/12) or

z = 2

1/6

exp(j9/12) or

z = 2

1/6

exp(j17/12)

4. z = (5/2)

1/5

exp(j3/20) or

z = (5/2)

1/5

exp(j5/20) or

z = (5/2)

1/5

exp(j13/20) or

z = (5/2)

1/5

exp(j21/20) or

z = (5/2)

1/5

exp(j29/20).

Introduction to linear circuit analysis and modelling Moura and Darwazeh

Chapter 3

Frequency domain electrical signal

and circuit analysis

Solution of problem 3.1

The effective value for each voltage waveform v

i

(t) can be determined as follows:

V

eff

i

=

1

T

_

t

o

+T

t

o

v

2

i

(t) dt (3.1)

where t

o

can be chosen to facilitate the calculation of the integral in the last eqn.

a) Using eqn 3.1 with t

o

= T/2 we can write:

V

eff

1

=

1

T

_

T/2

T/2

v

2

1

(t) dt

The integral of the last eqn can be determined as follows:

1

T

_

T/2

T/2

v

2

1

(t) dt =

V

2

A

T

_

T/4

T/4

cos

2

( t) dt (with = 2/T)

=

V

2

A

2 T

_

T/4

T/4

[1 + cos(2 t)] dt

=

V

2

A

2 T

_

t

_

T/4

T/4

+

V

2

A

4 T

_

sin(2 t)

_

T/4

T/4

=

V

2

A

4

Hence, V

eff

1

= V

A

/2.

b) Using eqn 3.1 with t

o

= 0 we can write:

V

eff

2

=

1

T

_

T

0

v

2

2

(t) dt

The integral of the last eqn can be determined as follows:

1

T

_

T

0

v

2

2

(t) dt =

V

2

B

T

3

_

T

0

t

2

dt

=

V

2

B

T

3

_

t

3

3

_

T

0

=

V

2

B

3

Hence, V

eff

2

= V

B

/

3.

3. Frequency domain electrical signal and circuit analysis 38

c) Using eqn 3.1 with t

o

= T/2 we can write:

V

eff

3

=

1

T

_

T/2

T/2

v

2

3

(t) dt

The integral of the last eqn can be determined as follows:

1

T

_

T/2

T/2

v

2

3

(t) dt =

V

2

C

T

_

T/4

T/4

sin

2

(4 t) dt (with = 2/T)

=

V

2

C

2 T

_

T/4

T/4

[1 + cos(8 t)] dt

=

V

2

C

2 T

_

t

_

T/4

T/4

+

V

2

C

2 T 8

_

sin(8 t)

_

T/4

T/4

=

V

2

C

4

Hence, V

eff

3

= V

C

/2.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 39

Solution of problem 3.2

Assuming that the AC voltage across Z

L

is:

v

a

(t) = V

a

cos( t +

v

)

and that the AC current through Z

L

is:

i

a

(t) = I

a

cos( t +

i

)

we can obtain the average power dissipated by Z

L

as follows:

P

AV

=

1

T

_

T

0

v

a

(t) i

a

(t) dt

=

V

a

I

a

2 T

_

T

0

cos(

v

i

) dt +

V

a

I

a

2 T

_

T

0

cos(2 t +

v

+

i

) dt

=

V

a

I

a

2

cos(

v

i

)

=

V

a

I

a

2

Real

_

e

j

v

e

j

i

=

1

2

Real[V

A

I

A

]

with

V

A

= V

a

e

j

v

I

A

= I

a

e

j

i

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 40

Solution of problem 3.3

We solve the circuits of this problem using the Nodal analysis method together with phasor analysis.

+

V

Z

C

Z

L

R

I

Figure 3.1: Circuit (a) of problem 3.3.

Circuit a): The impedances associated with the capacitor, Z

C

and the inductor, Z

L

, are:

Z

C

=

1

j C

=30 krad/s

= j 37.04

Z

L

= j L

=30 krad/s

= j 90.0

The (static) phasor associated with the voltage source is V = 10 exp(j /4) V. Since R is

connected in series with C and with L we can determine the current I as follows:

I =

V

Z

L

+Z

C

+R

=

10 e

j /4

j 90 j37.04 + 100

= 88.4 e

j 0.30

mA

The voltage across the resistance, V

R

, can be obtained from:

V

R

= RI

= 8.84 e

j 0.30

V

The voltage across the capacitance, V

C

, can be obtained from:

V

C

= Z

C

I

= 3.27e

j 0.30j /2

V

= 3.27e

j 1.27

V

The voltage across the inductance, V

L

, is:

V

L

= Z

L

I

= 7.95e

j 0.30+j /2

V

= 7.95e

j 1.87

V

Note that, as expected, the voltage and the current through the resistance are in phase, that

is, the phase difference between the voltage and the current is zero. On the other hand, the

voltage across the capacitor lags the current by /2 while the voltage across the inductor leads

the current by /2.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 41

+

Z

C

Z

L

R

2

V

R

1

V

A

V

B

V

C

b)

V

R

1

Z

CLR2

V

B

I

ZL

I

R1

I

ZC

V

A

= V

0

0

a)

Figure 3.2: a) Circuit (b) of gure 3.1. b) Equivalent circuit

Circuit b): The impedances associated with the capacitance and inductance are:

Z

C

=

1

j C

=30 krad/s

= j166.7

Z

L

= j L

=30 krad/s

= j 300.0

From gure 3.2 a) we observe that the series combination of R

2

with Z

L

is connected in

parallel with Z

C

. Hence, we can obtain an equivalent impedance, which represent these com-

binations, as follows:

Z

CLR

2

= Z

C

[[(Z

L

+R

2

)

= 77.3 j 201.0 (3.2)

Fromgure 3.2 b) we recognise that R

1

and Z

CLR

2

forman impedance voltage divider. Hence

we can write:

V

B

= V

Z

CLR

2

Z

CLR

2

+R

1

= 1.97 e

j 0.23

V

From gure 3.2 a) we also note that Z

L

and R

2

form an impedance voltage divider which

allows us to relate V

C

and V

B

as follows:

V

C

= V

B

R

2

Z

L

+R

2

= 1.39 e

j 1.02

V

Now, the current in each element can be obtained:

I

R

1

=

V V

B

R

1

= 9.1 e

j 0.97

mA

I

Z

C

=

V

B

Z

C

= 11.8 e

j 1.34

mA

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 42

I

Z

L

=

V

B

V

C

Z

L

= 4.6 e

j 1.02

mA

I

R

2

= I

Z

L

Circuit c): The impedances associated with the capacitance and inductance are:

+

+

V

I R

3

V

I

R

1

R

2

Z

L

Z

C

b)

a)

0

0

Z

CR2

R

3

V

A

V

B

V

C

V

C

V

D

V

A

I

LR1

Z

LR1

I

CR2

I

R3

Figure 3.3: a) Circuit (c) of gure 3.1. b) Equivalent circuit

Z

C

=

1

j C

=30 krad/s

= j47.6

Z

L

= j L

=30 krad/s

= j 150

Since R

1

is in series with Z

L

and R

2

is in series with Z

C

we can obtain the equivalent circuit

of gure 3.3 b) with

Z

LR

1

= Z

L

+R

1

= 250 +j 150

Z

CR

2

= Z

C

+R

2

= 200 j47.6

For this circuit we can write the following set of eqns:

_

_

_

I

LR

1

+I

R

3

= I

V

A

V

C

= V

(3.3)

that is:

_

_

V

A

Z

LR

1

+

V

C

R

3

= I

V

A

V

C

= V

(3.4)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 43

Solving in order to obtain V

A

and V

C

we get:

V

A

= Z

LR

1

V +I R

3

R

3

+Z

LR

1

= 27.38 e

j 1.26

V

V

C

= R

3

I Z

LR

1

V

R

3

+Z

LR

1

= 19.05 e

j 1.50

V

Hence, the current that ows through C and R

2

is given by:

I

CR

2

=

V

A

V

C

Z

CR

2

= 48.6 e

j 1.02

mA (3.5)

and the current that ows through L and R

1

is given by:

I

LR

1

=

V

A

Z

LR

1

= 93.9 e

j 0.72

mA (3.6)

The current that ows through R

3

is given by:

I

R

3

=

V

C

R

3

= 68.0 e

j 1.50

mA (3.7)

The voltages across R

2

and C are given by:

V

R

2

= I

CR

2

R

2

= 9.73 e

j 1.02

V

V

Z

C

= I

CR

2

Z

C

= 2.32 e

j 0.55

V

The voltages across R

1

and L are given by:

V

R

1

= I

LR

1

R

1

= 23.48 e

j 0.72

V

V

Z

L

= I

LR

1

Z

L

= 14.09 e

j 2.29

V

Circuit d): The impedances associated with the capacitance and inductance are:

Z

C

=

1

j C

=30 krad/s

= j 33.3

Z

L

= j L

=30 krad/s

= j 180

Since R

1

is in parallel with Z

C

and R

2

is in series with Z

L

we can obtain the equivalent circuit

of gure 3.4 b) with

Z

CR

1

=

Z

C

R

1

Z

C

+R

1

= 0.85 j 33.31

Z

LR

2

= Z

L

+R

2

= 800 +j180

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 44

+

V

1

+

V

Z

C

R

1

Z

L

R

2

G

m

V

1

(A)

G

m

V

1

(A)

+

V

1

V

B

V

A

= V = V

1

Z

CR1

V

Z

LR2

a)

b)

0

I

LR2

Figure 3.4: a) Circuit (d) of gure 3.1. b) Equivalent circuit

For this circuit we can write the following:

I

LR

2

+G

m

V

1

= 0

Since V

1

= V we can write the last eqn as:

V

B

Z

LR

2

G

m

V = 0

that is

V

B

= Z

LR

2

G

m

V

= 820.0 e

j 1.01

V

The currents that ow through C, I

Z

C

, and through R

1

, I

R

1

, are given by

I

Z

C

=

V

Z

C

= 0.3 e

j 2.36

A

I

R

1

=

V

R

1

= 7.7 e

j 0.79

mA

The current that ows through the series combination of L with R

2

is

I

LR

2

= 1.0 e

j 0.79

A

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 45

Solution of problem 3.4

In order to have maximum power transfer at f = 35 kHz Z

L

must be equal to Z

S

at this frequency.

Z

S

is the impedance of the series combination of the 120 resistor and the capacitor (see gure

+

Z

L

Z

L

V

v(t)

b)

a)

0.6 F

120

Z

S

Figure 3.5: a) Circuit of problem 3.4 b) Equivalent circuit.

3.5):

Z

S

= R +

1

j 2 f C

f=35 kHz

= 120 j 7.58

Hence Z

L

should be made equal to Z

S

= 120 + j 7.58 . A circuit which realises this impedance

Z

L

= Z

S

at f = 35 kHz is the series combination of a 120 resistance with an inductance L such

that;

j 2 f L

f=35 kHz

= j 7.58

that is L = 34.46 H.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 46

Solution of problem 3.5

a): The average value C

0

is determined as follows:

C

0

=

1

T

_

T/2

T/2

v

1

(t) dt

=

1

T

_

T/4

T/4

V

A

cos( t) dt ( = 2/T)

=

V

A

T

T

2

_

sin

_

2

T

t

__

T/4

T/4

=

V

A

The coefcients C

n

([n[ > 0) are determined as

C

n

=

1

T

_

T/2

T/2

v

1

(t) e

j 2

n

T

t

dt

=

V

A

T

_

T/2

T/2

cos

_

2

1

T

t

_

e

j 2

n

T

t

dt

=

V

A

2 T

_

T/4

T/4

e

j 2

1n

T

t

dt +

V

A

2 T

_

T/4

T/4

e

j 2

1+n

T

t

dt

=

V

A

2 T

T

j 2 (1 n)

_

e

j 2

1n

T

t

_

T/4

T/4

+

V

A

2 T

T

j 2 (1 +n)

_

e

j 2

1+n

T

t

_

T/4

T/4

=

V

A

2

_

sin

_

(1 n)

1 n

+

sin

_

(1 +n)

1 +n

_

=

V

A

4

sinc

_

1 n

2

_

+

V

A

4

sinc

_

1 +n

2

_

Figure 3.6 shows the spectrum of v

1

(t).

b): The average value C

0

is determined as follows:

C

0

=

1

T

_

T

0

v

2

(t) dt

=

1

T

_

T

0

V

B

t

T

dt

=

V

B

2

(3.8)

The coefcients C

n

([n[ > 0) are determined from

C

n

=

1

T

_

T

0

v

2

(t) e

j 2

n

T

t

dt

=

1

T

_

T

0

V

B

t

T

e

j 2

n

T

t

dt

=

V

B

T

2

_

e

j 2

n

T

t

_

j 2

n

T

_

2

_

1 +j 2

n

T

t

_

_

T

0

=

V

B

(2n)

2

_

e

j 2 n

. .

1

(1 +j 2 n) 1

_

=

j V

B

2n

(3.9)

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 47

2 4 6 4 6 2

6 2 4 6 4 2

1

f/T

|C

n

| (V)

C

n

(rad)

f/T

a)

b)

Figure 3.6: Spectrum of v

1

(t) a) Magnitude. b) Phase.

Figure 3.7 shows the spectrum of v

2

(t).

c): The average value C

0

is zero. The coefcients C

n

([n[ > 0) are determined from

C

n

=

1

T

_

T

0

v

3

(t) e

j 2

n

T

t

dt

=

1

T

_

T/4

T/4

V

C

cos(4 t) dt ( = 2/T)

=

V

C

4

sinc

_

4 n

2

_

+

V

A

4

sinc

_

4 +n

2

_

Figure 3.8 shows the spectrum of v

3

(t). Note that the spectrum contains no DC component.

Introduction to linear circuit analysis and modelling Moura and Darwazeh

3. Frequency domain electrical signal and circuit analysis 48

2 4 6 4 6 2

1

|C

n

| (V)

C

n

(rad)

f/T

a)

b)

6

4 2

2 4 6

f/T

Figure 3.7: Spectrum of v

2

(t) a) Magnitude. b) Phase.

Solution of problem 3.6

Using phasor analysis we determine the output voltage V

R

as follows:

V

R

= V

S

R

Z

C

+R

(3.10)

where Z

C