Professional Documents

Culture Documents

2.2 Basic Integrated Circuit Processes: Objective

Uploaded by

tutul_kOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2.2 Basic Integrated Circuit Processes: Objective

Uploaded by

tutul_kCopyright:

Available Formats

Basic IC Processes (5/30/00)

Page 1

2.2 BASIC INTEGRATED CIRCUIT PROCESSES

INTRODUCTION Objective The objective of this presentation is: 1.) Introduce the fabrication of integrated circuits 2.) Describe the basic fabrication process steps by which an integrated circuit is made Outline Integrated circuit fabrication Basic processing steps

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 2

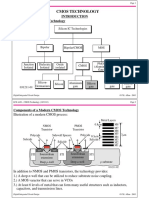

INTEGRATED CIRCUIT FABRICATION Classification of Silicon Technology

Silicon IC Technologies

Bipolar

Bipolar/MOS

MOS

Junction Isolated

Dielectric Isolated

Oxide isolated

CMOS

PMOS (Aluminum Gate)

NMOS

Aluminum gate

Silicon gate

Aluminum gate

Silicon gate

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 3

Comparison of Bipolar and CMOS Technologies Comparison of BJT and MOSFET technology from an analog viewpoint: Feature Cutoff Frequency(fT) Noise (thermal about the same) DC Range of Operation Small Signal Output Resistance Switch Implementation Capacitor Implementation 100 GHz Less 1/f 9 decades of exponential current versus vBE Slightly larger Poor Voltage dependent BJT MOSFET 50 GHz (0.25m) More 1/f 2-3 decades of square law behavior Smaller for short channel Good Reasonably good

Which is best? Almost every comparison favors the BJT, however a similar comparison made from a digital viewpoint would come up on the side of CMOS. Therefore, since large-volume technology will be driven by digital demands, CMOS is an obvious result as the technology of availability. Other factors: The potential for technology improvement for CMOS is greater than for BJT Performance generally increases with decreasing channel length BiCMOS may be the best compromise for the mixed signal system on a chip.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 4

BASIC FABRICATION PROCESSES Basic steps Oxide growth Thermal diffusion Ion implantation Deposition Etching Epitaxy Photolithography Photolithography is the means by which the above steps are applied to selected areas of the silicon wafer. Silicon wafer

125-200 mm (5"-8")

0.5-0.8mm

n-type: 3-5 -cm p-type: 14-16 -cm

Fig. 2.1-1r

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 5

Oxidation Description: Oxidation is the process by which a layer of silicon dioxide is grown on the surface of a silicon wafer.

Original silicon surface Silicon dioxide 0.44 tox tox

Silicon substrate

Fig. 2.1-2

Uses: Protect the underlying material from contamination Provide isolation between two layers. Very thin oxides (100 to 1000) are grown using dry oxidation techniques. Thicker oxides (>1000) are grown using wet oxidation techniques.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 6

Diffusion Diffusion is the movement of impurity atoms at the surface of the silicon into the bulk of the silicon. Always in the direction from higher concentration to lower concentration.

Low Concentration

Fig. 2.1-3

High Concentration

Diffusion is typically done at high temperatures: 800 to 1400C ERFC

N0 N0 t1 < t2 < t3 NB N(x) t1 Depth (x) (a) Infinite source of impurities at the surface. t2 t3 t1 t2 t3 t1 < t2 < t3

Gaussian

N(x) NB

Depth (x) (b) a finite source of impurities at the surface.)

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 7

Ion Implantation Ion implantation is the process by which impurity ions are accelerated to a high velocity and physically lodged into the target material.

Path of impurity atom Fixed Atom Fixed Atom Impurity Atom final resting place Fixed Atom

Fig. 2.1-5

Anneal is required to activate the impurity atoms and repair the physical damage to the crystal lattice. This step is done at 500 to 800C. Ion implantation is a lower temperature process compared to diffusion. Can implant through surface layers, thus it is useful for fieldConcentration peak threshold adjustment. N(x) Can achieve unique doping profile such as buried concentration peak.

NB 0 Depth (x)

Fig. 2.1-6

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 8

Deposition Deposition is the means by which various materials are deposited on the silicon wafer. Examples: Silicon nitride (Si3N4) Silicon dioxide (SiO2) Aluminum Polysilicon There are various ways to deposit a material on a substrate: Chemical-vapor deposition (CVD) Low-pressure chemical-vapor deposition (LPCVD) Plasma-assisted chemical-vapor deposition (PECVD) Sputter deposition Material that is being deposited using these techniques cover the entire wafer.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 9

Etching Etching is the process of selectively removing a layer of material. When etching is performed, the etchant may remove portions or all of: The desired material The underlying layer The masking layer Important considerations: Anisotropy of the etch is defined as, A = 1-(lateral etch rate/vertical etch rate) Selectivity of the etch (film to mask and film to substrate) is defined as, film etch rate Sfilm-mask = mask etch rate A = 1 and Sfilm-mask = are desired. There are basically two types of etches: Wet etch which uses chemicals Dry etch which uses chemically active ionized gases.

Fig. 2.1-7

a Mask Film Underlying layer Mask Film

Selectivity

Selectivity

c b

Anisotropy Underlying layer

(a) Portion of the top layer ready for etching.

(b) Horizontal etching and etching of underlying layer.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 10

Epitaxy Epitaxial growth consists of the formation of a layer of single-crystal silicon on the surface of the silicon material so that the crystal structure of the silicon is continuous across the interfaces. It is done externally to the material as opposed to diffusion which is internal The epitaxial layer (epi) can be doped differently, even oppositely, of the material on which it grown It accomplished at high temperatures using a chemical reaction at the surface The epi layer can be any thickness, typically 1-20 microns

Gaseous cloud containing SiCL4 or SiH4

Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si + Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si Si

+

Si

Si Si

Si Si Si Si

Si

+

Si

Si Si Si Si Si

Si Si Si Si Si Si

Si

+

Si

+ Si Si

- Si

Si Si

Si

Si

Si

Si

Fig. 2.1-7.5

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 11

Photolithography Components Photoresist material Mask Material to be patterned (e.g., oxide) Positive photoresist Areas exposed to UV light are soluble in the developer Negative photoresist Areas not exposed to UV light are soluble in the developer Steps 1. Apply photoresist 2. Soft bake (drives off solvents in the photoresist) 3. Expose the photoresist to UV light through a mask 4. Develop (remove unwanted photoresist using solvents) 5. Hard bake ( 100C) 6. Remove photoresist (solvents)

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 12

Illustration of Photolithography - Exposure The process of exposing selective areas to light through a photomask is called printing. Types of printing include: Contact printing Proximity printing Projection printing

Photomask

UV Light Photomask

Photoresist Polysilicon

Fig. 2.1-8

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 13

Illustration of Photolithography - Positive Photoresist

Develop Polysilicon Photoresist Photoresist Polysilicon Etch

Remove photoresist

Polysilicon

Fig. 2.1-9

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 14

Illustration of Photolithography - Negative Photoresist (Not used much any more)

Photoresist

Underlying Layer Photoresist

SiO2

Underlying Layer SiO2

SiO2

Underlying Layer

Fig. 2.1-10

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 15

SUMMARY Fabrication is the means by which the circuit components, both active and passive, are built as an integrated circuit. Basic process steps include: Oxide growth Thermal diffusion Ion implantation Deposition Etching Epitaxy These steps are restricted to a physical area by the use of photolithography. The use of photolithography to apply a process to a certain area is called a masking step. The complexity of a process can be measured in the terms of the number of masking steps or masks required to implement the process.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

You might also like

- LINEAR INTEGRATED CIRUITS - 2 Marks Question Bank - IV Sem ECEDocument19 pagesLINEAR INTEGRATED CIRUITS - 2 Marks Question Bank - IV Sem ECEJOHN PETER100% (7)

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocument15 pages2.2 Basic Integrated Circuit Processes: ObjectiveLalit BurrakNo ratings yet

- CMOS Tech-2UP (12 - 11 - 03)Document29 pagesCMOS Tech-2UP (12 - 11 - 03)Mountsinai CscNo ratings yet

- Unit - IDocument69 pagesUnit - IsaravananNo ratings yet

- Ic FabricationDocument7 pagesIc FabricationphooolNo ratings yet

- How Semicon WorksDocument15 pagesHow Semicon WorkskrisNo ratings yet

- Unit I Ic FabricationDocument23 pagesUnit I Ic FabricationBhuvana VaradharajNo ratings yet

- M Group: Linear Integrated Circuits (Ec1313) IC FabricationDocument17 pagesM Group: Linear Integrated Circuits (Ec1313) IC Fabricationscribdm100% (1)

- EC1313 Two Marks Linear Integrated CircuitsDocument11 pagesEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004No ratings yet

- Integrated CircuitDocument51 pagesIntegrated Circuitparthos100% (1)

- EE6303-Linear Integrated Circuits and Applications Q&ADocument24 pagesEE6303-Linear Integrated Circuits and Applications Q&AY RohitNo ratings yet

- Ee2254 Lica QBDocument0 pagesEe2254 Lica QBnjparNo ratings yet

- Dasar Design CMOS TransistorDocument49 pagesDasar Design CMOS Transistormaqbulloh darojatiNo ratings yet

- Technology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsDocument4 pagesTechnology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsAshima PatleyNo ratings yet

- Lecture 42Document18 pagesLecture 42Nathan KemboNo ratings yet

- Linear Integrated Circuits - EC2254Document77 pagesLinear Integrated Circuits - EC2254Muthu LakiNo ratings yet

- CMOS Fabrication: (With Extended Comments)Document26 pagesCMOS Fabrication: (With Extended Comments)srivardhana7No ratings yet

- The 243 Steps of Making Photonic Integrated Circuits in InpDocument5 pagesThe 243 Steps of Making Photonic Integrated Circuits in InpBaranigha CjNo ratings yet

- Manufacturing of Microprocessor: Farooq Ahmad ShahDocument18 pagesManufacturing of Microprocessor: Farooq Ahmad ShahCristianCristianHerreraNo ratings yet

- Microfabrication: Yash V. Kankal Roll No.Document31 pagesMicrofabrication: Yash V. Kankal Roll No.yogesh_lonkarNo ratings yet

- CM - MEMS - TWO MARKS Five UNITSDocument7 pagesCM - MEMS - TWO MARKS Five UNITSSandhiyaNo ratings yet

- EE476 VLSI Digital Circuits Summer 2011 Lecture 02: IC ManufacturingDocument42 pagesEE476 VLSI Digital Circuits Summer 2011 Lecture 02: IC ManufacturingTrung LyamNo ratings yet

- Chapter 4fabricationofICDocument20 pagesChapter 4fabricationofICManikandan RadhakrishnanNo ratings yet

- Introduction To Integrated Circuit TechnologyDocument45 pagesIntroduction To Integrated Circuit TechnologyShrikant JagtapNo ratings yet

- SM ART-CUT@ Techno Logy S 0 1 A New High Volume Application For Ion ImplantationDocument4 pagesSM ART-CUT@ Techno Logy S 0 1 A New High Volume Application For Ion ImplantationMarco Aurélio DonatoNo ratings yet

- IC Fabrication Process: Course: VLSI DesignDocument14 pagesIC Fabrication Process: Course: VLSI DesignDwayne WaltonNo ratings yet

- IC FabricationDocument27 pagesIC FabricationJohn PaulNo ratings yet

- CMOS/Processing TechnologyDocument15 pagesCMOS/Processing TechnologyYidnekachwe MekuriaNo ratings yet

- 001 Device FabricationDocument60 pages001 Device FabricationSerwan BamerniNo ratings yet

- Ee6303 - Linear Integrated CircuitsDocument13 pagesEe6303 - Linear Integrated CircuitsSaran ArunNo ratings yet

- Unit Process Steps VlsiDocument83 pagesUnit Process Steps Vlsis.r.No ratings yet

- Unit 1 IC Fabrication: Advantages of Integrated CircuitsDocument13 pagesUnit 1 IC Fabrication: Advantages of Integrated CircuitsVerloves Love0% (1)

- Semiconductor Device Fabrication (Chapter 9)Document13 pagesSemiconductor Device Fabrication (Chapter 9)Hasi De RustafariNo ratings yet

- Ic Fabrication Ansaf RmahDocument27 pagesIc Fabrication Ansaf RmahkaisobaiedNo ratings yet

- Lec 4 CMOS Technology ICFabricationDocument46 pagesLec 4 CMOS Technology ICFabricationMainak TarafdarNo ratings yet

- Fabrication of Ic'sDocument14 pagesFabrication of Ic'sBhaskar Rao OndruNo ratings yet

- Ic FabricationDocument31 pagesIc FabricationMukesh Nexus100% (1)

- 5 LicaDocument26 pages5 LicaVantharAlaNo ratings yet

- Basic Process DiffusionDocument104 pagesBasic Process DiffusionBalamurugan Velayutham100% (1)

- EE2254 LIC 2marks 2013Document16 pagesEE2254 LIC 2marks 2013sivagamiNo ratings yet

- Linear and Digital Integrated CircuitsDocument58 pagesLinear and Digital Integrated Circuitssuresh151971No ratings yet

- LIC Unit 1Document20 pagesLIC Unit 1sietgunaNo ratings yet

- CH 03Document37 pagesCH 03chilledkarthikNo ratings yet

- Optics, Modules, and Lenses: 5.1 Planar Lightwave CircuitsDocument30 pagesOptics, Modules, and Lenses: 5.1 Planar Lightwave CircuitsLauren StevensonNo ratings yet

- Unit-I Ic Fabrication: Part-ADocument32 pagesUnit-I Ic Fabrication: Part-Asanthosh sekarNo ratings yet

- Fabrication, Layout, and SimulationDocument26 pagesFabrication, Layout, and Simulationshiny johnNo ratings yet

- How Is Semiconductor ManufacturedDocument13 pagesHow Is Semiconductor ManufacturedjackNo ratings yet

- Fabrication Process: LithographyDocument15 pagesFabrication Process: LithographyBishanka Brata BhowmikNo ratings yet

- Fabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatDocument40 pagesFabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatRavi HosamaniNo ratings yet

- Ee6303 Uw LicDocument125 pagesEe6303 Uw LicVijay KumarNo ratings yet

- Unit 1Document66 pagesUnit 1srgperumalNo ratings yet

- Fabrication of Fet: Dr. R. Ramaprabha (Sec A)Document10 pagesFabrication of Fet: Dr. R. Ramaprabha (Sec A)Kapildev KumarNo ratings yet

- Nano SYNTHESIS &fabrication1Document39 pagesNano SYNTHESIS &fabrication1APOORV SINGHNo ratings yet

- Assignment (1) :-Part (1) - : Epitaxial Deposition:-: Name: Ziad Hosni Mohammed Hassan Section: 5 Number: 157Document10 pagesAssignment (1) :-Part (1) - : Epitaxial Deposition:-: Name: Ziad Hosni Mohammed Hassan Section: 5 Number: 157Mohamed El BazNo ratings yet

- Ceramic Materials for Energy Applications VIFrom EverandCeramic Materials for Energy Applications VIHua-Tay LinNo ratings yet

- Plasma Etching Processes for Interconnect Realization in VLSIFrom EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNo ratings yet

- Compendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)From EverandCompendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)No ratings yet

- FIFO IDT 72T Family PDFDocument53 pagesFIFO IDT 72T Family PDFtutul_kNo ratings yet

- Electromagnetism Amperes LawDocument21 pagesElectromagnetism Amperes Lawmohanb2002No ratings yet

- How To Compile and Run A C Program On Ubuntu LinuxDocument25 pagesHow To Compile and Run A C Program On Ubuntu Linuxtutul_kNo ratings yet

- How To Compile and Run A C Program On Ubuntu LinuxDocument25 pagesHow To Compile and Run A C Program On Ubuntu Linuxtutul_kNo ratings yet

- How To Compile and Run A C Program On Ubuntu LinuxDocument7 pagesHow To Compile and Run A C Program On Ubuntu LinuxafmalallafNo ratings yet

- Satellite Comm.Document156 pagesSatellite Comm.Akshay KarveNo ratings yet

- Size Chart - Footprint Selection Chart - Topline Dummy Component Foot Print Cross Reference. Packaging Types - Component Sizes - Smd Size , Capacitorsize , Capacitor Size , Capacitor Dimesion Code , Ic Package Size Chip Size 0102, 01005 , 1005, 0201 ,Document7 pagesSize Chart - Footprint Selection Chart - Topline Dummy Component Foot Print Cross Reference. Packaging Types - Component Sizes - Smd Size , Capacitorsize , Capacitor Size , Capacitor Dimesion Code , Ic Package Size Chip Size 0102, 01005 , 1005, 0201 ,tutul_k100% (1)

- EE2301 Exp 3 F08Document23 pagesEE2301 Exp 3 F08Pradeep Singh MaithaniNo ratings yet

- Multi VibratorsDocument11 pagesMulti VibratorsPallavi Kr K RNo ratings yet

- 2A Lab 4 - 2009Document9 pages2A Lab 4 - 2009tutul_kNo ratings yet

- 2A Lab 4 - 2009Document9 pages2A Lab 4 - 2009tutul_kNo ratings yet

- Report On Solar Photovoltaic TechnologiesDocument2 pagesReport On Solar Photovoltaic TechnologiesLAWRENCE KIM N. SACRISTANNo ratings yet

- 5 Allocation of Buffer Memories (BFM) 3 Installation and WiringDocument8 pages5 Allocation of Buffer Memories (BFM) 3 Installation and WiringArvind KumarNo ratings yet

- OTDR TRAINING 83 SlideDocument83 pagesOTDR TRAINING 83 SlideFerry Kurniawan80% (5)

- Boschrexroth Re29993Document4 pagesBoschrexroth Re29993Service - Anda Hydraulics Asia Pte LtdNo ratings yet

- Multiple Choice Questions and Answers On Transistor Biasing - Electronics PostDocument8 pagesMultiple Choice Questions and Answers On Transistor Biasing - Electronics PostDurga DeviNo ratings yet

- Logic Circuit & Switching Theory Pre - Final Quiz 1Document14 pagesLogic Circuit & Switching Theory Pre - Final Quiz 1Russel Mendoza100% (1)

- Two Port NetworkDocument7 pagesTwo Port NetworkAzim KhanNo ratings yet

- Linear Link™: Installation, Operation and Maintenance ManualDocument44 pagesLinear Link™: Installation, Operation and Maintenance ManualAlan Barros SallesNo ratings yet

- Interactive Schematic: This Document Is Best Viewed at A Screen Resolution of 1024 X 768Document39 pagesInteractive Schematic: This Document Is Best Viewed at A Screen Resolution of 1024 X 768Andy Sanchez GamarraNo ratings yet

- Instrument Transformer Reference Guide: Meter and Relay Applications For The Electrical IndustryDocument118 pagesInstrument Transformer Reference Guide: Meter and Relay Applications For The Electrical IndustrysdgafgafdhadNo ratings yet

- Single and Double Stub Matching Impedance With Smith ChartDocument21 pagesSingle and Double Stub Matching Impedance With Smith ChartAnima SanNo ratings yet

- Sony HCD-GNZ55D Service Manual v1.1Document100 pagesSony HCD-GNZ55D Service Manual v1.1Alver Tuiza75% (4)

- Metrum PQ Controller DB System 4page Eng R24 WebbDocument4 pagesMetrum PQ Controller DB System 4page Eng R24 WebbRAJESH KUMARNo ratings yet

- Gear Tooth Speed Sensor GS1001 GS1002 Datasheet 1075695Document3 pagesGear Tooth Speed Sensor GS1001 GS1002 Datasheet 1075695Sigit RomadhonNo ratings yet

- Frequency MeterDocument5 pagesFrequency MeterNh Chuminda YapaNo ratings yet

- Ug Zs1 Iom Man - en (Dong Abb)Document129 pagesUg Zs1 Iom Man - en (Dong Abb)Văn NguyễnNo ratings yet

- Dynamic Voltage and Frequency Scaling The Laws ofDocument6 pagesDynamic Voltage and Frequency Scaling The Laws ofQurat AnnieNo ratings yet

- WEG EPC Solar PresentationDocument31 pagesWEG EPC Solar PresentationHADJENE NoussaibaNo ratings yet

- Notice AXT25TC BoschDocument14 pagesNotice AXT25TC BoschPatrice GervoisNo ratings yet

- Wi-Fi Module and Solarpower App User'S ManualDocument16 pagesWi-Fi Module and Solarpower App User'S ManualOmegaNet BgNo ratings yet

- Ixan0010 PDFDocument26 pagesIxan0010 PDFBenito Rivera EdmundoNo ratings yet

- Control SystemsDocument25 pagesControl Systemskakaka12No ratings yet

- 5990 6347en PDFDocument17 pages5990 6347en PDFRekha YadavNo ratings yet

- Abeba DebruDocument90 pagesAbeba Debruabera alemayehuNo ratings yet

- Syllabus of Física de Semiconductores CourseDocument7 pagesSyllabus of Física de Semiconductores CourseJuanSebastianTovareNo ratings yet

- D3 Electronic Block DiagramDocument1 pageD3 Electronic Block DiagramjoseNo ratings yet

- Tutorial For Automated Design System (ADS) : You Chung Chung Cynthia FurseDocument23 pagesTutorial For Automated Design System (ADS) : You Chung Chung Cynthia Fursehassan abousalehNo ratings yet

- GSM Frame StructureDocument3 pagesGSM Frame StructureNoman SarwarNo ratings yet

- WPS 2Document41 pagesWPS 2Armin PatelNo ratings yet

- Amateur Band PlanDocument19 pagesAmateur Band PlandeanNo ratings yet