Professional Documents

Culture Documents

Coa Dec 2002

Uploaded by

api-3782519Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Coa Dec 2002

Uploaded by

api-3782519Copyright:

Available Formats

(4)

53

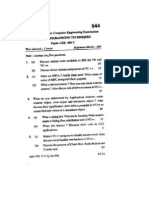

B. E. (Computer Science Engg.) Vth Semester

Examination, December-2002

COMPUTER ORGANISATION

Paper-CSE-303 C

9

8. Time allowed: 3 hours Maximum Marks: 100

(a) Discuss advantages of interleaved memory. 6 Explain

(b) . writing operation in associative memory. 6 A virtual

1. (a) Draw a combinational circuit that accepts a 3-bit number

(c) memory has a page size of 1 K words. There are 8 and generates an alp binary number equal to square of

pages and 4 blocks. The associative memory page table

ilp number. 8

contains:

(b) Implement following boolean fn. with NAND gates.

Make a list of all virtual addresses (in decimal) that Use inverters to complement ilps.

will cause a page fault if used by CPU. 8

F (x, y, z) = L (0, 2, 4, 5). 7

Block -..

Page

o 3

1 1

4 2

6 o

(c) JK flip flop can be converted to a D~ flip flop. True or

not? Justify.' 5

2. (a) Draw a block diagram for add micro-operation when

implemented in a serial computer.

Include two shift registers, one full-adder and a

flip flop to store the carry. Assume that initially carry

flip flop is cleared. 10

(b) Show that an n-bit binary counter connected to an

""~ -.-- .. - ~

7_--.- ... ~~"':~~ ..

-~~~- '~-~,:":."'~;~--:"::::::~_';-,<,:'~,7.~";;;;-.;"-~ -:;..;"..;;~;:.,:;-<:.-::-.::.:::..~;:.

,-=~~. ---~..;:;;~

(2) (3)

3. (a) Show how a 9-bit miclO operation field in a (%+C*D) +G.

microinstruction ,can be divided into subfields to 10.

x= C)

specify 46 micro-operations. How many micro- (D*E-F+ A

operations can be specified in one microinstruction?

7 6. (a) Draw a flow chart for addition and subtraction of

, (b) A microprogram control unit contains 1024 words of floating point numbers and explain,

100 bits each. If only 120 different bit combinations 10

(b) Explain the algorithm of BCD addition and

..••.

are used, how many bits can be saved by using a subtraction.

nanomemory ? What would be size of micromemory 10

7. (a) 'Define the following memory device characteristics:

and nanomemory ? 7

(c) Under what conditions would it be more feasible to use (i) Access Time

a hard-wired control than a microprogrammed control (ii) Access mode

unit? 6

(iii) Cycle time

4. (a) Explain the interrupt cycle through a flow chart. 10 (b)

(iv) Alterability. 1

What is Von-NeumannModel and stored program 0

principle ? 10 (b) The access time of a Cache memory is 100 ns and that

of main memory 1000 ns. It is estimated that 80% of

5. (a) What is addressing mode? Explain the following types of

the memory requests are for read and remaining 20%

addressing modes :

for write. The hit ratio for read accesses only is 0.9 . A

(i) Immediate

write through procedure is used.

(ii) Register indirect

(iii) Relative addressing mode.

<.0)'" 'W~~~~.p~f'''"'-·

-

:lTfl :llllllU:ll;')(1 'nnr T nnnr == /\'1 ST?q l~Trrrdnm nv

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Data Lake For HadoopDocument12 pagesData Lake For Hadoopg17_ram100% (2)

- Introduction To Compiler Design - SolutionsDocument23 pagesIntroduction To Compiler Design - Solutionsmonroe1010% (1)

- Next Generation NetworkDocument3 pagesNext Generation NetworkmusharafNo ratings yet

- Mtech1stsem SyllabusDocument4 pagesMtech1stsem Syllabusapi-3782519No ratings yet

- Discrete Struc Dec 2002Document2 pagesDiscrete Struc Dec 2002api-3782519No ratings yet

- MCA SyllabusDocument54 pagesMCA Syllabusapi-3782519100% (3)

- Discrete Struc May 2004Document2 pagesDiscrete Struc May 2004api-3782519No ratings yet

- BCA SyllabusDocument55 pagesBCA Syllabusapi-378251973% (11)

- MCA SyllabusDocument3 pagesMCA Syllabusapi-3782519100% (4)

- Mtech3rdsem SyllabusDocument3 pagesMtech3rdsem Syllabusapi-3782519No ratings yet

- BBA SyllabusDocument81 pagesBBA Syllabusapi-3782519100% (11)

- BDocument120 pagesBapi-3782519100% (3)

- APGDCA SyllabusDocument1 pageAPGDCA Syllabusapi-3782519No ratings yet

- Mca SyllabusDocument24 pagesMca Syllabusapi-3782519No ratings yet

- MBA SyllabusDocument4 pagesMBA Syllabusapi-3782519100% (1)

- M SC - SyllabusDocument2 pagesM SC - Syllabusapi-3782519No ratings yet

- BE IST YEAR COMMON-syllabusDocument34 pagesBE IST YEAR COMMON-syllabusapi-3782519No ratings yet

- B.tech It SyllabusDocument102 pagesB.tech It Syllabusapi-3782519100% (2)

- BCA SyllabusDocument3 pagesBCA Syllabusapi-3782519100% (2)

- B.tech Cse SyllabusDocument121 pagesB.tech Cse Syllabusapi-3782519100% (20)

- System ProgrammingDocument2 pagesSystem Programmingapi-3782519No ratings yet

- Visual Programming Techniques1Document2 pagesVisual Programming Techniques1api-3782519No ratings yet

- Theory of ComputeationDocument2 pagesTheory of Computeationapi-3782519No ratings yet

- Visual Prog Techniques1Document2 pagesVisual Prog Techniques1api-3782519No ratings yet

- Visual Programming TechniquesDocument2 pagesVisual Programming Techniquesapi-3782519No ratings yet

- TH of ComputationDocument2 pagesTH of Computationapi-3782519No ratings yet

- Theory of Automata and ComputationDocument2 pagesTheory of Automata and Computationapi-3782519No ratings yet

- Sys Prog Dec 2002Document2 pagesSys Prog Dec 2002api-3782519100% (1)

- Software Engg 3Document3 pagesSoftware Engg 3api-3782519No ratings yet

- TH of Computation Dec 2002Document3 pagesTH of Computation Dec 2002api-3782519No ratings yet

- Software Engg2Document2 pagesSoftware Engg2api-3782519No ratings yet

- Software EnggDocument1 pageSoftware Enggapi-3782519No ratings yet

- Software Engg1Document3 pagesSoftware Engg1api-3782519No ratings yet

- Orbit MCR Release Notes Rev AL - 9.2.2Document8 pagesOrbit MCR Release Notes Rev AL - 9.2.2David José Barrios ItriagoNo ratings yet

- System Requirement For Window Media ServerDocument11 pagesSystem Requirement For Window Media Serverสุรกิจ เวโรจน์No ratings yet

- EXAMPLE FS Functional - Specification - Payment Instruction - Payment Instruction AcknowledgementDocument16 pagesEXAMPLE FS Functional - Specification - Payment Instruction - Payment Instruction AcknowledgementJose Luis Becerril BurgosNo ratings yet

- Manny Marroquin EQ: WavesDocument13 pagesManny Marroquin EQ: WavesChris FunkNo ratings yet

- Lecture 2Document43 pagesLecture 2Alhussain DarbiNo ratings yet

- Alvarion'S Bmax Vision: Bawug Wimax Seminar Aug 5, 2004 Dr. Mo ShakouriDocument29 pagesAlvarion'S Bmax Vision: Bawug Wimax Seminar Aug 5, 2004 Dr. Mo ShakourirobolstadNo ratings yet

- ECC500 (PowerCube) User Manual (V300R001C01 - 03)Document137 pagesECC500 (PowerCube) User Manual (V300R001C01 - 03)Nguyen Minh Thanh50% (2)

- HASP Communication Problems With Sentinel License ManagersDocument2 pagesHASP Communication Problems With Sentinel License ManagersRicardo Andres Morales MuñozNo ratings yet

- DWM Unit2Document65 pagesDWM Unit2Hansica MadurkarNo ratings yet

- TCP/UDP Client-Server Practical GuideDocument67 pagesTCP/UDP Client-Server Practical GuidePrasad KokateNo ratings yet

- CE 204 Computer Programming Class SessionalDocument39 pagesCE 204 Computer Programming Class SessionalAhmedArefinNo ratings yet

- PythonDocument19 pagesPythonPrashant PailaNo ratings yet

- Fsfewfewfw PDFDocument4,214 pagesFsfewfewfw PDFAnonymous 27ljovUNo ratings yet

- Portfolio P9 Erika OrtegaDocument23 pagesPortfolio P9 Erika OrtegaErikaOrtegaNo ratings yet

- Guía de Actividades y Rúbrica de Evaluación - Tarea 1 - El Concepto de IntegralDocument46 pagesGuía de Actividades y Rúbrica de Evaluación - Tarea 1 - El Concepto de IntegralDany Fernando RodriguezNo ratings yet

- Practical File: Parallel ComputingDocument34 pagesPractical File: Parallel ComputingGAMING WITH DEAD PANNo ratings yet

- Design Patterns: Strategy PatternDocument11 pagesDesign Patterns: Strategy PatternilijakljNo ratings yet

- Illustrated Course Guide Microsoft Office 365 and Access 2016 Intermediate Spiral Bound Version 1st Edition Friedrichsen Test BankDocument24 pagesIllustrated Course Guide Microsoft Office 365 and Access 2016 Intermediate Spiral Bound Version 1st Edition Friedrichsen Test Bankfizzexponeo04xv0100% (25)

- MITRASTAR DSL-2401HNA-T1CC-2016-08-24 DatasheetDocument2 pagesMITRASTAR DSL-2401HNA-T1CC-2016-08-24 DatasheetCarlosNo ratings yet

- Folleto Ampliadora DigitalDocument4 pagesFolleto Ampliadora DigitalraulNo ratings yet

- ErrorDocument3 pagesErrorNangNo ratings yet

- RAC login device connection error logDocument2 pagesRAC login device connection error logVictoria Marie Mccarty0% (1)

- ADTRAN - CenturyLink 2014 Roadshow Mark RichmondDocument80 pagesADTRAN - CenturyLink 2014 Roadshow Mark Richmondaarnulfo100% (1)

- 8-Bit PIC® MCU Bootloader Code Generator: A Simple Way To Add Remote Update Capability To Your ApplicationDocument2 pages8-Bit PIC® MCU Bootloader Code Generator: A Simple Way To Add Remote Update Capability To Your ApplicationTonis KuikNo ratings yet

- Build Mobile Apps With Ionic 2 and Firebase: Printed BookDocument1 pageBuild Mobile Apps With Ionic 2 and Firebase: Printed BookSGNo ratings yet

- Huawei: H13-811 - V3.0 ExamDocument112 pagesHuawei: H13-811 - V3.0 Examia.2023i.epicsNo ratings yet

- TSM Courses Content First BatchDocument9 pagesTSM Courses Content First BatchKiran Kumar PeteruNo ratings yet