Professional Documents

Culture Documents

A Framework For The Design of High Speed Fir Filters On Fpgas

Uploaded by

amit1411narkhedeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Framework For The Design of High Speed Fir Filters On Fpgas

Uploaded by

amit1411narkhedeCopyright:

Available Formats

A FRAMEWORK FOR THE DESIGN OF HIGH SPEED FIR FILTERS ON FPGAS

Satish Mohanakrishnan and Joseph B. Evans Telecommunications & Information Sciences Laboratory Department of Electrical Engineering & Computer Science University of Kansas Lawrence, KS 66045-2228

This paper discusses a hardware design path from lter design to high performance FPGA implementation of FIR lters using Ptolemy, a freely distributable DSP prototyping environment developed in the University of California at Berkeley. The previously available hardware design path was either one of code generation for Digital Signal Processors or VHDL generation, which is currently in the developmental stages. Sythesis tools which map VHDL to FPGA rarely result in a high performance implementation. We demonstrate the ability to use Ptolemy to design a lter,simulate it and implement it on Xilinx XC3195 series of FPGAs. The target specic details of implementation are exported to the synchronous dataow (SDF) domain for accurate simulation. Several target independent and target dependent techniques are used to achieve a high performance mapping onto FPGAs. A VHDL model of the placed and routed logic cell array (LCA) is generated and simulated using VHDL simulators. 1. INTRODUCTION Low densities in the current generation FPGAs allow only limited DSP functionality such as digital lters to be supported [3, 4, 5, 6, 10]. Hence, there is a need for a framework for design and simulation of complete systems incorporating FPGAbased DSP functions. This work focuses on demonstrating such a framework for implementing high speed FIR lters on Xilinx XC3100 series FPGAs. The framework chosen is Ptolemy [12], a freely distributable, block-oriented prototyping environment developed in the University of California at Berkeley. In Ptolemy, signal processing algorithms are developed in the synchronous dataow domain. Blocks in the standard library and custom-coded blocks are used to build a DSP system. Depending on the target architecture, C or VHDL code generation domains can be used. The problem discussed here is the implementation of an FIR lter on an FPGA which can be a part of a DSP system. In the previously available design path, a custom-coded block is written in SDF, which simulates the behaviour of the lter, without taking the implementation details into account. A VHDL model of the lter is written and added to the VHDL library which describes the functionality. Synthesis tools are then used to map the lter onto the FPGA or any other architecture. As the synthesis tools are designed to be general purpose, they fail to yield a high performance FPGA mapping. Similar reasoning applies to the placement and route tools. Hence, an implementation based on application specic logic partitioning and placement is needed to yield high performance. A hardware design path which results in high performance is illustrated in Figure 1. Here the custom-coded block takes the implementation details into account in the synchronous dataow domain itself. This is possible because the target architecture has

This research is partially supported by the Kansas Technology Enterprise Corporation through the Center for Excellence in Computer-Aided Systems Engineering.

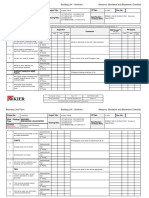

Filter Design

Target specific simulation in SDF

High performance logic partitioning and placement generation of netlist using C++ libraries

Simulate design for functional verification (VHDL generation)

Placement with user constraints and Routing (use Xilinx tools - xnfmap, map2lca, apr)

Extract delay parameters of routed design (use Xilinx tool lca2xnf)

Resimulate for timing verification (generate VHDL with routing delays)

Generate Configuration (use Xilinx tool makebits)

Program the FPGA (use Xilinx tool Xchecker)

Test

Figure 1. High performance hardware design path

X3

C 3 S3

X2

C 2 S2

X1

C1 S1

X0

C 0 S0

FA

FA

FA

FA

FA

FA

FA

FA

Figure 3. Main Window of the Filter Design Package

D D D D D D D D

X3 C 3

S3

X2 C2

S2

X1 C1

S1

X0 C 0

S0

Figure 2. Structure of the lter tap already been identied and the user utilizes his knowledge of the architecture and that of the support tools to partition and place the logic in a manner which results in high performance. 2. BACKGROUND

A methodology and CAD tool to implement high speed, multiplier-less FIR lters on XC3195 have been discussed previously [4, 5, 10]. The lter design consists of generation of a oating point coefcient set which is then optimized in the powerof-two coefcient space. The coefcients are constrained to be a sum or difference of two power-of-two terms. It has been shown that an FIR lter with -60dB of frequency response ripple magnitude can be realized using two power-of-two terms for each coefcient value using the appropriate optimization techniques [8]. The structure of a lter tap is shown in Figure 2. As the coefcients are split into two power-of-two terms, it requires two full adder stages to implement the carry save addition. The input data lines are routed to the corresponding full adders. The nal adder stage, which is needed to resolve the carries, is not implemented in the XC3000 series as it is not cost effective, but it can be done in the XC4000 series. 3. HARDWARE DESIGN PATH

Figure 4. Dialog box for entry of frequency specications

3.1. Filter Design There are two lter design packages in Ptolemy namely, optr and windowr. In addition to these two, another package MILP3 [7] is included in our extended version. Given the lter specications, MILP3 generates lter coefcients and optimizes them in the power-of-two coefcient space. The MILP3 can be invoked by using the pop-up menus in Ptolemy. A Motif interface, as shown in Figure 3, can be used to design the lter using MILP3, implement it on FPGAs, and edit the logic cell array (LCA). The frequency specications of the lter can be input as shown in Figure 4. 3.2. Simulation in the SynchronousData Flow (SDF) domain In Ptolemy, all xed point representations use the data type Fix in the Ptolemy kernel. Carry save addition, the arithmetic which is used in this FPGA implementation at present, is not supported by the Fix data type. To support this, member functions which

Figure 5. Specication of Implementation parameters in SDF

Figure 6. Block diagram to determine the frequency response of the lter perform bitwise operations on the Fix objects, such as bitwise logical AND and bitwise logical exclusive OR were added. A custom-coded block was written in the Ptolemy language (.pl), which represents the xed point FIR lter as shown in Figure 2. The full adders are realized using the bitwise operations. The parameters of the block, such as the number of input bits, coefcient bits, intermediate bits and output bits can be specied as shown in Figure 5. Depending on the number of bits, one can select the size of the FPGA. This block can be used along with other blocks from the Ptolemy library either to determine the lter characteristics or to build a DSP system. Figure 6 shows the interconnection of blocks to determine the frequency response of the lter. 3.3. High performance mapping onto FPGA In the FPGA design ow, the stage where the mapping onto FPGA architecture is performed, is very critical. User controlled logic partitioning and placement as opposed to using general synthesis tools is the key to achieving high performance. Libraries were developed in C++, which allow any digital design to be captured in terms of Xilinx CLB (Congurable Logic Block) and IOB (Input Output Block) primitives. Thus the design entry consists of writing C++ code, specifying partitioned and placed logic. The Xilinx Netlist Format le is automatically generated. 3.3.1. Logic Partitioning and Placement The basic block for this implementation is a full adder which ts in a CLB. The input data lines are shifted according to the coefcients and routed to the corresponding CLBs. The sign of coefcients is controlled by the logic inside the CLB. The mapping of a full adder to a CLB constitutes logic partitioning. The CLBs are pre-placed and only routing is done by the Xilinx APR (Automatic Placement and Route) tool. 3.3.2. Efcient Utilization of Routing Resources Inefcient use of routing resources manifests itself as unrouted pins or increased net delays. The structure of the lter tap is so designed that it reduces congestion in any channel and makes efcient use of the limited routing resources [10, 5]. These techniques are general and not restricted to the XC3100 series of FPGAs. Multiplication by a signed power-of-two term, as mentioned earlier, involves a shift and an optional inversion. The Low and High signals which are used in the least signicant bits during this operation, utilize a considerable amount of routing resources. These were absorbed into the combinatorial logic of the CLBs without increasing the CLB delay as it is independent of the functionality. This technique resulted in a signicant increase in speed. 3.3.3. Knowledge of Support Tools Though nets can be marked as critical and longline, the APR program does not permit the user to specify the exact assignment of longlines. Hence, we resort to making a rough estimate of APRs longline assignment and then buffering the nets close to their respective longlines. The estimate based on the average number of shifts required by the power-of-two terms has been

Figure 7. Layout of the rst of the two chips empirically found to produce good results. This technique reduced a considerable amount of routing delay. 3.3.4. Multiple Chips A single XC3195 chip can accomodate 10 to 11 taps. Using this CAD tool, higher order lters can be implemented as a cascade of chips. Due to the inherent pipelining and parallelism in the design, the speed is independent of the number of taps. In a multichip implementation, the outputs of one chip are fed as inputs to the next chip. Hence, in subsequent chips, there is an increased utilization of CLBs, I/O blocks and routing resources. Hence only 10 taps can be implemented in the subsequent chips whereas 11 taps can be implemented in the rst chip. The increased utilization of routing resources is shown in Figures 7 and 8. A 21 tap, linear phase, low-pass FIR lter with stop band from 0 to 0.1 fs , pass band from 0.15 fs to 0.5 fs and stop band rejection of 27 dB, was designed and implemented using this system on two XC3195s. The maximum clock speeds achieved were 46.2 MHz for the rst chip and 48.5 MHz for the second chip. Hence, the maximum sampling rate is 46.2 MHz. The user can also specify pin constraints which are very useful when there is an existing PCB. Again, the pin assignments do not have a bearing on the sampling rate as the input data lines are

4. CONCLUSION A high performance hardware design path for implementing high speed FIR lters using Ptolemy was dened and demonstrated. The target specic details are exported to the SDF domain for simulation. Enhancements to the xed point data type in the Ptolemy kernel were done to perform the SDF simulation. Libraries were written to automatically generate the Xilinx Netlist Format. Using these libraries for logic partitioning and placement was proved to achieve high speed. Libraries were written to generate VHDL model for Xilinx Chips for functional simulation and back annotation. This framework thus supports the design and simulation of complete systems incorporating FPGA-based FIR lters. REFERENCES [1] P. K. Chan and S. Mourad. Digital Design Using Field Programmable Gate Arrays. Prentice-Hall, Inc., 1994. [2] S. C. Chan, H. O. Ngai, and K. L. Ho. A programmable image processing system using FPGA. In IEEE Int. Symp. Circuits and Syst., pages 2.1252.128, May 1994. [3] C. J. Chou, S. Mohanakrishnan, and J. B. Evans. FPGA implementation of digital lters. In Proc. Int. Conf. Sig. Proc., Applcn. and Technology, pages 8088, 1993. [4] J. B. Evans. An efcient FIR lter architecture. In IEEE Int. Symp. Circuits and Syst., pages 627630, May 1993. [5] J. B. Evans. Efcient FIR lter architectures suitable for FPGA implementation. IEEE Trans. Circuits and Syst., July 1994. [6] R. D. Hack. Designing digital lters using eld programmable gate arrays. In Proc. Int. Conf. Sig. Proc.,Applcn. and Technology, pages 435438, 1993. [7] Y. C. Lim. MILP3 Manual. National University of Singapore, 1988. [8] Y. C. Lim and B. Liu. Design of cascade form FIR lters with discrete valued coefcients. IEEE Trans. Acoust., Speech, Signal Processing, ASSP-36:17351739, Nov 1988. [9] Y. C. Lim and S. R. Parker. FIR lter designed over a discrete power-of-two coefcient space. IEEE Trans. Acoust., Speech, Signal Processing, ASSP-31:583591, June 1983. [10] S. Mohanakrishnan and J. B. Evans. Automatic implementation of FIR lters on eld programmable gate arrays. Under review, IEEE Signal Processing Letters. [11] A. Oppenheim and R. Schafer. Digital Signal Processing. Prentice-Hall, Inc., 1975. [12] University of California at Berkeley. Ptolemy 0.5 Manuals, 1994. Volumes 1-4. [13] Xilinx Incorporated, San Jose, California. XACT Reference Guide, 1992. [14] Xilinx Incorporated, San Jose, California. The Programmable Gate Array Data Book, 1993.

Figure 8. Layout of the second of the two chips buffered near their respective long lines. 3.4. Functional Simulation The next step in the design process is to verify the functionality of the netlist which is created. Libraries were developed in C++ to generate VHDL models for functional simulation. The models for the CLBs and IOBs use the exact delays as given in the Xilinx data book [14], but the net delays are assumed to be zero. The VHDL code is at present simulated using commercial simulators, due to the unavailability of public domain versions. 3.5. Placement and Route With the logic partitioning done as above,the traditional automatic placement of CLBs takes an exhorbitant amount of time and the quality of placement is far from satisfactory. For the lter example considered, the placement took several hours on a SPARC 2 and the speed achieved was only 25 MHz. In this design ow, placement is already done when specifying the netlist and the Xilinx APR (Automatic Placement and Route) tool is used to perform the routing only. Routing typically takes a few minutes per chip. Speeds over 45 MHz were consistently achieved for several typical lters. Xilinx tools such as xnfmap, map2lca, and APR are used to generate the routed logic cell array (LCA). 3.6. Back Annotation The routing delay dominates in any FPGA design due to the numerous switching matrices and programmable interconnect points (PIP) through which the signal traverses. Hence in all FPGA designs, back annotation is essential to get an exact timing simulation. Using the Xilinx tool lca2xnf, the timing annotated .xnf le is generated which gives the net delays. A parser was written in yacc for creating the C++ objects from the XNF le. These net delays are incorporated into the VHDL models for timing simulation.

You might also like

- InterconnectsDocument6 pagesInterconnectsachuu1987No ratings yet

- C 789Document18 pagesC 789Ác QủyNo ratings yet

- Efficient Implementation of Scan Register Insertion On Integer Arithmetic Cores For FpgasDocument6 pagesEfficient Implementation of Scan Register Insertion On Integer Arithmetic Cores For FpgasAbhishek JoarderNo ratings yet

- FPGA Design Flow: Page 1 of 5Document6 pagesFPGA Design Flow: Page 1 of 5PRAVEEN034No ratings yet

- FPGA Advantages and ApplicationsDocument4 pagesFPGA Advantages and ApplicationsTushar GuptaNo ratings yet

- Synplicity Efficient DSPDocument8 pagesSynplicity Efficient DSPravindarsinghNo ratings yet

- FIR FilterDocument5 pagesFIR FilterManasa UpadhyayaNo ratings yet

- XC Sysgen43Document3 pagesXC Sysgen43YogeeshHtNo ratings yet

- An Introduction To How FPGA Programming WorksDocument12 pagesAn Introduction To How FPGA Programming WorksjackNo ratings yet

- MainPaper PallabDocument6 pagesMainPaper PallabkaoutarNo ratings yet

- Design of Arithmetic Calculator Using FpgaDocument58 pagesDesign of Arithmetic Calculator Using FpgavikramNo ratings yet

- Design of Embedded ProcessorsDocument80 pagesDesign of Embedded ProcessorsSayan Kumar KhanNo ratings yet

- Thesis VHDL PDFDocument6 pagesThesis VHDL PDFmarybrownarlington100% (2)

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- Reconfigurable FPGA Implementation of Digital Communication SystemDocument17 pagesReconfigurable FPGA Implementation of Digital Communication Systemsudha_804331380No ratings yet

- 8.programmable Asic Design SoftwareDocument21 pages8.programmable Asic Design Softwaresalinsweety50% (2)

- Vlsi ManualDocument110 pagesVlsi ManualSam Joel.DNo ratings yet

- Jimaging 05 00016Document22 pagesJimaging 05 00016vn7196No ratings yet

- FPGA Implementation of FIR Filters Using Pipelined Bit-Serial CSD MultipliersDocument34 pagesFPGA Implementation of FIR Filters Using Pipelined Bit-Serial CSD MultipliersSARATH MOHANDASNo ratings yet

- Design and Implementation of Traffic Controller Using VHDL: Interim Project ReportDocument21 pagesDesign and Implementation of Traffic Controller Using VHDL: Interim Project ReportAugusto Germano da SilvaNo ratings yet

- Implementation of Uart Using Systemc and Fpga Based Co-Design MethodologyDocument7 pagesImplementation of Uart Using Systemc and Fpga Based Co-Design MethodologyRakeshconclaveNo ratings yet

- Abstract:: Figure 1: Basic FPGA ConfigurationDocument4 pagesAbstract:: Figure 1: Basic FPGA ConfigurationEr Nayan PithadiyaNo ratings yet

- A VHDL Design Methodology For FpgasDocument16 pagesA VHDL Design Methodology For FpgasØla SültånNo ratings yet

- Master Thesis FpgaDocument5 pagesMaster Thesis Fpgatashahollowaylittlerock100% (1)

- White Paper Designing High-Performance DSP Hardware Using Catapult C Synthesis and The Altera Accelerated LibrariesDocument9 pagesWhite Paper Designing High-Performance DSP Hardware Using Catapult C Synthesis and The Altera Accelerated Librarieszahid52No ratings yet

- Fpga Based 32 Bit Risc Processor DesignDocument18 pagesFpga Based 32 Bit Risc Processor DesignAchit YadavNo ratings yet

- Design and Simulation of Mathematical Models Using Mixed HDL PlatformDocument11 pagesDesign and Simulation of Mathematical Models Using Mixed HDL PlatformInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- VHDL TutorialDocument127 pagesVHDL TutorialDeepanker KumeriaNo ratings yet

- Lecture Notes - Introduction To Accumulators and Fpgas: Accumulator BasicsDocument6 pagesLecture Notes - Introduction To Accumulators and Fpgas: Accumulator BasicsWaqar AzeemNo ratings yet

- Vlsi Design FlowDocument7 pagesVlsi Design FlowAster RevNo ratings yet

- FPGA Vs ASICDocument9 pagesFPGA Vs ASICKamleshNo ratings yet

- Efficient Design Using Fpgas: of Application Specific CoresDocument5 pagesEfficient Design Using Fpgas: of Application Specific CoresK.GurucharanNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- FPGA Implementation of a Fast Hadamard Transformer for WCDMADocument12 pagesFPGA Implementation of a Fast Hadamard Transformer for WCDMAOussama BoulfousNo ratings yet

- Fpga TutorialDocument10 pagesFpga Tutorialgsavithri_4017No ratings yet

- Digital Filters in Programmable Logic DevicesDocument13 pagesDigital Filters in Programmable Logic DevicesJoerg MenkeNo ratings yet

- Definition:: Field-Programmable Gate ArrayDocument6 pagesDefinition:: Field-Programmable Gate ArrayyaduyadavendraNo ratings yet

- Programmable Logic Arrays (PLA) ExplainedDocument5 pagesProgrammable Logic Arrays (PLA) ExplainedSitotaw NigussieNo ratings yet

- Comparison of HDL Coder and System Generator Tools in Terms of QPSK AnalysisDocument6 pagesComparison of HDL Coder and System Generator Tools in Terms of QPSK AnalysisAli H. NumanNo ratings yet

- Fir Compiler XilinxDocument85 pagesFir Compiler Xilinxalisadan_92No ratings yet

- VHDL Modeling and Synthesis in The Laboratory: Session 2647Document12 pagesVHDL Modeling and Synthesis in The Laboratory: Session 2647Красимир КостадиновNo ratings yet

- Fpga IntroDocument10 pagesFpga IntroJpradha KamalNo ratings yet

- Low Power ASIC Implementation From A CAL Dataflow DescriptionDocument15 pagesLow Power ASIC Implementation From A CAL Dataflow DescriptionMohan RajNo ratings yet

- Fpgas and DSP: Design Alternatives For DSP SolutionsDocument8 pagesFpgas and DSP: Design Alternatives For DSP Solutionsnguyendinh126No ratings yet

- Chameleon ChipDocument21 pagesChameleon Chip429by3100% (1)

- Project Report On Traffic Signal System Using FPGADocument10 pagesProject Report On Traffic Signal System Using FPGAanuragdhar dwivediNo ratings yet

- Cascaded Multilevel InvertersDocument6 pagesCascaded Multilevel InvertersMinhaj NaimNo ratings yet

- Implementation of Digital Clock On FPGA: Industrial Training Report ONDocument26 pagesImplementation of Digital Clock On FPGA: Industrial Training Report ONAdeel HashmiNo ratings yet

- Thesis Fpga ImplementationDocument6 pagesThesis Fpga Implementationjessicabriggsomaha100% (2)

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- Fpga Introduction 20190626aDocument26 pagesFpga Introduction 20190626atulasiNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document6 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- Evaluation of Power Efficient Adder and Multiplier Circuits for FPGA Based DSP ApplicationsDocument5 pagesEvaluation of Power Efficient Adder and Multiplier Circuits for FPGA Based DSP ApplicationsharithNo ratings yet

- Fpga Design FlowDocument3 pagesFpga Design FlowShaik IliyasNo ratings yet

- Smart Card:: Smart Cards-What Are They?Document12 pagesSmart Card:: Smart Cards-What Are They?infernobibekNo ratings yet

- Chapter 1Document39 pagesChapter 1Kalyan Reddy AnuguNo ratings yet

- Why Con Gurable Computing? The Computational Density Advantage of Con Gurable ArchitecturesDocument17 pagesWhy Con Gurable Computing? The Computational Density Advantage of Con Gurable ArchitecturesHari KrishnaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Improving Combat Efficiency of Army Engineers with MB 3 Bridge BoatDocument4 pagesImproving Combat Efficiency of Army Engineers with MB 3 Bridge BoatAnonymous sfkedkymNo ratings yet

- 8051 Memory Map PDFDocument6 pages8051 Memory Map PDFCh'ng ShufenNo ratings yet

- MEP Coordination - SE SponsorshipDocument42 pagesMEP Coordination - SE SponsorshipmoosuhaibNo ratings yet

- Semiosis and Intersemiotic Translation - Mouton-LibreDocument10 pagesSemiosis and Intersemiotic Translation - Mouton-LibreIsadora RodriguesNo ratings yet

- Checklist-Masonry - Brickwork and BlockworkDocument6 pagesChecklist-Masonry - Brickwork and Blockworkapi-372251810No ratings yet

- How To Prepare The SarDocument107 pagesHow To Prepare The Sargoldencomet100% (1)

- Myntra SRS Software RequirementsDocument19 pagesMyntra SRS Software RequirementsAravindNo ratings yet

- Hy14-3300 Mvi PDFDocument3 pagesHy14-3300 Mvi PDFPartsGopher.comNo ratings yet

- RC Chapter 8Document14 pagesRC Chapter 8ianiroy130% (1)

- Truck-Mounted Concrete Pump BSF 20-4.09 HDocument2 pagesTruck-Mounted Concrete Pump BSF 20-4.09 HAhmed BERRAHMANo ratings yet

- 4N35 OptocouplersDocument7 pages4N35 OptocouplersattapapaNo ratings yet

- Venus solar and heat pump water heaters guideDocument18 pagesVenus solar and heat pump water heaters guideajeet ranaNo ratings yet

- Shear Wall Design and BehaviorDocument34 pagesShear Wall Design and BehaviorRacharla Narasimha Raju Varma100% (1)

- MAHINDRADocument75 pagesMAHINDRAranjan80das80% (5)

- Operating System Assignment 4-Dos CommandsDocument7 pagesOperating System Assignment 4-Dos CommandsJayashree WawhalNo ratings yet

- Regulador 57 PDFDocument12 pagesRegulador 57 PDFJose Ines Mosqueda AguayoNo ratings yet

- Tube-To-tubesheet Joints - ASME (Mechanical) Code Issues - Eng-TipsDocument4 pagesTube-To-tubesheet Joints - ASME (Mechanical) Code Issues - Eng-Tipsagniva dattaNo ratings yet

- MS PowerPoint Views, Transitions, and Animations ExplainedDocument2 pagesMS PowerPoint Views, Transitions, and Animations Explainedaliwaqas48797No ratings yet

- ECligner V2 Quick Manual enDocument18 pagesECligner V2 Quick Manual enDao - Ngoc LamNo ratings yet

- AMD Assignment-6Document12 pagesAMD Assignment-6Arijit Das100% (1)

- Irc 11 1962Document14 pagesIrc 11 1962LokeshNo ratings yet

- Wawb Im20190924eDocument172 pagesWawb Im20190924eHumberto CervantesNo ratings yet

- HCC/HCF4042B: Quad Clocked "D" LatchDocument13 pagesHCC/HCF4042B: Quad Clocked "D" LatchjuenkkinNo ratings yet

- PVK Pump Features SummaryDocument99 pagesPVK Pump Features SummarySebastiao DuarteNo ratings yet

- Schematic Diagram For Model 2216: All VersionsDocument1 pageSchematic Diagram For Model 2216: All VersionsZa RacsoNo ratings yet

- Module 5: Fabrication Methods Photolithography: Raja SellappanDocument24 pagesModule 5: Fabrication Methods Photolithography: Raja SellappanAbhiramNo ratings yet

- Power Semiconductor Devices ThyristorsDocument140 pagesPower Semiconductor Devices ThyristorsNomanNo ratings yet

- Proposal To Conduct An Industry Centric Hackathon by Forum For Innovation Incubation Research and Entrepreneurship (Fiire) Program SummaryDocument3 pagesProposal To Conduct An Industry Centric Hackathon by Forum For Innovation Incubation Research and Entrepreneurship (Fiire) Program SummaryVenugopal T RNo ratings yet

- 13 07 2023 Nandhu Shiri Bill 1Document3 pages13 07 2023 Nandhu Shiri Bill 1Mana RashhiNo ratings yet

- Procedure ITP Austenitic SS Rev.0.3Document13 pagesProcedure ITP Austenitic SS Rev.0.3Ferdie OSNo ratings yet