Professional Documents

Culture Documents

VHDL Command Summary

Uploaded by

diego_tmOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL Command Summary

Uploaded by

diego_tmCopyright:

Available Formats

VHDL Command Summary

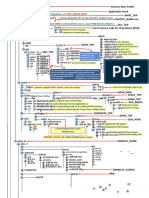

Concurrent Statements

block_statement

label: block [(guard_expression)] [generic] [ports] [declarations] begin concurrent_statements end block [label];

component_instantiation_statement

label : name [ generic map (map) ] [ port map (signals) ];

concurrent_assertion_statement

assert condition [ report string_expression ] [ severity {NOTE | WARNING | ERROR | FAILURE} ];

concurrent_procedure_call

[ label : ] procedure_name [ (parameters) ];

concurrent_signal_assignment_statement

[ label : ] [ {conditional_assignment | assignment | selected_assignment} ];

generate_statement

label : [{ for specification | if condition }] generate concurrent_statements end generate [label];

process_statement

[label : ] process [ (sensitivity_list) ] [ variable_declaration ] [ type_declaration ] [subprogram_declaration ] [ declarations ] begin sequential_statements -- Cannot contain a wait statement if sensitivity_list is used end process [ label ];

Sequential Statements

assertion_statement

assert condition -- When condition is false [strng_expression] is printed [ report string_expression ] [severity { NOTE | WARNING | ERROR | FAILURE } ];

case_statement

case expression is -- Avoid the use of parenthesis, if possible when choices_1 => sequential_statements . . when choices_n => sequential_statements end case;

exit_statement

exit [ label ] [ when condition ];

if_statement

if condition then sequential_statements { elsif condition then sequential_statements } [ else sequential_statements ] end if;

loop_statement

[ label : ] [ while condition | for loop_specification ] loop sequential_statements end loop [ label ] ;

next_statement

next [ label ] [ when condition ];

null_statement

null;

procedure_call_statement

procedure_name [ (parameters) ] ;

return_statement

return expression; --For use in a Function return; --For use in a Procedure

signal_assignment_statement

target <= expression [ after time_expression ] . . { , expression [ after time_expression ];

variable_assignment_statement

target := expression ;

wait_statement

wait --A Function may not contain a wait_statement [ on signal_name {, signal_name} ] [ until conditional_expression ] [ for time_expression ] ;

Specifications

attribute_specification

attribute attribute_name of entity_name is expression ;

configuration_specifications

for component_name use [ generic_map_part ] [port_map_part] ;

Library & Use Clause

library_clause

LIBRARY names ;

use_clause

USE selected_names ;

Declarations

alias_declaration

alias name1 : type [ (indexes) ] is name2 [ (indexes) ] ;

attribute_declaration

attribute name : type ;

component_declaration

component identifier : [ generic (generic_list) ; ] [ port (port_list) ; ] end component ;

constant_declaration

constant name : type := expression ; constant name : array_type [ (indexes) ] := expression ;

file_declaration

file name : type is [ mode ] logical_name ;

signal_declaration

signal names : type [ constraint ] [ := expression ] ;

port_declaration

port ( names : direction type [ := expression ] [ ; more_signals ] );

subprogram_declaration

{ procedure name [ (parameters) ] | function name [ (parameters) ] return type; }

sub_program_body

is declarations begin

sequential_declarations end [name] ;

subtype_declaration

subtype name is [ resolution_function] type [constraint] ;

type_declaration

type name is definition;

variable_declaration

variable names : type [ constraint ] [ := expression ] ;

Library Units

architecture_body

architecture name of entity_name is [types] [constants] [signals] [subprograms] [other declarations] begin concurrent_statements end [name];

configuration_declaration

configuration name of entity_name is declarative_part block_configuration end [name];

entity_declaration

entity name is [generics] [ports] [declarations] [begin statements] --typically, an entity does not have statements. If it does, the statemnts cannot operate on signals end name;

package_body

package body name is [subprogram] [type] [constant [signal] [declarations] end [name];

package_declaration

package name is [subprogram] [type] [constant] [signal] [file] [alias] [USE clause] [declarations] end [name];

You might also like

- Coding Standards: UI/Business/Data Layer StandardsDocument7 pagesCoding Standards: UI/Business/Data Layer StandardsRam BobbaNo ratings yet

- React Hooks: Cheat SheetsDocument13 pagesReact Hooks: Cheat Sheetssuraj satav100% (1)

- Oracle R12 Full MapDocument3 pagesOracle R12 Full MapSalim ChérifNo ratings yet

- Basic Data: Consent of Otis GMBHDocument30 pagesBasic Data: Consent of Otis GMBHRafael Bruno100% (5)

- C++ ReferenceDocument2 pagesC++ ReferenceAlessio BianchettiNo ratings yet

- AADL Syntax CardDocument2 pagesAADL Syntax CardRobin Alan CressentNo ratings yet

- Oracle PL-SQL Training Document PDFDocument76 pagesOracle PL-SQL Training Document PDFRodrigo TelesNo ratings yet

- React Hooks: Cheat SheetsDocument36 pagesReact Hooks: Cheat SheetsnambimunnaNo ratings yet

- Systemverilog Quick ReferenceDocument3 pagesSystemverilog Quick Referencesabare100% (2)

- Oracle 9I PL/SQL: by System ConsultantDocument141 pagesOracle 9I PL/SQL: by System ConsultantJaswanth KumarNo ratings yet

- ExceptionDocument188 pagesExceptionAzhar MullaNo ratings yet

- Design and Verification of Router 1x3 Using UVMDocument4 pagesDesign and Verification of Router 1x3 Using UVMShasha Bhanu100% (2)

- Limits and Continuity Worksheet PDFDocument9 pagesLimits and Continuity Worksheet PDFknlsinhaNo ratings yet

- Document Number Rev. Document Title Number: Click On The Document Title To Go To That Section of The DocumentDocument244 pagesDocument Number Rev. Document Title Number: Click On The Document Title To Go To That Section of The DocumentmahaveenNo ratings yet

- PLSQL NotesDocument78 pagesPLSQL NotesRaghavendra PrabhuNo ratings yet

- PLSQL Course WareDocument135 pagesPLSQL Course Warenaga5825No ratings yet

- PLSQLDocument196 pagesPLSQLanugula ramNo ratings yet

- Stored ProceduresDocument6 pagesStored ProceduresSantosh KamalNo ratings yet

- Scan Path DesignDocument54 pagesScan Path DesignaguohaqdoNo ratings yet

- Coding GuidelinesDocument2 pagesCoding GuidelinesSapan DoshiNo ratings yet

- Advanced SQL: Stored Procedures: Instructor: Mohamed Eltabakh Meltabakh@cs - Wpi.eduDocument23 pagesAdvanced SQL: Stored Procedures: Instructor: Mohamed Eltabakh Meltabakh@cs - Wpi.edusanaNo ratings yet

- Stored ProceduresDocument19 pagesStored ProceduresSathyamurthy DuraikkannuNo ratings yet

- CSTM ToolDocument2 pagesCSTM ToolMohammed NasirNo ratings yet

- Logger Log - Time: Create PL/SQL Package Procedure and Function: - Table To Wok With ProcedureDocument4 pagesLogger Log - Time: Create PL/SQL Package Procedure and Function: - Table To Wok With ProcedureSarfaraz AhmedNo ratings yet

- Cli RBQLDocument8 pagesCli RBQLLuis MuchakiNo ratings yet

- MGMT Ebs LL MetricsDocument29 pagesMGMT Ebs LL Metricsanon-58026No ratings yet

- Card VHDL PDFDocument2 pagesCard VHDL PDFgiri_placidNo ratings yet

- VHDL SummaryDocument10 pagesVHDL SummaryKatia BitamNo ratings yet

- Bluespec Systemverilog Reference Card: ItalicDocument3 pagesBluespec Systemverilog Reference Card: ItalicManojNo ratings yet

- Bluespec Systemverilog Reference Card: ItalicDocument3 pagesBluespec Systemverilog Reference Card: ItalicManojNo ratings yet

- Notation of Algorithm and C++ Programming LanguageDocument16 pagesNotation of Algorithm and C++ Programming LanguageMangaras Yanu FlorestiyantoNo ratings yet

- ConfigDocument3 pagesConfigReniel De Villa EstanislaoNo ratings yet

- DBMS Stored Function, Cursor & TriggerDocument10 pagesDBMS Stored Function, Cursor & TriggerAustinNo ratings yet

- SQL Objects and PLSQLDocument32 pagesSQL Objects and PLSQLpavanreddy16No ratings yet

- VHDL Cookbook 3Document6 pagesVHDL Cookbook 3Charbel TadrosNo ratings yet

- ConfigDocument3 pagesConfigtaiiq zhouNo ratings yet

- Xilinx Vivado Quick Reference GuideDocument2 pagesXilinx Vivado Quick Reference GuideNikhil P GowdaNo ratings yet

- Alinhar TEdit A Direita-AndersonDocument2 pagesAlinhar TEdit A Direita-AndersonmarciorossettiNo ratings yet

- Log4j Using SpringDocument9 pagesLog4j Using SpringJagan NemmojuNo ratings yet

- 02 5 Functions and ProceduresDocument7 pages02 5 Functions and ProceduresSusan AliceNo ratings yet

- PL SQL NotesDocument159 pagesPL SQL NotespgrittechnologiesNo ratings yet

- React CheatsheetDocument14 pagesReact Cheatsheetking fisherNo ratings yet

- React 1690266470Document14 pagesReact 1690266470HatdogNo ratings yet

- Stored Procedures: What Is A Stored Procedure?Document5 pagesStored Procedures: What Is A Stored Procedure?ppavandsNo ratings yet

- Summary of Basic Java Syntax: 1 Primitive TypesDocument6 pagesSummary of Basic Java Syntax: 1 Primitive TypesAarifaBegumNo ratings yet

- 13 Sub ProgramsDocument17 pages13 Sub Programsapi-3827483No ratings yet

- Mysql ProceduresDocument22 pagesMysql ProceduresHamisi NhabayuNo ratings yet

- 8th SeminarDocument5 pages8th SeminarRobert BaciuNo ratings yet

- CL Gui AlvDocument35 pagesCL Gui Alvrvigrag8805No ratings yet

- Standard Serial Driver Description: Linux 2.6 KernelDocument14 pagesStandard Serial Driver Description: Linux 2.6 KernelHenk BoshoffNo ratings yet

- Asset and LoggingDocument8 pagesAsset and Loggingvinayagam bNo ratings yet

- Log 4 Net OverviewDocument8 pagesLog 4 Net Overviewcall_vipvipin725No ratings yet

- Stored ProcedureDocument23 pagesStored ProcedureSri LestariNo ratings yet

- Part 2Document15 pagesPart 2Nguyễn Thanh PhátNo ratings yet

- Android Project GuidelinesDocument13 pagesAndroid Project GuidelinesKalash DkalashNo ratings yet

- Emsuix EcfDocument3 pagesEmsuix EcfKluKlux LandNo ratings yet

- Storage ClassesDocument16 pagesStorage ClassesAkhilesh WunaNo ratings yet

- CIS 103 Study GuideDocument13 pagesCIS 103 Study GuideguidodiorNo ratings yet

- CnotesDocument2 pagesCnotesshaheda AktharNo ratings yet

- Java Programming Tutorial With Screen Shots & Many Code ExampleFrom EverandJava Programming Tutorial With Screen Shots & Many Code ExampleNo ratings yet

- Ra DevelopmentDocument39 pagesRa DevelopmentRasik WankhedeNo ratings yet

- Empowerment Technologies - STEM - Part 1Document66 pagesEmpowerment Technologies - STEM - Part 1Ritchie FegsarNo ratings yet

- Chap 3: Fuzzy Rules and Fuzzy ReasoningDocument28 pagesChap 3: Fuzzy Rules and Fuzzy Reasoningsaye_sNo ratings yet

- BIT 2109 Integrative Programming and TechnologiesDocument4 pagesBIT 2109 Integrative Programming and TechnologiesHerwin CapiñanesNo ratings yet

- Message StructuresDocument42 pagesMessage StructureskodandaNo ratings yet

- Land Surveying Chapter 2 Leveling p2Document60 pagesLand Surveying Chapter 2 Leveling p2Azrul ZulwaliNo ratings yet

- Archmodels 06Document5 pagesArchmodels 06Ahmed SamiNo ratings yet

- Blogging Using Wordpress: Empowerment TechnologiesDocument80 pagesBlogging Using Wordpress: Empowerment Technologiesmenchu galdonesNo ratings yet

- Isa s88Document2 pagesIsa s88Sd Weds DsNo ratings yet

- Rehabilitation For The Postsurgical Orthopedic Patient PDFDocument2 pagesRehabilitation For The Postsurgical Orthopedic Patient PDFManuel Duran100% (1)

- How Can You Find Out Which Process Is Listening On A Port On WindowsDocument8 pagesHow Can You Find Out Which Process Is Listening On A Port On WindowsMartaSekulicNo ratings yet

- Brandon L. Lenoir: Murfreesboro, TN 37127 CELL PHONE: 615-987-5689Document3 pagesBrandon L. Lenoir: Murfreesboro, TN 37127 CELL PHONE: 615-987-5689Brandon LenoirNo ratings yet

- CS8451-Design and Analysis of Algorithms PDFDocument18 pagesCS8451-Design and Analysis of Algorithms PDFkathirpkNo ratings yet

- Job Description - BIM Coordinator: Key Requirements & ResponsibilitiesDocument1 pageJob Description - BIM Coordinator: Key Requirements & ResponsibilitiesAbdalla.JNo ratings yet

- Blue Eyes TechnologyDocument39 pagesBlue Eyes TechnologyRaktim RoyNo ratings yet

- A e Specification Pro Network Video Recorder Dhi-Nvr5416 5432 5464-16p-4ks2 v001 001Document7 pagesA e Specification Pro Network Video Recorder Dhi-Nvr5416 5432 5464-16p-4ks2 v001 001Saeed JavaidNo ratings yet

- Physical Accessibility: Student AccommodationsDocument3 pagesPhysical Accessibility: Student Accommodationsyasir muhammadNo ratings yet

- GEO1007 - Geoweb Technology - Lab 8Document9 pagesGEO1007 - Geoweb Technology - Lab 8Chirag GargNo ratings yet

- WWW Personal Kent Edu Rmuhamma Algorithms MyAlgorithms SortDocument20 pagesWWW Personal Kent Edu Rmuhamma Algorithms MyAlgorithms SortAhmad Imran Rafique100% (1)

- Database Systems: University of GujratDocument15 pagesDatabase Systems: University of GujratAbdul MananNo ratings yet

- Manually Install or Upgrade VMware Tools in A Linux Virtual Machine PDFDocument2 pagesManually Install or Upgrade VMware Tools in A Linux Virtual Machine PDFOmar FigoNo ratings yet

- MSP430 DLL Developer's GuideDocument30 pagesMSP430 DLL Developer's Guideiky77No ratings yet

- Lesson 1 Introduction To CATIA ProgrammingDocument8 pagesLesson 1 Introduction To CATIA Programmingmilasko86No ratings yet

- Exida IEC 61508 Overview ReportDocument12 pagesExida IEC 61508 Overview ReportEmmanu MakembaNo ratings yet

- Anti ForensicsDocument44 pagesAnti ForensicsOdilon Regina Luiza100% (1)