Professional Documents

Culture Documents

Tl082 Datasheet

Uploaded by

Adit LalOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tl082 Datasheet

Uploaded by

Adit LalCopyright:

Available Formats

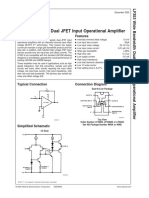

TL082 Wide Bandwidth Dual JFET Input Operational Amplifier

April 1998

TL082 Wide Bandwidth Dual JFET Input Operational Amplifier

General Description

These devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The TL082 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and most LM358 designs. These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The devices also exhibit low noise and offset voltage drift.

Features

n n n n n n n n n Internally trimmed offset voltage: 15 mV Low input bias current: 50 pA Low input noise voltage: 16nV/Hz Low input noise current: 0.01 pA/Hz Wide gain bandwidth: 4 MHz High slew rate: 13 V/s Low supply current: 3.6 mA High input impedance: 1012 Low total harmonic distortion AV = 10,: < 0.02% RL = 10k, VO = 20 Vp p, BW = 20 Hz20 kHz n Low 1/f noise corner: 50 Hz n Fast settling time to 0.01%: 2 s

Typical Connection

Connection Diagram

DIP/SO Package (Top View)

DS008357-3 DS008357-1

Order Number TL082CM or TL082CP See NS Package Number M08A or N08E

Simplified Schematic

DS008357-2

BI-FET II is a trademark of National Semiconductor Corp.

1999 National Semiconductor Corporation

DS008357

www.national.com

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Supply Voltage Power Dissipation Operating Temperature Range Tj(MAX) Differential Input Voltage

18V (Note 2) 0C to +70C 150C 30V

(Note 5)

Input Voltage Range (Note 3) Output Short Circuit Duration Storage Temperature Range Lead Temp. (Soldering, 10 seconds) ESD rating to be determined.

15V Continuous 65C to +150C 260C

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

DC Electrical Characteristics

Symbol VOS VOS/T IOS IB RIN AVOL Parameter Input Offset Voltage Average TC of Input Offset Voltage Input Offset Current Input Bias Current Input Resistance Large Signal Voltage Gain

Conditions Min RS = 10 k, TA = 25C Over Temperature RS = 10 k Tj = 25C, (Notes 5, 6) Tj 70C Tj = 25C, (Notes 5, 6) Tj 70C Tj = 25C VS = 15V, TA = 25C VO = 10V, RL = 2 k Over Temperature VS = 15V, RL = 10 k VS = 15V RS 10 k (Note 7) 25 15

TL082C Typ 5 10 25 50 1012 100 200 4 400 8 Max 15 20

Units mV mV V/C pA nA pA nA V/mV V/mV

VO VCM CMRR PSRR IS

Output Voltage Swing Input Common-Mode Voltage Range Common-Mode Rejection Ratio Supply Voltage Rejection Ratio Supply Current

12 11

70 70

13.5

+15 12 100 100 3.6 5.6

V V V dB dB mA

AC Electrical Characteristics

Symbol Parameter Amplifier to Amplifier Coupling SR GBW en in Slew Rate Gain Bandwidth Product Equivalent Input Noise Voltage Equivalent Input Noise Current

(Note 5) Conditions Min TA = 25C, f = 1Hz20 kHz (Input Referred) VS = 15V, TA = 25C VS = 15V, TA = 25C TA = 25C, RS = 100, f = 1000 Hz Tj = 25C, f = 1000 Hz 8 TL082C Typ 120 13 4 25 0.01 Max dB V/s MHz nV/Hz pA/Hz Units

Note 2: For operating at elevated temperature, the device must be derated based on a thermal resistance of 115C/W junction to ambient for the N package. Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage. Note 4: The power dissipation limit, however, cannot be exceeded. Note 5: These specifications apply for VS = 15V and 0C TA +70C. VOS, IB and IOS are measured at VCM = 0. Note 6: The input bias currents are junction leakage currents which approximately double for every 10C increase in the junction temperature, Tj. Due to the limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, PD. Tj = TA + jA PD where jA is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum. Note 7: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice. VS = 6V to 15V.

www.national.com

Typical Performance Characteristics

Input Bias Current Input Bias Current Supply Current

DS008357-18

DS008357-19

DS008357-20

Positive Common-Mode Input Voltage Limit

Negative Common-Mode Input Voltage Limit

Positive Current Limit

DS008357-23 DS008357-21 DS008357-22

Negative Current Limit

Voltage Swing

Output Voltage Swing

DS008357-24

DS008357-25

DS008357-26

www.national.com

Typical Performance Characteristics

Gain Bandwidth Bode Plot

(Continued) Slew Rate

DS008357-27

DS008357-28

DS008357-29

Distortion vs Frequency

Undistorted Output Voltage Swing

Open Loop Frequency Response

DS008357-30 DS008357-31 DS008357-32

Common-Mode Rejection Ratio

Power Supply Rejection Ratio

Equivalent Input Noise Voltage

DS008357-33

DS008357-34 DS008357-35

www.national.com

Typical Performance Characteristics

Open Loop Voltage Gain (V/V)

(Continued) Inverter Setting Time

Output Impedance

DS008357-37 DS008357-36

DS008357-38

Pulse Response

Small Signal Inverting Small Signal Non-Inverting

DS008357-6

DS008357-7

Large Signal Inverting

Large Signal Non-Inverting

DS008357-8

DS008357-9

www.national.com

Pulse Response

(Continued) Current Limit (RL = 100)

DS008357-10

Application Hints

These devices are op amps with an internally trimmed input offset voltage and JFET input devices (BI-FET II). These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore, large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit. Exceeding the negative common-mode limit on either input will cause a reversal of the phase to the output and force the amplifier output to the corresponding high or low state. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode. Exceeding the positive common-mode limit on a single input will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state. The amplifiers will operate with a common-mode input voltage equal to the positive supply; however, the gain bandwidth and slew rate may be decreased in this condition. When the negative common-mode voltage swings to within 3V of the negative supply, an increase in input offset voltage may occur. Each amplifier is individually biased by a zener reference which allows normal circuit operation on 6V power supplies. Supply voltages less than these may result in lower gain bandwidth and slew rate.

The amplifiers will drive a 2 k load resistance to 10V over the full temperature range of 0C to +70C. If the amplifier is forced to drive heavier load currents, however, an increase in input offset voltage may occur on the negative voltage swing and finally reach an active current limit on both positive and negative swings. Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit. Because these amplifiers are JFET rather than MOSFET input op amps they do not require special handling. As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize pick-up and maximize the frequency of the feedback pole by minimizing the capacitance from the input to ground. A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feedback pole is less than approximately 6 times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

www.national.com

Detailed Schematic

DS008357-11

Typical Applications

Three-Band Active Tone Control

DS008357-12

www.national.com

Typical Applications

(Continued)

DS008357-13

All potentiometers are linear taper Use the LF347 Quad for stereo applications

Note 8: All controls flat. Note 9: Bass and treble boost, mid flat. Note 10: Bass and treble cut, mid flat. Note 11: Mid boost, bass and treble flat. Note 12: Mid cut, bass and treble flat.

Improved CMRR Instrumentation Amplifier

DS008357-14

C and E are separate isolated grounds Matching of R2s, R4s and R5s control CMRR With AVT = 1400, resistor matching = 0.01%: CMRR = 136 dB Very high input impedance Super high CMRR

www.national.com

Typical Applications

(Continued) Fourth Order Low Pass Butterworth Filter

DS008357-15

Fourth Order High Pass Butterworth Filter

DS008357-16

www.national.com

Typical Applications

(Continued) Ohms to Volts Converter

DS008357-17

www.national.com

10

Physical Dimensions

inches (millimeters) unless otherwise noted

Order Number TL082CM NS Package M08A

Order Number TL082CP NS Package N08E

11

www.national.com

TL082 Wide Bandwidth Dual JFET Input Operational Amplifier

Notes

LIFE SUPPORT POLICY NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

National Semiconductor Corporation Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com www.national.com National Semiconductor Europe Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Franais Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com

National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

You might also like

- TL082 EqualizerDocument16 pagesTL082 EqualizerMecabot DzibNo ratings yet

- tl082cp DatasheetDocument15 pagestl082cp DatasheetHeriberto Flores AmpieNo ratings yet

- Datasheet LF 353Document14 pagesDatasheet LF 353Anggridho MeilandanuNo ratings yet

- tl082 Op Amp DatasheetDocument23 pagestl082 Op Amp DatasheetnurburgNo ratings yet

- TL081Document9 pagesTL081Vero PorrasNo ratings yet

- LF353Document13 pagesLF353cromus_9000No ratings yet

- OpAmp - LF451Document8 pagesOpAmp - LF451Ludwig SchmidtNo ratings yet

- Datasheet LF412CNDocument14 pagesDatasheet LF412CNJose Fernando Perdomo BolañosNo ratings yet

- LF351 Wide Bandwidth JFET Input Operational Amplifier Spec SheetDocument11 pagesLF351 Wide Bandwidth JFET Input Operational Amplifier Spec SheetAndres CampoNo ratings yet

- HV7802 14068Document6 pagesHV7802 14068Djzedamendoa Jose LopesNo ratings yet

- Quad Power Amplifier For Car Radio: Protections: DescriptionDocument18 pagesQuad Power Amplifier For Car Radio: Protections: DescriptionMiloud ChouguiNo ratings yet

- INA106Document14 pagesINA106Juan Pablo RosalesNo ratings yet

- TDA7370B: Quad Power Amplifier For Car RadioDocument18 pagesTDA7370B: Quad Power Amplifier For Car RadioMiloud ChouguiNo ratings yet

- TDA7372BDocument10 pagesTDA7372BCarlos MartinezNo ratings yet

- Data SheetDocument10 pagesData SheetselocaNo ratings yet

- Pam8610 PDFDocument15 pagesPam8610 PDFRaka Satria PradanaNo ratings yet

- 1A Step-Down LED Driver Data SheetDocument12 pages1A Step-Down LED Driver Data SheetselocaNo ratings yet

- LM324 OpampDocument9 pagesLM324 OpampYuvarajaNo ratings yet

- LM 1875Document13 pagesLM 1875pblhnrqNo ratings yet

- Exelente Amplificador de 100w TDA7294Document17 pagesExelente Amplificador de 100w TDA7294Everson CorreaNo ratings yet

- LF347n PDFDocument13 pagesLF347n PDFDiego PeñuelaNo ratings yet

- PT1301Document9 pagesPT1301dcastrelos2000No ratings yet

- LM392Document6 pagesLM392Brzata PticaNo ratings yet

- High Efficiency 2A Step Down ConverterDocument9 pagesHigh Efficiency 2A Step Down Converterbob75No ratings yet

- LM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesDocument22 pagesLM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesselocaNo ratings yet

- Low Voltage Audio Power AmplifierDocument9 pagesLow Voltage Audio Power AmplifierJuan V Castro SotoNo ratings yet

- lm386 PDFDocument11 pageslm386 PDFNicolás MoraNo ratings yet

- 28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionDocument11 pages28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionbaczonifNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- LMC6034 CMOS Quad Operational Amplifier: General DescriptionDocument13 pagesLMC6034 CMOS Quad Operational Amplifier: General DescriptionPeter JordanNo ratings yet

- 700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolDocument6 pages700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolNathan WilliamsNo ratings yet

- TDA7294Document18 pagesTDA7294frank121212No ratings yet

- LF442Document14 pagesLF442atavachronNo ratings yet

- High Efficiency Low-Side N-Channel Controller For Switching RegulatorsDocument33 pagesHigh Efficiency Low-Side N-Channel Controller For Switching Regulatorssoft4gsmNo ratings yet

- LF155Document24 pagesLF155Brzata PticaNo ratings yet

- Boost Controller With Power Factor CorrectionDocument14 pagesBoost Controller With Power Factor CorrectionChiseledPrawnNo ratings yet

- Datasheet TDA2052Document14 pagesDatasheet TDA2052FrancoilNo ratings yet

- LF442CNDocument13 pagesLF442CNFSNo ratings yet

- Tda7294 DatasheetDocument17 pagesTda7294 DatasheetTecmicro GonzalezNo ratings yet

- LM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorDocument22 pagesLM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorVinoth Kumar RajendranNo ratings yet

- TE CH: Features General DescriptionDocument10 pagesTE CH: Features General DescriptionJuan VillanuevaNo ratings yet

- Description: Green-Power PWM Controller With Freq. JigglingDocument8 pagesDescription: Green-Power PWM Controller With Freq. JigglingLuis GuevaraNo ratings yet

- Unisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational AmplifierDocument5 pagesUnisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational Amplifiergaldos08No ratings yet

- LM148/LM248/LM348 Quad 741 Op Amps: General DescriptionDocument4 pagesLM148/LM248/LM348 Quad 741 Op Amps: General DescriptionJunedy Pandapotan SaragihNo ratings yet

- High Performance Video Op AmpDocument16 pagesHigh Performance Video Op Ampsrboghe651665No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Symetrix Solutions: Tech Tip: Transient Suppressor DSP ModuleDocument1 pageSymetrix Solutions: Tech Tip: Transient Suppressor DSP ModuleJess AJNo ratings yet

- Et Series Solid State Toasters: Standard Features ModelsDocument2 pagesEt Series Solid State Toasters: Standard Features ModelsJess AJNo ratings yet

- Hamilton Beach 22810 ToasterDocument24 pagesHamilton Beach 22810 ToasterJess AJNo ratings yet

- 511.79 Nvidia Control Panel Quick Start GuideDocument28 pages511.79 Nvidia Control Panel Quick Start GuideMusik BaratNo ratings yet

- Bottom Freezer Refrigerator: Refrigerador Con Congelador InferiorDocument92 pagesBottom Freezer Refrigerator: Refrigerador Con Congelador InferiorJess AJNo ratings yet

- Dpa-300s - 600S - 900S - 1200S - Service - 1401 2Document86 pagesDpa-300s - 600S - 900S - 1200S - Service - 1401 2ЕвгенийNo ratings yet

- Shopjimmy T Con Board Samsung Bn96 42319aDocument1 pageShopjimmy T Con Board Samsung Bn96 42319aJess AJNo ratings yet

- 70VMultizoneSingleAmpAudioSystem 251Document1 page70VMultizoneSingleAmpAudioSystem 251Jess AJNo ratings yet

- T3 PINBALL sb145 PDFDocument1 pageT3 PINBALL sb145 PDFJess AJNo ratings yet

- Terminator3 Manual PDFDocument218 pagesTerminator3 Manual PDFJess AJNo ratings yet

- AMD-V Hyper-V EULA - FinalDocument4 pagesAMD-V Hyper-V EULA - FinalsumodiningratNo ratings yet

- T3 PINBALL sb140 PDFDocument1 pageT3 PINBALL sb140 PDFJess AJNo ratings yet

- VP 100 Users Manual PDFDocument8 pagesVP 100 Users Manual PDFJess AJNo ratings yet

- TSPP Manual PDFDocument216 pagesTSPP Manual PDFJess AJNo ratings yet

- TT2000 Ticket Eater MANUAL WITH BJ 100 LOGIC PCB PDFDocument31 pagesTT2000 Ticket Eater MANUAL WITH BJ 100 LOGIC PCB PDFJess AJNo ratings yet

- TS PP PINBALL sb138 PDFDocument1 pageTS PP PINBALL sb138 PDFJess AJNo ratings yet

- T3 PINBALL sb142 PDFDocument1 pageT3 PINBALL sb142 PDFJess AJNo ratings yet

- Drift Upgrade BrochureDocument1 pageDrift Upgrade BrochureJess AJNo ratings yet

- T3 PINBALL sb143 PDFDocument1 pageT3 PINBALL sb143 PDFJess AJNo ratings yet

- 32LP1D Service ManualDocument1 page32LP1D Service ManualJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- Datasheet 2SD2627Document4 pagesDatasheet 2SD2627Jess AJNo ratings yet

- LG LCD TV 42lp1d Service ManualDocument52 pagesLG LCD TV 42lp1d Service ManualDamiaoNo ratings yet

- Max 17105Document26 pagesMax 17105Jess AJNo ratings yet

- Irfib7N50A: Smps MosfetDocument8 pagesIrfib7N50A: Smps MosfetJess AJNo ratings yet

- P6NA60FP DatasheetDocument5 pagesP6NA60FP DatasheetJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- Drift Conversion ManualDocument32 pagesDrift Conversion ManualJess AJNo ratings yet

- Drift Conversion BrochureDocument1 pageDrift Conversion BrochureJess AJNo ratings yet

- Ashlok Safe Earthing Electrode LimitedDocument28 pagesAshlok Safe Earthing Electrode LimitedSugumaranNo ratings yet

- Portable Generators and OSHA Construction Standards 3-05Document7 pagesPortable Generators and OSHA Construction Standards 3-05canslayyNo ratings yet

- Power Factor CorrectionDocument48 pagesPower Factor Correctionskaarz86% (7)

- Repair Manual For Universal Machine Power Supply (UMPS) (P/No 220010) Doc. No. 957-001 Revision A02Document14 pagesRepair Manual For Universal Machine Power Supply (UMPS) (P/No 220010) Doc. No. 957-001 Revision A02German ParceroNo ratings yet

- FCRO2100 Product GuideDocument2 pagesFCRO2100 Product GuideChenaker HamzaNo ratings yet

- Trj608e Manual - Eng 07302020-M Final PDFDocument16 pagesTrj608e Manual - Eng 07302020-M Final PDFjNo ratings yet

- Technical Performance and Stability Anal PDFDocument178 pagesTechnical Performance and Stability Anal PDFMeD1kNo ratings yet

- GA Drawing Pondasi Tower SUTT 150 KV Tarjun - Revisi 26 November 2021Document8 pagesGA Drawing Pondasi Tower SUTT 150 KV Tarjun - Revisi 26 November 2021Faizal SetiawanNo ratings yet

- Igt Door Optic BypassDocument1 pageIgt Door Optic BypassJohn SmithNo ratings yet

- Hits Lab ManualDocument25 pagesHits Lab ManualOMR XEROXNo ratings yet

- Monarch-10EE-Operators Manual 1940s PDFDocument49 pagesMonarch-10EE-Operators Manual 1940s PDFdd100% (1)

- SMAF5.0A Thru Smaf220A: Surface Mount Transient Voltage Suppressor Power 200 WattsDocument5 pagesSMAF5.0A Thru Smaf220A: Surface Mount Transient Voltage Suppressor Power 200 WattsMohammed SairawanNo ratings yet

- LC1Kpp - Improve Motor Starting Safety with Schneider Electric Overload RelaysDocument1 pageLC1Kpp - Improve Motor Starting Safety with Schneider Electric Overload RelaysRafael CarmoNo ratings yet

- ABB Surge Arrester POLIM-H SD - Data Sheet 1HC0075860 E02 ABDocument4 pagesABB Surge Arrester POLIM-H SD - Data Sheet 1HC0075860 E02 ABHan HuangNo ratings yet

- OLY Battery Charger TroubleshootingDocument3 pagesOLY Battery Charger TroubleshootingJavier MorontaNo ratings yet

- Principles of Electronic Engineering : DR - Eng. Eslam Samy EL-MokademDocument20 pagesPrinciples of Electronic Engineering : DR - Eng. Eslam Samy EL-Mokademmacaruois samehNo ratings yet

- ACI Detailing Manual-2004: Reported by ACI Committee 315Document1 pageACI Detailing Manual-2004: Reported by ACI Committee 315vacamia2No ratings yet

- SMPS and amplifier schematic diagramDocument12 pagesSMPS and amplifier schematic diagramValentin NichiforNo ratings yet

- PhoenixContact-Current Voltage Transcd MCR-SDocument13 pagesPhoenixContact-Current Voltage Transcd MCR-SSusanto PausinugrohoNo ratings yet

- 4 EcDocument13 pages4 EcayushmanaNo ratings yet

- What Is Distribution System? Define: Feeder, Distributor, Service MainDocument20 pagesWhat Is Distribution System? Define: Feeder, Distributor, Service MainSERDROGOUS AKANDAHOUSNo ratings yet

- Line Surge Arresters For Increased System ReliabilityDocument2 pagesLine Surge Arresters For Increased System ReliabilitymustafaNo ratings yet

- G-Enex Battery Replacement - QRTG0005Document6 pagesG-Enex Battery Replacement - QRTG0005rafaNo ratings yet

- 5” Ceiling Fire Loudspeaker with Dome - FG-SP5R_APDocument2 pages5” Ceiling Fire Loudspeaker with Dome - FG-SP5R_APbaddar bedarNo ratings yet

- Operating Instructions Air Conditioner: Model No. Indoor Unit Outdoor UnitDocument20 pagesOperating Instructions Air Conditioner: Model No. Indoor Unit Outdoor UnitjorgeNo ratings yet

- ATV320 IS Option Module Adapter NVE22661 02Document2 pagesATV320 IS Option Module Adapter NVE22661 02Jefferson PachecoNo ratings yet

- Electrical Drive and Control SystemsDocument18 pagesElectrical Drive and Control SystemsNasreddine SiaghNo ratings yet

- DSASW0071941Document68 pagesDSASW0071941ali mohammedNo ratings yet

- 11kV Switchgear SchemesDocument17 pages11kV Switchgear SchemesEdciel EbuenNo ratings yet

- Linear Systems Reintroduces LSK389Document2 pagesLinear Systems Reintroduces LSK389attapapaNo ratings yet