Professional Documents

Culture Documents

Microprocessor BC 0046

Uploaded by

ubuntu_linuxOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microprocessor BC 0046

Uploaded by

ubuntu_linuxCopyright:

Available Formats

1BC0046 – Microprocessor

February 2011

Bachelor of Computer Application (BCA) –

Semester 3 BC0046 –

Microprocessor – 4 Credits

(Book ID: B0807)

Assignment Set – 1

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

2BC0046 – Microprocessor

1. Convert the decimal number 321.145 to octal and

hexadecimal.

Ans. 125 / 8^2 = 1

125 − ((8^2)*1) = 61

61 / 8^1 = 7

61 − ((8^1)*7) = 5

Therefore, 12510 = 1758.

321.145 = 321/8^

2. Write an assembly language program to find the smallest

among two numbers.

Ans. Program

MVI B, 30H

MVI C, 40H

MOV A, B

CMP C

JZ EQU

JC SML

OUT PORT1

HLT

EQU: MVI A, 01H

OUT PORT1

HLT

SML: MOV A, C

OUT PORT1

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

3BC0046 – Microprocessor

HLT

OR

.model small

.stack 64

.data

n1 db 08h,02h

res db ?

.code

mov ax,@data

mov ds,ax

mov cx,02

lea si,n1

mov bl,0ffh

mine:mov al,[si]

cmp al,bl

jne loop1

jmp loop2

loop1:jnc loop2

mov bl,al

inc si

loop mine

jmp exit

loop2:inc si

loop mine

exit:mov res,bl

hlt

end

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

4BC0046 – Microprocessor

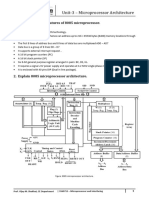

3. Draw and explain the internal architecture of 8085.

Ans.

Figure 3: Internal Architecture of 8085

8085 System Bus

Typical system uses a number of busses, collection of wires, which

transmit binary numbers, one bit per wire. A typical microprocessor

communicates with memory and other devices (input and output)

using three busses: Address Bus, Data Bus and Control Bus.

Address Bus

One wire for each bit, therefore 16 bits = 16 wires. Binary number

carried alerts memory to ‘open’ the designated box. Data (binary) can

then be put in or taken out. The Address Bus consists of 16 wires,

therefore 16 bits. Its “width” is 16 bits. A 16 bit binary number allows

216 different numbers, or 32000 different numbers, ie

0000000000000000 up to 1111111111111111. Because memory

consists of boxes, each with a unique address, the size of the address

bus determines the size of memory, which can be used. To

communicate with memory the microprocessor sends an address on

the address bus, eg 0000000000000011 (3 in decimal), to the

memory. The memory selects box number 3 for reading or writing

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

5BC0046 – Microprocessor

data. Address bus is unidirectional, i.e numbers only sent from

microprocessor to memory, not other way.

Data Bus

Data Bus: carries ‘data’, in binary form, between microprocessor and

other external units, such as memory. Typical size is 8 or 16 bits. The

Data Bus typically consists of 8 wires. Therefore, 28 combinations of

binary digits. Data bus used to transmit “data”, ie information, results

of arithmetic, etc, between memory and the microprocessor. Bus is bi-

directional. Size of the data bus determines what arithmetic can be

done. If only 8 bits wide then largest number is 11111111 (255 in

decimal). Therefore, larger number have to be broken down into

chunks of 255. This slows microprocessor. Data Bus also carries

instructions from memory to the microprocessor. Size of the bus

therefore limits the number of possible instructions to 256, each

specified by a separate number.

Control Bus

Control Bus are various lines which have specific functions for

coordinating and controlling microprocessor operations. Eg:

Read/NotWrite line, single binary digit. controls whether memory is

being ‘written to’ (data stored in mem) or ‘read from’ (data taken out

of mem) 1 = Read, 0 = Write. May also include clock line(s) for

timing/synchronising, ‘interrupts’, ‘reset’ etc. Typically microprocessor

has 10 control lines. Cannot function correctly without these vital

control signals.

CPU Architecture

Control Unit

Generates signals within microprocessor to carry out the instruction,

which has been decoded. In reality causes certain connections

between blocks of the microprocessor to be opened or closed, so that

data goes where it is required, and so that ALU operations occur.

Arithmetic Logic Unit

The ALU performs the actual numerical and logic operation such as

‘add’, ’subtract’, ‘AND’, ‘OR’, etc. Uses data from memory and from

Accumulator to perform arithmetic. Always stores result of operation in

Accumulator.

Registers

The 8085/8080A-programming model includes six registers, one

accumulator, and one flag register, as shown in Fig. 2.1 In addition, it

has two 16-bit registers: the stack pointer and the program counter.

They are described briefly as follows.

The 8085/8080A has six general-purpose registers to store 8-bit data;

these are identified as B,C,D,E,H and L as shown in the figure. They

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

6BC0046 – Microprocessor

can be combined as register pairs – BC, DE, and HL – to perform some

16-bit operations. The programmer can use these registers to store or

copy data into the registers by using data copy instructions.

Accumulator

The accumulator is an 8-bit register that is a part of arithmetic/logic

unit (ALU). This register is used to store 8-bit data and to perform

arithmetic and logical operations. The result of an operation is stored

in the accumulator. The accumulator is also identified as register A.

Temporary Register: It is used to hold the data during the arithmetic

and logical operations.

Flags

The ALU includes five flip-flops, which are set or reset after an

operation according to data conditions of the result in the accumulator

and other registers. They are called Zero(Z), Carry (CY), Sign (S), Parity

(P), and Auxiliary Carry (AC) flags. The most commonly used flags are

Zero, Carry, and Sign. The microprocessor uses these flags to test data

conditions. For example, after an addition of two numbers, if the sum

in the accumulator is larger than eight bits, the flip-flop uses to

indicate a carry — called the Carry flag (CY) – is set to one. When an

arithmetic operation results in zero, the flip-flop called the Zero(Z) flag

is set to one. The Fig. 2.1 shows an 8-bit register, called the flag

register, adjacent to the accumulator. However, it is not used as a

register; five bit positions out of eight are used to store the outputs of

the five flip-flops. The flags are stored in the 8-bit register so that the

programmer can examine these flags (data conditions) by accessing

the register through an instruction.

These flags have critical importance in the decision-making process of

the micro- processor. The conditions (set or reset) of the flags are

tested through the software instructions. For example, the instruction

JC (Jump on Carry) is implemented to change the sequence of a

program when CY flag is set. The thorough understanding of flag is

essential in writing assembly language programs.

Program Counter (PC)

This 16-bit register deals with sequencing the execution of instructions.

This register is a memory pointer. Memory locations have 16-bit

addresses, and that is why this is a 16-bit register. The microprocessor

uses this register to sequence the execution of the instructions. The

function of the program counter is to point to the memory address

from which the next byte is to be fetched. When a byte (machine code)

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

7BC0046 – Microprocessor

is being fetched, the program counter is incremented by one to point

to the next memory location

Stack Pointer (SP)

The stack pointer is also a 16-bit register used as a memory pointer. It

points to a memory location in R/W memory, called the stack. The

beginning of the stack is defined by loading 16-bit address in the stack

pointer.

Instruction Register/Decoder

Temporary store for the current instruction of a program. Latest

instruction sent here from memory prior to execution. Decoder then

takes instruction and ‘decodes’ or interprets the instruction. Decoded

instruction then passed to next stage.

Memory Address Register

Holds address, received from PC, of next program instruction. Feeds

the address bus with addresses of location of the program under

execution.

Control Generator

Generates signals within microprocessor to carry out the instruction

which has been decoded. In reality causes certain connections

between blocks of the microprocessor to be opened or closed, so that

data goes where it is required, and so that ALU operations occur.

Register Selector

This block controls the use of the register stack in the example. Just a

logic circuit which switches between different registers in the set will

receive instructions from Control Unit.

General Purpose Registers

Microprocessor requires extra registers for versatility. Can be used to

store additional data during a program. More complex processors may

have a variety of differently named registers.

Timing and Control unit:

• It has three control signals ALE, RD (Active low) and WR (Active

low) and three status signals IO/M(Active low), S0 and S1.

• ALE is used for provide control signal to synchronize the

components of microprocessor and timing for instruction to

perform the operation.

• RD (Active low) and WR (Active low) are used to indicate whether

the operation is reading the data from memory or writing the

data into memory respectively.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

8BC0046 – Microprocessor

• IO/M(Active low) is used to indicate whether the operation is

belongs to the memory or peripherals.

• If,

Interrupt Control Unit:

It receives hardware interrupt signals and sends an acknowledgement

for receiving the interrupt signal.

4. Draw and explain the internal architecture of 8086.

Ans. CPU Architecture of 8086

Figure 4 shows the internal architecture of the 8086. Except for the

instruction register, which is actually a 6-byte queue, the control unit

and working registers are divided into three groups according to their

functions. There is a data group, which is essentially the set of

arithmetic registers; the pointer group, which includes base and index

registers, but also contains the program counter and stack pointer; and

the segment group, which is a set of special purpose base registers. All

of the registers are 16 bits wide.

The data group consists of the AX, BX, CX and DX registers. These

registers can be used to store both operands and results and each of

them can be accessed as a whole, or the upper and lower bytes can be

accessed separately. For example, either the 2 bytes in BX can be used

together, or the upper byte BH or the lower byte BL can be used by

itself by specifying BH or BL, respectively.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

9BC0046 – Microprocessor

Fig 4: Internal Architecture of 8086

In addition to serving as arithmetic registers, the BX, CX and DX

registers play special addressing, counting, and I/O roles:

BX may be used as a base register in address calculations.

CX is used as an implied counter by certain instructions.

DX is used to hold the I/O address during certain I/O operations.

The pointer and index group consists of the IP, SP, BP, SI, and DI

registers. The instruction pointer IP and SP registers are essentially the

program counter and stack pointer registers, but the complete

instruction and stack addresses are formed by adding the contents of

these registers to the contents of the code segment (CS) and stack

segment (SS) registers. BP is a base register for accessing the stack

and may be used with other registers and/or a displacement that is

part of the instruction. The SI and DI registers are for indexing.

Although they may be used by themselves, they are often used with

the BX or BP registers and/or a displacement. Except for the IP, a

pointer can be used to hold an operand, but must be accessed as a

whole.

To provide flexible base addressing and indexing, a data address may

be formed by adding together a combination of the BX or BP register

contents, SI or DI register contents, and a displacement. The result of

such an address computation is called an effective address (EA) or

offset. The word “displacement” is used to indicate a quantity that is

added to the contents ‘of a register(s) to form an EA. The final data

address, however, is determined by the EA and the appropriate data

segment (DS), extra segment (ES), or stack segment (SS) register.

The segment group consists of the CS, SS, DS, and ES registers. As

indicated above, the registers that can be used for addressing, the BX,

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

10BC0046 – Microprocessor

IP, SP, BP, SI, and DI registers, are only 16 bits wide and, therefore, an

effective address has only 16 bits. On the other hand, the address put

on the address bus, called the physical address, must contain 20 bits.

The extra 4 bits are obtained by adding the effective address to the

contents of one of the segment registers as shown in Fig. 4.1. The

addition is carried out by appending four 0 bits to the right of the

number in the segment register before the addition is made; thus a 20-

bit result is produced. As an example, if (CS) = 1234 and (IP) = 0002,

then the next instruction will be fetched from

0002 Effective address

+ 12340 beginning segment address

12342 Physical address of instruction

[It is standard notation for parentheses around an entity to mean

"contents of," e.g., (IP) means the contents of IP. Also, all addresses

are given in hexadecimal.]

Fig. 4.1 Generation of physical Address

The utilization of the segment registers essentially divide the memory

space into overlapping segments, with each segment being 64K bytes

long and beginning at a 16-byte, or paragraph, boundary, i.e.,

beginning at an address that is divisible by 16. We will hereafter refer

to the contents of a segment register as the segment address, and the

segment address multiplied by 16 as the beginning physical segment

address, or simply, the beginning segment address. An illustration of

the example above is given in Fig.4.1(a) and the overall segmentation

of memory is shown in Fig. 4.2(b).

The advantages of using segment registers are that they:

1. Allow the memory capacity to be 1 MB even though the addresses

associated with the individual instructions are only 16 bits wide.

2. Allows the instruction, data, or stack portion of a program to be

more than 64K bytes long by using more than one code, data, or

stack segment.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

11BC0046 – Microprocessor

3. Facilitate the use of separate memory areas for a program, its data,

and the stack.Permit a program and/or its data to be put into

different areas of memory each time the program is executed.

Fig 4.2 Memory segmentation

The 8086’s PSW contains 16 bits, but 7 of them are not used. Each bit

in the PSW is called a flag. The 8086 flags are divided into the

conditional flags,

which reflect the result of the previous operation involving the ALU,

and the control

flags, which control the execution of special functions. The flags are

summarized in Fig. 4.3

The condition flags are:

SF (Sign FIag)-Is equal to the MSB of the result. Since in 2’s

complement negative numbers have a 1 in the MSB and for

nonnegative numbers this bit is 0, this flag indicates whether the

previous result was negative’ or nonnegative.

ZF (Zero Flag)-Is set to 1 if the result is zero and 0 if the result is

nonzero.

PF (Parity Flag)-Is set to 1 if the low-order 8 bits of the result

contains an even number of 1’s; otherwise it is cleared.

CF (Carry Flag)-An addition causes this flag to be set if there is a

carry out of the MSB, and a subtraction causes it to be set if a borrow

is needed. Other instructions also affect this flag and its value will be

discussed when these instructions are defined.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

12BC0046 – Microprocessor

AF (Auxiliary Carry Flag)-Is set if there is a carry out of bit 3 during

an addition or a borrow by bit 3 during a subtraction. This flag is used

exclusively for BCD arithmetic.

OF (Overflow Flag)-Is set if an overflow occurs, i.e., a result is out of

range. More specifically, for addition this flag is set when there is a

carry into the MSB and no carry out of the MSB or vice versa. For

subtraction, it is set when the MSB needs a borrow and there is no

borrow from the MSB or vice versa.

As an example, if the previous instruction performed the addition

0010 0011 0100 1101

+ 0011 0010 0001 0001

0101 0101 0101 1110

then following the instruction:

SF=0 ZF=0 PF=0 CF=0 AF=0 OF=0

Fig 4.3: PSW register of 8086

If the previous instruction performed the addition

0101 0100 0011 1001

+ 0100 0101 0110 1010

1001 1001 1010 0011

then the flags would be:

SF = 1 ZF = 0 PF = 1 CF = 0 AF = 1 CF = 1

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

13BC0046 – Microprocessor

The control flags are:

DF (Direction Flag)-Used by string manipulation instructions. If zero,

the string is processed from its beginning with the first element having

the lowest address. Otherwise, the string is processed from the high

address towards the low address.

IF (Interrupt Enable Flag)-If

set, a certain type of interrupt (a maskable interrupt) can be recognized by the CPU;

otherwise, these interrupts are ignored.

TF (Trap Flag)-If

set, a trap is executed after each instruction

5. Write a sequence of instructions to reverse a two digit

hexadecimal number available in the register AX using shift

and rotate instructions

Ans. Shift and rotate instructions

The shift and rotate instructions for the 8086 are defined in Fig. 5.

These instructions shift all of the bits in the operand to the left or right

by the specified count, CNT. For the shift left instructions, zeroes are

shifted into the right end of the operand and the MSBs are shifted out

the left end and lost, except that the least significant bit of these MSBs

is retained in the CF flag. The shift right instructions similarly shift bits

to the right; however, SAR (shift arithmetic right) does not

automatically insert zeroes from the left; it extends the sign of the

operand by repeatedly inserting the MSB. The rotate instructions differ

from the

shift instructions in that the operand is treated like a circle in which the

bits shifted out of one end are shifted into the other end. The RCL and

RCR instructions include the carry flag in the circle and the ROL and

ROR do not, although the carry flag is affected in all cases

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

14BC0046 – Microprocessor

Figure 5: Shift and rotate instructions.

6. Explain the concept of Linking and Relocation.

Ans. Linking and Relocation

In constructing a program some program modules may be put in the

same source

module and assembled together; others may be in different source

modules and assembled separately. If they are assembled separately,

then the main module, which has the first instruction to be executed,

must be terminated by an END statement with the entry point

specified, and each of the other modules must be terminated by an

END statement with no operand. In any event, the resulting object

modules, some of which may be grouped into libraries, must be linked

together to form a load module before the program can be executed.

In addition to outputting the load module, normally the linker prints a

memory map that indicates where the linked object modules will be

loaded into memory. After the load module has been created it is

loaded into the memory of the computer by the loader and execution

begins. Although the I/O can be performed by modules within the

program, normally the I/O is done by I/O drivers that are part of the

operating system. All that appears in the user’s program are

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

15BC0046 – Microprocessor

references to the I/O drivers that cause the operating system to

execute them.

The general process for creating and executing a program is illustrated

in Fig 6. The process for a particular system may not correspond

exactly to the one diagrammed in the figure, but the general concepts

are the same. The arrows

indicate that corrections may be made after anyone of the major

stages.

Fig. 6: Creation and Execution of a program

7. Differentiate macros and procedures.

Ans.

Macro Procedures

Macro is a group of instruction. Procedures are a group of

The macro assembler generates instructions stored as a separate

the code in the program each program in memory and it is

time where the macro is called. called

Macros are defined by MACRO & from the main program whenever

ENDM directives. Creating required. The type of procedure

macro is similar to creating new depends on where the

opcodes that can be used in the procedures are stored in memory.

program If it is in the same code segment

INIT MACRO as that of the main program

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

16BC0046 – Microprocessor

MOV AX, data

MOV DS then it is a near procedure

MOV ES, AX otherwise it is a far procedure

ENDM

Accessed during assembly with Accessed by CALL & RET

name given to macro when instruction during program

defined execution

Machine code is generated for Machine code for instruction is put

instruction each time when macro only once in the memory

is called

With Macro more memory is With procedures less memory is

required required

Parameters passed as part of Parameters can be passed in

statement which calls macro registers, memory locations or

stack

8. What is the operational difference between the IRET and

RET instructions

Ans. It is sometimes necessary to have the computer automatically

execute one of a collection of special routines whenever certain

conditions exist within a program or the computer system. The action

that prompts the execution of one of these routines is called an

interrupt and the routine that is executed is called an interrupt routine.

There are two general classes of interrupts and associated routines.

There are the internal interrupts that are initiated by the state of the

CPU or by an instruction, and the external interrupts that are caused

by a signal being sent to the CPU from elsewhere in the computer

system. Typical internal interrupts are those caused by a division by

zero or a special instruction and typical external interrupts are caused

by the need of an I/O device to be serviced by the CPU.

An interrupt routine is similar to a procedure in that it may be

branched to from any other program and a return branch is made to

that program after the

interrupt routine has executed. The interrupt routine must be written

so that, except for the lapse in time, the interrupted program will

proceed just as if nothing had happened. This means that the PSW and

the registers used by the routine must be saved and restored and the

return must be made to the instruction following the last instruction

executed before the interrupt. An interrupt routine is unlike a

procedure in that, instead of being linked to a particular-program, it is

sometimes put in a fixed place (absolutely located) in memory.

Because it is not linked to other segments, it can use only common

areas that are absolutely located to communicate with other programs.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

17BC0046 – Microprocessor

Because some kinds of interrupts -are initiated by external events,

they occur at random points in the interrupted program. For such

interrupts, no parameters or parameter addresses can be passed to

the interrupt routine. Instead, data communication must be made

through variables that are directly accessible by both routines.

Regardless of the type of interrupt, the actions that result from an

interrupt are the same and are known as the interrupt sequence. The

interrupt sequence for the 8086 is shown in Fig. 5.8. Some kinds of

interrupts are controlled by the IF and TF flags and in those cases

these flags must be properly set or the interrupt action is blocked. If

the conditions for an interrupt are met and the necessary flags are set,

the instruction that is currently executing is completed and the

interrupt sequence proceeds by pushing the current contents of the

PSW, CS, and IP onto the stack, inputting the new contents of IP and CS

from a double word whose address is determined by the type of

interrupt, and clearing the If and TF flags. The new contents of the IP

and CS determine the beginning address of the interrupt routine to be

executed. After the interrupt has been executed the return is made to

the interrupted program by an instruction that pops the IP, CS, and

PSW from the stack.

The double word containing the new contents of IP and CS is called an

interrupt pointer (or vector). Each interrupt type is given a number

between 0 and 255, inclusive, and the address of the interrupt pointer

is found by multiplying the type by 4. If the type is 9, then the interrupt

pointer will be in bytes 00024 through 00027. Since it takes 4 bytes to

store a double word, the interrupt pointers may occupy the first 1024

bytes of memory and these bytes should never be used for other

purposes. Some of the 256 interrupt types may be reserved by the

operating system and may be initialized when the computer system is

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

18BC0046 – Microprocessor

first brought up. Users may tailor the other interrupt types according to

their particular applications.

The kinds of interrupts and their designated types summarized in Fig.

8., by illustrating the layout of their pointers within memory. Only the

first five types have explicit definitions the other types may be used by

interrupt instructions or external interrupts.

Fig. 8: Layout of interrupt pointers

Instructions that initiate interrupts are sometimes called software

interrupts. Also, given in the figure is the definition of the instruction

IRET which is used to return from an interrupt routine. It is similar to

the RET instruction except that it pops the original

9. Describe about each flag of a 8086 flag register.

Ans. The 8086’s PSW contains 16 bits, but 7 of them are not used.

Each bit in the PSW is called a flag. The 8086 flags are divided into the

conditional flags, which reflect the result of the previous operation

involving the ALU, and the control flags, which control the execution of

special functions. The flags are summarized in Fig. 9

The condition flags are:

SF (Sign FIag)-Is equal to the MSB of the result. Since in 2’s

complement negative numbers have a 1 in the MSB and for

nonnegative numbers this bit is 0, this flag indicates whether the

previous result was negative’ or nonnegative.

ZF (Zero Flag)-Is set to 1 if the result is zero and 0 if the result is

nonzero.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

19BC0046 – Microprocessor

PF (Parity Flag)-Is set to 1 if the low-order 8 bits of the result

contains an even number of 1’s; otherwise it is cleared.

CF (Carry Flag)-An addition causes this flag to be set if there is a

carry out of the MSB, and a subtraction causes it to be set if a borrow

is needed. Other instructions also affect this flag and its value will be

discussed when these instructions are defined.

AF (Auxiliary Carry Flag)-Is set if there is a carry out of bit 3 during

an addition or a borrow by bit 3 during a subtraction. This flag is used

exclusively for BCD arithmetic.

OF (Overflow Flag)-Is set if an overflow occurs, i.e., a result is out of

range. More specifically, for addition this flag is set when there is a

carry into the MSB and no carry out of the MSB or vice versa. For

subtraction, it is set when the MSB needs a borrow and there is no

borrow from the MSB or vice versa. As an example, if the previous

instruction performed the addition

0010 0011 0100 1101

+ 0011 0010 0001 0001

0101 0101 0101 1110

then following the instruction:

SF=0 ZF=0 PF=0 CF=0 AF=0 OF=0

or

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

20BC0046 – Microprocessor

Fig 9: PSW register of 8086

If the previous instruction performed the addition

0101 0100 0011 1001

+ 0100 0101 0110 1010

1001 1001 1010 0011

then the flags would be:

SF = 1 ZF = 0 PF = 1 CF = 0 AF = 1 CF = 1

The control flags are:

DF (Direction Flag)-Used by string manipulation instructions. If zero,

the string is processed from its beginning with the first element having

the lowest address. Otherwise, the string is processed from the high

address towards the low address.

IF (Interrupt Enable Flag)-If

set, a certain type of interrupt (a maskable interrupt) can be

recognized by the CPU; otherwise, these interrupts are ignored.

TF (Trap Flag)-If

set, a trap is executed after each instruction.

10. Write an assembly program to add and display two

numbers.

Ans. Program:

To add two 16-bit numbers

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

21BC0046 – Microprocessor

; PROGRAM TO ADD TWO 16 – BIT DATA

DATA SEGMENT ;Assembler directive

ORG 1100H ; Assembler directive

DATA1 DW 0 ; Assembler directive

DATA 2 DW 0 ; Assembler directive

SUM DW 0 ; Assembler directive

CARRY 0 ; Assembler directive

DATA ENDS

CODE SEGMENT

ASSUME CS : CODE ; Assembler directive

ASSUME DS: DATA ; Assembler directive

ORG 1000 H ; Assembler directive

MOV AX, DATA1 ; Load the first data in AX register

MOV CL, 00H ; Clear the CL register for

carry

ADD AX, DATA2 ;Add 2nd data to AX, sum will be in

AX

MOV SUM, AX ;Store sum in memory

location (1104H)

JNC AHEAD ;Check the status of carry flag

INC CL ;If carry is set, increment CL

by one

AHEAD: MOV CARRY, CL ;Store carry in memory location

(1106H)

HLT

CODE ENDS :Assembler directive

END ;Assembler directive

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

22BC0046 – Microprocessor

February 2011

Bachelor of Computer Application (BCA) –

Semester 3 BC0046 –

Microprocessor – 4 Credits

(Book ID: B0807)

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

23BC0046 – Microprocessor

Assignment Set – 2

1. What is the value of SI after the execution of following

block of code? Explain how?

CLD

MOV CX, 0

MOV SI, 1

REP LODSB

Ans. The CLD Instruction reset the designation flag to zero. This

instruction has no effect on the registers or other flags. When the

direction flag is cleared / reset SI and DI will automatically be

incremented when one of the string instruction such as MOVS, CMPS,

SCAS, MOVSB and STOSB executes.

Examples:

CLD ; Set Auto-Increment mode

Mnemonic Meaning Format Operation Flags

Affected.

CLD Clear DF CLD (DF) → 0 df

The MOV instruction copies a word or a byte of byte of data from a

specified source to specified destination.

MOVS moves a byte (or a word) from DS:[si] to ES:[di], and increments

(or decrements) SI and DI, depending on the setting of DF, the

direction flag

(by 1 for bytes and by 2 for words). You may use CS:[si], SS:[si] or ES:

[si], but

you MAY NOT OVERRIDE ES:[di]. Though the following is not a legal

instruction, it

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

24BC0046 – Microprocessor

signifies the equivalent action to MOVS (not including changing DI and

SI):

mov WORD PTR ES:[DI], DS:[SI] ; or BYTE PTR for bytes

CLD ; Set Auto-Increment mode

MOV CX, 0 ; MOV 0 into the CX.

MOV SI,1 ; MOV 1 in to the SI

Mnemonic Meaning Format Operation Flags

Affected.

MOV Move MOV D,S (S) →(D) None

Rep Instruction: Repeat string instruction until specified condition

exist.

The string instructions may be prefixed by REP/REPE/REPNE which will

repeat the

instructions according to the following conditions:

rep decrement cx ; repeat if cx is not zero

repe decrement cx ; repeat if cx not zero AND zf = 1

repz decrement cx ; repeat if cx not zero AND zf = 1

repne decrement cx ; repeat if cx not zero AND zf = 0

repnz decrement cx ; repeat if cx not zero AND zf = 0

Here, 'e' stands for equal, 'z' is zero and 'n' is not. These repeat

instructions should NEVER be used with a segment override, since the

8086 will forget the override if hardware interrupt occurs in the middle

of the REP loop.

REP LODSB ; Repeat and move one byte at a time.

LODSB : The Load String Byte transfers the byte pointed to by DS:SI

into AL register and increments or decrements SI (depending on the

state of the Direction Flag) to point to the next byte of the string

Logic: al <- (ds:si)

if df = 0 si <- si+1

else si <- si-1

Therefore the Answer is 2

2. When working with strings, what are the advantages of the

MOVS and CMPS instructions over the MOV and CMP

instructions?

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

25BC0046 – Microprocessor

Ans. When working with strings, the advantages of the MOVS and

CMPS instructions over the MOV and CMP instructions are:

1. They are only 1 byte long.

2. Both operands are memory operands.

3. Their auto-indexing obviates the need for separate incrementing

or decrementing instructions, thus decreasing overall processing time.

As an example consider the problem of moving the contents of a block

of memory to another area in memory. A solution that uses only the

MOV instruction, which cannot perform a memory-to-memory transfer,

is shown in Fig. 2.

Fig. 2: Program sequences for moving a block of data

A solution that employs the MOVS instruction is given in Fig. 2. Note

that the second program sequence may move either bytes or words,

depending on the type of STRING1 and STRING2.

3. Explain the working of DMA.

Ans. If the data transfer rate to or from an I/O device is relatively low,

then the communication can be performed using either programmed

or interrupt I/O. Some devices, such as magnetic tape and disk units

and analog to-digital converters, may operate at data rates that are

too high to be handled by byte or word transfers. Data rates for I/O and

mass storage devices are often determined by the devices, not the

CPU, and the computer must be capable of executing I/O according to

the maximum speed of the device. For a disk unit the data rate is

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

26BC0046 – Microprocessor

determined by the speed with which data pass under the read/write

head and quite often this rate exceeds 200,000 bytes per second.

Thus, there is less than 5 microseconds to transfer each byte to or

from memory. For data rates of this magnitude, block transfers, which

use DMA controllers to communicate directly with memory, are

required.

During any given bus cycle, one of the system components connected

to the system bus is given control of the bus. This component is said to

be the master during that cycle and the component it is

communicating with is said to be the slave. The CPU with its bus

control logic is normally the master, but other specially designed

components can gain control of the bus by sending a bus request to

the CPU. After the current bus cycle is completed the CPU will return a

bus grant signal and the component sending the request will become

the master. Taking control of the bus for a bus cycle is called cycle

stealing. Just like the bus control logic, a master must be capable of

placing addresses on the address bus and directing the bus activity

during a bus cycle. The components capable of becoming masters are

processors (and their bus control logic) and DMA controllers.

Sometimes a DMA controller is associated with a single interface, but

they are often designed to accommodate more than one interface.

The 8086 receives bus requests through its HOLD pin and issues grants

from its hold acknowledge (HLDA) pin. A request is made when a

potential master sends a 1 to the HOLD pin. Normally, after the current

bus cycle is complete the 8086 will respond by putting a 1 on the HLDA

pin. When the requesting device receives this grant signal it becomes

the master. It will remain master until it drops the signal to the HOLD

pin, at which time the 8086 will drop the grant on the HLDA pin. One

exception to the normal sequence is that if a word which begins at an

odd address is being accessed, then two bus cycles are required to

complete the transfer and a grant will not be issued until after the

second bus cycle

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

27BC0046 – Microprocessor

Fig.3A: Minimal DMA interface configuration

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

28BC0046 – Microprocessor

Fig. 3B: Minimal DMA interface configuration

A block transfer is a succession of the datum transfers described

above. Each successive DMA uses the next consecutive memory

location. Although DMA controllers could be designed around a variety

of configurations, all of these configurations must satisfy certain

requirements. Since the DMA controller must supply the address when

it is master, it must be capable of storing the next memory address

that is to be accessed. It must also be able to know when to stop the

block transfer. The sequence of actions taken during a single output

DMA is illustrated in Fig. 3A. A minimal DMA controller/interface design

is shown in Fig. 3B.

The controller design contains two registers in addition to whatever

status and control registers are required, one for holding the address

of the next memory location and one for noting the number of bytes

yet to be transferred. These registers are I/O ports, so that they can be

initialized before the block transfer begins. After each datum is moved

the address register is incremented (or perhaps decremented,

depending on the design) and the byte count register is decremented.

The incrementing and decrementing are by 1 for byte transfers, and by

2 for word transfers. During a block input byte transfer, the following

sequence occurs as the datum is sent from the interface to the

memory:’

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

29BC0046 – Microprocessor

1. The interface sends the controller a request for DMA service.

2. The controller gains control of the bus.

3. The contents of the address register are put on the address bus.

4. The controller sends the interface a DMA acknowledgment which

tells the interface

to put data on the data bus. (For an output it signals the interface

to latch the next

data placed on the bus.)

5. The data byte is transferred to the memory location indicated by

the address bus.

6. The controller relinquishes the bus.

7. The address register is incremented by 1.

8. The byte count register is decremented by 1.

9. If the byte count register in nonzero, return to step1; otherwise,

stop.

4. Write short notes on (i) programmed I/O and (ii) Interrupt

I/O

ANS. Programmed I/O: It consists of continually examining the status of an interface and

performing an I/O operation with the interface when its status indicates that it has data to

be input or its data-out buffer register is ready to receive data from the CPU. A typical

programmed input operation is flowcharted in Fig.4A.

As a more complete example, suppose that a line of characters is to be input from a

terminal to an 82-byte array beginning at BUFFER until a carriage return is encountered

or more than 80 characters are input. If a carriage return is not found in the first 81

characters then the message “BUFFER OVERFLOW” is to be output to the terminal;

otherwise, a line feed is to be automatically appended to the carriage return

The program for solving the above problem is given in Fig. 4B. The interface for

Programmed IO is shown in Fig. 4C.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

30BC0046 – Microprocessor

Fig. 4A: Programmed IO Example

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

31BC0046 – Microprocessor

Fig. 4B: Programmed IO Example

Fig. 4C: Interface for the Programmed IO Example

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

32BC0046 – Microprocessor

Program instructions are controlling the transfer of data during the IN

and OUT operations. The software therefore initiates, as well as, controls

the process of data transfer. The hardware’s responsibilities are

confined to merely performing the necessary operations. The

appropriate device is first checked in the device interface to determine

whether it is ready. Device readiness must be tested because the CPU is

much faster than peripheral devices. The test is followed by a

conditional skip instruction. If the ready flag is '1' (device ready), the

program proceeds to the next step. If the Ready Flag is '0', the program

loops back to the test instruction. The CPU, therefore, waits for a slow

device by continually testing the readiness of the device, until it reports

ready. When the I/O device is ready, the data transfer operation takes

place. Immediately after the transfer of one character, the CPU reset the

ready Flag to 0. The device then sets the Flag back to 1, when it is again

ready to receive the data.

Programmed data transfer has the advantage that it allows simple

hardware interfaces, because most of the management of the I/O

operations is performed by software. The disadvantage of this

technique is that valuable CPU time is wasted while the CPU waits for

the peripheral device to get ready.

Interrupt I/O

When interfacing a peripheral to a microprocessor, the microprocessor

is not knowing when the peripheral is ready. That is, the peripheral

operates asynchronously with respect to the microprocessor. One

solution is to programme the CPU to repeatedly check the peripheral's

READY flag. However, this has a built-in disadvantage in that all the

resources of the processor are devoted to waiting for this flag. No

other task can be performed. If the peripheral is READY once in every

10,000µsec, the CPU will spend most of its time idling. A more logical

approach would be to have the peripheral "tell the CPU" when it is

ready. This is the purpose of the microprocessor'sin terrup t input. An

interrupt is used to cause a temporary halt in the execution of a

program. The microprocessor responds to the interrupt with an

Interrupt Service Sub-routine (ISS) which is a short programme or a

subroutine that instructs the microprocessor on how to handle the

interrupt.

Fig. 4D diagrams the CPU's response to an interrupt. During time 1 the

processor is assumed to be executing its main task. At time 2 the

peripheral's READY flag causes an interrupt to occur. After finishing the

current instruction at time 3, the CS, IP and flag

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

33BC0046 – Microprocessor

registers are pushed on to the stack at time 4. Control then transfers to

the ISS at time 5. During time 6, the ISS is executed, terminating with

the instruction IRET (interrupt return). The CS, IP and flag registers are

recovered from the stack during time 7 and the original task is

resumed at time 8.

Figure 4D: Execution Process of Interrupt Service Routine.

If we assume that 100µs is required to respond to the interrupt and

supply the

peripheral with data, then in the case of a 10,000µs per character

printer, 9900µs will be

available to the processor for its main task.

The 8086 has two interrupt pins labeled INTER and NM1. NM1 is a

nonmaskable interrupt, which means that it requires an immediate

response from the processor and it cannot be blocked. INTR is

maskable via the IF flag. Only when this flag is set will interrupts on

this input be accepted. Interrupts can be generated by both hardware

and software. Interrupts are also prioritized to allow for the case when

more than one interfere

Because the NMI input is nonmaskable, care must be taken when using

this interrupt. This is because there may be some programs which we

do not want to interrupt- reading or writing data to a disk drive, for

example. For this reason, NMI input is normally reserved for

catastrophic events like memory error or impending power failure.

5. Explain about the semaphore operations.

Ans. In multiprogramming systems, processes are allowed to share

common software and data resources as well as hardware resources.

In many situations, a common resource may be accessed and updated

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

34BC0046 – Microprocessor

by only one process at a time and other processes must wait until the

one currently using the shared resource is finished with it. A resource

of this type, which is commonly referred to as a serially reusable

resource, must be protected from being simultaneously accessed and

modified by two or more processes. A serially reusable resource may

be a hardware resource (such as a printer, card reader, or tape drive),

a file of data, or a shared memory area.

For example, let us consider a personnel file that is shared by

processes 1 and 2. Suppose that process 1 performs insertions,

deletions, and changes, and process 2 puts the file in alphabetical

order according to last names. If accessed sequentially, this file would

either be updated by process 1 and then sorted by process 2, or vice

versa. However, if both processes were allowed to access the file at

the same time, the results would be unpredictable and almost certainly

incorrect. The solution to this problem is to allow only one process at a

time to enter its critical section of code, i.e., that section of code that

accesses the serially reusable resource.

Preventing two or more processes from simultaneously entering their

critical sections for accessing a shared resource is called mutual

exclusion. One way to attain mutual exclusion is to use flags to

indicate when the shared resource is already in use. To examine how

this is done and some of the problems associated with this approach

let us consider the possibility of using only one flag. If there is only one

flag and FLAG = 1 indicates that the resource is free and FLAG = 0

indicates it is busy, then two processes that access the resource might

be implemented as follows:

Process 1

P1 :

TRYAGAIN1 : TEST FLAG,1

JZ TRYAGAIN1

MOV FLAG,0

} Critical section in process 1

MOV FLAG, 1

Process 2

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

35BC0046 – Microprocessor

P2:

TRYAGAIN2:

TEST FLAG,1

JZ TRYAGAIN2

MOV FLAG, 0

} Critical section in process 2

MOV FLAG, 1

where the first MOV instructions set the flag to 0 in an attempt to

prevent the other process from entering the resource. The last MOV

instructions are to reset; the FLAG to 1 after the access is complete so

that the other process can once again’ enter the resource.

The problem with the above approach is that it is possible for both

processes to enter their critical sections. To see how this can happen,

suppose that FLAG = 1 and that the following sequence occurs:

1. The TEST instruction in process 1 is executed.

2. A switch is made to process 2 before the JZ instruction in process 1

is executed.

3. The TEST instruction in process 2 is executed.

At this point both processes are free to enter their critical sections of

code.

To avoid the above problem two flags can be employed, one which

indicates that process 1 is in its critical section and one for indicating

that process 2 is in its critical section. Before either process can enter

its critical section it would first clear its flag to indicate its intention and

then repeatedly test the flag associated with the other process until it

becomes 1. This could be implemented by coding both processes as

follows:

P1 :

MOV FLAG 1, 0

CHECK1 : TEST FLAG2,1

JZ CHECK1

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

36BC0046 – Microprocessor

} Critical section

MOV FLAG1, 1

While this solution does guarantee mutual exclusion, it introduces yet

another problem, called mutual blocking. If a switch from, say,

process 1 to process 2 occurs between the MOV and TEST instructions,

then process 2 might clear FLAG2, causing both flags to be 0. Since

neither TEST has been performed at that time, neither process will be

able to enter its critical section. Both processes will be hung up in their

waiting loops.

For a solution to the critical section problem that both provides mutual

exclusion and avoids mutual blocking, a third flag is needed that

indicates which process has the higher priority when the mutual

blocking occurs. This concept was first proposed by Dekker and was

discussed by Dijkstra. Dijkstra has also extended this solution to the n-

process case.

When using an 8086 or 8088, a simple solution to the problem is

provided by the presence of the XCHG instruction. The required access

control can be obtained by using a single flag and structuring the

processes as indicated below:

P1 :

MOV AL, 0

TRYAGAIN1 : XCHG AL, FLAG

TEST AL.AL

JZ TRYAGAIN1

} Critical section

MOV FLAG,1

If FLAG = 1 when the XCHG instruction is executed, FLAG is cleared

and AL is set to 1. Even if the system switches processes after the

XCHG instruction, the new process cannot enter its critical section

because FLAG has already been cleared. This solution is attributed to

the capability of loading and setting an operand with a single

instruction (i.e., the XCHG instruction), and can be applied to any

number of processes.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

37BC0046 – Microprocessor

A flag used to reserve a shared resource is called a semaphore and the

operations of requesting and releasing the resource are commonly

known as the P and V semaphore operators. As shown above, the P

operator can be easily implemented with the MOV, XCHG, TEST, and JZ

instructions, and the V operator with a MOV instruction. However, for

this implementation, when one process is in its critical section, other

processes that are presently competing for the same resource will be

idling in the wait loops associated with their P operators. This may

cause a significant amount of CPU time to be wasted. To better utilize

the CPU time, the P operator could be modified as follows:

AGAIN: MOV AL,O

XCHG AL,SEMAPHORE

TEST AL.AL

JNZ NEXT

Call the monitor in such a way that it

will put the current process into the blocked state

JMP SHORT AGAIN

NEXT:

} Critical section

Therefore, if the semaphore is cleared, instead of repeating the wait

loop, the monitor changes the state of the current process to blocked

and switches a ready process to running. Similarly, the V operator

should be modified to be:

MOV SEMAPHORE,1

Call the monitor in such a way that it will unblock

those processes that were blocked due to the semaphore

This sets the semaphore to 1 and allows the monitor to move those

processes which were blocked because the shared resource was

unavailable from the blocked list to the ready list. The first of these

processes that resumes its execution will be able to enter its critical

section.

6. Explain what a virtual memory is?

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

38BC0046 – Microprocessor

Ans. Virtual Memory

The more sophisticated memory management scheme can be

achieved by the hardware dynamic address translation design

illustrated in Fig.6. For each memory reference, the logical address

output by the CPU is translated into the physical address, which is the

address sent to the memory by the memory management hardware.

Logical addresses are the addresses that are generated by the

instructions according to the addressing modes.

Memory Logical M

C Logical Address management logic

for mapping logical

Address

E

P Control Lines

addresses into

physical addresses Control

M

Lines O

U R

Y

DATA

Fig.6: Dynamic Address Translation

Because the logical addresses may be different from the physical

addresses, the user can design a program in a logical space, also

called a virtual space, without consideration for the limitations imposed

by the real memory. This provides two major advantages. First,

dividing a program into several pieces with each mapped into an area

in real memory, a program need not occupy a contiguous memory

section. Therefore, memory fragmentation is reduced and less memory

space is wasted. Second, it is not necessary to store the entire

program in memory while it is executing. Whenever a portion of the

program that is not currently in memory is referenced, the operating

system can suspend the program, load in the required section of code,

and then resume the program’s execution. This allows a program’s size

to be larger than the actual memory available. In

other words, a user “virtually” has more memory to work with than

actually exists.

With address translation hardware, the program is divided into

segments according to the logical structure of the program and the

resulting memory management scheme is called segmentation. When

using segmentation, each logical address consists of two fields, the

segment number and the offset within the segment. The number of

bits representing the segment number governs the maximum number

of segments allowed in a program, and the number of bits allocated to

the offset specifies the maximum segment size. For example, if the

segment number and offset have m and n bits, respectively, a program

may have up to 2m segments, with each segment having a maximum

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

39BC0046 – Microprocessor

size of 2n bytes, thus providing each user with a virtual storage of 2m+n

bytes.

Fig. 6A illustrates the mapping of logical addresses into physical

addresses.

Fig. 6A: Segmentation Scheme

The segment number S in a logical address is used as an index into the

segment table, which returns the beginning physical address X of the

referenced segment. This address added to the offset L to form the

physical address of the memory location. Because each job may be

assigned a separate area in the segment table, the base address of

that section of the segment table that is associated with the currently

executing job is stored in a register called the segment table register.

The index S is made relative to the segment table register. When the

system switches from one job to another, the segment table register is

updated to point to a new section of the segment table. Because the

address translation must be performed for every memory reference,

either the entire segment table or that portion of the table containing

the beginning addresses of the segments that are currently in use

must be stored in registers which are part of the memory management

hardware.

Each entry in the segment table is referred to as a segment descriptor.

Depending on ,the particular implementation, a segment descriptor

may include attributes in addition to the beginning segment address.

The most common of these additional attributes are the.:

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

40BC0046 – Microprocessor

Status Field - Indicates whether or not the referenced segment is in

the memory.

Segment Length Field - Indicates the size of the segment.

Protection Field - Provides protection against unauthorized reading,

writing, or execution.

Reference Field - Provides useful information in determining which

segment is to be replaced.

Change field - Indicates whether or not the segment has been

modified since being brought into memory .

7. Differentiate between minimum mode and maximum mode

of configuration in microprocessor.

Ans.

• In Minimum mode, all control signals are self generated by

8086/8088 microprocessor such as RD' and WR'.

• In maximum mode, the control signals are generated by external

chip such as MRDC' (memory read) and MWTC' (memory write) by

8288 chip.

• In Minimum mode the 8086 processor works in a single processor

environment.

All control signals for memory and I/O are generated by the

microprocessor.

• In Maximum mode is designed to be used when a coprocessor exists

in the system.

8086 works in a multiprocessor environment. Control signals for

memory and

I/O are generated by an external BUS Controller.

• The pin#33 selects the mode. If connected to +5vcc => minimum

mode & if grounded => maximum mode. Both have different

functions because changing the mode changes the functionality of

some others pins too.

• INTEL's pre release 8085A, to support its features, minimum mode

was there while to support the modern design journey of

microprocessors, maximum mode was available.

• Minimum mode operation is least expensive way to operate the

8086/8088 because all the control signals were generated, for the

IO or and Memory, by the processor and allowed the 8085A without

any special consideration

• Maximum mode ; some of the control signals must be generated

externally, requires an addition of an external bus controler 8288.

maximum mode had the ability to control the external buses and

was used only when coprocessors were attached with the processor

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

41BC0046 – Microprocessor

• In Minimum mode mn/mx- is connected to vcc .here now mn will be

one and in Min Mode one processor is present without any co

processor and in min mode only one processor is present without

any co processor

• 8086 microprocessors can be configured to work in either of the two

modes: the minimum mode and the maximum mode

• Minimum mode:

Pull MN/MX to logic 1

Typically smaller systems and contains a single microprocessor

• Maximum mode

Pull MN/MX logic 0

Larger systems with more than one processor

8088 Minimum- Mode Block Diagram

System Bus Timing

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

42BC0046 – Microprocessor

The length of a bus cycle in an 8086 system is four clock cycles,

denoted T1 through T4, plus an indeterminate number of wait state

clock cycles, denoted Tw. If the bus is to be inactive after the

completion of a bus cycle, then the gap between successive cycles is

filled with idle state clock cycles represented by T1. Wait states are

inserted between T3 and T4 when a memory or I/O interface is not able

to respond quickly enough during a transfer. A typical succession of

bus cycles is given in Fig. 9.9.

The timing diagrams for 8086 minimum mode input and output transfers that require no

wait states are shown in Fig. 7B. When the state of the processor is such that it is ready to

initiate a bus cycle it applies a pulse to the ALE pin during Tl. Before the trailing edge of

the ALE signal the address, BHE, M/IO, DEN, and DT/R signals should be stable, with

DEN= 1 and DT/R = 0 for an input and DT/R = 1 for an output. At the trailing edge of

the ALE signal the 8282s latch the address. During T2 the address is dropped and S3

through S7 are output on AD16/S3-AD19/S6 and BHE/S7, and DEN, is lowered to

enable the 8286 transceivers. If an input is being conducted, RD is activated low during

T2 and AD15-AD0 enter a high-impedance state in preparation for input. If the memory

or I/O interface can perform the transfer immediately, there are no wait states and the

data are put on the bus during T3. After the input data are accepted by the processor, RD

is raised to 1 at the beginning of T4 and, upon detecting this transition, the memory or

I/O interface will drop its data signals. For an output, the processor applies the WR = 0

signal and then the data during T2, and in T4 WR is raised and the data signals are

dropped. For either an input or output, DENis raised during T4 to disable the transceivers

and the M/IO, signal is set according to the next transfer at this time or during a

subsequent T1 state.

Fig. 7A: Typical sequence of bus cycles

The timing diagrams for input and input and output transfers on a maximum mode system

are given in Fig. 7B. The S0, S1 and S2 bits are set just prior to the beginning of the bus

cycle. Upon detecting a change from the passive S0 = S1 = S2 = 1 state, the 8288 bus

controller will output a pulse on its ALE pin and apply the appropriate signal to its DT/R

pin during Tl. In T2, the 8288 will set DEN= 1, thus enabling the transceivers, and, for an

input, will activate either MRDC or IORC. These signals will be maintained until T4′.

For an output, the AMWC or AIOWC is activated from T2 to T4 and the MWTC or

IOWC is activated from T3 to T4. The status bits S0 and S2 will remain active until T3

and will become passive (all 1s) during T3 and T4. As with the minimum mode, if the

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

43BC0046 – Microprocessor

READY input is not activated before the beginning of T3, wait states will be inserted

between T3 and T4.

1. Input

(b) Output

Fig. 7B: 8086 minimum mode bus timing diagrams

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

44BC0046 – Microprocessor

1. Input

(b) Output

Fig. 7C: Timing diagrams for maximum mode system

8. Explain the 8288 Bus controller.

Ans. An expanded view of a maximum mode system which shows only

the connections to an 8288 is given in Fig.8. The s0, s1and s2 pins are

for receiving the corresponding status bits from the processor. The

ALE, DT/R and DEN pins provide the same outputs that are sent by the

processor when it is in minimum mode.The CLK input permits the bus

controller activity to be synchronized with that of the processor. The

AEN, IOB, and CEN pins are for multiprocessor systems. In a single-

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

45BC0046 – Microprocessor

processor system AEN, IOB are normally grounded and a 1 is applied to

CEN. The meaning of the MCE/PDEN output depends on the mode,

which is determined by the signal applied to IOB. When IOB is

grounded it assumes its master cascade enable (MCE) meaning and

can be used to control cascaded 8259. As In the event that +5 V is

connected to IOB, the peripheral data enable (PDEN) meaning, which is

used in multiple-bus configurations, is assumed.

The remaining pins given in Fig.8 have the following definitions:

INTA- Issues the two interrupt acknowledgment pulses to a priority

interrupt controller or an interrupting device when S0 = S1 = S2 =0

IORC - (I/O Read Command)- Instructs an I/O interface to put the data

contained in the addressed port on the data bus.

IOWC - (I/O Write Command)-Instructs an I/O interface to accept the

data on the data bus and put the data into the addressed port.

MRDC - (Memory Read Command)-Instructs the memory to put the

contents of the

addressed location on the data bus.

MWTC - (Memory Write Command)-Instructs the memory to accept the

data on the data bus and put the data into the addressed memory

location.

These signals are active low and are output during the middle portion

of a bus cycle. Clearly, only one of them will be issued during any

given bus cycle.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

46BC0046 – Microprocessor

Fig. 8: Connection to an 8288 bus controller.

9. Draw the block diagram of 8087

Ans.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

47BC0046 – Microprocessor

Block Diagram of 8087

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

48BC0046 – Microprocessor

10. Explain why the processor utilization rate can be improved

in a multiprocessor system by an instruction queue.

Ans. Because the 8086 has a 6-byte instruction queue, the instruction

that has just been fetched may not be executed immediately. In order

to allow external logic to monitor the execution sequence, a maximum

mode 8086 outputs the queue status through its QSl and QS0 pins.

During each clock cycle the queue status is examined and the QSl and

QS0 bits are encoded as follows:

00-No instruction was taken from the queue.

0l-The first byte of the current instruction was taken from the queue.

10-The queue was flushed because of ‘a transfer instruction.

11-A byte other than the first byte of an instruction was taken from the

queue.

By monitoring the bus and the queue status, external logic can

simulate the CPU’s instruction execution sequence and determine

which instruction is currently being executed. This facility is necessary

so that the 8086 can indicate when an instruction is to be executed by

a coprocessor.

It is necessary to control the accesses to the shared resources in a

multiprogramming environment. Normally, semaphores, are used to

ensure that at any given time only one may enter its critical section of

code in which a shared resource is accessed.

Let us now reconsider the semaphore implementation:

MOV AL, 0

TRYAGAIN : XCHG SEMAPHORE,AL

TEST AL, AL

JZ TRYAGAIN

{Critical section in which a process accesses a shared resource}

MOV SEMAPHORE, 1

This implementation works fine for a system in which all of the

processes an executed by the same processor, because the processor

cannot switch from one process to another in the middle of an

instruction. However, if competing processes are running on different

processors, the situation is more complex.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

49BC0046 – Microprocessor

Suppose that processor A is concurrently ready to update a record in

memory while processor B is ready to sort the same record. Since both

processors are running independently, they might test the semaphore

at the same time. Note that the XCHG instruction requires two bus

cycles, one which inputs the old semaphore and one which outputs the

new semaphore. It is possible that after processor A fetches the

semaphore, processor B gains control of the next bus cycle and fetches

the same semaphore.

Suppose that the location SEMAPHORE contains a 1 and both

processors A and B are executing

TRY AGAIN: XCHG SEMAPHORE,AL and

1. Processor A uses the first available bus cycle to get the contents of

SEMAPHORE.

2. Processor B uses the next bus cycle to get the contents of

SEMAPHORE

3. Processor A clears SEMAPHORE during the next bus cycle, thus

completing its XCHG

instruction.

4. Processor B clears SEMAPHORE during the next bus cycle, thus

completing its XCHG

instruction.

After this sequence is through, the AL registers in both processors will

contain 1 and the

TEST AL,AL

instruction will cause the JZ instructions to fail. Therefore both

processors will enter their critical sections of code.

To avoid this problem, the processor that starts executing its XCHG

instruction first (which in this example is processor A) must have

exclusive use of the bus until the XCHG instruction is completed. On

the 8086 this exclusive use is guaranteed by a LOCK prefix:

1111100001

which for a maximum mode CPU, activates the LOCK output pin during

the execution of the instruction that follows the prefix. The LOCK signal

indicates to the bus control logic that no other processors may gain

control of the system bus until the locked instruction is completed. To

get around the problem encountered in the above example the XCHG

instructions could be replaced with:

TRYAGAIN: LOCK XCHG SEMAPHORE, AL

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

50BC0046 – Microprocessor

This would ensure that each exchange will be completed in two

consecutive bus cycles.

Physically, in a loosely coupled system each processing module

includes a bus arbiter and the bus arbiters are connected together by

special control lines in the system bus. One of these lines is a busy line

which is active whenever the bus is in use. When a processing

module’s arbiter is given control of the bus it will activate the busy

line, which will prevent other arbiters from seizing the bus until after

the next bus cycle. If a signal is sent to the arbiter controlling the bus,

then that arbiter will retain control of the system by holding the busy

line active until the signal is dropped. Thus, if a processor applies a

signal throughout the execution of an entire instruction, its arbiter will

not relinquish the system bus until the instruction is complete.

In a module including a coprocessor or closely coupled configuration, if

a bus request is made through one of the 8086’s / pins while the pin is

active, then the request will be held until the signal is dropped. Then

the 8086 will respond to the request by returning a grant. In addition to

being activated by a prefix, an interrupt request on a CPU’s INTR pin

will cause the pin to be held low from the beginning of the first pulse

until after the second pulse. This guarantees availability of the bus

until the completion of an interrupt cycle.

Another possible application of the bus lock capability is to allow fast

execution of an instruction which requires several bus cycles. For

example, in a multiprocessor system a block of data can be

transferred at a higher speed by using the LOCK prefix as follows:

LOCK REP MOVS DEST, SRC

During the execution of this instruction the system bus will be reserved

for the sole use of the processor executing the instruction.

Assignment by: Paramjeet Singh Virdi, Roll number: 521022919

You might also like

- Basics of Micro ProcessorDocument27 pagesBasics of Micro ProcessorBibin LeeNo ratings yet

- MPI GTU Study Material E-Notes Unit-3 13052022115048AMDocument15 pagesMPI GTU Study Material E-Notes Unit-3 13052022115048AMmailsender787No ratings yet

- Microprocessors and Microcontrollers Answer KeyDocument14 pagesMicroprocessors and Microcontrollers Answer KeyselvaNo ratings yet

- Introduction To Microprocessor and Microcomputer ArchitectureDocument6 pagesIntroduction To Microprocessor and Microcomputer Architecturesri vatsaNo ratings yet

- Introduction to 8085 Architecture and Programming TutorialDocument23 pagesIntroduction to 8085 Architecture and Programming TutorialKorak MitraNo ratings yet

- Introduction to 8085 Microprocessor Architecture and ProgrammingDocument23 pagesIntroduction to 8085 Microprocessor Architecture and ProgrammingdevNo ratings yet

- 8085 MicroprocessorDocument23 pages8085 Microprocessorauromaaroot196% (55)

- 8085 Microprocessor NotesDocument25 pages8085 Microprocessor NotesAjay Roopesh100% (1)

- Ebooks For FreeDocument24 pagesEbooks For FreeNihar KhuranaNo ratings yet

- 8086 PDFDocument261 pages8086 PDFndeshmukh83No ratings yet

- Architecture of 8-bit Intel 8085 microprocessorDocument34 pagesArchitecture of 8-bit Intel 8085 microprocessorUtshab ChapagainNo ratings yet

- Microprocessor and Micro Controller Lecture NotesDocument118 pagesMicroprocessor and Micro Controller Lecture NotesSivanesh SK50% (2)

- Tutorial On Introduction To 8085 Architecture and ProgrammingDocument23 pagesTutorial On Introduction To 8085 Architecture and ProgrammingDennish KarkiNo ratings yet

- MCT Unit 2Document26 pagesMCT Unit 2Aravind RajNo ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Cs2252 - MPMC 16 M With Answers Upto 2Document40 pagesCs2252 - MPMC 16 M With Answers Upto 2archumeenabaluNo ratings yet

- Part 2Document41 pagesPart 2ah chongNo ratings yet

- Microprocessor & microcontroller introductionDocument20 pagesMicroprocessor & microcontroller introductionjeravi84No ratings yet

- 8085 Microprocessor Unit 1Document13 pages8085 Microprocessor Unit 1Sajid Akram100% (1)

- Microprocessor lecture notes on theory and applicationsDocument114 pagesMicroprocessor lecture notes on theory and applicationsKumar GaneshNo ratings yet

- Cs 2252 FinalnotesDocument182 pagesCs 2252 Finalnotesearth2hellothereNo ratings yet

- Important 8085 Microprocessor QuestionsDocument59 pagesImportant 8085 Microprocessor QuestionsParamartha BanerjeeNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet