Professional Documents

Culture Documents

jmb385 Car Reader

Uploaded by

zerohcodeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

jmb385 Car Reader

Uploaded by

zerohcodeCopyright:

Available Formats

JMB385

JMB385 (Version D)

PCI Express to Card Reader

Host Controller

Data Sheet

Rev. 1.2

JMicron Technology Corporation

1F, No.13, Innovation Road 1,

Science-Based Industrial Park, Hsinchu, Taiwan, R.O.C

http://www.jmicron.com

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 1 NDA Required

JMB385

© Copyright JMicron Technology, 2008.

All Rights Reserved.

Printed in Taiwan 2008

JMicron and the JMicron Logo are trademarks of JMicron Technology Corporation in Taiwan and/or other

countries. Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in

this document are NOT intended for use implantation or other life supports application where malfunction

may result in injury or death to persons. The information contained in this document does not affect or

change JMicron’s product specification or warranties. Nothing in this document shall operate as an express

or implied license or environments, and is presented as an illustration. The results obtained in other

operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIEDE ON AN “AS IS” BASIS.

In no event will JMicron be liable for damages arising directly or indirectly from any use of the

information contained in this document.

JMicron Technology Corporation

1F, No.13, Innovation Road 1,

Science-Based Industrial Park

Hsinchu, Taiwan, R.O.C

For more information on JMicron products, please visit the JMicron web site at

http://www.jmicron.com or send email to sales@jmicron.com

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 2 NDA Required

JMB385

Revision History

Version Date Revision Description

1.0 2008/11/06 Initial Release

1.1 2008/11/21 Change pin30 from TAV33 to NC

1.2 2008/12/01 Modify power consumption

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 3 NDA Required

JMB385

Table of Contents

1. Overview......................................................................................................................................................5

2. Features ........................................................................................................................................................7

2.1 Compliance ........................................................................................................................................7

2.2 Overall................................................................................................................................................7

2.3 PCI Express........................................................................................................................................7

2.4 Memory Card .....................................................................................................................................7

2.5 DOS Utility ........................................................................................................................................7

3. Electrical Characteristic ...............................................................................................................................9

3.1 Absolute Maximum Rating................................................................................................................9

3.2 PCI Express PHY DC/AC Specification ...........................................................................................9

3.3 Digital DC/AC Specification ...........................................................................................................10

3.4 Power Specification .........................................................................................................................10

3.5 Power Supply Noise Requirement ...................................................................................................11

3.6 Transmitter Jitter Specification ........................................................................................................11

3.7 Reference Clock Input Requirement................................................................................................11

3.8 Card Reader Access Timing Characteristic .....................................................................................12

4. Pin Description...........................................................................................................................................15

4.1 Pin List Table & Floorplan...............................................................................................................15

4.2 System Control Pin ..........................................................................................................................17

4.3 PCI Express Analog Pin...................................................................................................................18

4.4 Card Reader Pin ...............................................................................................................................19

4.5 Power/Ground Pin............................................................................................................................22

5. Function Description..................................................................................................................................23

5.1 Block Diagram .................................................................................................................................23

5.2 Operating Mode Configuration........................................................................................................25

5.3 Clocking...........................................................................................................................................25

5.4 Reset and Disable Mechanism .........................................................................................................26

5.5 PCI Express Link .............................................................................................................................26

5.6 D3 Enhancement (D3E) Mode.........................................................................................................27

6. System Programming Interface..................................................................................................................28

6.1 Card Reader Pin Arrangement .........................................................................................................28

6.2 Software Development Resource.....................................................................................................29

6.3 Driver Supporting ............................................................................................................................29

7. Product Information ...................................................................................................................................30

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 4 NDA Required

JMB385

1. Overview

JMB380/1/2/3/5/7 is product family that includes 1394 OHCI and Memory Card Reader Host

Controller. They are one-lane PCI Express to 1/2-port 1394a and 1/2-slot SD/MMC/MS/xD Memory Card

Reader Host Controller. The table below shows the brief feature lists of JMB38X product family.

Table 1.1 JMB38X Product Families

JMB380 JMB381 JMB382 JMB383 JMB385 JMB387

Host IF PCIe PCIe PCIe PCIe PCIe PCIe

1394a IF x1 Port x2 Port None x1 Port None None

Card Reader x1 Combo None x2 Combo x2 Combo x1 Combo x1 Combo

TQFP64

Package QFN48 LQFP48 LQFP64 (E-pad) LQFP48 LQFP48

Boot Function None None Support None None Support

Version A B A B A B C D A B

D3E x v x v x v v v v v

EEPROM v x v v v x x v x v

SPI(Boot) x x x x x x x x v v

CR1_CD2 x x x x x x v x v x

Co-layout Co-layout

For JMB380/5/7, only one set of 4-in-1 Combo Memory Card Reader Mechanism supporting no matter

which one of SD/MMC/MS/MS Duo/MS-HG (1/4/8-bit) & xD access at the same time due to only 48-pin

count. For JMB382/3, two sets of 4-in-1 Combo Memory Card Reader Mechanisms that include one of

SD/MMC/MS/MS Duo/MS-HG (1/4/8-bit) & xD and the other of SD/MMC/MS/MS Duo/MS-HG (1/4/8

-bit) at the same time. JMB382/3 is especially suitable for bigger NB when two Combo Memory Card

Reader slots needed access at the same time.

JMB380/2/3/5/7 is multi-function architecture on PCI domain. JMB381 has only 1394 OHCI

function. For 1394 OHCI function, JMB380/2/3 use Windows default driver to achieve better compatibility.

Of course, JMicron offers Windows / MAC driver on Memory Card Reader to achieve the better

compatibility and performance.

JMB380/1/2/3/5/7 supports hot-plug behavior on both 1394a ports and memory card slots. For 1394a

PHY, Programmable Output Swing Control is reserved for better compatibility. For memory card host

controller, the programmable IO driving capacity and dynamic pull high/low control is also reserved for

better system feasibility. These system feasibility guarantees better compatibility for all kinds of 1394a and

Memory Card Devices.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 5 NDA Required

JMB385

JMB380/5 Version A, JMB385 Version D, JMB387 Version B and JMB381/2/3 also reserve Serial

EEPROM interface for SVID/SSID/GUID programming. System makers can use Serial EEPROM to store

specific information in it. We also provide simple update & management tool for makers.

JMB380/1/2/3/5/7 might need some internal register setting for the best performance under different

platforms. We will provide the binary code for customers no matter binary code in Serial EEPROM or

binary code in Main BIOS.

JMB380/5 Version B/C/D and JMB387 supports D3 Enhancement (D3E) mode to make the lowest

power consumption when no 1394 device or memory cards inserted. It is very suitable for NB Application.

JMB385 Version C and JMB387 Version D use three dedicated card detection pins to detect

SD/MMC, MS and xD. These pins are connected to card connector. It can save BOM cost of one diode.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 6 NDA Required

JMB385

2. Features

2.1 Compliance

• Compliant with PCI Express Base Spec. Revision 1.1

• Compliant with SD Spec. Part 1 Physical Layer Spec. Version 2.00

• Compliant with SD Spec. Part A2 SD Host Controller Standard Spec. Version 2.00

• Compliant with SD Spec. Part E1 SDIO Spec. Version 2.00

• Compliant with SD Spec. Part 2 File System Spec. Version 2.00

• Compliant with MultiMediaCard System Spec. Version 4.2

• Compliant with Memory Stick Standard Format Spec. Version 1.43-00

• Compliant with Memory Stick Standard Memory Stick PRO Format Spec. – without security spec. –

Version 1.02-00

• Compliant with Memory Stick Pro-HG Duo Spec. Version 1.00

• Compliant with xD-Picture CardTM Card Spec. Version 1.20

• Compliant with xD-Picture CardTM Host Guideline Version 1.20

• Compliant with xD-Picture CardTM Host Compliance Design Check Spec. Version 1.20D

• Compliant with xD-Picture CardTM Format Spec. Version 1.11

• Compliant with System Management Bus Specification Revision 1.1

2.2 Overall

• Integrated PCI Express PHY and 2.5G PLL for PCI Express bus

• Output swing control and Automatic impedance calibration for PCI Express PHY

• Fabricated 0.18um/3.3V CMOS Standard Logic Process with single 3.3V power source

• JMB385 is available in 48-pin LQFP package

• Co-layout between JMB380, JMB381, JMB382 and JMB383

• Integrate External PMOS Power Switch for power control of memory card

• Integrate External Regulator for 1.8V Power source of JMB385 to save system BOM

• Support D3E mode to save more power when no 1394 device or memory card inserted

2.3 PCI Express

• Supports 1-Lane 2.5Gbps PCI Express bus

• Internal native interface multiplexed to Memory Card (SD/MMC/MS/xD)

• All registers of Memory Card accessible in unified memory space

2.4 Memory Card

• Supports 1 set of “4-in-1 Combo Memory Card Reader Mechanism”

• Programmable IO driving to adjust signal trace length

• Programmable pull high/low control for different memory card bus topology

2.5 DOS Utility

• Provide Serial EEPROM DOS Update Utility

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 7 NDA Required

JMB385

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 8 NDA Required

JMB385

3. Electrical Characteristic

3.1 Absolute Maximum Rating

Parameter Description Rating Unit

DV33 Digital IO Supply Voltage (Input) 3.96 V

DV18 Digital Core Power Voltage (Output) 2.02 V

APV18, APVDD PCIE Analog Power Voltage (Input) 2.02 V

VIN Input Voltage -0.3~VDD+0.3 V

0

ӨJC Thermal Resistance (Junction to Case) 29.37 C/W

0

TOPERATING Operating Environment Temperature 0~70 C

0

TSTORAGE Storage Temperature -25~135 C

3.2 PCI Express PHY DC/AC Specification

PCIE Spec JMB385

TX Parameter Min. Typ. Max. Min. Typ. Max. Unit Note

T UI 399.88 400 400.12 399.99 400.00 400.02 ps SSC is off

V tx_diff_pp 0.8 1.2 1.0 V Differential amplitude

V tx_de_ratio -3 -3.5 -4 -3.38 dB

T tx_eye 0.75 0.8563 UI @APTXP/N

T tx_eye_median_to_max_jitter 60 26.23 30.35 36.47 ps

T tx_rise 50 69.41 ps 20%~80% @APTXP/N

T tx_fall 50 71.16 ps 80%~20% @APTXP/N

V tx_cm_ac_p 20 11 mV

V tx_dc_cm 0 3.6 1.177 V

V tx_rcv_detect 600 244 mV

Z tx_diff_dc 80 100 120 95 ohm Differential impedance

C tx 75 200 100 nF AC coupled Cap.

RX Parameter Min. Typ. Max. Min. Typ. Max. Unit Note

T UI 399.88 400 400.12 399.98 400.00 400.02 ps SSC is off

V rx_diff_pp 0.175 1.2 0.869 V Differential amplitude

T rx_eye 0.4 0.85 UI @APRXP/N

T rx_eye_median_to_max_jitter 120 24.03 29.55 39.42 ps

V rx_cm_ac_p 150 84 93.57 104 mV

Z rx_diff_dc 80 100 120 95 ohm Differential impedance

V rx_idle_det_diff_pp 65 175 115 mV

ps. All symbols used are followed PCI Express Base Specification Revision 1.1.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 9 NDA Required

JMB385

3.3 Digital DC/AC Specification

Parameter Min. Typ. Max. Unit Note

DC driving at VOH(min) 8 mA Measured at GPIO1 pin

DC driving at VOL(max) 8 mA Measured at GPIO1 pin

Output High Voltage VOH 2.4 V

Output Low Voltage VOL 0.4 V

Input High Voltage VIH 1.5 V @GPIO1 pin, 8mA

Input Low Voltage VIL 1.28 V @GPIO1 pin, 8mA

Weak pull high R value 70.0 kΩ Measured at GPIO1 pin

Weak pull low R value 70.0 kΩ Measured at GPIO1 pin

AC rising time 3.6 ns @GPIO1 pin, 8mA, 10%~90%, 20pF loading

AC falling time 3.8 ns @GPIO1 pin, 8mA, 10%~90%, 20pF loading

3.4 Power Specification

Parameter Min. Typ. Max. Unit Note

Digital IO (DV33) 3.14 3.3 3.63 V -5%~10%

Digital 3.3V Power 3.14 3.3 3.63 V -5%~10%

Digital Core (DV18) 1.76 1.85 1.95 V -5%~5%

PCIE PHY Power (APV18+APVDD) 1.76 1.85 1.95 V -5%~5%

Digital Core (DV18 from DV33) 45.0 mA Measured under memory card access

Digital IO (DV33) 45.0 mA Measured under memory card access and

including power consumption of memory card

PCIE PHY Power (APV18+APVDD 80.0 mA Measured under memory card access

from DV33)

Digital 3.3V Power 1.0 mA Measured under memory card access

All Power Source (DV18+DV33+ 30.0 80.0 mA Normal D3(HOT) Power Down Mode

APV18+APVDD)

All Power Source (DV18+DV33+ 0.5 1.0 mA Advance D3E(HOT) Power Down Mode

APV18+APVDD)

0

Surface Temperature TCASE 45.1 C @JMicron EVB under room temperature 250C

0

Surface Temperature Range TCASE 100 C

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 10 NDA Required

JMB385

3.5 Power Supply Noise Requirement

Parameter Min. Typ. Max. Unit Note

Digital 3.3V Power 100 mV

Digital IO (DV33) 250 mV

1.8V Power (DV18/APVDD/APV18) 100 250 mV Need de-coupled capacitors

3.6 Transmitter Jitter Specification

Parameter Min. Typ. Max. Unit Note

PCIE PHY short-term jitter 70 ns @N=5

PCIE PHY long-term jitter (1) 75 90 ns @N=250

PCIE PHY long-term jitter (2) 75 250 ns @N=10000

3.7 Reference Clock Input Requirement

Parameter Min. Typ. Max. Unit Note

Absolute Max. Input Voltage VMAX 1.15 V

Absolute Min. Input Voltage VMIN -0.3 V

Input High Voltage VIH 150 mV @APCLKP&APCLKN, Differential waveform

Input Low Voltage VIL -150 mV @APCLKP&APCLKN, Differential waveform

Absolute cross point voltage VCROSS 250 550 mV Single ended waveform

Variation of VCROSS VCROSS DELTA 140 mV Single ended waveform

Ring-back Margin VRB -100 100 mV Differential waveform

Time before VRB TSTABLE 500 ps Differential waveform

Average Clock Accuracy TPERIOD AVG -300 2800 ppm Differential waveform, SSC is ON

Absolute Period TPERIOD ABS 9.847 10.203 ps Differential waveform, cycle-to-cycle jitter, PPM

& SSC effect are included

Cycle-to-cycle jitter TCCJITTER 150 ps Differential waveform

Rising Edge Rate 0.6 4.0 V/ns Between VIH and VIL

Falling Edge Rate 0.6 4.0 V/ns Between VIH and VIL

Rise-Fall Matching 20 % Single ended waveform

Duty Cycle 40 60 % Differential waveform

Clock Source Impedance ZC-DC 40 60 Ω Single ended impedance

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 11 NDA Required

JMB385

3.8 Card Reader Access Timing Characteristic

3.8.1 SD Timing

SD Spec. JMB380

Default Mode Min. Typ. Max. Min. Typ. Max. Unit Note

f PP 0 25 24.96 MHz

CLK f OD 0 400 195.0 kHz

t WL 10 17.89 ns @10% level

t WH 10 19.86 ns @90% level

t TLH 10 1.53 ns 10%~90% @card

t THL 10 0.64 ns 90%~10% @card

CMD & DAT t ISU 5 28.0 ns 90% level @card

(Output) t IH 5 9.6 ns 90% level @card

SD Spec. JMB380

High Speed Mode Min. Typ. Max. Min. Typ. Max. Unit Note

f PP 0 50 49.75 MHz

CLK t WL 7 8.05 ns @10% level

t WH 7 9.8 ns @90% level

t TLH 3 1.54 ns 10%~90% @card

t THL 3 0.62 ns 90%~10% @card

CMD & DAT t ISU 6 10.4 ns 90% level @card

(Output) t IH 2 7.0 ns 90% level @card

ps. All symbols used are followed SD Specification Part 1 Physical Layer Specification Version 2.00

3.8.2 MMC testing Result

MMC Spec. JMB380

Backward Compatible Mode Min. Typ. Max. Min. Typ. Max. Unit Note

f PP 0 20 19.97 20 MHz

CLK f OD 0 400 195.3 kHz

t WL 10 24.5 ns @10% level

t TLH 10 1.6 ns 10%~90% @card

t THL 10 0.48 ns 90%~10% @card

CMD & DAT t ISU 3 34.4 ns 90% level @card

(Output) t IH 3 15.6 ns 90% level @card

MMC Spec. JMB380

High Speed Mode Min. Typ. Max. Min. Typ. Max. Unit Note

f PP 0 26/52 49.5 MHz tolerance:100KHz

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 12 NDA Required

JMB385

CLK f OD 0 400 195.2 kHz tolerance:20KHz

t WL 6.5 9.87 ns @10% level

t TLH 3 1.57 ns 10%~90% @card

t THL 3 0.64 ns 90%~10% @card

CMD & DAT t ISU 3 11.77 ns 90% level @card

(Output) t IH 3 8.3 ns 90% level @card

ps. All symbols used are followed MultiMediaCard System Specification Version 4.2

3.8.3 MS testing Result

MS Spec. JMB380

Serial Interface Min. Typ. Max. Min. Typ. Max. Unit Note

t SCLKc 50 50 50.2 ns 50%~50% @card

t SCLKwh 15 25.5 ns @90% level

SCLK t SCLKwl 15 24.6 ns @10% level

t SCLKr 10 2.13 ns 10%~90% @card

t SCLKf 10 2.33 ns 90%~10% @card

t BSsu 5 24.5 ns 50%~2/80% @card

BS t BSh 5 23.9 ns 50%~2/80% @card

t BSr 10 1.77 ns 10%~90% @card

t BSf 10 1.83 ns 90%~10% @card

t Dsu 5 23.8 ns 50%~2/80% @card

DATA t Dh 5 25.1 ns 50%~2/80% @card

t Dr 10 1.38 ns 10%~90% @card

t Df 10 1.4 ns 90%~10% @card

t Dd 15 8.86 ns 50%~2/80% @card

MS Spec. JMB380

Parallel Interface Min. Typ. Max. Min. Typ. Max. Unit Note

t SCLKc 25 25 25.3 ns 50%~50% @card

t SCLKwh 5 10.2 ns @90% level

SCLK t SCLKwl 5 15.2 ns @10% level

t SCLKr 10 2.15 ns 10%~90% @card

t SCLKf 10 1.93 ns 90%~10% @card

t BSsu 8 17.5 ns 50%~2/80% @card

BS t BSh 1 5.5 ns 50%~2/80% @card

t BSr 10 2.24 ns 10%~90% @card

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 13 NDA Required

JMB385

t BSf 10 4.13 ns 90%~10% @card

t Dsu 8 17 ns 50%~2/80% @card

DATA t Dh 1 6.5 ns 50%~2/80% @card

t Dr 10 1.69 ns 10%~90% @card

t Df 10 3.36 ns 90%~10% @card

t Dd 15 9.97 ns 50%~2/80% @card

ps. All symbols used are followed Memory Stick PRO Format Specification - without security specification – ver.1.02-00

3.8.4 xD testing Result

xD Spec. JMB380

Min. Typ. Max. Min. Typ. Max. Unit Note

T CLS 20 50.3 ns 50%~50% @card

T CLH 40 49.5 ns 50%~50% @card

T CS 20 49.2 ns 50%~50% @card

T CH 40 200.5 ns 50%~50% @card

T WP 40 50 ns 50%~50% @card

T ALS 20 49.7 ns 50%~50% @card

T ALH 40 50.4 ns 50%~50% @card

T DS 30 49.6 ns 50%~50% @card

T DH 20 50.3 ns 50%~50% @card

T WC 80 100.2 ns 50%~50% @card

T WH 20 50 ns 50%~50% @card

T WW 100 585 ns 50%~50% @card

T RR 20 183 ns 50%~50% @card

T RP 60 75 ns 50%~50% @card

T RC 80 8.45 ns 50%~50% @card

T CEH 100 24 ns 50%~50% @card

T REH 20 24 ns 50%~50% @card

T WHR 50 60 ns 50%~50% @card

T AR1 100 120 ns 50%~50% @card

T AR2 50 80 ns 50%~50% @card

T CR 100 250 ns 50%~50% @card

TM

ps. All symbols used are followed xD-Picture Card Card Specification Vision 1.2

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 14 NDA Required

JMB385

4. Pin Description

JMB385 is LQFP48 package. The pin list table and pin floorplan of JM385 is list as below.

A: Analog, D: Digital, I: Input, O: Output, Z: I/O, L: Internal pull-low, H: Internal pull-low, S: Smittch Trigger Input,

OD: Open-Drain, PWR: Power, GND: Ground

4.1 Pin List Table & Floorplan

Table 4.1 Pin List Table of JMB385 Version D

No. Pin Name No. Pin Name No. Pin Name No. Pin Name

1 XRSTN 13 CPPEN 25 MDIO12 37 DV18

2 XTEST 14 SEECLK 26 MDIO11 38 NC

3 APCLKN 15 CR1_CD1N 27 MDIO10 39 SEEDAT

4 APCLKP 16 CR1_CD0N/WAKEN 28 MDIO9 40 MDIO7

5 APVDD 17 CR1_PCTLN 29 MDIO8 41 MDIO6

6 APGND 18 DV18 30 NC 42 MDIO5

7 APREXT 19 DV33 31 GND 43 MDIO4

8 APRXP 20 DV33 32 GND 44 DV33

9 APRXN 21 CR1_LEDN 33 GND 45 MDIO3

10 APV18 22 MDIO14 34 NC 46 MDIO2

11 APTXN 23 MDIO13 35 NC 47 MDIO1

12 APTXP 24 GND 36 NC 48 MDIO0

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 15 NDA Required

JMB385

Figure 4.1 Pin Floorplan of JMB385 Version D

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 16 NDA Required

JMB385

4.2 System Control Pin

Table 4.2 System Control Pin

Signal Location Type Description

XRSTN 1 DIHS Whole Chip Reset#. Low-active.

It is used to reset whole chip except PLL.

XTEST 2 DIL Test Mode Enable. High-active.

It enables Testing and Debug mode. All Testing and Debug modes definition is

referenced in Section 5.2.

CPPEN 13 DO CPPEN for D3E Mode.

8mA It is low active to inform NB or SB that JMB38X hopes to wake from D3E

mode.

SEECLK 14 DOH JMB385 Serial Interface Clock. This serial interface has multiple functions

8mA Serial EEPROM Master: Clock Output

SMBUS Slave (address h’46) on SMBUS: Clock Output

SEEDAT 39 DZH Serial Interface Data.

8mA Serial EEPROM Master: Data Input/Output

SMBUS Slave (address h’46) on SMBUS: Data Input/Output

CR1_LEDN 21 DOH 1st Card Slot LED Indicator. It is CMOS push/pull type only.

(GPIO0) 8mA LED Indicator when SD/MMC/MS/xD Card access. Please reference

Application Schematic for detail LED setting.

CR1_PCTLN 17 DO 1st Card Slot Power Line. It is driving power for SD/MMC/MS/xD Card

(GPIO1) (PWR) Reader directly. Please note that at least 20 mil trace width is necessary and

250mA needs 10uF and 0.1uF de-coupled capacitors near pin.

CR1_CD0N/ 16 DIH 1st Card Slot Card Detection Pin 0/ NB or SB wakes JMB38X (see note)

WAKEN Pin status: Show at E0h.[11] when XRSTN de-assert to select mode

(GPIO2) SD/MMC: Card Detection Pin for SD/MMC Card insertion (low active)

SD/MMC: (CR1_CD1N,CR1_CD0N) = 2’b10

xD: (CR1_CD1N,CR1_CD0N) = 2’b00

Note: Please reference D3E Application Note for “NB or SB wakes

JMB38X” system behavior in detail.

CR1_CD1N 15 DIH 1st Card Slot Card Detection Pin 1.

GPIO3) Pin status: Show at E0h.[10] when XRSTN de-assert to select mode

MS: Card Detection Pin for MS Card access (low active)

MS: (CR1_CD1N,CR1_CD0N) = 2’b10

xD: (CR1_CD1N,CR1_CD0N) = 2’b00

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 17 NDA Required

JMB385

4.3 PCI Express Analog Pin

Table 4.3 PCI Express Analog Pin

Signal Location Type Description

APTXP 12 AO PCI Express Serial Data Transmitter.

It transmits positive output of differential signal.

APTXN 11 AO PCI Express Serial Data Transmitter.

It transmits negative output of differential signal.

APRXP 8 AI PCI Express Serial Data Receiver.

It receives positive input of differential signal.

APRXN 9 AI PCI Express Serial Data Receiver.

It receives negative input of differential signal.

APREXT 7 AI PCI Express External Reference Resistor.

An external 8.2KΩ resistor should be connected and bypass to the APGND.

APCLKP 4 AI PCI Express PHY Differential Clock+ Input.

If it is differential clock signal, The 100MHz signal is from PCI Express finger.

APCLKN 3 AI PCI Express PHY Differential Clock- Input.

If it is differential clock signal, The 100MHz signal is from PCI Express finger.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 18 NDA Required

JMB385

4.4 Card Reader Pin

Table 4.4 Card Reader Pin

Signal Location Type Description

MDIO0 48 DZ 1st Card Slot Digital IO Pin 0.

8mA SD: Data Bus Bit 0

MMC: Data Bus Bit 0

MS: Data Bus Bit 0

xD: Data Bus Bit 0

MDIO1 47 DZ 1st Card Slot Digital IO Pin 1.

8mA SD: Data Bus Bit 1

MMC: Data Bus Bit 1

MS: Data Bus Bit 1

xD: Data Bus Bit 1

MDIO2 46 DZ 1st Card Slot Digital IO Pin 2.

8mA SD: Data Bus Bit 2

MMC: Data Bus Bit 2

MS: Data Bus Bit 2

xD: Data Bus Bit 2

MDIO3 45 DZ 1st Card Slot Digital IO Pin 3.

8mA SD: Data Bus Bit 3

MMC: Data Bus Bit 3

MS: Data Bus Bit 3

xD: Data Bus Bit 3

MDIO4 43 DZ 1st Card Slot Digital IO Pin 4.

12mA SD: Command Line Signal

MMC: Command Line Signal

MS: Bus State Signal

xD: Write Enable (low active) Signal

MDIO5 42 DZ 1st Card Slot Digital IO Pin 5.

12mA SD: Clock Signal

MMC: Clock Signal

MS: Clock Signal

xD: Card Select (low active) Signal

MDIO6 41 DZ 1st Card Slot Digital IO Pin 6.

8mA SD: Write Protection (high active) Signal

MMC: Write Protection (low active) Signal

MS: No used

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 19 NDA Required

JMB385

xD: Write Protection (low active) Signal

MDIO7 40 DZ 1st Card Slot Digital IO Pin 7.

8mA SD: No used

MMC: No used

MS: No used

xD: Command Latch (high active) Signal

MDIO8 29 DZ 1st Card Slot Digital IO Pin 8.

8mA SD: No used

MMC: Data Bus Bit 4

MS: Data Bus Bit 4 (only for MS-Pro HG)

XD: Data Bus Bit 4

MDIO9 28 DZ 1st Card Slot Digital IO Pin 9.

8mA SD: No used

MMC: Data Bus Bit 5

MS: Data Bus Bit 5 (only for MS-Pro HG)

xD: Data Bus Bit 5

MDIO10 27 DZ 1st Card Slot Digital IO Pin 10.

8mA SD: No used

MMC: Data Bus Bit 6

MS: Data Bus Bit 6 (only for MS-Pro HG)

xD: Data Bus Bit 6

MDIO11 26 DZ 1st Card Slot Digital IO Pin 11.

8mA SD: No used

MMC: Data Bus Bit 7

MS: Data Bus Bit 7 (only for MS-Pro HG)

xD: Data Bus Bit 7

MDIO12 25 DZ 1st Card Slot Digital IO Pin 12.

8mA SD: No used

MMC: No used

MS: No used

xD: Read Enable (low active) Signal

MDIO13 23 DZ 1st Card Slot Digital IO Pin 13.

8mA SD: No used

MMC: No used

MS: No used

xD: Ready (high active)/ Busy (low active) Signal

MDIO14 22 DZ 1st Card Slot Digital IO Pin 14.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 20 NDA Required

JMB385

8mA SD: No used

MMC: No used

MS: No used

xD: Address Latch (high active) Signal

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 21 NDA Required

JMB385

4.5 Power/Ground Pin

Table 4.5 Power and Ground Pin

Signal Location Type Description

APVDD 5 PWRI Analog PCI Express PHY Power Supply.

It is 1.8V power pins and should be bypassed to ground by a 10uF, 0.1uF &

1000pF capacitance.

APV18 10 PWRI Analog PCI Express PHY Power Supply.

It is 1.8V power pins and should be bypassed to ground by 0.1uF capacitance

and shared 10uF with APVDD.

APGND 6 GND Analog PCI Express PHY Ground. It is ground for APVDD & APV18.

DV33 19,20,44 PWRI Digital Power Supply.

It is 3.3V power source and should be bypassed to ground by a 0.1uF

capacitance and share big capacitors with 3.3V main power.

DV18 18,37 PWRO Digital Power Supply.

It is 1.8V power pins and should be bypassed to ground by 0.1uF capacitance

and shared 10uF with APVDD. This power source is generated by internal

Regulator.

GND 24,31,32, GND Ground. It is ground for DV33 and DV18.

33

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 22 NDA Required

JMB385

5. Function Description

JMB385 is a highly integrated single chip. It builds in 2.5GHz PLL and internal regulator to achieve

high-speed serial data transmission. Memory Card Interface that supports SD/MMC/MS/xD creates

feasible storage device connectivity. With 48-pin low pin-count package, it makes easy system application,

especially on NB. Favor to PCI Express bus, high performance and low pin count are major advantages on

hardware viewpoint of JMB385.

From Driver view, JMB385 supports multiple-function mode that includes SD/MMC/MS and xD

functions.

5.1 Block Diagram

The Figure 5.1 shows the Block Diagram of JMB385. Yellow parts define pins of JMB385. Gray part

includes PCI Express PHY and Memory Card pins. Light Green parts define protocol view of PCI Express

and other color parts define protocol view of SD/MMC/MS and xD.

Figure 5.1 Function View of JMB385

Figure 5.2 shows Block Diagram of Card Reader of JMB385. For each host controller of SD/MMC,

MS and xD, they all have one PCI Configuration Space and its Host Controller Register Space. For

registers in PCI Configuration Space, they define general behavior on system. For registers in Host

Controller Register Space, they define specific memory card behavior, just like DMA, Interrupt and Error

handling.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 23 NDA Required

JMB385

Figure 5.2 Block Diagram of Card Reader in JMB385

JMB385 supports 1 set of combo memory card at the same time. Due to pin limitation, first set of

memory card supports SD/MMC/MS MS Duo/MS-HG (1/4/8-bit) and xD. For different memory card, they

usually operate under different working frequency. So, frequency synchronizer is necessary to in-sync

memory card protocol control and internal FIFO control.

Table 5.1 lists all PCI Function List on SD/MMC/MS and xD.

Table 5.1 JMB385 PCI Function List

Part Number JMB385

SD/MMC Function No. Function 0

SD Standard Function No. Function 2

MS Function No. Function 3

xD Function No. Function 4

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 24 NDA Required

JMB385

5.2 Operating Mode Configuration

JMB385 uses XTEST, CR1_CD0N and CR1_CD1N pins to define 4 operation modes. These modes

except Normal are reserved for Testing before JMB385 is shipment.

IDDQ mode is used for testing on power consumption, especially on current leakage. BIST/FL Mode

is BIST mode and Far-end Loopback. After negotiation by protocol of PCI Express, JMB385 transmits an

expected data pattern to opposite DUT, and the opposite DUT transmits its received data patterns directly.

JMB385 compares received data pattern with expected value to report status. At the same time, BIST

module will write/read internal FIFO with predicted pattern to check FIFO.

The last mode is Nandtree. All digital IO pins are chained with NAND type to check mounting status

on EVB with all input data pattern is 1.

Table 5.2 JMB385 Operating Modes

Normal IDDQ BIST/FL Nandtree

XTEST 0 1 1 1

CR1_CD0N x 0 0 1

CR1_CD1N x 0 1 1

5.3 Clocking

There are 5 clock domains existed that is in PCI Express, SD/MMC, MS and xD.

Clock Rate of internal Phase Locked Loop (PLL) of PCI Express is 2.5GHz. The clock rate for

internal parallel bus is 250MHz under 8-bit data bus and 62.5 MHz under 32-bit data bus.

For SD/MMC, the shared clock topology and its maximum clock rate is up to 50MHz. For MS, the

maximum clock rate is up to 60MHz. For xD, the maximum clock rate is up to 25MHz. Table 5.3 shows

the corresponding relationship between them.

Table 5.3 JMB385 Clock Domain List

Clock Domain Maximum Clock rate

PCI Express PHY 250MHz

PCI Express Controller 62.5MHz

SD/MMC Host Controller 50MHz

MS Host Controller 60MHz

xD Host Controller 25MHz

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 25 NDA Required

JMB385

5.4 Reset and Disable Mechanism

There are 3-level reset mechanisms in JMB385, Chip Reset, Protocol Reset and Domain Reset

controlled by internal registers.

JMB385 uses XRSTN pin for Chip Reset that is Fundamental Reset from Pin 11 of Side A on PCI

Express slot. Besides external Chip pin, internal Power-On Reset (POR) signal is also used for Chip Reset.

The latest finishing timing for these signals is final Chip Reset of JMB385. At this time, PCI Express clock

source is already ready.

Another Reset mechanism is Protocol Reset existed in both PCI Express protocol. Protocol Reset of

PCI Express is de-asserted after Configuration.Linkwidth.Accept State and assert again when Detect,

Disable, Hot Reset or Loopback State. When Protocol Reset asserts, some PCI Configuration Register

(00~3F) must be clear to default value to fit PCI-SIG Compliance Testing.

The other Reset mechanism is Domain Reset. All function domains have itself “Reset Register” in

PCI Configuration Register Space. BIOS or Driver can reset each function domains if reset action is

necessary.

JMB385 reserves Disable mechanism for un-used memory card functions. These un-used functions

can be disabled by internal register setting through Software Programming or Serial EEPROM Master

Interface.

5.5 PCI Express Link

JMB385 is compliant with PCI Express Base Specification Revision 1.1. After Chip Reset period,

PCI Express Link Initialization is needed before Host and JMB385 start to communicate with TLP. It

includes PLL Locking, Receiver Detection, Link Training and Configuration with TS ordered set and Data

Link Layer Configuration with initial FC DLLP. Their relations are like con-circle that one step is Ok and

then later step starts.

After clock source of PCI Express is applied, PLL is stable and locking its phase to reference clock

under specific time. During this unstable-clock time period, internal POR is assert to keep Chip Reset of

JMB385. Receiver Detection starts repeating until finding differential 100Ω termination at opposite side

under stable clock. After locking COM code, MAC layer starts to train and configure PCI Express Link.

Through TS ordered set, link number, lane number and some control capability of opposite side are

available for Link Maintain when errors occurred in Physical Layer. When MAC finishes its initial

behavior, link-up status is reporting to Data Link Layer. And Data Link Layer starts its initialization with

initial FC DLLP to exchange FIFO status of opposite side as Flow Control credit value. After these actions,

TLP is starting to communicate each other from BIOS or Driver of Host to get status of JMB385.

There are 2 power management modes of PCI Express. One is PCI-PM from Driver view and another

is ASPM. ASPM is hardware-controlled actions without software effort and makes 2 Link PM State L0 and

L0s existed under D0 state. For PIPE interface of PCI Express PHY, PIPE-PM is combined with PCI-PM

and ASPM. Table 5.4 shows all PM relations and MAC LTSSM State.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 26 NDA Required

JMB385

Table 5.4 PCI-PM, ASPM and PIPE-PM Relation

PCI-PM Link-PM LTSSM PIPE-PM Active Condition Description

D0 L0 L0 P0 Normal operation.

D0 L0s L0s P0 ASPM and ASPM condition are both active

D3HOT L1 L1 P1 Non-D0 code and DLLP PM Protocol are both OK

D3HOT L2/3 Ready L2 P2 TLP PM Message and DLLP PM Protocol are both OK

5.6 D3 Enhancement (D3E) Mode

JMB385 Version B/C/D and JMB387 A/B supports D3 Enhancement (D3E) mode to make the lowest

power consumption when no memory cards inserted. It is very suitable for NB Application to reduce more

power consumption under so-called IDLE mode.

From system view, there are 2 ways to pull D3E_WAKEN signal to inform system that JMB385 is

wake up from D3E mode. One is D3E_WAKEN is connected to GPIO pin of South Bridge with on-board

or on-chip pull high resistor that is must within the same 3.3V Power Domain to avoid current leakage

under System S3 mode. The other is connecting to Embedded Controller on NB or Super IO Controller on

MB that is used to generate an interrupt event to inform system that PCIe link status of JMB385 changes.

If you want to implement D3E mode of JMB385, please directly contact your AE window to get the

fully supporting on HW and BIOS.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 27 NDA Required

JMB385

6. System Programming Interface

There are some Programming interfaces to expansion system application that are Card Reader

Interface, and Software Development Resource.

Card Reader Interface is used to control command and data transfer between memory card and

JMB385. Please reference Compliance List in Chapter 2 for the detail registers programming. GPIO

Interface has dedicated function on JMB385. It controls card detection on combo memory card mechanism,

LED to show up memory card access and external PMOS Power switch for memory cards.

Software Development Resource is included 2 set of Timer with Interrupt mechanism and 2 DW free

spaces to store some extra information between hardware, software and system.

6.1 Card Reader Pin Arrangement

Digital pins named as MDIO of JMB385 has dedicated functions when Card Reader (SD, MMC, MS

or xD) function turns on. The table below describes the full configuration and normal function of MDIO

pins.

Except MDIO pins, there is one IO group that have dedicated function when card Reader (SD, MMC,

MS or xD) function turns on. The table below describes the full configuration and normal function of

GPIO pins.

Table 6.1 Card Reader Pin Configuration and Function Table

Pin Name Default Mode SD/MMC Card MS Card XD Card

MDIO0 SD/MMC/MS/xD SD1_DAT0 MS1_DAT0 XD_DAT0

MDIO1 SD1_DAT1 MS1_DAT1 XD_DAT1

MDIO2 SD1_DAT2 MS1_DAT2 XD_DAT2

MDIO3 SD1_DAT3 MS1_DAT3 XD_DAT3

MDIO4 SD1_CMD MS1_BS XD_WE#

MDIO5 SD1_CLK MS1_CLK XD_CE#

MDIO6 SD1_WP XD_WP#

MDIO7 XD_CLE

MDIO8 MMC_DAT4 MS1_DAT4 XD_DAT4

MDIO9 MMC_DAT5 MS1_DAT5 XD_DAT5

MDIO10 MMC_DAT6 MS1_DAT6 XD_DAT6

MDIO11 MMC_DAT7 MS1_DAT7 XD_DAT7

MDIO12 XD_RE#

MDIO13 XD_R/B#

MDIO14 XD_ALE

CR1_LEDN SD1_LED# MS1_LED# XD_LED#

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 28 NDA Required

JMB385

CR1_PCTLN SD1_PCTL# MS1_PCTL# XD_PCTL#

CR1_CD0 SD1_CD# XD_CD#

CR1_CD1 MS1_CD# XD_CD#

6.2 Software Development Resource

Inside JMB385, there are 2 Software Timer with Interrupt. It is generally used for accurate timeout

control and generate interrupt message for SD, MMC, MS and xD functions by software setting. They are

located at E8h.[31:0] and ECh.[31:0] and have the same meaning in register fields.

Programmer sets proper timeout count value (time base is 256ns) at E8h.[26:0], selects proper

function (SD, MMC, MS or xD) at E8h.[29:28] for this Timer, enable interrupt at E8h.[30], and then

enable Timer at E8h.[31]. When the Timer counts to E8h.[26:0], one interrupt status bit appears at E8h.[27],

and generate interrupt message according to function selection (E8h.[29:28]) and interrupt enable

(E8h.[30]).

There are 2 free double-word locations for development. One is located at F0h.[31:0] and reserved

for Software Development. The other is located at F4h.[31:0] and reserved for Firmware Development.

The detail definition will be final later when Software or Firmware needs to communicate with HW or

Main system BIOS.

6.3 Driver Supporting

JMB385 needs System Driver to initial the best performance through internal registers based on

different platform. JMicron will provide Windows XP/Vista 32/64-bit and MAC OS X driver.

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 29 NDA Required

JMB385

7. Product Information

JMicron uses 12 digits number for part number.

1 2 3 4 5 6 7 8 9 10 11 12

Ex: J M B 3 8 5 - L G E Z 0 D

Part No

The comparison table of numbering

Digit Classification Numbering Definition

1~2 Brand Name JM JMicron

B: Bridge

C: Communication

P: PHY Chip

3 Product Index B,C,P…

S: SOC

V: Video

E: EVB (Evaluation Board)

4~6 Product Serial Number 001~999 A serial no, it’s up to the real situation

7 Assembly Type T, L, S… See the comparison table of assembly type

S: Standard Package

8 Environment Indicate S, G

G: Green Package

9 Bonding Type A~Z Same product has a different bonding, from A~Z

Same product has a code mask change, from

10~11 Code Mask A0~Z9

A0~Z9, ROM-free default is Z0

12 Version Code A~Z Dice Revision (From A to Z)

The comparison table of package type

Numbering Assembly Type

T TQFP

L LQFP

Q QFN

S SOP

N TSSOP

R SSOP

B BGA

JMB385 is fabricated with 0.18um/3.3V CMOS Standard Logic Process with 1.8V and 3.3V power

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 30 NDA Required

JMB385

source that 1.8V power source is generated internally. JMB385 is available in LQFP48 package. Figure 7.1

shows the physical dimension of JMB385.

Figure 7.1 Physical Dimension of JMB385

Copyright © 2008 JMicron Inc. All rights reserved. 2008/12/01

Data Sheet Reversion 1.2 Page 31 NDA Required

You might also like

- 269 3206 DatasheetzDocument264 pages269 3206 DatasheetzGiovanni LorchaNo ratings yet

- JM20337 Datasheet v1.1Document15 pagesJM20337 Datasheet v1.1Mehmet DemirNo ratings yet

- B141ew05-V0 AuoDocument36 pagesB141ew05-V0 AuoTEGUH RIYANTONo ratings yet

- JM20337 Datasheet v1.1Document15 pagesJM20337 Datasheet v1.1k4k4zim100% (1)

- Twn4 Multitech Oem Pcbs Docrev8Document8 pagesTwn4 Multitech Oem Pcbs Docrev8Davidescu IoanNo ratings yet

- B121ew09 V2Document37 pagesB121ew09 V2nuevacuent904No ratings yet

- EL9800e Ver3.02Document31 pagesEL9800e Ver3.02mikeNo ratings yet

- TMS28F512A 12C4FML Texas Instruments PDFDocument56 pagesTMS28F512A 12C4FML Texas Instruments PDFR BauerNo ratings yet

- Z8 MicrocontrollersDocument84 pagesZ8 MicrocontrollersMarco Antonio DamacenoNo ratings yet

- Auo B121EW09 V2 PreDocument37 pagesAuo B121EW09 V2 PreFachry MohamadNo ratings yet

- B154ew01 V4 AuoDocument37 pagesB154ew01 V4 AuoFranklin JimenezNo ratings yet

- KTD 00782 I ktq45 Users GuideDocument92 pagesKTD 00782 I ktq45 Users Guidesunnlight8No ratings yet

- DE10-Lite User Manual PDFDocument74 pagesDE10-Lite User Manual PDFFelix GonzalezNo ratings yet

- Capturevision Station: User Manual - EnglishDocument38 pagesCapturevision Station: User Manual - EnglishMohammed ElheddadNo ratings yet

- KINO PV D5252 D4252 - UMN - v1.02Document163 pagesKINO PV D5252 D4252 - UMN - v1.02Rafael SoaresNo ratings yet

- REMOTE IO PCI Set-Up For DX200Document7 pagesREMOTE IO PCI Set-Up For DX200Marcelo Brito MicoNo ratings yet

- Smart 5 Boot Block Flash Memory Family 2, 4, 8 MBIT: Advance InformationDocument39 pagesSmart 5 Boot Block Flash Memory Family 2, 4, 8 MBIT: Advance InformationPEIDELUO PEREIRANo ratings yet

- Apple ProRes Bitstream SyntaxDocument39 pagesApple ProRes Bitstream SyntaxMoaz ElgabryNo ratings yet

- B140XW01 V.0Document37 pagesB140XW01 V.0OnionNo ratings yet

- RTS5138 One-LUN USB 2.0 Card Reader Controller DatasheetDocument13 pagesRTS5138 One-LUN USB 2.0 Card Reader Controller Datasheetari factoryNo ratings yet

- S905X3 Public Datasheet HardkernelDocument1,081 pagesS905X3 Public Datasheet HardkernelEnriqueNo ratings yet

- Genesys Logic, Inc.: Revision 1.32 Jul. 15, 2011Document33 pagesGenesys Logic, Inc.: Revision 1.32 Jul. 15, 2011nqrcNo ratings yet

- Z8 Encore! XP F042A Series 8-Pin Development KitDocument18 pagesZ8 Encore! XP F042A Series 8-Pin Development KitKevin GaloNo ratings yet

- FPGA IPUG 02037 2 2 CNN Accelerator IP CoreDocument28 pagesFPGA IPUG 02037 2 2 CNN Accelerator IP Corepaul leeNo ratings yet

- Okidata - Pacemark 3410 Service ManualDocument249 pagesOkidata - Pacemark 3410 Service Manual19jayster84No ratings yet

- LM555 Timer: 1 Features 3 DescriptionDocument25 pagesLM555 Timer: 1 Features 3 DescriptionAugusto PolveriniNo ratings yet

- lm555 PDFDocument27 pageslm555 PDFsurinder singhNo ratings yet

- 555 Pagina FabricanteDocument24 pages555 Pagina FabricanteDavid Asensio IbarraNo ratings yet

- LM 555Document25 pagesLM 555api-276948567No ratings yet

- lm555 PDFDocument25 pageslm555 PDFAndes PutraNo ratings yet

- LM555 Timer: 1 Features 3 DescriptionDocument27 pagesLM555 Timer: 1 Features 3 DescriptionKarim KarimmNo ratings yet

- lm555 PDFDocument25 pageslm555 PDFrenatoNo ratings yet

- Intel 82855 MBDocument56 pagesIntel 82855 MBSaasnalan PalanisamyNo ratings yet

- Manuale Pitney Piegatrice NuovaDF800 - 900serviceDocument84 pagesManuale Pitney Piegatrice NuovaDF800 - 900servicegiuseppe mocciaNo ratings yet

- PA28F400B5T80Document44 pagesPA28F400B5T80Andrey TushkanovNo ratings yet

- Technical Note BRT - TN - 004 Bridgetek Example IC PCB FootprintsDocument21 pagesTechnical Note BRT - TN - 004 Bridgetek Example IC PCB FootprintsMehmet KibarNo ratings yet

- Intel D81EEA Technical Product SpecificationDocument126 pagesIntel D81EEA Technical Product SpecificationFarid IrwanNo ratings yet

- H 3600 Series User ManualDocument85 pagesH 3600 Series User ManualBeltazor HellboyNo ratings yet

- Fuji FRENICeco PDP ManualDocument36 pagesFuji FRENICeco PDP ManualHamadi Ben SassiNo ratings yet

- Realtek: For V4L ConfidentialDocument53 pagesRealtek: For V4L Confidentialstmacount stmacountNo ratings yet

- Arm11 Mpcore r1p0 TRMDocument730 pagesArm11 Mpcore r1p0 TRMAman SainiNo ratings yet

- NY8B062D_v1.8Document115 pagesNY8B062D_v1.8webebe9888No ratings yet

- Tinno Ev730 Service ManualDocument44 pagesTinno Ev730 Service ManualEdgar Jose Aranguibel MorilloNo ratings yet

- RM68090 Datasheet v04 20110427Document123 pagesRM68090 Datasheet v04 20110427Bojan PapuckoskiNo ratings yet

- Cortex - M3: Technical Reference ManualDocument133 pagesCortex - M3: Technical Reference ManualDuc Huy LeNo ratings yet

- PCI 8134+PCI 8134A - 50 11173 1000 - 300 - en PDFDocument175 pagesPCI 8134+PCI 8134A - 50 11173 1000 - 300 - en PDFAnonymous uWvAodfNo ratings yet

- Intel DG965OT Desktop BoardDocument96 pagesIntel DG965OT Desktop BoardshorinryuNo ratings yet

- PDS-16002 JMS578 Datasheet (Rev. 1.01)Document23 pagesPDS-16002 JMS578 Datasheet (Rev. 1.01)kok86845No ratings yet

- Zilog DatasheetDocument276 pagesZilog DatasheetJed PNo ratings yet

- Fido1100 JTAG Interface PDFDocument33 pagesFido1100 JTAG Interface PDFVictor Avendaño GrilloNo ratings yet

- Jms 580Document10 pagesJms 580Arya RamadhanNo ratings yet

- Datasheet pdf - http://www.DataSheet4U.netDocument26 pagesDatasheet pdf - http://www.DataSheet4U.netMugia LanaNo ratings yet

- UMC 180nm MM RF FDK CDN Userguide VB04 PB 3Document260 pagesUMC 180nm MM RF FDK CDN Userguide VB04 PB 3VLSISD36 Edwin DominicNo ratings yet

- Specification for 14-inch HD LCD with LED BacklightDocument34 pagesSpecification for 14-inch HD LCD with LED BacklightweyoNo ratings yet

- B156XW04 V.8Document35 pagesB156XW04 V.8Juan Carlos SrafanNo ratings yet

- ZXSDR BS8900A L200 Product DescriptionDocument43 pagesZXSDR BS8900A L200 Product DescriptionK OuertaniNo ratings yet

- Datasheet Red - DVR Rtl8211f-Cg c187932Document69 pagesDatasheet Red - DVR Rtl8211f-Cg c187932Luis Felipe CasasNo ratings yet

- Triple Play: Building the converged network for IP, VoIP and IPTVFrom EverandTriple Play: Building the converged network for IP, VoIP and IPTVNo ratings yet

- Complex Numbers: Problem-SolvingDocument2 pagesComplex Numbers: Problem-SolvingK TariNo ratings yet

- Hemi EngineDocument23 pagesHemi Enginesurendrabarwar7No ratings yet

- Stheory Balagtas Activity Lesson 15Document6 pagesStheory Balagtas Activity Lesson 15xVlad LedesmaNo ratings yet

- Science Clinic Gr10 Chemistry Questions 2016Document44 pagesScience Clinic Gr10 Chemistry Questions 2016BhekiNo ratings yet

- Quasi VarianceDocument2 pagesQuasi Varianceharrison9No ratings yet

- FY&ZM JofHY (ASCE) 1943-7900Document12 pagesFY&ZM JofHY (ASCE) 1943-7900DM1988MM1No ratings yet

- Engineering Graphics (046) Marking Scheme: Sample Question Paper (2017-18)Document8 pagesEngineering Graphics (046) Marking Scheme: Sample Question Paper (2017-18)RaghuSrinivasanNo ratings yet

- Propulsion ResistanceDocument14 pagesPropulsion ResistanceEduardo LopesNo ratings yet

- 34 DuPont MECS Startup Shutdown Procedure For MET Plants Sulfuric AcidDocument4 pages34 DuPont MECS Startup Shutdown Procedure For MET Plants Sulfuric AcidLouis Andree Bujanda RufattNo ratings yet

- Engineering Physics Question BankDocument10 pagesEngineering Physics Question BankReji K DhamanNo ratings yet

- Astrology, Believe It or Not - OCRDocument155 pagesAstrology, Believe It or Not - OCRShashwat Singh Pokharel100% (2)

- Staad FoundationDocument25 pagesStaad FoundationAnonymous nwByj9L100% (2)

- Module 11A-09 Turbine Aeroplane Aerodynamics, Structures and SystemsDocument133 pagesModule 11A-09 Turbine Aeroplane Aerodynamics, Structures and SystemsИлларион ПанасенкоNo ratings yet

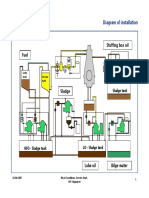

- Westfalia Separator Installation DiagramDocument68 pagesWestfalia Separator Installation DiagramOno Jr Araza100% (3)

- Data Communication & Computer NetworksDocument32 pagesData Communication & Computer NetworksMuhammad NadeemNo ratings yet

- BIS 14665 Part 2Document6 pagesBIS 14665 Part 2Sunil ChadhaNo ratings yet

- Math 2nd Year CompleteDocument369 pagesMath 2nd Year CompleteJabir Ali Siddique100% (1)

- E8244 Ahu Catalogue 2014 PDFDocument174 pagesE8244 Ahu Catalogue 2014 PDFmurugesanNo ratings yet

- Experiment List (FEE)Document5 pagesExperiment List (FEE)bpkeleNo ratings yet

- Theory of Financial Decision Making PDFDocument392 pagesTheory of Financial Decision Making PDFEmmanuel K'pkorNo ratings yet

- Petroleum GeomechanicsDocument35 pagesPetroleum GeomechanicsAnonymous y6UMzakPW100% (1)

- FOUNDATION REPAIR AND REGROUT FOR BODYMAKER AT CARNDAUD METALBOX SINGAPOREDocument15 pagesFOUNDATION REPAIR AND REGROUT FOR BODYMAKER AT CARNDAUD METALBOX SINGAPORETrúc NguyễnNo ratings yet

- Iota Tangle 2.0: Toward A Scalable, Decentralized, Smart, and Autonomous Iot EcosystemDocument8 pagesIota Tangle 2.0: Toward A Scalable, Decentralized, Smart, and Autonomous Iot EcosystemMarcos PonceNo ratings yet

- Qualcomm Snapdragon 660 Mobile Platform Product BriefDocument2 pagesQualcomm Snapdragon 660 Mobile Platform Product BriefTuxInfoNo ratings yet

- Lesson Statement Sheet.Document2 pagesLesson Statement Sheet.Anya AshuNo ratings yet

- SQL Injection Attack Detection and Preve PDFDocument12 pagesSQL Injection Attack Detection and Preve PDFPramono PramonoNo ratings yet

- Week 2Document11 pagesWeek 2KISHANo ratings yet

- EEE415 Digital Image Processing: Frequency Domain FilteringDocument50 pagesEEE415 Digital Image Processing: Frequency Domain FilteringFAISAL NAWABNo ratings yet

- Deep Glow v1.4.6 ManualDocument6 pagesDeep Glow v1.4.6 ManualWARRIOR FF100% (1)

- h2 PR Final Key SP 13Document3 pagesh2 PR Final Key SP 13George ConstantinouNo ratings yet