Professional Documents

Culture Documents

10 1 1 126

Uploaded by

ravi_phyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 1 1 126

Uploaded by

ravi_phyCopyright:

Available Formats

1 of 4

Array Hybrid Multiplier versus Modified Booth Multiplier: Comparing Area and

Power Consumption of Layout Implementations of Signed Radix-4 Architectures

Leonardo L.de Oliveira Eduardo Costa Sergio Bampi

UFSM/PPGEE – Santa Maria, Brazil UCPel, Pelotas, Brazil UFRGS,P.Alegre,Brazil

leonardo@mail.ufsm.br ecosta@atlas.ucpel.tche.br bampi@inf.ufrgs.br

João Baptista José Monteiro

UFSM/PPGEE – Santa Maria, Brazil IST/INESC,Lisboa,Portugal

batista@inf.ufsm.br jcm@inesc.pt

Abstract- In this paper, we describe the fully automated custom A. Hybrid Code

layout implementations of two architectures for signed The idea of the hybrid code is to split the operands in

multiplication. Performance comparisons between the two, groups of m-bits, encode each group using the Gray code and

namely in terms of their power consumption and area estimation to use the Binary approach to propagate the carry between the

are provided for 8 and 16-bit operands. The first architecture groups. In this way, a compromise between the minimum

consists of a signed array multiplier that uses a radix-4 hybrid Hamming distance between consecutive values of the Gray

encoding to reduce the partial product lines and switching code and the minimum bit dependency of the Binary code is

activity in the data buses. This new arithmetic operand encoding achieved [3]. Table I shows the 2’s complement Hybrid

was recently proposed in [4], however only results at the logic encoding for 4-bit numbers and m=2.

level were presented. The second architecture implemented was

the widely used modified Booth multiplier [9]. The layout of TABLE I

both multipliers was generated by an automatic layout synthesis 2’S COMPLEMENT HYBRID CODE REPRESENTATION FOR M=2.

tool called TROPIC [10]. We compare the layout Dec Hyb Dec Hyb Dec Hyb Dec Hyb

implementations in terms of area and power, as well as provide

0 0000 4 0100 -8 1100 -4 1000

comparisons to first-order area estimates done in the logic design 1 0001 5 0101 -7 1101 -3 1001

phase. The results show that the new hybrid array multiplier 2 0011 6 0111 -6 1111 -2 1011

can be significantly more efficient, with close to 30% power 3 0010 7 0110 -5 1110 -1 1010

savings. B. Radix-2m Hybrid Array Multiplier

I. INTRODUCTION The radix-2m operation in 2’s complement representation is

Multiplier modules are common to many DSP applications. given by Equation 1.

W

−1

The fastest types of multipliers are parallel multipliers. m

Among these, the Wallace multiplier [13] is among the R × Y = R′ × Y ′ − R′yW −1 yW −1 2W − m − rW −1rW −1 ∑ y j 2W − m + j

m m

j=0

fastest. However, they do not have such a regular structure as (1)

the conventional array [8] or Booth [9] multipliers. Hence, This operation is illustrated in Fig. 1. For the case of radix-

when layout regularity, high-performance and low power are 4 we have a conversion from hybrid code to binary code at

primary concerns, Booth multipliers tend to be the primary the input of values. After that, the bits are calculated to

choice [2], [5], [7], [9], [11]. In this paper, we present layout binary encoding. Finally, at the end of multiplication, the

implementations for both the Modified Booth multiplier and final value is converted to hybrid encoding.

the new array multiplier using hybrid code proposed in [4]. HYBRID

REPRESENTATION -1 3 1 2 Decimal Representation

BINARY REPRESENTATION

We synthesize the multipliers by using an automatic synthesis 10 10 01 11 (-10)

11110110

10

11110110

11

X X

tool named Tropic [10]. In order to compare the Modified X

-2 1 3 2

0100 Type I

0110 Type I

sign extension

Booth and the hybrid array architectures, both using radix-4, 11 01 10 11 (-98) 0010

0110

Type I

Type I

0011

1001

Type I

Type I

the ELDO which is a spice-like simulator and is part of the (1 0)1 1 1 1 1 0 1 1 0 0 + 1110 Type II

+ 1101 Type II

Mentor Graphics environment, was used. The results show + 1111100010 1111101100 1111100010

that the new array multiplier is significantly more efficient, (1 0)1 1 1 1 0 1 1 1 0 1 0 0

+ 1111110110

saving more than 30% in power consumption. The power

(1 0)1 1 1 1 1 0 1 1 0 1 0 1 0 0

reduction presented by the new array multiplier is mainly due 11110110 11110110

+ 0000010100 10 01

to the lower logic depth, which has a large impact in the X

Type II

X

Type I

00 00 00 111101 0100 1100 0010

amount of glitching in the circuit. We should stress further 1110

1010

Type II

Type II

0001

0011

Type I

Type I

that, in contrast to the architecture presented in [4], increasing EXOR

- 0010 Type III

+ 1111 Type II

the radix for the Booth architecture is a difficult task, thus not 0000010100 1111110110

being able to leverage from the potential savings of higher 00 00 00 10 10 01 01 00

radices. This paper is organized as follows. The next section 214x0 212 x0 210 x0 28x3 26x3 24x1 22x1 20x0

HYBRID

REPRESENTATION

briefly describes the radix-4 hybrid code, the hybrid array

multiplier and the modified Booth multiplier. After this, we 0 + 0 + 0 + 768 + 192 + 16 + 4 + 0 = (980)

describe the design methodology, the fully automated layout

synthesis and how area and power results were obtained. Fig. 1 2’s complement 8-bit wide radix-4 hybrid

Comparisons between the radix-4 hybrid array multiplier multiplication

architecture and the Modified Booth, for both switch level For the W-m least significant bits of the operands unsigned

and electrical level are presented following the sequence. multiplication can be used. The partial product modules at

Finally we conclude this paper, discussing the main the left and bottom of the array need to be different to handle

contributions and future work. the sign of the operands. For this architecture, three types of

II. 2’S COMPLEMENT MULTIPLIERS modules are needed as shown in Fig. 3. Type I are the

unsigned modules. Type II modules handle the m-bit partial

In this section, we summarize the methodology of [4] for product of an unsigned value with a 2´s complement value.

the generation of regular structures for arithmetic operators Finally, Type III are modules that operate on two signed

using signed radix-2m representation and hybrid encoding. values.

2 of 4

Y7Y6 R7R6 Y5Y4 R7R6 Y3Y2 R7R6 Y1Y0 R7R6 Y7Y6 R5R4 Y5Y4 R5R4 Y3Y2 R5R3 Y1Y0 R5R3 Y7Y6 R3R2 Y5Y4 R3R2 Y3Y2 R3R2 Y1Y0 R3R2 Y7Y6 R1R0 Y5Y4 R1R0 Y3Y2 R1R0 Y1Y0 R1R0

2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2

* * * *

Type II Type I Type I Type I

2 2 2 2 2 2 2

* * * * + + + +

1 1 1

Type II Type I Type I Type I

2 2 2 2 2 2 2 2 2 2 2

* * * * + + + +

Type II Type I Type I Type I 1 1 1

2 2 2 2 2 2 2 2 2 2 2 2

* * * * + + + +

Type III Type II Type II Type II 1 1 1

sign extension

2 2 2 2 2 2 2 2 2 2 2 2

- - - - + 1 + 1 + 1 + 1 +

1 1 1

2 2 2 2

2 2 2 2 2

sign extension

+ 1 + 1 + 1 + 1 +

2 2 2 2

sign extension

+ 1 + 1 + 1 + 1 +

2 2 2 2 2 2 2 2

P15P14 P13P12 P11P10 P9P8 P7P6 P5P4 P3P2 P1P0

Fig. 2 8-bit wide 2’s complement radix-4 array multiplier.

perform addition-subtraction-no operation and controlled left-

shift of the bits of the multiplicand. Besides taking more area,

TYPE TYPE

II I this complexity also makes it more difficult to increase the

radix value in the Booth architecture.

R7..R0 0 Y7..Y0

8 1 8

TYPE TYPE II R1R0

III MULTIPLIER ENCODER MULTIPLEXER

2 2

R1 1 9

m

Fig. 3 General structure for a 2’s complement radix-2 3 R3R2R1 +

multiplier. Y7..Y0 8 7

ENCODER MULTIPLEXER

2

9

1 R3

Only one Type III module is required for any type of

multiplier, whereas (2 m − 2) Type II modules and ( m − 1)

W W 2 +

3 R5R4R3 Y7..Y0 8 7

ENCODER MULTIPLEXER

Type I modules are needed. We present a concrete example 2

1 R5 9

for W=8 bit wide operands using radix-4 (m=2) in Fig. 2.

+

7

Y7..Y0 8

C. Modified Booth 3 R7R6R5

ENCODER MULTIPLEXER

2

The radix-4 modified Booth algorithm has been presented 1 R7

9

in [9]. In this architecture it is possible to reduce the number +

of partial products by encoding the two’s complement 1 7 2 2 2

multiplier. In the circuit the control signals (0, +Y, +2Y, -Y

P15 P14 P13..P6 P5P4 P3P2 P1P0

and –2Y) are generated from the multiplier operand Y for

each 3-bit group. A multiplexer produces the partial product Fig. 5 8-bit Modified Booth Architecture.

according to the encoded control signal.

As can be observed in Fig. 5, for an 8-bit architecture, 4

One of the main problems in the modified Booth multiplier encoders and 4 multiplexers are necessary in order to

is the generation of the 2´s complement for the multiplicand calculate the partial product terms. The multiplexers produce

term. This is calculated by each multiplexer shown in the the multiplicand term according to the 3 bits that are

example of Fig. 4 for an 8-bit wide. generated in the encoder circuit. The partial product terms are

MD 1 0 1 1 0 1 1 1 (-73) 1 0 1 1 0 1 1 1 0 (2*MD) shifted by the adders, which are also used to produce the final

MR 0 1 0 1 1 0 1 0(0) (+90) 0 0 1 0 0 1 0 0 1 (-MD)

0 1 0 0 1 0 0 1 0 (-2*MD)

result.

III. DESIGN METHODOLOGY

10 0 0 0 0 0 0 0 0 0 0 (PP)

10 1 01 001 001 0 In this section, we present the design flow for the layout

01 1 implementation of the multipliers based on an automatic

0 0 0 1 0 0 1 0 0 1 0 (shift)

01 0

00 100 100 1

layout generation tool called TROPIC [10].

0 0 0 0 1 1 0 1 1 0 1 1 0 (shift)

A. Design Flow

10 110 111 0

1 1 1 1 0 0 0 1 0 0 1 0 1 1 0 (shift) Fig. 6 shows the design flow used in the logic [3], in gray,

11 011 011 1 and layout synthesis of the multipliers. In this figure we

(-6570) 1 1 1 1 0 0 1 1 0 0 1 0 1 0 1 1 0 (shift)

present both our methodology in black and the methodology

used in [4], in grey, for the analysis of the multipliers.

Fig. 4 Example of an 8-bit multiplication using Modified

Booth algorithm The multiplier circuits were described in a Berkeley Logic

Common to both architectures is that, at each step of the Interchange Format (BLIF). Thus, BLIF files are used as

algorithm, two bits are processed. However, the basic Booth input of the design flow, as can be observed in Fig. 6. In [3],

cells are not simple adders as in the array multiplier, but must where the multipliers were synthesized in a logic level, the

3 of 4

SIS tool [12] is used in order to estimate area of the

multipliers. In the methodology of [3], the power

consumption of the multipliers was estimated using the

switch-level simulator SLS [6]. Thus, it was necessary to use

a converter from BLIF to SLS format. For the power

estimation, different types of vectors, in SLS format, were

used in the primary inputs of the multipliers. For the

synthesis of the multipliers implemented in this work, the

Tropic tool is used. This tool uses a sim format as input and

performs an automatic synthesis of the layout of the circuit.

Thus, a converter from BLIF to sim format has been

developed in this work. In the Tropic environment, the total

area and the number of transistors of the circuits are also

estimated. Since the Tropic tool generates the widely used cif

format, the resulting circuit layout can be visualized with

Mentor Graphics IC Station tool (Mentor Graphics

Environment). Extracted SPICE netlist files were simulated in

the Mentor Graphics environment for power consumption

estimation at the back-annotated electrical level. The ELDO

electrical simulator was used. Power simulation is dependent on a

set of input vectors. In this paper we compare results for two sets

of vectors: random and representing sinusoidal signal. These

vectors were generated for the SLS tool binary digit format and Fig. 7 Layout of an 8-bit hybrid multiplier generated

converted into a set of input vectors in SPICE format for transient automatically by TROPIC.

analysis also using a tool made especially for this project (Gerabits

Converter). IV. PERFORMANCE COMPARISONS

.blif file In this section, we present area and power results for the

multiplier architectures after layout, both W=8 and 16 bit-

wide operands. The modified Booth and the hybrid array

BLIF2SIM TOOL

multiplier proposed in [4] are compared. In the design a

SIS

ENVIRONMENT

HCMOS 0.25µm technology is used. We set the number of

AREA .sim file cell bands generated by TROPIC such that the aspect ratio

width/height close to 1 was obtained.

IC STATION TROPIC

VISUALIZATION AREA Area results were obtained using the TROPIC tool and are

presented both in terms of total area and in terms of number

BLIF2SLS

of transistors. Automatic layout compaction is not used in

.cif file

TOOL this design. Total average power is presented and was

obtained by ELDO simulations. Real trace input signals and a

SLS VECTORS EXTRACTION random pattern signal with 500 input vectors was used. The

GENERATOR

real trace signal represents two sinusoidal signals with 90

spice file degrees phase difference. In these simulations we have used

GERABITS Vdd=2.5V and f=50MHz frequency operation. We have also

CONVERTER

compared our results with those reported in [4], considering

SLS TOOL ELDO

POWER ESTIMATION POWER ESTIMATION 16-bit architectures and for random pattern input vectors.

A. Area Results

Fig. 6 Design tools for synthesis and power and area

estimation. In the Booth multiplier, an encoding scheme is used in

order to reduce the number of stages in multiplication. Two

B. TROPIC Layout Generation Tool bits of multiplication are performed at once and thus the

multiplier requires half the stages. In the hybrid array

Tropic is an automatic synthesis tool that is used in this work in multiplier proposed in [4] the number of stages can be

order to generate the multiplier layout circuits. It is a macro-cell reduced by more than half while the regularity can be kept as

generator, i.e., the complete circuit is generated. This tool uses a in the pure array multiplier. Table II presents area results for

specific input syntax to describe transistor netlists. The static 8-bit radix-4 Booth and the new hybrid array multiplier

CMOS gates layout is automatically generated with up to 3 metal proposed in [4], both implemented in layout level.

layers. The main features of the layout style are: linear matrix

layout style, where each cell row is composed of two horizontal TABLE II

diffusion strips, and the width of the transistors is orthogonal to the AREA RESULTS FOR 8-BIT HYBRID ARRAY AND MODIFIED BOOTH RADIX-4

diffusion strips; over the cell routing is implemented with 3 metal MULTIPLIER ARCHITECTURES.

layers and stacked contacts, reducing the routing area; layout 8-bit multiplier

Parameter

without compaction is used (cif format); the complete parasitic Booth Hybrid Diff(%)

capacitance evaluation after layout synthesis is performed; simple Number of transistors 2542.0 3418 +34.5

technology files are used to describe design rules (28 rules) and Width (µm) 225.4 276.45 +22.6

parasitic capacitances (26 rules). Before the layout synthesis of the Height(µm) 221.0 258.6 +17.0

circuits, it is necessary to set the width and length of the transistors Total area (mm2) 0.04982 0.07149 +43.5

in a cell library. Additionally, we have to specify parameters of the

technology and the number of bands. This last parameter is useful As can be observed in Table II, the hybrid array multiplier

to set the aspect ratio width/height. Fig. 7 shows the layout for the presents the highest area and number of transistors values. The

8-bit array multiplier, which was generated automatically by same results can be observed in Table III, for 16-bit multipliers.

Tropic tool. This occurs due to the fact that the partial product lines operate on

group of m bits and the basic multiplier elements, which compose

4 of 4

the modules for the product terms, are slightly more complex. As glitches generated in the modified Booth makes this architecture

can be compared in Table II and Table III, a larger area results for more power consuming, which is captured with the SLS simulator.

both the 8 and 16-bit array multipliers we proposed. This validates the results reported in [4] for the gate level design.

TABLE III

V. CONCLUSIONS

AREA RESULTS FOR 16-BIT HYBRID ARRAY AND MODIFIED BOOTH RADIX-4

MULTIPLIER ARCHITECTURES. We have described the layout implementation of a new hybrid

16-bit multiplier array multiplier that operates in 2´s complement numbers using

Parameter

Booth Hybrid Diff(%) radix-2m encoding. The signed radix-2m hybrid array multiplier we

Number of transistors 10064 14066 +39.8 proposed exhibits much lower power consumption than the

Width (µm) 468.7 520 +10.9 modified Booth multipliers. The power saving have reached up to

Height(µm) 463.4 594.4 +28.3 32% considering 16-bit architectures and a random pattern input

Total area (mm2) 0.2172 0.30909 +42.3 vector. Comparison of the logic and electrical level estimates were

done and support that the modified Booth multiplier consumes

more power when glitching activity is correctly simulated.

B. Power Results We combined both academic and commercial tools in this

As observed in [1], the major sources of power dissipation in design and power estimation. Delay and silicon results are being

multipliers are spurious transitions and logic races that flow experimentally tested and will be shown in future work.

through the circuit. Thus, the significantly less amount of spurious

transitions in the new array multiplier justifies the gain in power ACKNOWLEDGMENT

when compared against the Booth multiplier, as observed in Table This research was partially supported by the CNPQ

IV and Table V, for 8 and 16-bit circuits respectively. Also (Brasília, Brazil) and FCT (Portugal) foundations for R&D

noticeable in these tables, the array and Booth multipliers present support.

more power reduction when using a sinusoidal waveform as input.

This occurs due to the larger degree of correlation between input REFERENCES

samples, leading to less abrupt variations, hence a smaller number [1] Callaway, T.; Swartzlander, E. Optimizing multipliers for

of input bits toggling. As observed in [4], the new hybrid array WSI. In Fifth Annual IEEE International Conference on Wafer

multiplier presents less logic depth due to the more balanced paths Scale Integration, pages 85-94, 1993.

to the basic blocks that compose the array architecture. This

contributes for improvement in power reduction because of the [2] Cherkauer, B; Friedman, E. A Hybrid Radix-4/Radix-8 Low

less generation of useless transitions. Power, High Speed Multiplier Architecture for Wide Bit

Widths. In IEEE International Symposium on Circuits and

TABLE IV Systems, volume 4, pages 53–56, 1996.

POWER RESULTS FOR 8-BIT HYBRID ARRAY AND MODIFIED BOOTH. [3] Costa E. da; Monteiro J., and S. Bampi. Power Efficient

8-bit multiplier Arithmetic Operand Encoding. In Proceedings Symposium on

Vectors Integrated Circuits and Systems Design, pages 201–206, 2001

Booth (mW) Hybrid (mW) Diff(%)

Sinusoidal 6.5 3.8 -41.5 [4] Costa E. da; Monteiro J., and S. Bampi. A New Architecture for

Random pattern 14.5 10.1 -30.3 2's Complement Gray Encoded Array Multiplier. In

TABLE V

Proceedings Symposium on Integrated Circuits and Systems,

pages 14-19, 2002

POWER RESULTS FOR 16-BIT HYBRID ARRAY AND MODIFIED BOOTH..

16-bit multiplier

[5] Gallagher, W. and Swartzlander, E. High Radix Both

Vectors Multipliers Using Reduced Area Adder Trees. In Twenty-

Booth (mW) Hybrid (mW) Diff(%)

Eighth Asilomar Conference on Signals, Systems and

Sinusoidal 67.2 42.9 -36.2

Random pattern 83.0 56.4 -32.0

Computers, volume I, pages 545-549, 1994.

[6] Genderen, A. J. SLS: An Efficient Switch-Level Timing

It is also important observe the results obtained in [4] with the Simulator Using Min-Max Voltage Waveforms. Proceedings of

results obtained in our work in terms of way of simulation. In [4], VLSI Conference, pages 79-88, 1989.

power consumption of the multipliers was estimated using the SLS [7] Goto, G.; et al. A 4.1-ns Compact 54 x 54-b Multiplier Utilizing

switch-level simulator, where glitching activity is taken into Sign-Select Booth Encoders. IEEE Journal of Solid-State

account. Moreover, at the logic level power results were obtained Circuits, 32:1676-1682, 1997.

by using a random pattern input signal with 10,000 input vectors. [8] Hwang, K. Computer Arithmetic - Principles, Architecture and

Area was estimated in SIS [12] environment and the results were Design. John Wiley & Sons, 1979.

presented in terms of number of literals, which is approximately [9] Khater, I.; Bellaouar, A.; Elmasry, M. Circuit Techniques for

half of the number of transistors CMOS Low-Power, High-Performance Multipliers. IEEE

TABLE VI Journal of Solid-State Circuits, 31:1535-1546, 1996.

COMPARISON BETWEEN ELECTRICAL/LOGIC SIMULATIONS (16-BIT). [10] Moraes, F. A Virtual CMOS Library Approach for Fast Layout

Parameter Logic Level Electrical Level Synthesis. In: IFIP TC10 WG10.5 International Conference on

Area (number Very Large Scale Integration, 10, pages 415-426, 1999.

+35.8% +42.3%

of transistors) [11] Seidel P., Mcfearin, L. and MATULA D. Binary Multiplication

Power (mW) -31.3% -32.0% Radix-32 and Radix-256. In 15th Symposium. on Computer

Arithmetic, pages 23–32, 2001.

Table VI shows area and power percentage changes between

the new hybrid array and modified Booth multipliers. The [12] Sentovich, E. and et al. SIS: A System for Sequential Circuit

estimates at the logic level and after layout correlate extremely Synthesis. Technical report, University of California at

Berkeley, UCB/ERL – Memorandum nº M92/41, 1992.

well for both area and power. Area estimates at the logic level is

just the number of literals coming from logic synthesis. The [13] Wallace, C. A Suggestion for a Fast Multiplier. IEEE

relative power estimations are fairly close. The larger number of Transactions on Electronic Computers, 13:14–17, 1964.

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Temenos On AwsDocument3 pagesTemenos On AwsDeepak Kk100% (2)

- Media Access MethodDocument4 pagesMedia Access MethodYolanda Konde100% (1)

- Exercise 2 - The User InterfaceDocument23 pagesExercise 2 - The User InterfaceManasses juniorNo ratings yet

- New Vulnerabilities in 5G Networks: Altaf Shaik, Ravishankar BorgaonkarDocument7 pagesNew Vulnerabilities in 5G Networks: Altaf Shaik, Ravishankar BorgaonkarИрина ВасиленкоNo ratings yet

- Mysql Architecture GuideDocument17 pagesMysql Architecture GuideKramer KramerNo ratings yet

- Features: Intel Celeron N2930/J1900 Quad-Core™ Soc Fanless Signage Platform With Advanced Nvidia Geforce GT 730M GraphicsDocument2 pagesFeatures: Intel Celeron N2930/J1900 Quad-Core™ Soc Fanless Signage Platform With Advanced Nvidia Geforce GT 730M Graphicsu7788No ratings yet

- Website: Vce To PDF Converter: Facebook: Twitter:: Aca-Cloud1.Vceplus - Premium.Exam.50QDocument15 pagesWebsite: Vce To PDF Converter: Facebook: Twitter:: Aca-Cloud1.Vceplus - Premium.Exam.50QTulus100% (1)

- Book - KVM en PDFDocument174 pagesBook - KVM en PDFbonilla03No ratings yet

- Accelerate Performance On Apache Hadoop Workloads With Intel Optane DC SSDs and HPE ProLiant DL380 Gen10 Servers - InfographicDocument1 pageAccelerate Performance On Apache Hadoop Workloads With Intel Optane DC SSDs and HPE ProLiant DL380 Gen10 Servers - InfographicPrincipled TechnologiesNo ratings yet

- Creating Link Between RFID Data and ExcelDocument11 pagesCreating Link Between RFID Data and ExceljmtriggerzNo ratings yet

- LinuxDocument9 pagesLinuxManu RajNo ratings yet

- BÁO GIÁ NGÀY 22/12/2009: CPU INTEL (Socket 775)Document20 pagesBÁO GIÁ NGÀY 22/12/2009: CPU INTEL (Socket 775)Vuong DoanNo ratings yet

- CDocument12 pagesCరాహుల్ దేవ్No ratings yet

- Fortinet Fortiweb Cloud Waf-As-A-Service Solution Getting Started GuideDocument12 pagesFortinet Fortiweb Cloud Waf-As-A-Service Solution Getting Started Guidejun chanNo ratings yet

- Integrating R and Hadoop For Big Data AnalysisDocument12 pagesIntegrating R and Hadoop For Big Data Analysisbogdan.oancea3651No ratings yet

- HA031522 1 USB CPI Clip User ManualDocument18 pagesHA031522 1 USB CPI Clip User ManualGavril VengescuNo ratings yet

- Kiran S Typing TutorDocument23 pagesKiran S Typing Tutorshid kumarNo ratings yet

- Kas Vs OthersDocument3 pagesKas Vs Othersarslan khanNo ratings yet

- Jntuk 4 1 Cse Network Programming Lab ManualDocument28 pagesJntuk 4 1 Cse Network Programming Lab Manualadi24291No ratings yet

- Content LogDocument17 pagesContent LogpelissonpauloricardoNo ratings yet

- Rmi ProgrammingDocument39 pagesRmi ProgrammingzelalemNo ratings yet

- 11TB01 - Performance Guidelines For IBM InfoSphere DataStage Jobs Containing Sort Operations On Intel Xeon-FinalDocument22 pages11TB01 - Performance Guidelines For IBM InfoSphere DataStage Jobs Containing Sort Operations On Intel Xeon-FinalMonica MarciucNo ratings yet

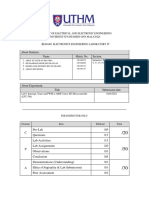

- About Students: Name Matric No. SectionDocument19 pagesAbout Students: Name Matric No. SectionsarahNo ratings yet

- 3fl12936aaaawbzza 02Document242 pages3fl12936aaaawbzza 02bleuhawkNo ratings yet

- Teamcenter 2007 Installation Mt00300Document286 pagesTeamcenter 2007 Installation Mt00300alexws77No ratings yet

- CCP603Document15 pagesCCP603api-3849444No ratings yet

- Intro - HPC Cluster Computing v2 PDFDocument73 pagesIntro - HPC Cluster Computing v2 PDFkucaisoftNo ratings yet

- FNIS FNIS Readme 7.4.5Document17 pagesFNIS FNIS Readme 7.4.5macaquinho.No ratings yet

- 8085 CodeDocument12 pages8085 CodeSanjay SharmaNo ratings yet

- Shared Device With F-CPU S7-1500 and SINAMICS: STEP 7 Safety Advanced V13 SP1Document13 pagesShared Device With F-CPU S7-1500 and SINAMICS: STEP 7 Safety Advanced V13 SP1AlexandraLlumigusinNo ratings yet