Professional Documents

Culture Documents

Digital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab Report

Uploaded by

Orangzaib RaoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab Report

Uploaded by

Orangzaib RaoCopyright:

Available Formats

Digital Logic for Computers

(ACOE161)

Experiment #8

Flip-Flops – Pre-Lab Report

Student’s Name: Reg. no.:

Semester: Spring 2021 Date: 07 December 2021

Assessment:

Assessment Point Weight Grade

Methodology and correctness of results

Discussion of results

Participation

Assessment Points’ Grade:

Comments:

© Konstantinos Tatas Page 1 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

Experiment #8:

Flip-Flops

Objectives:

The objectives of this experiment are to:

1. study and use a D flip-flop and a JK flip-flop flip-flops, and

2. to construct a Toggle (T) flip-flop using a JK flip-flop and a D flip-flop

Procedure:

Use Multisim or Electronics Workbench (EWB) to solve the following exercises.

Exercise 1:

(a) In Multisim place a 74LS113D (74LS Family) JK flip-flop. Use the F1 function

(help file) to find out information for the 74LS113D IC (left-click on the IC and

press F1) and complete Table 1 below.

Table 1. 74LS113D IC JK flip-flop truth table.

(b) Connect the JK flip-flop with a word generator and use a function generator to

provide clock pulses as illustrated in Figure 1. Place a logic analyzer to record the

changes in Q and Q . Use the settings from Figure 2 in order to obtain appropriate

results.

© Konstantinos Tatas Page 2 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

XLA1

T R 1

31 15

VCC

X

5V

X VCC

X 4

~1PR

Q

O 3 1J 1Q 5

1 1CLK F

O NOT_Q C Q T

2 6

K 1K ~1Q

O J CLK

16 0

U1A

XWG1 74LS113D

XFG1

Function Generator

GND

GND

Figure 1. 74LS113D IC JK flip-flop.

Figure 2. Settings for Word, Function Generator and Logic Analyzer.

Word Generator Function Generator Logic Analyzer

(c) Show the Multisim Logic Analyzer timing diagram of the 74LS113D IC JK flip-flop.

[Insert Multisim screen here]

Figure 3. 74LS113D IC JK flip-flop timing diagram.

© Konstantinos Tatas Page 3 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

(d) Given the timing diagram of the 74LS113D IC JK flip-flop complete Table 2.

Table 2. 74LS113D IC JK flip-flop.

~PR J K Q+ ~Q+

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Exercise 2:

(a) In Multisim place a 74LS175D (74LS Family) D flip-flop. Use the F1 function (help

file) to find out information for the 74LS175D IC (left-click on the IC and press F1)

and complete Table 3 below.

Table 3. 74LS175D IC D flip-flop truth table.

(b) Connect the D flip-flop with a word generator and use a function generator to

provide clock pulses as illustrated in Figure 4. Place a logic analyzer to record the

changes in Q and Q . Use the settings from Figure 5 in order to obtain appropriate

results.

© Konstantinos Tatas Page 4 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

T R

31 15 XLA1

1

X

X

U1

D 4 1D 1Q 2 Q

5 2D ~1Q 3

X 12 7

13

3D

4D

2Q

~2Q 6 NOT_Q

10

CLR 1 ~CLR

3Q

~3Q 11

O 9 CLK 4Q 15

~4Q 14

O CLK

74LS175D

O F

C Q T

16 0 XFG1

XWG1 Function Generator

GND

GND

Figure 4. 74LS175D IC D flip-flop.

Figure 5. Settings for Word, Function Generator and Logic Analyzer.

Word Generator Function Generator Logic Analyzer

(c) Show the Multisim Logic Analyzer timing diagram of the 74LS175D IC D flip-flop.

[Insert Multisim screen here]

Figure 6. 74LS175D IC D flip-flop timing diagram.

© Konstantinos Tatas Page 5 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

(d) Given the timing diagram of the 74LS139D IC D flip-flop complete Table 4.

Table 4. 74LS175D IC D flip-flop.

~CLR D Q+ ~Q+

0 0

0 1

1 0

1 1

Exercise 3:

(a) In Multisim design a Toggle (T) flip-flop using a JK flip-flop. Simulate your circuit

to verify T flip-flop functionality.

(b) Show the Multisim design of a T flip-flop using JK flip-flop.

[Insert Multisim screen here]

Figure 7. T flip-flop using a JK flip-flop.

© Konstantinos Tatas Page 6 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

(c) Show the Multisim Logic Analyzer timing diagram of the T flip-flop.

[Insert Multisim screen here]

Figure 8. T flip-flop timing diagram.

(e) Given the timing diagram of the T flip-flop complete Table 5.

Table 5. T flip-flop truth table.

~PR T Q+ ~Q+

0 0

0 1

1 0

1 1

Exercise 4:

(a) In Multisim design a Toggle (T) flip-flop using a D flip-flop and an XOR gate.

Simulate your circuit to verify T flip-flop functionality.

(b) Show the Multisim design of a T flip-flop using a D flip-flop and an XOR gate in

Figure 9 below.

© Konstantinos Tatas Page 7 of 8

ACOE161: Digital Logic for Computers – Pre-Lab Report Experiment # 8

[Insert Multisim screen here]

Figure 9. T flip-flop using a D flip-flop and an XOR gate.

(c) Show the Multisim Logic Analyzer timing diagram of the T flip-flop.

[Insert Multisim screen here]

Figure 10. T flip-flop timing diagram.

(d) Given the timing diagram of the T flip-flop in Figure 10, compare the results with

Table 5 in Exercise 3.

© Konstantinos Tatas Page 8 of 8

You might also like

- Lab D4 CounterDocument8 pagesLab D4 Counterdhanabadee.kNo ratings yet

- EEE102 Final Spring 2007Document13 pagesEEE102 Final Spring 2007berk.bozkurtNo ratings yet

- VHDL Contadores e Registradores: IC/Unicamp 2011s2 Prof Mario CôrtesDocument19 pagesVHDL Contadores e Registradores: IC/Unicamp 2011s2 Prof Mario CôrtesLeonardo GonçalvesNo ratings yet

- Experiment 8: Asynchronous Counter CircuitDocument5 pagesExperiment 8: Asynchronous Counter CircuitMarkLloydValleNo ratings yet

- TTL-inverter-experimentDocument6 pagesTTL-inverter-experimentRaghav BansalNo ratings yet

- Flip FlopsDocument35 pagesFlip FlopsGaurav0% (1)

- 324 Review Notes 2Document44 pages324 Review Notes 2John Jerry Nathaniel TonoNo ratings yet

- Lab 1Document8 pagesLab 1Mulugeta AbebawNo ratings yet

- Data SheetDocument16 pagesData SheetAdrian MasNo ratings yet

- Expt No:7. Design and Testing of Ring Counter Date: and Johnson CounterDocument4 pagesExpt No:7. Design and Testing of Ring Counter Date: and Johnson CounterChiranjeeviNo ratings yet

- Shift Registers: Socketed 74LS164 8-Bit Shift Register ChipDocument46 pagesShift Registers: Socketed 74LS164 8-Bit Shift Register Chipangelgalaxylife87No ratings yet

- Logic Gates & Flip-FlopsDocument5 pagesLogic Gates & Flip-FlopsStaś DutkiewiczNo ratings yet

- Lab 08Document16 pagesLab 08Aleena KhalidNo ratings yet

- CombinepdfDocument12 pagesCombinepdfZakuan HassanNo ratings yet

- Lab 7A Flip-Flops - RegistersDocument7 pagesLab 7A Flip-Flops - RegistersRifah Shanjida MomoNo ratings yet

- Universidad Carlos III de Madrid Digital Electronics ExercisesDocument9 pagesUniversidad Carlos III de Madrid Digital Electronics ExercisesTrendkill Trendkill TrendkillNo ratings yet

- X Nucleo Plc01a1Document7 pagesX Nucleo Plc01a1disturbedphaetonNo ratings yet

- CSE231L Lab 8 Synchronous Sequential Circuits 1Document9 pagesCSE231L Lab 8 Synchronous Sequential Circuits 1Tasnim MaishaNo ratings yet

- PW 4 WithanswersheetDocument11 pagesPW 4 WithanswersheetAiman 4444No ratings yet

- IC LCD Driver 7106 PDFDocument16 pagesIC LCD Driver 7106 PDFhareeshgsNo ratings yet

- Digital Logic and 555 Timer ExperimentDocument19 pagesDigital Logic and 555 Timer ExperimentRanit HalderNo ratings yet

- IC LCD Driver 7106 PDFDocument16 pagesIC LCD Driver 7106 PDFhareeshgsNo ratings yet

- Screenshot 2566-09-08 at 20.27.55Document8 pagesScreenshot 2566-09-08 at 20.27.55dhanabadee.kNo ratings yet

- 402061 - Digital System Design 1 - Chapter 9 SlideDocument24 pages402061 - Digital System Design 1 - Chapter 9 Slide42200405No ratings yet

- Notes 326 Set11Document16 pagesNotes 326 Set11Dhanu ChettyNo ratings yet

- Latches and Flip Flops CharacteristicsDocument13 pagesLatches and Flip Flops CharacteristicsWeaam RaedNo ratings yet

- Digital-Electronics 5Document37 pagesDigital-Electronics 5manavh857No ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- Shift Register: ObjectivesDocument10 pagesShift Register: ObjectivesDinh LâmNo ratings yet

- 06 CSL38 Manual LDDocument9 pages06 CSL38 Manual LDJoshua Daniel RajNo ratings yet

- Chapter 6Document7 pagesChapter 6DAWA PENJORNo ratings yet

- Um1918 Getting Started With The Xnucleoplc01a1 Industrial Inputoutput Expansion Board For stm32 Nucleo StmicroelectronicsDocument16 pagesUm1918 Getting Started With The Xnucleoplc01a1 Industrial Inputoutput Expansion Board For stm32 Nucleo Stmicroelectronicscherraj ahmedNo ratings yet

- 24 Mar - ASYNCOUNTERDocument8 pages24 Mar - ASYNCOUNTERDd DdNo ratings yet

- Digital Logic Design Lab ReportDocument16 pagesDigital Logic Design Lab ReportTrương Quang Tường100% (1)

- A Random Counter in Using Shift Register and EncoderDocument5 pagesA Random Counter in Using Shift Register and EncoderNurhaliza HsNo ratings yet

- Rangkaian Sekuensial (Flip-Flop & Latch)Document50 pagesRangkaian Sekuensial (Flip-Flop & Latch)Hairun NisaNo ratings yet

- Digital Design FundamentalsDocument25 pagesDigital Design FundamentalsnileshchaurasiaNo ratings yet

- Lab 13 (Sequential Circuit Design and Implementation)Document6 pagesLab 13 (Sequential Circuit Design and Implementation)Husnain 18No ratings yet

- Electrical, Digital and Industrial Circuits: IT IL IcDocument4 pagesElectrical, Digital and Industrial Circuits: IT IL IcNGOUNENo ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- Pertemuan 12 Counter Asinkron 2015Document27 pagesPertemuan 12 Counter Asinkron 2015Khalif GaffarezkaNo ratings yet

- CSE231L Lab 7 Flip Flops RegistersDocument7 pagesCSE231L Lab 7 Flip Flops RegistersTasnim MaishaNo ratings yet

- JK Flip FlopDocument7 pagesJK Flip FlopMohammad AbdulMajidNo ratings yet

- (Total: 80 Marks) INSTRUCTION: Answer ALL QuestionsDocument14 pages(Total: 80 Marks) INSTRUCTION: Answer ALL Questionssyiraa kimNo ratings yet

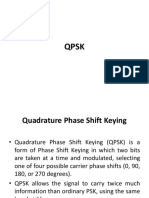

- QPSKDocument28 pagesQPSKgopiNo ratings yet

- MPLAB Tutorial Using Assembly Language For The PIC16F877 WitDocument23 pagesMPLAB Tutorial Using Assembly Language For The PIC16F877 WitPumzile FaleniNo ratings yet

- EET 1131 Lab - Latches and Flip-Flops OperationDocument9 pagesEET 1131 Lab - Latches and Flip-Flops OperationAtija LihićNo ratings yet

- Experiment No. 4 Astable & Monostable Multivibrator Using 555 TimerDocument7 pagesExperiment No. 4 Astable & Monostable Multivibrator Using 555 TimerchaitanyaNo ratings yet

- MC74HC173 semiconductor dataDocument6 pagesMC74HC173 semiconductor dataMuhammad Rizwan Haider DurraniNo ratings yet

- Counters: Asynchronous and Synchronous Digital CircuitsDocument33 pagesCounters: Asynchronous and Synchronous Digital CircuitsAMIT KUMAR SINGHNo ratings yet

- Interrogation 1: Nom: Prenom: ..Document3 pagesInterrogation 1: Nom: Prenom: ..capoNo ratings yet

- Lab 9 Areeba Sana 220610Document13 pagesLab 9 Areeba Sana 220610Bismah AsifNo ratings yet

- DLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Document7 pagesDLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Anonymous AnonymousNo ratings yet

- ET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)Document19 pagesET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)kaesarsabahNo ratings yet

- EEE 248 CNG 232: LogicDocument6 pagesEEE 248 CNG 232: LogicARSALANNo ratings yet

- Sequence DetectorDocument25 pagesSequence DetectorYudish Nandraj KistoNo ratings yet

- Lecture 1 Synchronous Sequential Logic Circuit DesignDocument60 pagesLecture 1 Synchronous Sequential Logic Circuit Designjamesphilip sorianoNo ratings yet

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- Synchronous Sequential Logic Circuit DesignDocument20 pagesSynchronous Sequential Logic Circuit Designjamesphilip sorianoNo ratings yet

- CE-2019 Guidelines For Apply OnlineDocument21 pagesCE-2019 Guidelines For Apply OnlineAzeem ChaudharyNo ratings yet

- HCNA Entry v2 0 PDFDocument418 pagesHCNA Entry v2 0 PDFOrangzaib RaoNo ratings yet

- HCNA Huawei Certified Network Associate TrainingDocument1 pageHCNA Huawei Certified Network Associate TrainingJesus Gonzalez CañasNo ratings yet

- 3 GDocument1 page3 GOrangzaib RaoNo ratings yet

- Book LinkDocument1 pageBook LinkOrangzaib RaoNo ratings yet

- Revised Syllabus CE-2016 10 Jul 2015Document158 pagesRevised Syllabus CE-2016 10 Jul 2015Muhammad Faisal TahirNo ratings yet

- Chapter 3 Feasibility PlanningDocument31 pagesChapter 3 Feasibility Planningrathnakotari63% (8)

- Welfare FormDocument1 pageWelfare FormOrangzaib RaoNo ratings yet

- Ewsd 2Document1 pageEwsd 2Orangzaib RaoNo ratings yet

- Welfare FormDocument1 pageWelfare FormOrangzaib RaoNo ratings yet

- Projects of 09 TLDocument5 pagesProjects of 09 TLOrangzaib RaoNo ratings yet

- Animal BitesDocument48 pagesAnimal BitesJalouis GabalfinNo ratings yet

- ProgDocument16 pagesProgRenon MadariNo ratings yet

- Inquisitor Character Creation and AdvancementDocument10 pagesInquisitor Character Creation and AdvancementMichael MonchampNo ratings yet

- Bivariate Lagrange InterpolationDocument11 pagesBivariate Lagrange InterpolationThiago NobreNo ratings yet

- Business Communication - Case - Josh Miller Is A Finance Student - 2Document4 pagesBusiness Communication - Case - Josh Miller Is A Finance Student - 2Sailpoint CourseNo ratings yet

- MWSS v. CADocument15 pagesMWSS v. CAAlexander AbonadoNo ratings yet

- Preparation Total Consecration PDFDocument872 pagesPreparation Total Consecration PDFgbarcelonNo ratings yet

- PH.D Scholars List 01022016Document64 pagesPH.D Scholars List 01022016vishalNo ratings yet

- Environmental Sanitation LessonDocument4 pagesEnvironmental Sanitation LessonMARIS GRACE CARVAJALNo ratings yet

- Learning CurveDocument7 pagesLearning CurveSyed FaizanNo ratings yet

- Why Men Are The Submissive SexDocument8 pagesWhy Men Are The Submissive SexWilliam Bond89% (9)

- Writing Essays B1Document6 pagesWriting Essays B1Manuel Jose Arias TabaresNo ratings yet

- Daß Ich Erkenne, Was Die Welt Im Innersten Zusammenhält (Lines 382-83) So That I Know What Holds The Innermost World TogetherDocument2 pagesDaß Ich Erkenne, Was Die Welt Im Innersten Zusammenhält (Lines 382-83) So That I Know What Holds The Innermost World TogetherEmanuel MoşmanuNo ratings yet

- WFISD Agenda Special SessionDocument1 pageWFISD Agenda Special SessionDenise NelsonNo ratings yet

- Pro ManualDocument67 pagesPro ManualAlan De La FuenteNo ratings yet

- KMBS RRDocument147 pagesKMBS RRNicole Athena Sofia MiranoNo ratings yet

- Case Study For Engineering ProblemDocument37 pagesCase Study For Engineering ProblemAfiq AfifeNo ratings yet

- 00 HR Analytics 2018Document40 pages00 HR Analytics 2018Aalya ModiNo ratings yet

- Semester I Listening Comprehension Test A Good Finder One Day Two Friends Went For A Walk. One of Them Had A Dog. "See HereDocument13 pagesSemester I Listening Comprehension Test A Good Finder One Day Two Friends Went For A Walk. One of Them Had A Dog. "See HereRichard AndersonNo ratings yet

- English - Vocabulary - in - Use - Pre - Intermediate - and - Intermediate - Book 2Document2 pagesEnglish - Vocabulary - in - Use - Pre - Intermediate - and - Intermediate - Book 2Наталия БруслинецNo ratings yet

- Physiotherapy's Role in Rehabilitation and Health Promotion Across the LifespanDocument3 pagesPhysiotherapy's Role in Rehabilitation and Health Promotion Across the LifespanMariana OspinaNo ratings yet

- Certification 5Document10 pagesCertification 5juliet.clementeNo ratings yet

- Lindtner, Ch. - Madhyamakahrdayam of BhavyaDocument223 pagesLindtner, Ch. - Madhyamakahrdayam of Bhavyathe Carvaka100% (2)

- Full Research PaperDocument31 pagesFull Research PaperMeo ĐenNo ratings yet

- Reviewer Constitutional LawDocument6 pagesReviewer Constitutional LawMoireeGNo ratings yet

- Homework #3 - Coursera CorrectedDocument10 pagesHomework #3 - Coursera CorrectedSaravind67% (3)

- Department of Information TechnologyDocument1 pageDepartment of Information TechnologyMuhammad ZeerakNo ratings yet

- Quieting of TitleDocument11 pagesQuieting of TitleJONA PHOEBE MANGALINDANNo ratings yet

- Evaluation Criteria LomceDocument4 pagesEvaluation Criteria LomceEnrique Delgado SeseñaNo ratings yet

- Papal InfallibilityDocument6 pagesPapal InfallibilityFrancis AkalazuNo ratings yet