Professional Documents

Culture Documents

Max Ref Des 1013

Uploaded by

rahul kCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Max Ref Des 1013

Uploaded by

rahul kCopyright:

Available Formats

12W Offline Flyback Converter

Using MAX17595

MAXREFDES1013

Introduction Hardware Specification

The MAX17595 is a peak-current-mode controller for An offline DCM flyback converter using the MAX17595 is

designing wide input-voltage flyback regulators. The demonstrated for a 24V DC output application. The power

MAX17595 offers optimized input thresholds for universal supply delivers up to 0.5A at 24V. Table 1 shows an over-

input AC-DC converters and telecom DC-DC (36V to 72V view of the design specification.

input range) power supplies. It contains a built-in gate

driver for an external n-channel MOSFET. The MAX17595 Table 1. Design Specification

houses an internal error amplifier with 1% accurate

PARAMETER SYMBOL MIN MAX

reference, eliminating the need for an external reference.

The switching frequency is programmable from 100kHz Input Voltage VIN 200V AC 240V AC

to 1MHz with an accuracy of 8%, allowing optimization Frequency fSW 140kHz

of magnetic and filter components, resulting in compact Maximum Efficiency η 87%

and cost-effective power conversion. For EMI-sensitive

Output Voltage VOUT 24V

applications, the MAX17595 incorporates a program-

mable frequency dithering scheme, enabling low-EMI Output Voltage Ripple ∆VOUT 1% of VOUT max

spread-spectrum operation. Users can start the power Output Current IOUT 0 0.5A

supply precisely at the desired input voltage, implement

Output Power POUT 12W

input overvoltage protection, and program soft-start time.

A programmable slope compensation scheme is provid-

ed to ensure stability of the peak current-mode control Designed–Built–Tested

scheme. Hiccup-mode overcurrent protection and thermal This document describes the hardware shown in Figure 1. It

shutdown are provided to minimize dissipation in overcur- provides a detailed systematic technical guide to design-

rent and overtemperature fault conditions. ing an offline discontinuous conduction mode (DCM) fly-

●● Programmable Switching Frequency Allows Optimiza- back using Maxim’s MAX17595 current-mode controller.

tion of the Magnetic and Filter Components, Resulting The power supply has been built and tested, details of

in Compact, Cost-Effective, Efficient Isolated/ which follow later in this document.

Nonisolated Power Supplies

●● 100kHz to 1MHz Programmable Switching Frequency

with Optional Synchronization

●● Peak Current Mode Control Provides Excellent

Transient Response—Offline (Universal Input AC)

and Telecom (36V to 72V) Flyback Controller

●● Programmable Frequency Dithering Enables Low

EMI Spread-Spectrum Operation

●● Integrated Protection Features Enhance System

Reliability

●● Adjustable Current Limit with External Current Sense

Resistor Figure 1. MAXREFDES1013 hardware.

●● Fast Cycle-By-Cycle Peak Current Limiting

Hiccup-Mode Short-Circuit Protection

●● Overtemperature Protection

●● Programmable Soft-Start and Slope Compensation

●● Input Overvoltage Protection

Rev 1; 4/18 Maxim Integrated │ 1

Generic Isolated Power Supply During the on-time when the primary switch is closed, a

Figure 2 shows a generic isolated power-supply block dia- current, IP, flows through the primary winding as shown in

gram. It consists of a power stage, an isolation transform- Figure 4. IP can be written as follows:

er, rectifier, secondary-side error amplifier, and opto-cou- 1 t 1

pler to provide a feedback for the primary side control. IP (t)

= =∫ VINdτ VINt

LP 0 LP

Different isolated power supplies are different depending

upon how the transformer is being used in them. The peak magnitude of the primary current can be written

as follows:

1 t ON

ISOLATION BOUNDARY

1

VIN VOUT IP−P

= = ∫ VINdτ VINt ON

LP 0 LP

TRANSFORMER

POWER

RECTIFIER CO

In the secondary winding, a negative voltage is induced

STAGE

due to the current flowing in to the primary. The rectifier

diode is reverse-biased and no current is flowing in the

secondary winding. The induced voltage in the primary

can be written as:

dIP (t)

PRIMARY ERROR AMP VS (t)

= LS ×

SIDE AND dt

CONTROL REFERENCE

During the off-time when the primary switch opens as shown

in Figure 5, the magnetic field in the primary winding collaps-

es and the voltage at the winding reverses, while current

FEEDBACK PATH ISOLATION keeps flowing in the same direction until the field fades away.

(USUALLY OPTO-COUPLERS)

The secondary current IS flows and the secondary and rec-

Figure 2. Generic isolated power supply. tifier diode is forward-biased. Output voltage VOUT is now

available across the secondary coil if we ignore the forward

Flyback Principle voltage drop of the rectifier diode. The secondary winding

A transformer in a flyback configuration acts differently voltage is now flown away to primary side as K x VOUT. This

than its usual operation of transformation of energy from voltage is present across the switch until the current in the

primary to secondary. During a transformer’s usual opera- secondary winding decays to zero. Total voltage available

tion, both primary and secondary windings conduct togeth- across the switch during the off-time can be written as:

er at the same time to make the transfer of energy possible VSW = VIN + K x VOUT

from primary to secondary. In a flyback configuration the

primary and secondary windings do not conduct at the This voltage also causes the breakdown of the magnetic

same time and the transformer acts more like a coupled flux in the primary winding (no current is flowing in the pri-

inductor. Note that in this document we have used the fol- mary winding after this reset). Here we can see that unlike

lowing notations for the transformer turns ratio: a usual transformer action where current flows in both the

winding at the same time, in a flyback transformer the cur-

NP rent flows into the primary winding during the on-time and

K= into the secondary winding during the off-time. This is why

NS

we use the term “coupled storage inductor” for transformers

NS used in flyback operation. It should be noted though that

k=

NP mechanically these transformers are like any transformer.

Use in flyback operations makes transformers act differently

This means capital K for primary turns/secondary turns as coupled inductors. The required duty cycle for a given

and small k for secondary turns/primary turns. input voltage and output voltage can be calculated from:

Figure 3 shows a simple flyback topology that consists

VOUT

of a transformer whose primary winding is connected D=

to the drain of a switching MOSFET. The source of the VOUT + VIN

MOSFET is connected to ground. The secondary winding

is connected to the output capacitor through a rectifier where:

diode. In this flyback configuration the current flows into

N

the primary winding during the on time of the switching = (VOUT + VF ) × P

VOUT

period and flows into the secondary winding during the off NS

time of the switching period.

www.maximintegrated.com Maxim Integrated │ 2

Figure 6 shows a typical CCM mode flyback primary and

secondary winding current, and Figure 7 shows a typical

DCM mode flyback waveform.

IPRI

VIN 0

ISEC

NP NS VOUT

IO

0

SW

ICAP

0

Figure 3. Simple flyback topology.

IO

VS Figure 6. A typical CCM mode flyback primary and secondary

VIN

winding current.

IP NP NS VOUT

VG ON OFF ON

Figure 4. Flyback topology during on-time, tON.

t

VIN

VSW VOUT/K

IS

K x VOUT NP NS VOUT VIN

t

VSW

VS

Figure 5. Flyback topology during off-time, tOFF. t

COLLAPSING

SECONDARY

MAGNETIC FIELD

IP

DIODE STOPS

CONDUCTING

IS

Figure 7. A typical DCM mode flyback topology waveform.

www.maximintegrated.com Maxim Integrated │ 3

Design Procedure for In this offline application, the DC bus voltage varies from

282V DC to 340V DC. But the actual minimum input

Offline Flyback Using MAX17595 operating voltage depends on the 100Hz ripple present

Now that the basic principle of the DCM flyback is under- on the DC bus capacitor. In this application, the ripple

stood, a practical design can be illustrated. The design is assumed to be 70.71V (25% of VINMIN) and hence the

parameters are obtained by using expressions given in minimum DC input to the converter.

Maxim Application Note 5504. This document is primarily

concerned with the power stage and the feedback loop VINMIN = 200 × 2 − 70 = 212.13V

design, and is intended to complement the information

contained in the MAX17595 data sheet. Substituting the above values in the expression of LMAG

as follows:

Flyback converters can be operated in discontinuous

conduction mode (DCM) or continuous conduction mode 2

(CCM). The component choices, stress level in power 0.4 × (212.8 × 0.43)

L PRI ≤ 1925µH

=

devices, and controller design vary depending on the 24 × 0.5 × 140k

operating mode of the converter. The design discussed

in this document is a DCM design and expressions for To account for 10% tolerance in primary inductance for our

calculating component values and ratings are presented design, LMAG is chosen as 1750µH, LPRI = 1750µH.

to achieve the design goals. The leakage inductance of the transformer should be tar-

geted as low as possible. For this design, we achieved a

Step 1: Switching Frequency

1% leakage inductance of 17.5µH, LLKG = 17.5µH.

For offline flyback operation, the selection of switching

frequency is of prime importance. Thermal limits and A customized transformer 750316881 from Würth

junction temperature of the device limits the selected Electronik is used in this design. This transformer also

switching frequency to be less than 150kHz. For this fulfills the specification of turns ratio, bias winding, and

design we have selected a switching frequency of primary/secondary currents requirement of the design

140kHz. The MAX17595 switching frequency is program- that is calculated step by step in this document. The trans-

mable between 100kHz and 1000kHz with a resistor RRT former has dielectric isolation specification of 3900V AC.

connected between RT and SGND. The RRT is calculated Step 3: Maximum Duty Cycle Calculation

as follows: with Selected LPRI

10 10 Use the following expressions to calculate the maximum

R=

RT Ω duty cycle of the converter for the selected frequency and

f SW magnetizing inductance:

10 10

R

= RT = 71.5kΩ 2.5 × L PRI × VOUT × I OUT × f SW

140k D NEW =

VINMIN

A standard 71.5kΩ resistor is selected for RRT. 2.5 × 1750µ × 24 × 0.5 × 140k

= D NEW = 0.404

Step 2: Transformer Magnetizing Inductance 212.13

and Turns Ratio

In a DCM flyback converter, the energy stored in the pri- Calculate the required transformer turns ratio (k) using the

mary inductance of the flyback transformer is delivered expressions as follows:

entirely to the output. The maximum primary-inductance N s (VOUT + VD ) × (1 − D NEW )

value for which the converter remains in DCM at all oper- k

= =

ating conditions can be calculated as: Np D NEW × VINMIN

N s (24 + 0.7) × (1 − 0.404)

0.4 × (VINMIN × D MAX )

2 k =

= = 0.1717

L PRI ≤ Np 0.404 × 212.13

VOUT × I OUT × f sw

For the present design, k is chosen as 1:0.1717.

where:

DMAX = 0.43V

VD = 0.7V is the forward voltage drop of the rectifier diode

of the secondary winding.

www.maximintegrated.com Maxim Integrated │ 4

Step 4: Calculation of Peak/RMS Current Step 6: MOSFET Selection

Primary and secondary RMS and primary peak currents MOSFET selection criteria includes maximum drain volt-

calculations are needed to design the transformer in age, peak/RMS current in the primary, and the maximum

switched-mode power supplies. Also, primary peak cur- allowable power dissipation of the package without

rent is used in setting the current limit. Use the following exceeding the junction temperature limits. The voltage

expressions to calculate the primary and secondary peak seen by the MOSFET drain is the sum of the input

and RMS currents. voltage, the reflected secondary voltage on the trans-

former primary, and the leakage inductance spike. The

VINMIN × D NEW 212.13 × 0.43 MOSFET’s absolute maximum VDS rating must be higher

IPRIPEAK

= = = 0.35A than the worst-case drain voltage as follows:

L PRI × f SW 1750µ × 140kHz

D NEW 0.43 2.5 × (VOUT + Vd)

IPRIRMS =

IPRIPEAK × =0.35 × =0.128A VDSMAX

= VINMAX +

3 3 k

I 0.35 2.5 × (24 + 0.7)

= PRIPEAK

I SECPEAK = = 2.038A VDSMAX =339.4 + 699V

k 0.1717 0.1716 =

2 × I OUT × IPRIPEAK

=I SECRMS = 0.824A

3×k For this application, the 800V 11A n-channel MOSFET

STB11NM80T4 from ST Micro is selected as the primary

MOSFET.

Step 5: Current Limit Resistor Calculation

Step 7: Snubber Selection

For current limit setting, the peak current can be calculat-

ed as follows: Ideally, the external MOSFET experiences a drain-source

voltage stress equal to the sum of the input voltage and

ILIM = 1.2 x IPRIPEAK = 1.2 x 0.35 = 0.4199A reflected voltage across the primary winding during the

The devices include a robust overcurrent protection off period of the MOSFET. In practice, parasitic inductors

scheme that protects the device under overload and and capacitors in the circuit, such as leakage inductance

short-circuit conditions. A current-sense resistor, connect- of the flyback transformer, cause voltage overshoot and

ed between the source of the MOSFET and PGND, sets ringing in addition to the ideally expected voltage stress.

the peak current limit. The current-limit comparator has a Snubber circuits are used to limit the voltage overshoots

voltage trip level (VCS-PEAK) of 300mV. Use the following to safe levels within the voltage rating of the external

equation to calculate the value of RCS: MOSFET. The snubber capacitor can be calculated using

the following expression:

300m 300m

R

= CS = = 715mΩ 2 × L LK × IPRIPEAK 2 × k 2

IMOSFET 0.41 C SNUB =

VOUT 2

where IMOSFET is the peak current flowing through the 2 × 17.5µ × 0.35 2 × 0.1717 2

=

MOSFET. A typical 750mΩ current-sense resistor is C SNUB = 219.28pF

selected, RCS = 750mΩ. 24 2

Considering the derating of the capacitor, we selected a

capacitor of value 470pF, CSNUB = 470pF.

www.maximintegrated.com Maxim Integrated │ 5

VDC VDC VOUT

D2 D1

RIN1

NP NS COUT

VOUT

RSTART RIN2 NP

MAX17595

RIN3 NDRV RLED

VDRV

LDO DRV RU

CS

CSTART VIN

VDRV CCF1

VFB

COMP FB

CVDRV CCF2 U2 TLV

RFB

431

RB

R1

R2

VFB

Figure 8. Bias winding configuration.

The power that must be dissipated in the snubber resistor the following expression to calculate the secondary diode

is calculated using the following expressions: voltage rating:

PSNUB = 0.833 x LLKG x IPRIPEAK2 x fSW VSEC,DIODE = 1.25 x (k x VINMAX + VOUT)

PSNUB = 0.833 x 17.5µ x 0.352 x 140k = 0.25W VSEC,DIODE = 1.25 x (0.1717 x 339.4 + 24) = 102.8V

The snubber resistor is calculated based on the below The current rating of the secondary diode should be

expression: selected so that the power loss in the diode (given as the

product of forward-voltage drop and the average diode

6.25 × VOUT 2 6.25 × 24 2 current) should be low enough to ensure that the junction

R=

SNUB = = 488.78kΩ

PSNUB × k 2 0.25 × 0.1717 2 temperature is within limits. It is recommended to select

fast-recovery diodes with a recovery time less than 50ns,

A standard resistor of 499kΩ 0.4W is selected, RSNUB = or Schottky diodes with low junction capacitance.

499kΩ. For this application a 200V, 6A, ultra-fast recovery rectifier

The voltage rating of the snubber diode is: diode PDU620-13 from Diodes Inc. is selected as a sec-

ondary rectifier diode.

V

= VINMAX + (2.5 × OUT )

VD SNUB Step 9: Bias Winding Supply Configuration

k

The MAX17595 is implemented with a 20V VIN UVLO

24 wake-up level with 13V hysteresis to optimize the size of

VD SNUB = 340 + (2.5 × ) = 688V

0.1717 bias capacitor. A simple RC circuit is used to start up the

MAX17595. To sustain the operation of the circuit, the

An 800V, 1A diode US1K-TP from Micro Commercial input supply to the IC is bootstrapped through diode D2

Components is selected as the snubber diode for this design. as shown in Figure 8.

Use VBIAS = 12V. Bias winding turns ratio kb can be

Step 8: Selection of Secondary Diode calculated as follows:

The maximum operating reverse-voltage rating of the

secondary rectifier diode must be higher than the sum of V + VD2 12 + 0.8

the output voltage and the reflected input voltage. We use k × BIAS

kb = 0.1717 ×

= 0.889

=

VOUT + VD1 24 + 0.7

www.maximintegrated.com Maxim Integrated │ 6

In isolated applications where a bias winding configura-

tion is used to power up the MAX17595, CSTART can be V

R U OUT − 1 × R B

=

calculated as follows: VREF

CSTART = 0.75 x (CDRV + 0.1 x IIN x tSS +

0.04 x tSS x QG x fSW) where VREF is the reference set by the secondary-side

controller (VREF = 1.24V for TLV431 is used in this design).

CSTART is the startup capacitor, CDRV is the cumulative

capacitor used at the DRV pin, IIN is the MAX17595 qui-

escent current, tSS is the soft-start time, VOUT is the output 24

RU

= − 1 × 750

= 13.7kΩ

voltage, COUT is the output capacitor used, and QG is the 1.24

gate charge of the primary n-channel MOSFET.

Select: A standard resistor of 13.7kΩ is selected, RU = 13.7kΩ.

CDRV = 1µF Step 11: Soft-Start Capacitor

IIN = 2mA The soft-start period for the devices can be programmed

QG = 23nC by selecting the value of the capacitor CSS connected from

the SS pin to SGND. Capacitor CSS can be calculated as:

tSS = 12ms

CSS = 8.264 x tSS

CSTART = 0.75 x (1µ + 0.1 x 2m x 12m +

0.4 x 12m x 23n x 140k) where tSS is expressed in ms and the resultant value of

CSS is in nF.

CSTART = 3.7µF

CSS = 8.264 x tSS = 8.264 x 12 = 99.17nF

It is recommended to consider the derating of the startup

capacitor. A typical value of 4.7µF is selected as CSTART, A standard 100nF is selected as the soft-start capacitor,

CSTART = 4.7µF. CSS = 100nF.

RSTART can be calculated as follows: Step 12: Input Capacitor Selection

The MAX17595 is optimized to implement offline AC-DC

(VSTART − 10) × 50

=R START kΩ applications. In such applications, the input capacitor

1 + C START must be selected based on either the ripple due to the

rectified line voltage, or based on holdup-time require-

where CSTART is in µF. ments. Holdup time can be defined as the time period

over which the power supply should regulate its output

(212.13 − 10) × 50 voltage from the instant the AC power fails.

R START

= = 1773kΩ

1 + 4.7 For the flyback converter, the input capacitor supplies the

input current when the diode rectifier is off. The voltage

RSTART is divided into three equal value resistors of value discharge on the input capacitor, due to the input average

591kΩ each. Standard 1206 resistor value of 590kΩ current, should be within the limits specified. Assuming

250mW is selected for RIN1, RIN2, and RIN3, respectively. 25% ripple present on input DC capacitor, the input

RIN1 = RIN2 = R1N3 = 590kΩ capacitor can be calculated as follows:

Step 10: Feedback Resistor Selection RU, RB 0.045 × PLOAD

C IN =

For all the applications that use a startup network to bias η × VINPK 2

the VIN pin during the power-up sequence, calculate the

feedback potential divider using the following formulas: where:

η = Target efficiency = 85%

10 × (30 × C START − 20 × C DRV − IIN × t SS )

RB = PLOAD = 24 ×0.5 = 12W

VOUT × C OUT × (IIN + Q G × f SW )

VINPK = Peak voltage at minimum AC voltage = 282.84V

10 × (30 × 3.7µ − 20 × 1µ − 2m × 12m)

R=

B = 767Ω

24 × 7µ × (2m + 23n × 140kHz) 0.045 × 12

=C IN = 8µF

0.85 × 282.84 2

A standard resistor of 750Ω is selected, RB = 750Ω.

www.maximintegrated.com Maxim Integrated │ 7

Step 13: Output Capacitor Selection Step 14: Loop Compensation

X7R ceramic output capacitors are preferred in industrial Optocoupler feedback is used in isolated flyback converter

applications due to their stability over temperature. The designs for precise control of isolated output voltage. Figure 9

output capacitor is usually sized to support a step load shows the overall scheme of the optocoupler feedback.

of a certain percentage of the rated output current so Use RFB = 470Ω (typ), for an optocoupler transistor cur-

that the output voltage deviation is contained to 3% of rent of 1mA. Select R1 = 49.9kΩ and R2 = 22kΩ (typical

the rated output voltage. The output capacitance can be values) to use the full range of available COMP voltage.

calculated by using the below expressions: U3 is a low-voltage adjustable shunt regulator with a

1.24V reference voltage. In this design a 1.24V, 0.5%

0.33 1

t RESPONSE ≅ + shunt regulator TLV431BFTA from Diodes Inc. is selected.

fC f SW

Calculate RLED using expression below:

I ×t

C OUT = STEP RESPONSE RLED = 400 x CTR x (VOUT - 2.7)

∆VOUT

RLED = 400 x 1 x (24 - 2.7) = 8.52kΩ

where ISTEP is the load step, tRESPONSE is the response A standard 8.66kΩ resistor is selected, RLED = 8.66kΩ.

time of the controller, ∆VOUT is the allowable output volt- The bandwidth of typical optocouplers limits the achiev-

age deviation, and fC is the target closed-loop crossover able closed-loop bandwidth of opto-isolated converters.

frequency. In our application, we selected fC = 3kHz, typi- Considering this limitation, the closed-loop crossover

cal bandwidth at nominal voltage for isolated applications frequency can be chosen at the nominal input voltage by

to minimize noise and proportionally increase the gain. selecting fC = 3kHz. Closed-loop compensation values

I STEP = 0.6 × I OUT = 0.6 × 0.5 = 0.30A (60% of I OUT ) are designed based on the open-loop gain at the desired

crossover frequency, fC. The open-loop at fC is calculated

∆VOUT = 0.03 × 24= 720mV (3% of VOUT , typ) using the following expressions.

0.33 1

t RESPONSE ≅ + =73.14µs I OUT 0.5

5k 140k =fP = = 414.4Hz

π × VOUT × C OUT π × 24 × 16µ

I STEP × t RESPONSE 0.3 × 73.14µ

C OUT

= = = 30.476µF fP L PRI × f SW × VOUT

2 × ∆VOUT 2 × 0.720 G PLANT = × ×

fC 8 × I OUT

Due to the DC-bias characteristics, 4 x 10µF 50V capaci- VIN

tors are selected as COUT for this design. VIN × R CS + 50 × 10 3 × L PRI

Capacitor values change with temperature and applied

voltage. Refer to the capacitor data sheets to select

capacitors that guarantee the required output capacitance 414.4 1750µ × 140k × 24

G PLANT = × ×

across the operating range. For design calculations, use 3kHz 8 × 0.5

the worst-case derated value of capacitance, based on 311.13

temperature range and applied voltage. In our case the

311.13 × 750m + 50 × 10 3 × 1750µ

worst-case derated value of capacitors is 16µF.

G PLANT = 0.1381× 38.34 × 0.9922 = 5.255

For the flyback converter, the output capacitor supplies

the load current when the main switch is on, and therefore

the output voltage ripple is a function of load current and Three controller configurations are suggested in

duty cycle. Use the following expression to estimate the Application Note 5504 based on open-loop gain and the

output capacitor ripple: RLED value. For typical designs, the current transfer ratio

(CTR) of the optocoupler designs can be assumed to be

2 unity. It is known that the comparator and gate-driver delays

0.5 × IPRIPEAK − (K × 0.5)

∆VCOUT = associated with the input voltage variations affect the opto-

IPRIPEAK 2 × f SW × C OUT coupler CTR. Depending on the optocoupler selected,

2 variations in CTR causes wide variations in bandwidth of

0.5 × 0.35 − (0.1717 × 0.5)

=∆VCOUT = 290.6mV the closed-loop system across the input-voltage operating

0.35 2 × 140kHz × 7µ

www.maximintegrated.com Maxim Integrated │ 8

range. It is recommended to select an optocoupler with of the resistor-divider can be selected so the EN/UVLO

less CTR variations across the operating range. Checking pin voltage exceeds the 1.23V turn-on threshold at the

the condition as stated in Application Note 5504: desired input DC bus voltage. The same resistor-divider

R FB R 1 can be modified with an additional resistor (ROVI) to imple-

G PLANT × CTR × × = ment input overvoltage protection in addition to the EN/

R LED R 2

UVLO functionality as shown in Figure 11.

470 49.9k

5.255 × 1× × =0.6646 When voltage at the OVI pin exceeds 1.21V the devices

8.53k 22k

stop switching and resume switching operations only if

voltage at the OVI pin falls below 1.15V. For given values

As 0.6646 < 0.8, therefore, as stated in

of startup DC input voltage (VSTART) and input overvolt-

Application Note 5504, configuration 1 is selected.

age-protection voltage (VOVI), the resistor values for the

Figure 10 shows a typical schematic of configuration 1.

divider can be calculated as follows:

The RF value can be calculated from the expression

below: Select ROVI = 24.9kΩ.

R LED × R2 VOVI

RF − 1 × R U R EN =

R OVI × − 1

G PLANT × CTR × R FB × R1 V

START

8.66kΩ × 22kΩ

RF

= − 1 × 13.7k

= Ω 7.48kΩ where VOVI = maximum allowed overvoltage = 260 x

5.255 × 1 × 470 × 49.9k Ω

1.414 = 367.69V.

A typical value of 7.5kΩ is selected as RF, RF = 7.5kΩ. The

CF value can be calculated from the expression below: 367.69

R EN

= 24.9k × 1 18.25kΩ

−=

1

212.13

=CF =

2π × (R U + R F ) × f P

A standard 20kΩ resistor is selected, where REN = 20kΩ.

1

= 18.12nF The same resistor-divider can be modified to implement

2π × (13.7kΩ + 7.5kΩ) × 414.46

input overvoltage protection. When the voltage at the OVI

A standard 18nF capacitor is selected as CF, CF = 18nF. pin exceeds 1.215V (typ), the device stops switching. The

The CCF1 value can be calculated from the expressions device resumes switching operations only if the voltage at

below: the OVI pin falls below 1.1V (typ).

1

C CF1 = V

π × R F × f SW R SUM = R OVI + R EN × START − 1

1 1.21

= = 303.3pF

π × 7.5kΩ × 140kHz 212.13

= [24.9k + 20k] ×

R SUM 1 7826.7kΩ

−=

1.21

A standard 330pF capacitor is selected as CCF1 = 330pF.

In universal AC input applications, RSUM may need to be

Step 15: EN/UVLO and OVI Setting implemented as equal resistors in series (RDC1, RDC2, and

The device’s EN/UVLO pin serves as an enable/disable RDC3) so that voltage across each resistor is limited to its

input, as well as an accurate programmable input UVLO maximum operation voltage.

pin. The device does not commence startup operation

unless the EN/UVLO pin voltage exceeds 1.21V. The 7826.7

R=

DC1 R=

DC2 R=

DC3 = kΩ 2.6MΩ

device turns off if the EN/UVLO pin voltage falls below 3

1.15V. A resistor-divider from the input DC bus to ground

can be used to divide down and apply a fraction of the

A standard 2.8MΩ resistor is selected for RDC1, RDC2, and

input DC voltage (VDC) to the EN/UVLO pin. The values

RDC3.

www.maximintegrated.com Maxim Integrated │ 9

VOUT

4 RLED

VDRV 1 RU

R2 RF CF

3 2

FB VFB VFB

CM U2

RFB CCF1

R1 CCF2

RM 2

SGND U3

COMP 3 1

RL

GND0

Figure 9. A typical opto-coupler-based feedback compensation.

VOUT

CDRV RLED RU

4 1

VDRV

R2

FB VFB VFB 3 2 RF CF

U2

R1

COMP RFB 2 CCF1

U3

3 1

SGND RL

GND0

Figure 10. Opto-coupler feedback compensation configuration 1 schematic.

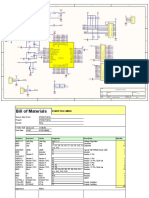

Design Resources

Download the complete set of Design Resources

RDC1 including the schematics, bill of materials, PCB layout,

and test files.

RSUM RDC2

RDC3

EN/UVLO

REN MAX17595

OVI

ROVI

Figure 11. Programming EN/UVLO and OVI.

www.maximintegrated.com Maxim Integrated │ 10

Revision History

REVISION REVISION PAGES

DESCRIPTION

NUMBER DATE CHANGED

0 10/17 Initial release —

1 4/18 Updated Figure 7. 3

Maxim Integrated

www.maximintegrated.com

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses

are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits)

shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

© 2018 Maxim Integrated Products, Inc. All rights reserved. Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc., in

the United States and other jurisdictions throughout the world. All other marks are the property of their respective owners.

You might also like

- U 217 B / U 217 B-FP: Zero Voltage Switch / Temperature Control For General ApplicationsDocument14 pagesU 217 B / U 217 B-FP: Zero Voltage Switch / Temperature Control For General ApplicationsGüner GüvençNo ratings yet

- Overvoltage Protection For Isolated DC/DC Converter: Koteshwar Rao, Applications Lead, Isolation, Interface ProductsDocument3 pagesOvervoltage Protection For Isolated DC/DC Converter: Koteshwar Rao, Applications Lead, Isolation, Interface ProductsShaik Abdul HameedNo ratings yet

- LM3481MM NOPB National SemiconductorDocument22 pagesLM3481MM NOPB National Semiconductorvs674584No ratings yet

- LM5008 High Voltage (100V) Step Down Switching Regulator: General Description FeaturesDocument15 pagesLM5008 High Voltage (100V) Step Down Switching Regulator: General Description FeaturesBrix MatacsilNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- TEA1024Document8 pagesTEA1024piotreNo ratings yet

- STMicroelectronics L4981AD DatasheetDocument17 pagesSTMicroelectronics L4981AD Datasheetgafesa electronicsNo ratings yet

- STMicroelectronics L4962E A DatasheetDocument16 pagesSTMicroelectronics L4962E A DatasheetJosé AdelinoNo ratings yet

- Yaesu FL-2100Z UserDocument15 pagesYaesu FL-2100Z Userjos34800No ratings yet

- 95-Wat Laptop PSU 12V in - 19V 5A Out PDFDocument7 pages95-Wat Laptop PSU 12V in - 19V 5A Out PDFRodrigo SantosNo ratings yet

- 502ag0207 Designing A SEPIC ConverterDocument9 pages502ag0207 Designing A SEPIC Converterempeeno1No ratings yet

- An 71Document11 pagesAn 71vijaybabukoreboinaNo ratings yet

- U217B/ U217B-FP: Zero Voltage Switch With Adjustable RampDocument11 pagesU217B/ U217B-FP: Zero Voltage Switch With Adjustable RampvalkovNo ratings yet

- L4981ADocument17 pagesL4981AMcu CdiiNo ratings yet

- Integrated Circuit Operational AmplifierDocument13 pagesIntegrated Circuit Operational AmplifierFaizan NazirNo ratings yet

- LM5642 High Voltage, Dual Synchronous Buck Converter With Oscillator SynchronizationDocument24 pagesLM5642 High Voltage, Dual Synchronous Buck Converter With Oscillator SynchronizationcsclzNo ratings yet

- BM1513 EtcDocument7 pagesBM1513 EtcDimas BarretoNo ratings yet

- Slua 053Document13 pagesSlua 053carlosibaNo ratings yet

- AND8331/D Quasi-Resonant Current-Mode Controller For High - Power Ac-Dc AdaptersDocument16 pagesAND8331/D Quasi-Resonant Current-Mode Controller For High - Power Ac-Dc AdaptersLucía MitchellNo ratings yet

- 1.5A Switching Regulator: DescriptionDocument18 pages1.5A Switching Regulator: DescriptionindustronicaNo ratings yet

- Lecture-3-Signal ConditioningDocument36 pagesLecture-3-Signal ConditioningEphrem AbabiyaNo ratings yet

- TFT LCD DC-DC Converter With Integrated Charge Pumps, OP-AMP and HV-SwitchDocument20 pagesTFT LCD DC-DC Converter With Integrated Charge Pumps, OP-AMP and HV-SwitchАлександрNo ratings yet

- Precision Attenuator With Digital Control: (B) OutputDocument1 pagePrecision Attenuator With Digital Control: (B) OutputdendylawNo ratings yet

- S G M BH: Simple Phase Control CircuitDocument9 pagesS G M BH: Simple Phase Control CircuitAbdel MUNDENNo ratings yet

- Description: Quick Start Guide For Demonstration Circuit 575 LTC2410Document5 pagesDescription: Quick Start Guide For Demonstration Circuit 575 LTC2410donatoNo ratings yet

- Acs 120Document17 pagesAcs 120Mafia BetawiNo ratings yet

- Varactor DiodeDocument22 pagesVaractor Diodespam_biggerNo ratings yet

- Gainclone CompositeDocument7 pagesGainclone CompositeDragan LalkovicNo ratings yet

- LNB Supply and Control-Voltage Regulator: Preliminary InformationDocument9 pagesLNB Supply and Control-Voltage Regulator: Preliminary InformationJoil AlvesNo ratings yet

- Experiment 1 Op-Amps and Basics of Signal ConditioningDocument6 pagesExperiment 1 Op-Amps and Basics of Signal ConditioningAnonymous XZUyueNNo ratings yet

- LM3478MM PDFDocument22 pagesLM3478MM PDFkarimNo ratings yet

- Basic Opamp ApplicationsDocument5 pagesBasic Opamp ApplicationsNorbertNo ratings yet

- Description Features: LT1952/LT1952-1 Single Switch Synchronous Forward ControllerDocument28 pagesDescription Features: LT1952/LT1952-1 Single Switch Synchronous Forward ControllerDuta HastaNo ratings yet

- Datasheet - HK mr1721 1692087Document8 pagesDatasheet - HK mr1721 1692087heribertosfaNo ratings yet

- Simple Electrification UnitDocument2 pagesSimple Electrification UnitPeeters GuyNo ratings yet

- High Current Switching Regulators: DescriptionDocument22 pagesHigh Current Switching Regulators: DescriptionClaudio MartinsNo ratings yet

- 6283-Article Text-16473-1-10-20140217Document8 pages6283-Article Text-16473-1-10-20140217ivasi ivasiNo ratings yet

- V/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseDocument8 pagesV/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseAlim SheikhNo ratings yet

- Auto-Tuned Transition Scheme in Bias-Flip Rectifier For Piezoelectric Energy HarvestingDocument4 pagesAuto-Tuned Transition Scheme in Bias-Flip Rectifier For Piezoelectric Energy HarvestingHafeez KtNo ratings yet

- Bidirectional Current Source-TIDocument9 pagesBidirectional Current Source-TIestraj1954100% (1)

- 497 2334 5 DatasheetzDocument17 pages497 2334 5 DatasheetzanandaeizzNo ratings yet

- Chapter Three Part ThreeDocument41 pagesChapter Three Part ThreeAbrhamNo ratings yet

- Act 4065Document9 pagesAct 4065bob75No ratings yet

- Pc2250 Series: Bipolar Analog Integrated CircuitDocument13 pagesPc2250 Series: Bipolar Analog Integrated CircuitkeisinhoNo ratings yet

- L4970ADocument21 pagesL4970ASURESH CHANDRA ROUTNo ratings yet

- Application Note 106 February 2007 Instrumentation Circuitry Using RMS-to-DC ConvertersDocument20 pagesApplication Note 106 February 2007 Instrumentation Circuitry Using RMS-to-DC ConvertersIldo ParnowNo ratings yet

- Automatic Night Lamp Using An LDRDocument25 pagesAutomatic Night Lamp Using An LDRStevenjumahNo ratings yet

- Current Transformers: For Worldwide CooperationDocument40 pagesCurrent Transformers: For Worldwide CooperationPrashant Trivedi100% (1)

- Current Transformers: For Worldwide CooperationDocument40 pagesCurrent Transformers: For Worldwide CooperationPrashant TrivediNo ratings yet

- Ta 8429 HDocument14 pagesTa 8429 HrikyNo ratings yet

- Power Supply Battery Charger Regulation Control Circuit: Semiconductor Technical DataDocument20 pagesPower Supply Battery Charger Regulation Control Circuit: Semiconductor Technical DataKarim MuhammedNo ratings yet

- Linear Integrated CircuitsDocument15 pagesLinear Integrated CircuitsAISWARYA MNo ratings yet

- Understanding DC-DC BUCKDocument4 pagesUnderstanding DC-DC BUCKchronixNo ratings yet

- Understanding Output Voltage Limitations of DC/DC Buck ConvertersDocument4 pagesUnderstanding Output Voltage Limitations of DC/DC Buck ConvertersHossam SobhyNo ratings yet

- Understanding Output Voltage Limitations of DC/DC Buck ConvertersDocument4 pagesUnderstanding Output Voltage Limitations of DC/DC Buck ConvertersHossam SobhyNo ratings yet

- Rem S RaDocument3 pagesRem S RaStefan CorjucNo ratings yet

- See A3964SLB: Dual Full-Bridge PWM Motor DriverDocument8 pagesSee A3964SLB: Dual Full-Bridge PWM Motor DriverPaulo SwarosvishNo ratings yet

- L9911ADocument15 pagesL9911Amar_barudjNo ratings yet

- Philips On OpampsDocument10 pagesPhilips On OpampsSpun_GNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- TechinterDocument3 pagesTechinterrahul kNo ratings yet

- Sample RFPDocument7 pagesSample RFPrahul kNo ratings yet

- QuestionsDocument47 pagesQuestionsrahul kNo ratings yet

- HR Summit 05042018 HyderabadDocument3 pagesHR Summit 05042018 Hyderabadrahul kNo ratings yet

- Sr. Full Stack DeveloperDocument1 pageSr. Full Stack Developerrahul kNo ratings yet

- Myanatomy Expense Reimbursement Form Rahul K Metricstream 19-23 Aug & 30 Aug Amr Techpark, BomanahalliDocument1 pageMyanatomy Expense Reimbursement Form Rahul K Metricstream 19-23 Aug & 30 Aug Amr Techpark, Bomanahallirahul kNo ratings yet

- Myanatomy Expense Reimbursement Form Rahul K Teksystems, Mce, Hassan 26/9/2019 HassanDocument1 pageMyanatomy Expense Reimbursement Form Rahul K Teksystems, Mce, Hassan 26/9/2019 Hassanrahul kNo ratings yet

- CCCCDocument2 pagesCCCCrahul kNo ratings yet

- VMWAREDocument23 pagesVMWARErahul kNo ratings yet

- Myanatomy Expense Reimbursement Form Rahul K Teksystems, Mce, Hassan 26/9/2019 HassanDocument2 pagesMyanatomy Expense Reimbursement Form Rahul K Teksystems, Mce, Hassan 26/9/2019 Hassanrahul kNo ratings yet

- DigivaletDocument9 pagesDigivaletrahul kNo ratings yet

- A Decision Making MCQDocument18 pagesA Decision Making MCQcik siti89% (9)

- System Requirements and Instruction Before Starting The MAPIT Online AssesmentDocument1 pageSystem Requirements and Instruction Before Starting The MAPIT Online Assesmentrahul kNo ratings yet

- Tavi ScaDocument2 pagesTavi Scarahul kNo ratings yet

- Angular JsDocument45 pagesAngular Jsrahul kNo ratings yet

- 0k5093 A sd100 6 7l PDFDocument6 pages0k5093 A sd100 6 7l PDFmarpadanNo ratings yet

- Multi-Band Panel Dual Polarization Half-Power Beam Width Adjust. Electrical DowntiltDocument2 pagesMulti-Band Panel Dual Polarization Half-Power Beam Width Adjust. Electrical DowntiltFachri MNo ratings yet

- 03 Passat Wiring Diagrams PDFDocument45 pages03 Passat Wiring Diagrams PDFEsther KoltermanNo ratings yet

- L Completely Fair Scheduler PDFDocument10 pagesL Completely Fair Scheduler PDFpelao321No ratings yet

- Vs-Vsk.230..Pbf Series: Vishay SemiconductorsDocument9 pagesVs-Vsk.230..Pbf Series: Vishay SemiconductorsrenidwilNo ratings yet

- Module Code and Title: Programme: Credit: Module Tutor: General ObjectivesDocument5 pagesModule Code and Title: Programme: Credit: Module Tutor: General ObjectivesAmrith SubidiNo ratings yet

- Benchmarking EV and HEV Technologies: Tim Burress Oak Ridge National LaboratoryDocument22 pagesBenchmarking EV and HEV Technologies: Tim Burress Oak Ridge National LaboratoryTanawat ThanthongNo ratings yet

- Santhosh S. Design & Development of Solar Electric Boat, 2021Document43 pagesSanthosh S. Design & Development of Solar Electric Boat, 2021VitBarNo ratings yet

- 2012 Karakehayov - Data Acquisition ApplicationsDocument351 pages2012 Karakehayov - Data Acquisition ApplicationsLEO_GONZALEZNo ratings yet

- Radioactivity UitmDocument25 pagesRadioactivity UitmMoody6861No ratings yet

- V.35 Cable Interface: TutorialDocument4 pagesV.35 Cable Interface: Tutorialamin_bravoNo ratings yet

- JKT05 SHD CSS 1908 REV B Equipment Layout Domestic Water Pump Room ReviewedDocument5 pagesJKT05 SHD CSS 1908 REV B Equipment Layout Domestic Water Pump Room ReviewedKhoirul RezqiNo ratings yet

- Effect of Unified Power Quality Conditioner in Smart Grid Operation and ControlDocument5 pagesEffect of Unified Power Quality Conditioner in Smart Grid Operation and ControlDrAshok Kumar TiwariNo ratings yet

- Ces Manual-Ame 513Document31 pagesCes Manual-Ame 513Anush AntonyNo ratings yet

- RRU 4G &5G Heatsink Design and Experimental EvaluationDocument13 pagesRRU 4G &5G Heatsink Design and Experimental EvaluationAnonymous P8Bt46mk5I100% (1)

- Brake Switch B HighDocument2 pagesBrake Switch B HighDannyDDannyDNo ratings yet

- snc2d Chemistry Quiz Review - TeacherDocument3 pagessnc2d Chemistry Quiz Review - Teacherapi-263850753No ratings yet

- TH D74ae IdmDocument64 pagesTH D74ae Idmudal64No ratings yet

- Power Semiconductor Drives Question BankDocument16 pagesPower Semiconductor Drives Question BankSaileela Reddy GangasaniNo ratings yet

- MINI STM32 Schematic DiagramDocument2 pagesMINI STM32 Schematic DiagramNoveri Dwi Hardyanto100% (1)

- PCAAD6 ManualDocument105 pagesPCAAD6 ManualIván IvanovNo ratings yet

- SH 24 As 6Document38 pagesSH 24 As 6Stefano SinigagliesiNo ratings yet

- Intel Core I5-4570 3.2Ghz Quad-Core ProcessorDocument6 pagesIntel Core I5-4570 3.2Ghz Quad-Core Processormuhammad yakhsyaNo ratings yet

- Donnelly PDFDocument2 pagesDonnelly PDFTung Bui ThanhNo ratings yet

- How To Create A Bootable CD To Upgrade BIOS If You Don't Hav... - HP Support Forum - 872531Document2 pagesHow To Create A Bootable CD To Upgrade BIOS If You Don't Hav... - HP Support Forum - 872531Greed CssNo ratings yet

- Translating Orcad Layout Designs Using The Cadence Orcad and Allegro PCB Editors Rev A PDFDocument12 pagesTranslating Orcad Layout Designs Using The Cadence Orcad and Allegro PCB Editors Rev A PDFgem1144aaNo ratings yet

- Introduction To Bond GraphsDocument8 pagesIntroduction To Bond GraphsamiritehNo ratings yet

- Fiche Technique BarrièreDocument2 pagesFiche Technique Barrièrepuriste modéréNo ratings yet

- Question BankDocument3 pagesQuestion BankTARUN PRASADNo ratings yet