Professional Documents

Culture Documents

A Review On Implementation of Parallel Prefix Adders Using FPGA'S

Uploaded by

Editor IJTSRDOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Review On Implementation of Parallel Prefix Adders Using FPGA'S

Uploaded by

Editor IJTSRDCopyright:

Available Formats

International Journal of Trend in Scientific

Research and Development (IJTSRD)

International Open Access Journal

ISSN No: 2456 - 6470 | www.ijtsrd.com | Volume - 2 | Issue – 1

A Review

eview on Implementation of Parallel

Prefix Adders using FPGA’S

S. Lakshmipriya - PG (Scholar)

M.E, Embedded Systems, Department of Electronic and Instrumentation Engineering,

Bannari Amman Institute of Technology, Sathyamangalam

Sathyamangalam,, Tamil Nadu

ABSTRACT

The paper mainly used in the implementation of Application Specific computer circuit designs. The skill

parallel prefix adders using FPGA’S. The carrycarry-tree benefit is mainly key with the increasing value of

adders constitute spanning tree adder, sparse Kogge

Kogge- mobile as well as portable physical science, which

Stone & Kogge-Stone Stone adder. It also presents a causes austere use of DSP functions (Yezerla, S.K. and

representation of the carry skip adder. The best B. Rajendra Naik, 2014).

resolution of the VLSI system is obtained by the Prefix

adders. Thus the implementation of the block diagram Though, because of the structure of the configurable

is difficult so the FPGA technology is used instead. logic as well as steering income in FPGA, parallel-

parallel

They produce the high efficiency of the layout using prefix adders can have an improved performance than

the FPGA analysis. Better delay and performance of the Very Large Scale Integration implementations. Field

RCA design in the 128 bits in the use of the fast

fast-chain Programmable Gate Arrays which are up to date use a

array. Xilinx Spartan 3E is used in the implementation fast-carry

carry chain that enhances the carry passageway

passage for

of the design. RCA is most commonly used in the the Ripple Carry Adder. From this paper, problems

implementation of the full adder and half adder. RCA is appeared in coming with as well as designing tree- tree

a serial which can perform many numbe number of the based adders on Field Programmable Gate Arrays are

addition but due to some situation delay occurs. Xilinx labeled. Assistant degree in luxurious testing criteria for

ISE is used in the simulation of the design. contrasting the feat of those adders is described (Roy,

S., et al.,

., 2014). Numerous tree-based

tree adder designs are

I. INTRODUCTION compulsory and featured on a Field Programmable

Gate Arrays as well as estimated with the Ripple Carry

Inn the binary addition unit, the main component in the Adder as well as also the Carry Skip Adder.

majority digital path classes together with digital signal

processors as well as micro chip find out passageway The binary adder is the critical element in most digital

units. Generally, severe examination carries on being circuit designs including digital signal processors

beneath fire at rising the capabilityy holdup time of the (DSP) and microprocessor data path units. As such,

adder (Hoe, D.H.K., et al.,., 2011). Reconfigurable extensive research continues to be focused on

logics such as Field Programmable Gate Arrays are improving the power delay performance of the adder.

most popular from the past few years and are latest in In VLSI implementations, parallel-prefix

paral adders are

technology. As significance, it provides us with the known to have the best performance. Reconfigurable

benefits of improved rate and nd power for DSP and logic such as Field Programmable Gate Arrays

microprocessor based resolutions for abundant (FPGAs) has been gaining in popularity in recent years

reasonable styles including mobile DSP as well as because it offers improved performance in terms of

telecommunications applications as well as a deep speed and power over DSP-based

based and

a microprocessor-

degradation in progress time as well as price on to based solutions for many practical designs involving

@ IJTSRD | Available Online @ www.ijtsrd.com | Volume – 2 | Issue – 1 | Nov-Dec

Dec 2017 Page: 1304

International Journal of Trend in Scientific Research and Development (IJTSRD) ISSN: 2456-6470

mobile DSP and telecommunications applications and a

significant reduction in development time and cost over

Application Specific Integrated Circuit (ASIC) designs.

The power advantage is especially important with the

growing popularity of mobile and portable electronics,

which make extensive use of DSP functions.

However, because of the structure of the configurable

logic and routing resources in FPGAs, parallel-prefix

adders will have a different performance than VLSI

implementations. In particular, most modern FPGAs

employ a fast-carry chain which optimizes the carry

path for the simple Ripple Carry Adder (RCA). In this

paper, the practical issues involved in designing and

implementing tree-based adders on FPGAs are

described. An efficient testing strategy for evaluating

the performance of these adders is discussed. Several

tree-based adder structures are implemented and Post process stage:

characterized on a FPGA and compared with the Ripple

Carry Adder (RCA) and the Carry Skip Adder (CSA). This is the final work out of the neglected set of

Finally, some conclusions and suggestions for instructions. This is similar for the adders.

improving FPGA designs to enable better tree based

Si =Pi xor Ci

adder performance are given.

Ci = (Pi . Co) + Gi

II. Parallel prefix adder:

Design:

It is a sort of a carry look ahead. It is designed in

High performance adders, also known as carry-tree

innumerable ways. These are fast adders and they are

adders, pre-compute the propagate and generate signals.

rapid adders. They are mainly used in the arithmetic

In tree adders, carries are generated in parallel and fast

calculations. The addition is mainly used here is a three

computation is obtained at the expense of increased

step process.

area and power. The main advantage of the design is

that the carry tree reduces the number of logic levels

Pre-processing adder: (N) by essentially generating the carries in parallel.

It is worked out produce and broadcast signals. A and B

In the proposed approach a high speed parallel prefix

are the inputs. It generates a carry output for the each

adder is proposed. In the proposed methodology, a high

input. These signals are given by the equations

speed kogge stone adder is realized using high speed

Pi = Ai xor Bi adder logic. The overall performance of the system is

Gi = Ai .Bi aimed to be improved in conditions of both area and

timing complexity. In the proposed method the carry

select adder is divided into further four blocks. In the

Carry generation network:

first unit simple half adder logic is implemented.

The carry is generated in the processing of the each bit. The parallel-prefix tree adders are more favorable in

This is done by the parallel process. To process the data terms of speed due to the complexity O(log2N) delay

in parallel they are substituted in the small items. The through the carry path compared to that of other adders.

process of generation of the carry bit and the addition The prominent parallel prefix tree adders are Kogge-

by the process of AND gate and the OR gates. The Stone, Brent-Kung, Han-Carlson, and Skanska. It was

following equations give the carry generation: found from the literature that Kogge-stone adder is the

fastest adder when compared to other adders. The adder

Pi:k = Pi:j . Pj-1:k priority in terms of worst-case delay is found to be

Gi:k = Gi:j +(Gj-1:k . Pi:j) Ripple-Carry, Carry-Look-Ahead, Carry- Select and

Kogge-Stone. This is due to the number of “Reduced

stages”. Kogge-Stone adder implementation is the most

straightforward, and also it has one of the shortest

@ IJTSRD | Available Online @ www.ijtsrd.com | Volume – 2 | Issue – 1 | Nov-Dec 2017 Page: 1305

International Journal of Trend in Scientific Research and Development (IJTSRD) ISSN: 2456-6470

critical paths of all tree adders. The drawback with the REFERENCE:

Kogge- Stone adder implementation is the large area

consumed and the more complex routing (Fan-Out) of 1. AhmetAkkas and Michael J Schult (2011), “A

interconnects. A Parallel Prefix Adder (PPA) is Decimal Floating-Point Fused Multiply-Add Unit

equivalent to the CLA adder. The two different in the with a Novel Decimal Leading-Zero

way their carry generation block is implemented. Anticipator”, AMD IEEE.

The parallel prefix carry look- ahead adder was first 2. Anitha R and BagyaveereswaranV(2012), “High

proposed some twenty years ago as a means of Performance Parallel Prefix Adders with Fast Carry

accelerating n-bit addition in VLSI technology. It Chain Logic”,International Journal ofVLSI Design

widely considered as the fastest adder and used for high &Communication Systems, Vol. 3, No. 2,pp. 01-10,

performance arithmetic circuits in the industries. A ISSN 0976-6499.

three step process is generally involved in the

construction of a Parallel Prefix Adder. The first step 3. David Jeff Jackson and Sidney Joel Hannah (1993),

involves the creation of generate and propagate signals “Modeling and Comparison of Adder Designs with

for the input operand bits. The second step involves the Verilog HDL”, 25th South-Eastern Symposium on

generation of carry signals. In the final step, the sum System Theory, March, pp. 406-410.

bits of the adder following stages of the operand bits 4. Kogge P and Stone H (1973), “A Parallel

and the preceding stage carry bit using a xor gate. Algorithm for the Efficient Solution of a General

Class of Recurrence Relations”, IEEE

RESULT AND DISCUSSION: Transactionson Computers, Vol. C-22, No. 8, pp.

786-793.

The proposed technique is executed using the Xilinx

Spartan 3 FPGA and Verilog language is used for the 5. Krishna Kumari V, Sri Chakrapani Y and Kamaraju

implementation of the design. The technique is M (2013), “Design and Characterization of

associated with the basic RCA approach and the result Koggestone, Sparse Koggestone, Spanning Tree

shows an enhancement in both the area consumed by and Brentkung Adders”, International Journalof

the device and the maximum combinational path delay. Scientific & Engineering Research, Vol. 4, No. 10,

In Table 1 the comparison of both the approaches is pp. 1502-1506, ISSN 2229-5518.

shown on the basis of various performance parameters 6. Madhu Thakur and Javed Ashraf (2012),“Design of

like number of slices, number of look up tables, delay Braun Multiplier with Kogge-Stone Adder & It’s

and maximum operating frequency. Number of slices, Implementation on FPGA”, International Journal

number of 4 input LUTs are a amount of the number of of Scientific& Engineering Research, Vol. 3, No.

resources used by the FPGA which comes out to be less 10,pp. 03-06, ISSN 2229-5518.

in case of the proposed approach.

7. NurdianiZamhari, Peter Voon, KuryatiKipli, Kho

CONCLUSION: Lee Chin and MaimunHujaHusin (2012),

“Comparison of Parallel Prefix Adder (PPA)”,

This paper presents an innovative way of modifying the Proceedings of the World Congress on Engineering,

already existing Kogge-Stone adder by re-routing WCE, Vol. 2, July 4-6, London, UK.

(wiring) and Black-cell reduction for increasing the

speed of execution. The design originates from the

principle of removing the redundant black cells and

compensating this removed cells by rerouting.

Arithmetic unit is the most widely researched and used

designs in the digital electronics circuits. Many

researchers in recent past have proposed different

approaches for the design of adders and other logical

circuits and compared their merits and demerits with

the existing approaches. Parallel prefix adder is

designed in this approach by using optimized CSLA in

terms of area and speed.

@ IJTSRD | Available Online @ www.ijtsrd.com | Volume – 2 | Issue – 1 | Nov-Dec 2017 Page: 1306

You might also like

- Bhattacharjee 2011Document5 pagesBhattacharjee 2011harithNo ratings yet

- ECE Project Abstract PDFDocument6 pagesECE Project Abstract PDFkondareddy pathapatiNo ratings yet

- ECE Project Abstract2015 PDFDocument6 pagesECE Project Abstract2015 PDFkondareddy pathapatiNo ratings yet

- Lal15IJAERArif2015 PDFDocument6 pagesLal15IJAERArif2015 PDFkondareddy pathapatiNo ratings yet

- ECE Project Abstract2015 PDFDocument6 pagesECE Project Abstract2015 PDFkondareddy pathapatiNo ratings yet

- Chapter 1Document6 pagesChapter 1db.rama krishna ReddyNo ratings yet

- Systolic FIR Filter Design With Various Parallel Prefix Adders in FPGA: Performance AnalysisDocument5 pagesSystolic FIR Filter Design With Various Parallel Prefix Adders in FPGA: Performance AnalysishariNo ratings yet

- Real-Time Speech Pitch Shifting On An FPGA (Estephan Sawyer WanningerDocument20 pagesReal-Time Speech Pitch Shifting On An FPGA (Estephan Sawyer Wanningerklumpakojis0% (1)

- Design of Parallel Prefix Adder For High Speed ApplicationsDocument6 pagesDesign of Parallel Prefix Adder For High Speed ApplicationsAmshuman GkNo ratings yet

- 1 s2.0 S0026269219303799 MainDocument13 pages1 s2.0 S0026269219303799 MainShylu SamNo ratings yet

- No Guera 2011Document11 pagesNo Guera 2011DomRuanNo ratings yet

- Asynchronous Hybrid Kogge-Stone Structure Carry Select Adder Based IEEE-754 Double-Precision Floating-Point AdderDocument8 pagesAsynchronous Hybrid Kogge-Stone Structure Carry Select Adder Based IEEE-754 Double-Precision Floating-Point AdderYermakov Vadim IvanovichNo ratings yet

- DOC-Reducing The Hardware Complexity of A Parallel Prefix AdderDocument48 pagesDOC-Reducing The Hardware Complexity of A Parallel Prefix AdderSai Teja100% (1)

- Microprocessors and Microsystems: Prateek Sikka, Abhijit R. Asati, Chandra ShekharDocument6 pagesMicroprocessors and Microsystems: Prateek Sikka, Abhijit R. Asati, Chandra ShekharBhargav BhatNo ratings yet

- 652413ijsetr2411 0102Document7 pages652413ijsetr2411 0102sreelakshmi.ece eceNo ratings yet

- Fast Powerand Performance Evaluationof FPGAbased Wireless Communication SystemsDocument15 pagesFast Powerand Performance Evaluationof FPGAbased Wireless Communication SystemsShashank RocksNo ratings yet

- Energyefficient Backend Compiler Design For Embedded SystemsDocument7 pagesEnergyefficient Backend Compiler Design For Embedded Systemsaishpradik RRVNo ratings yet

- Implementation of DSP Algorithms On Reconfigurable Embedded PlatformDocument7 pagesImplementation of DSP Algorithms On Reconfigurable Embedded PlatformGV Avinash KumarNo ratings yet

- Chapter 1Document39 pagesChapter 1Kalyan Reddy AnuguNo ratings yet

- Signal Processing: Image Communication: B. Krill, A. Ahmad, A. Amira, H. RabahDocument11 pagesSignal Processing: Image Communication: B. Krill, A. Ahmad, A. Amira, H. RabahŢoca CosminNo ratings yet

- DOC-Reducing The Hardware Complexity of A Parallel Prefix AdderDocument46 pagesDOC-Reducing The Hardware Complexity of A Parallel Prefix AdderSai Teja100% (1)

- Performance Analysis of Fast Adders Using VHDL: January 2009Document6 pagesPerformance Analysis of Fast Adders Using VHDL: January 2009ssabinayaa12No ratings yet

- Abcdplace Tcad2020 LinDocument13 pagesAbcdplace Tcad2020 LinEric WangNo ratings yet

- High Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDocument5 pagesHigh Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDrSakthivelNo ratings yet

- Vardhini 2021Document7 pagesVardhini 2021Abdelkbir WsNo ratings yet

- FPGA Code Accelerators - The Compiler Perspective: Conference PaperDocument7 pagesFPGA Code Accelerators - The Compiler Perspective: Conference Paperadarsh mishraNo ratings yet

- CCDE Training OutlineDocument14 pagesCCDE Training OutlineSrishti BaliyanNo ratings yet

- Efficient Design Using Fpgas: of Application Specific CoresDocument5 pagesEfficient Design Using Fpgas: of Application Specific CoresK.GurucharanNo ratings yet

- Digital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaDocument23 pagesDigital Signal Processing Designing For FPGA Architectures: Mariusz Rawski, Bogdan J. Falkowski, and Tadeusz ŁubaSrinivas CherukuNo ratings yet

- New Performance-Driven FPGA Routing Algorithms: Michael J. Alexander,, and Gabriel RobinsDocument13 pagesNew Performance-Driven FPGA Routing Algorithms: Michael J. Alexander,, and Gabriel RobinsAmira A. MehrizNo ratings yet

- Sine/Cosine Generator Using Pipelined CORDIC Processor: R. Ranga Teja, P. Sudhakara Reddy, IEEE, MemberDocument4 pagesSine/Cosine Generator Using Pipelined CORDIC Processor: R. Ranga Teja, P. Sudhakara Reddy, IEEE, MemberMohamed GanounNo ratings yet

- Parallel Prefix AdderDocument4 pagesParallel Prefix AdderArjun RamNo ratings yet

- Performance Evaluation of Fixed-Point Array Multipliers On Xilinx FpgasDocument5 pagesPerformance Evaluation of Fixed-Point Array Multipliers On Xilinx FpgasMeghanand KumarNo ratings yet

- Ullah 2021Document14 pagesUllah 2021roopa_kothapalliNo ratings yet

- A Fully Pipelined and Dynamically Composable Architecture of CGRADocument9 pagesA Fully Pipelined and Dynamically Composable Architecture of CGRABanusha chandranNo ratings yet

- Adarsh Patil: Personal DetailsDocument4 pagesAdarsh Patil: Personal DetailsAdarsh PatilNo ratings yet

- VlsiDocument32 pagesVlsibalasaravanan0408No ratings yet

- Kulmala - Scalable MPEG-4 Encoder oDocument15 pagesKulmala - Scalable MPEG-4 Encoder obinazharNo ratings yet

- PP AdderDocument33 pagesPP AddermariadomNo ratings yet

- Design of Arithmetic Unit For High Speed Performance Using Vedic MathematicsDocument6 pagesDesign of Arithmetic Unit For High Speed Performance Using Vedic MathematicssaraNo ratings yet

- Fraisse 2018Document8 pagesFraisse 2018aham krishnahaNo ratings yet

- Design of High Speed 128 Bit Parallel Prefix Adders: T.Kiran Kumar, P.SrikanthDocument4 pagesDesign of High Speed 128 Bit Parallel Prefix Adders: T.Kiran Kumar, P.SrikanthPasumarthy SrikanthNo ratings yet

- Pipeline Dae S With FeedbackDocument10 pagesPipeline Dae S With Feedbackyame asfiaNo ratings yet

- An Efficient ASIC Architecture For Real-Time Edge DetectionDocument10 pagesAn Efficient ASIC Architecture For Real-Time Edge Detectionprakashjyoti0901No ratings yet

- Choi Asap14 KmeansDocument8 pagesChoi Asap14 KmeansjefferyleclercNo ratings yet

- FPGA Implementation of Hybrid Han-Carlson AdderDocument4 pagesFPGA Implementation of Hybrid Han-Carlson AdderRENJITH GNo ratings yet

- Major Conference PaperDocument14 pagesMajor Conference Papermanishmeenahlm2No ratings yet

- Design and Testing of Systolic Array Multiplier Using Fault Injecting SchemesDocument9 pagesDesign and Testing of Systolic Array Multiplier Using Fault Injecting SchemesCSIT iaesprimeNo ratings yet

- Energy-Ef Cient Low-Latency Signed Multiplier For FPGA-based Hardware AcceleratorsDocument4 pagesEnergy-Ef Cient Low-Latency Signed Multiplier For FPGA-based Hardware AcceleratorsTRIAD TECHNO SERVICESNo ratings yet

- Fpgas and DSP: Design Alternatives For DSP SolutionsDocument8 pagesFpgas and DSP: Design Alternatives For DSP Solutionsnguyendinh126No ratings yet

- Design and Implementation of High Speed Carry Select AdderDocument6 pagesDesign and Implementation of High Speed Carry Select AdderseventhsensegroupNo ratings yet

- Performance Analysis and Implementation 097e10b9Document20 pagesPerformance Analysis and Implementation 097e10b9balasaravanan0408No ratings yet

- Implementation of Full Adder at One Terabyteper Second Speed Using CadenceDocument5 pagesImplementation of Full Adder at One Terabyteper Second Speed Using Cadenceanil kasotNo ratings yet

- Performance, Analysis and Comparison of Digital Adders: Jasmine Saini Somya Agarwal, Aditi KansalDocument4 pagesPerformance, Analysis and Comparison of Digital Adders: Jasmine Saini Somya Agarwal, Aditi Kansalssabinayaa12No ratings yet

- Design and Implementation of Efficient 4x4 Vedic Multiplier For DSP ApplicationsDocument6 pagesDesign and Implementation of Efficient 4x4 Vedic Multiplier For DSP Applicationsrakesh hiremathNo ratings yet

- 22.multioperand Redundant Adders On FPGAsDocument13 pages22.multioperand Redundant Adders On FPGAsadaNo ratings yet

- DSP Architecture Design EssentialsDocument353 pagesDSP Architecture Design Essentialssup3rnarutoNo ratings yet

- FPGA Dynamic and Partial Reconfiguration: A Survey of Architectures, Methods, and ApplicationsDocument39 pagesFPGA Dynamic and Partial Reconfiguration: A Survey of Architectures, Methods, and Applicationssrinivas eNo ratings yet

- Chapter-2: Literature ReviewDocument11 pagesChapter-2: Literature ReviewPritam SirpotdarNo ratings yet

- Sustainable EnergyDocument8 pagesSustainable EnergyEditor IJTSRDNo ratings yet

- Design Simulation and Hardware Construction of An Arduino Microcontroller Based DC DC High Side Buck Converter For Standalone PV SystemDocument6 pagesDesign Simulation and Hardware Construction of An Arduino Microcontroller Based DC DC High Side Buck Converter For Standalone PV SystemEditor IJTSRDNo ratings yet

- Deconstructing The Hijra Narrative Reimagining Trans Identities Through Literary PerspectivesDocument6 pagesDeconstructing The Hijra Narrative Reimagining Trans Identities Through Literary PerspectivesEditor IJTSRDNo ratings yet

- Educational Unity Embracing Diversity For A Stronger SocietyDocument6 pagesEducational Unity Embracing Diversity For A Stronger SocietyEditor IJTSRDNo ratings yet

- A Pharmaceutical Review On Kaanji and Its Wide Range of ApplicabilityDocument6 pagesA Pharmaceutical Review On Kaanji and Its Wide Range of ApplicabilityEditor IJTSRDNo ratings yet

- An Analysis On The Use of Image Design With Generative AI TechnologiesDocument4 pagesAn Analysis On The Use of Image Design With Generative AI TechnologiesEditor IJTSRDNo ratings yet

- Women Before and After Islam With Special Reference To ArabDocument3 pagesWomen Before and After Islam With Special Reference To ArabEditor IJTSRDNo ratings yet

- Collective Bargaining and Employee Prosocial Behaviour in The Hospitality Sector in Port HarcourtDocument10 pagesCollective Bargaining and Employee Prosocial Behaviour in The Hospitality Sector in Port HarcourtEditor IJTSRDNo ratings yet

- Differential Equations Third Order Inhomogeneous Linear With Boundary ConditionsDocument6 pagesDifferential Equations Third Order Inhomogeneous Linear With Boundary ConditionsEditor IJTSRDNo ratings yet

- Activating Geospatial Information For Sudans Sustainable Investment MapDocument13 pagesActivating Geospatial Information For Sudans Sustainable Investment MapEditor IJTSRDNo ratings yet

- International Journal of Trend in Scientific Research and Development (IJTSRD)Document13 pagesInternational Journal of Trend in Scientific Research and Development (IJTSRD)Editor IJTSRDNo ratings yet

- Artificial Intelligence A Boon in Expanding Online Education Through Social Media and Digital Marketing Post Covid 19Document9 pagesArtificial Intelligence A Boon in Expanding Online Education Through Social Media and Digital Marketing Post Covid 19Editor IJTSRDNo ratings yet

- Challenges Faced by The Media in An Attempt To Play Their Roles in Public Awareness On Waste Management in Buea and DoualaDocument18 pagesChallenges Faced by The Media in An Attempt To Play Their Roles in Public Awareness On Waste Management in Buea and DoualaEditor IJTSRDNo ratings yet

- Sustainable Development A PrimerDocument9 pagesSustainable Development A PrimerEditor IJTSRDNo ratings yet

- Role of Dashamooladi Niruha Basti Followed by Katibasti in The Management of "Katigraha" W.R.S To Lumbar Spondylosis A Case StudyDocument3 pagesRole of Dashamooladi Niruha Basti Followed by Katibasti in The Management of "Katigraha" W.R.S To Lumbar Spondylosis A Case StudyEditor IJTSRDNo ratings yet

- Consumers' Impulsive Buying Behavior in Social Commerce PlatformsDocument5 pagesConsumers' Impulsive Buying Behavior in Social Commerce PlatformsEditor IJTSRDNo ratings yet

- An Investigation of The Temperature Effect On Solar Panel Efficiency Based On IoT TechnologyDocument7 pagesAn Investigation of The Temperature Effect On Solar Panel Efficiency Based On IoT TechnologyEditor IJTSRDNo ratings yet

- Knowledge Related To Diabetes Mellitus and Self Care Practice Related To Diabetic Foot Care Among Diabetic PatientsDocument4 pagesKnowledge Related To Diabetes Mellitus and Self Care Practice Related To Diabetic Foot Care Among Diabetic PatientsEditor IJTSRDNo ratings yet

- Evan Syndrome A Case ReportDocument3 pagesEvan Syndrome A Case ReportEditor IJTSRDNo ratings yet

- To Assess The Knowledge and Attitude of Non Professionals Regarding COVID 19 Vaccination A Descriptive StudyDocument4 pagesTo Assess The Knowledge and Attitude of Non Professionals Regarding COVID 19 Vaccination A Descriptive StudyEditor IJTSRDNo ratings yet

- Effectiveness of Video Teaching Program On Knowledge Regarding 5Fs of Disease Transmission Food, Finger, Fluid, Fomite, Faces Among Children at Selected Setting, ChennaiDocument3 pagesEffectiveness of Video Teaching Program On Knowledge Regarding 5Fs of Disease Transmission Food, Finger, Fluid, Fomite, Faces Among Children at Selected Setting, ChennaiEditor IJTSRDNo ratings yet

- A Study To Assess The Effectiveness of Art Therapy To Reduce Depression Among Old Age Clients Admitted in Saveetha Medical College and Hospital, Thandalam, ChennaiDocument5 pagesA Study To Assess The Effectiveness of Art Therapy To Reduce Depression Among Old Age Clients Admitted in Saveetha Medical College and Hospital, Thandalam, ChennaiEditor IJTSRDNo ratings yet

- Challenges in Pineapple Cultivation A Case Study of Pineapple Orchards in TripuraDocument4 pagesChallenges in Pineapple Cultivation A Case Study of Pineapple Orchards in TripuraEditor IJTSRDNo ratings yet

- H1 L1 Boundedness of Rough Toroidal Pseudo Differential OperatorDocument8 pagesH1 L1 Boundedness of Rough Toroidal Pseudo Differential OperatorEditor IJTSRDNo ratings yet

- Financial Risk, Capital Adequacy and Liquidity Performance of Deposit Money Banks in NigeriaDocument12 pagesFinancial Risk, Capital Adequacy and Liquidity Performance of Deposit Money Banks in NigeriaEditor IJTSRDNo ratings yet

- Importance of Controlled CreditDocument3 pagesImportance of Controlled CreditEditor IJTSRDNo ratings yet

- An Approach To The Diagnostic Study On Annavaha Srotodusti in Urdwaga Amlapitta WSR To Oesophagogastroduodenoscopic ChangesDocument4 pagesAn Approach To The Diagnostic Study On Annavaha Srotodusti in Urdwaga Amlapitta WSR To Oesophagogastroduodenoscopic ChangesEditor IJTSRDNo ratings yet

- A Study On Human Resource AccountingDocument3 pagesA Study On Human Resource AccountingEditor IJTSRDNo ratings yet

- Concept of Shotha W.S.R To Arishta LakshanaDocument3 pagesConcept of Shotha W.S.R To Arishta LakshanaEditor IJTSRDNo ratings yet

- A Study To Assess The Knowledge Regarding Iron Deficiency Anemia Among Reproductive Age Women in Selected Community ThrissurDocument4 pagesA Study To Assess The Knowledge Regarding Iron Deficiency Anemia Among Reproductive Age Women in Selected Community ThrissurEditor IJTSRDNo ratings yet

- Clase 1-Fisiopatología de La Artritis ReumatoideaDocument45 pagesClase 1-Fisiopatología de La Artritis ReumatoideaPercy Williams Mendoza EscobarNo ratings yet

- Tyler. The Worship of The Blessed Virgin Mary in The Church of Rome: Contrary To Holy Scripture, and To The Faith and Practice of The Church of Christ Through The First Five Centuries. 1844.Document438 pagesTyler. The Worship of The Blessed Virgin Mary in The Church of Rome: Contrary To Holy Scripture, and To The Faith and Practice of The Church of Christ Through The First Five Centuries. 1844.Patrologia Latina, Graeca et Orientalis0% (1)

- Laboratory Exercise No. 2A. Microscopic Observation of Bacteria - Sep 13Document6 pagesLaboratory Exercise No. 2A. Microscopic Observation of Bacteria - Sep 13Adrian MiguelNo ratings yet

- Power To Regulate Practice of LawDocument27 pagesPower To Regulate Practice of LawSarah Jade LayugNo ratings yet

- View ResultDocument1 pageView ResultHarshal RahateNo ratings yet

- Project MaricoDocument23 pagesProject Maricoharishma29100% (1)

- Visual Interpretation QuestionsDocument7 pagesVisual Interpretation Questionssoomro76134No ratings yet

- Anime ListDocument9 pagesAnime ListTeofil MunteanuNo ratings yet

- Sharm o Hayaa-AshaarDocument127 pagesSharm o Hayaa-Ashaarbari bhattiNo ratings yet

- Cawis vs. Cerilles - G.R. No. 170207 - April 19, 2010Document2 pagesCawis vs. Cerilles - G.R. No. 170207 - April 19, 2010Lordy Jessah AggabaoNo ratings yet

- Personal Development: Quarter 2 - Module 19: Becoming Responsible in Personal RelationshipsDocument27 pagesPersonal Development: Quarter 2 - Module 19: Becoming Responsible in Personal RelationshipsSamantha Beatriz B ChuaNo ratings yet

- Microbiology Best Laboratory PracticesDocument47 pagesMicrobiology Best Laboratory PracticesQAV_CRS100% (1)

- Katapayadi SystemDocument5 pagesKatapayadi Systemnieotyagi100% (2)

- 1st Summative Test in Mapeh 8Document4 pages1st Summative Test in Mapeh 8Mary JuanNo ratings yet

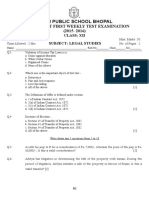

- Legal Studies XII - Improvement First Weekly Test - 2Document3 pagesLegal Studies XII - Improvement First Weekly Test - 2Surbhit ShrivastavaNo ratings yet

- Designing Organizational Structure: Authority and ControlDocument48 pagesDesigning Organizational Structure: Authority and ControlArvind DawarNo ratings yet

- The Birth of The Bipolar Disorder: Historical ReviewDocument10 pagesThe Birth of The Bipolar Disorder: Historical ReviewFELIPE ABREONo ratings yet

- Corporation Law Cases Set 1Document32 pagesCorporation Law Cases Set 1Rodney AtibulaNo ratings yet

- Tenses MergedDocument76 pagesTenses MergedMihály Bence SzabóNo ratings yet

- BD20203 - Lecture Note Week 4 - Bank Negara MalaysiaDocument40 pagesBD20203 - Lecture Note Week 4 - Bank Negara MalaysiaLim ShengNo ratings yet

- 09Document69 pages09Sakshi VermaNo ratings yet

- Test Bank For Essentials of Life Span Development 6th Edition John SantrockDocument60 pagesTest Bank For Essentials of Life Span Development 6th Edition John Santrockhanhvaleriefq7uNo ratings yet

- Api 119Document8 pagesApi 119hokhmologNo ratings yet

- SLICS Classification DetailedDocument7 pagesSLICS Classification DetailedOj AlimbuyuguenNo ratings yet

- UGC NET June 2012 NotificationDocument2 pagesUGC NET June 2012 Notificationsan2santoshNo ratings yet

- Oral-Communication WEEK 5Document18 pagesOral-Communication WEEK 5Alkin RaymundoNo ratings yet

- Review Brent Strawn The Old Testament Is Dying PDFDocument6 pagesReview Brent Strawn The Old Testament Is Dying PDFCarl GriffinNo ratings yet

- Fise Tehnice Ancore Standard PDFDocument48 pagesFise Tehnice Ancore Standard PDFcrnkarlosNo ratings yet

- Covid FeversDocument7 pagesCovid FeversdbvidyaNo ratings yet

- Indian MuseumsDocument32 pagesIndian MuseumsRavi ShankarNo ratings yet