Professional Documents

Culture Documents

Electrónica Digital

Uploaded by

Hiram LoyaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrónica Digital

Uploaded by

Hiram LoyaCopyright:

Available Formats

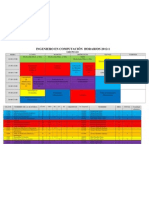

Electrónica Digital 1

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Examen Unidad 6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 1

Electrónica Digital 2

Portafolio de evidencias

INSTITUTO TECNOLÓGICO DE CD. JUÁREZ

Examen unidad 6 ELECTRONICA DIGITAL Titular de la materia: Ing. Armando Peinado Rentería.

Nombre:____________________________ carrera:_________________

Aula:________ clave:_____ hora de clase:_________ fecha:______________

1) ¿Qué es un temporizador?

2) Diferencia entre un circuito 555 monoestable - astable

3) Tipos de flip flop

4) ¿Qué es un maestro – esclavo?

5) ¿Qué es un síncrono?

6) ¿Qué es un circuito asíncrono?

7) Dibujar el modelo de moore

8) ¿Que es una memoria?

9) Tipos de memoria

10) ¿Qué son los circuitos lógicos prográmales?

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 2

Electrónica Digital 3

Portafolio de evidencias

1. Aparato mediante la cual podemos regular la conexión o desconexión de un

circuito eléctrico basado en un tiempo

2. El mono estable entrega un solo pulso de un ancho establecido por el

diseño y el estable se caracteriza por una salida de onda cuadrada

3. R-S, J-K, D, T, maestro-esclavo

4. Son contruidos a partir de dos flip flops uno sirve de maestro y otro sirve de

esclavo atraves de una compuerta, los datos de entrada se transmiten a a

ls salida del filp flop maestro

5. Un flip flop sincronisado

6. Un flip flop desincronisado

7. Dibujo

8. Circuito electrónico capaz de almacenar y reproducir una información digital

durante un cierto tiempo.

9. RAM, ROM, DRAM, SRAM

10. (PLD) es un componente electrónico usado para construir circuitos digitales

reconfigurables

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 3

Electrónica Digital 4

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Mapa Conceptual U6

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 4

Electrónica Digital 5

Portafolio de evidencias

Circuitos Secuenciales

Tenemos

Maquinas Mealy y Maquinas Moore

Temporizadores

Permiten FLIP FLOPS

Son

Unir expresiones

booleanas Se diferencian

Una expresión booleana es

Tipos

una sucesión de símbolos

que incluye 0,1, algunas

And

R-S

variables y las operaciones

booleanas. Or

Not

Tipos J-K

a == b

a != b

a<b

a <= b Maestro-Esclavo

a>b

a >= b

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 5

Electrónica Digital 6

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Mapa Mental U6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 6

Electrónica Digital 7

Portafolio de evidencias

Circuitos secuenciales

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 7

Electrónica Digital 8

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Lista de asistencia U6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 8

Electrónica Digital 9

Portafolio de evidencias

Semestre: Agosto/Diciembre 2017 MES: Octubre

CONTROL DE ASISTENCIA DIARIA/MENSUAL

N° NOMBRE Y APELLIDO 04 05 06 07 08 11 12 13 14 15 18 19 20 21 22 25 26 27 28 29 P A

1 Arellano Briones Dafne

2 García Peña Paulina

3 García Santos Jonathan Ramón

4 Loya González Hiram Emmanuel

5 Naquid Ramírez Sergio Antonio

=Asistencia

X = Falta

P = Práctica

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 9

Electrónica Digital 10

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Exposición Unidad 6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 10

Electrónica Digital 11

Portafolio de evidencias

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 11

Electrónica Digital 12

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Apuntes tomados en clase

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 12

Electrónica Digital 13

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Tarea de Investigación U6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 13

Electrónica Digital 14

Portafolio de evidencias

Máquinas de Mealy y Moore son circuitos sin cronos. Un circuito síncrono es un

circuito digital en el cual sus partes están sincronizadas por una señal de reloj. En

un circuito síncrono ideal, cada cambio en los diferentes niveles lógicos es

simultáneo. Estas transacciones se realizan después de un cambio de nivel de una

señal llamada reloj. Idealmente a la entrada a cada elemento de almacenamiento

alcanza su valor final antes de que la siguiente señal de reloj ocurra, por lo tanto el

comportamiento de un circuito se puede predecir exactamente. Se requiere de cierto

retardo para cada operación lógica, por lo que existe una máxima rapidez en el que

cada sistema síncrono puede responder. El análisis de un diagrama de tiempo

puede darnos esta rapidez. Una máquina de Mealy es una máquina de estados finita

donde las salidas están determinadas por el estado actual y la entrada. Esto

significa que en el diagrama de estados se incluye una señal de salida para cada

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 14

Electrónica Digital 15

Portafolio de evidencias

arista de transición. Por ejemplo, en la trayectoria del estado 1 a un estado 2, si la

entrada es 0 la salida puede ser 1, y se debe poner sobre la arista la etiqueta “0-1”

en contraste, la salida de una máquina de estado finito Moore, depende solo del

estado actual y no depende de la entrada actual. Por lo tanto, los estados de una

máquina de Moore son la unión de los estados de la máquina de Mealy y el producto

cartesiano de estos estados y alfabeto de entrada (posibles entradas), máquinas de

Mealy máquina de Moore la salida depende del estado actual y de las entradas la

salida depende solo del estado actual por lo regular, tiene menos número de

estados el número de estados es mayor o igual a la máquina de Mealy es menos

estable es más estable para probar un circuito primero se hace el cambio en la

entrada X y después se da el pulso del reloj para probar un circuito primero se da el

pulso del reloj y después se hace el cambio en la entrada X la salidas se encuentran

en la arista las salidas se encuentran dentro del estado AGPS 2-2 definición formal:

una máquina de Moore se define como una tupla (secuencia finita) de 5 { S, Σ, Λ,

T, G} que consiste de:

Un conjunto finito de estados (S).

Un conjunto finito llamado alfabeto de entrada (Σ).

Una función de transición (T).

Un conjunto finito llamado alfabeto de salida (Λ).

Una función de transición (T : S x Σ → S) que dirige a cada estado o a cada

entrada al siguiente estado.

Una función de salida (G : S → Λ) que dirige a cada estado al alfabeto de

salida.

El número de estados en una máquina de Moore es mayor o igual al número de

estados a subcorrespondiente máquina de Mealy. Una máquina de Mealy es una

tupla de 6 (S, S0, Σ, Λ, T, G), que consiste de:

Un conjunto finito de estados (S).

Un estado inicial S0 el cual es un elemento de (S).

Un conjunto finito llamado alfabeto de entrada (Σ).

Un conjunto finito llamado alfabeto de salida (Λ).

Una función de transición (T : S x Σ → S).

Una función de salida (G : S x Σ → Λ).

Se denomina temporizador a dispositivo mediante el cual podemos regular la

conexión o desconexión de un circuito eléctrico durante un tiempo determinado.

El temporizador es un tipo de relé auxiliar, pero se diferencia en que sus contactos

no cambian de posición instantáneamente.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 15

Electrónica Digital 16

Portafolio de evidencias

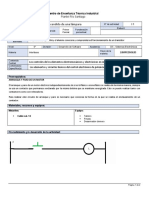

Circuito integrado 555

Los circuitos integrados son circuitos funcionales que han sido reducidos a unos

cuantos milímetros y colocados dentro de encapsulados como los que se muestran

en la imagen.

Existen circuitos integrados de toda clase y para todas las funciones que se desee.

De hecho, arduino nace a partir de un circuito integrado (AT mega).

El primer circuito integrado será el NE 555.

CIRCUITO INTEGRADO 555

El N 555 es un circuito muy sencillo pero con múltiples usos.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 16

Electrónica Digital 17

Portafolio de evidencias

Se usa principalmente como temporizador – oscilador. Dependiendo de las

conexiones de sus patas se puede obtener diferentes resultados. Incluso este

dispositivo puede ser utilizado como amplificador operacional.

Uno de los primeros post que hice fue el de como encender y hacerlo parpadear

con arduino.

Existen dos posibles configuraciones para el 555, ya sea la configuración

monoestable o la biestable.

Configuración monoestable

El circuito 555 permanece en un solo estado (encendido o apagado) durante un

periodo de tiempo determinado por el usuario.

Normalmente la configuración más utilizada para armar un circuito 555 monoestable

es la siguiente:

Si no están acostumbrados a la simbología de los circuitos electrónicos aquí les

presento una breve descripción:

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 17

Electrónica Digital 18

Portafolio de evidencias

Pero ¿Cómo funciona este circuito? Pues es sencillo el circuito se enviara con un

pulso (voltaje) durante un tiempo determinado. Dicho tiempo puede ser establecido

por el usuario.

El retardo obedece la siguiente ecuación:

T= In(3) * R * C

Donde T representa el tiempo en segundos, R es la resistencia que sale en el

diagrama y C es la capacitancia de condensador (capacitor) que se encierra en el

recuadro.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 18

Electrónica Digital 19

Portafolio de evidencias

En la imagen por ejemplo, la resistencia es de 50 K ohm y la capacitancia es de 100

microfaradios. Si calculamos el tiempo:

T=(In(3))*50000*0.0001=5.49 segundos

Es decir, cuando se dispare el circuito led permanecerá encendido durante 5.49

segundos. Pero, ¿Cómo se dispara el circuito?

Los flip flop son dispositivos síncronos de dos estados (estado alto y estado bajo),

también conocidos como multivibradores biestables. La salida de estado cambia de

manera sincronizada con el pulso del reloj.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 19

Electrónica Digital 20

Portafolio de evidencias

Un flip flop de disparo por flanco cambia de estado con el flanco positivo (flanco de

subida) o con flanco negativo (flanco de bajada) del impulso de reloj y solo es

sensible a sus entradas solo en esa transición del reloj.

Los flip flop son unidades básicas de todos los sistemas secuenciales, existen

cuatro tipos: el SR, el JK, el T y el D. Y los últimos tres son implementados a partir

del primero.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 20

Electrónica Digital 21

Portafolio de evidencias

Flip flop SR

Tabla

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 21

Electrónica Digital 22

Portafolio de evidencias

Ecuación

Flip flop JK

Tabla

Ecuación

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 22

Electrónica Digital 23

Portafolio de evidencias

Flip flop D

Tabla

Flip flop T

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 23

Electrónica Digital 24

Portafolio de evidencias

Tabla

Flip flop maestro esclavo

Los flip flop maestro- esclavo son construidos a partir con dos flip flop uno sirve de

maestro y otro de esclavo durante el pulso del reloj se habilita el de maestro y otro

de esclavo. Durante la subida del pulso del reloj se habilita el de maestro y se

deshabilita el del esclavo a través de la compuerta not puesta a la entrada del clock

del segundo flip flop. Los datos de entrada se transmiten a la salida del flip flop

maestro. Cuando el pulso baja nuevamente a cero se deshabilita el maestro lo cual

evita que lo afecten las entradas externas y se habilita el esclavo. Entonces el

esclavo pasa al mismo estado del maestro.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 24

Electrónica Digital 25

Portafolio de evidencias

Ecuación de estado y ecuación de la salida en espacio de estados...

Junio 2, 2012 in Control Automático, Control Teory, Espacio de Estado, LTI MIMO

SISO Universidad Nacional de Ingeniería

En toda la literatura se reporta que luego de plantear la definición de espacio de

estado llegan a las siguientes ecuaciones:

X´ (t)=f(x, u, t)

Y (t)=g(x, u, t)

Que son la ecuación de estado y la ecuación de la salida respectivamente. Si las

funciones vectoriales f(x, u, t) y/o g(x, u, t) involucran explícitamente el tiempo “t”, el

sistema se denomina sistema variante con el tiempo si se analizan las ecuaciones

mencionadas alrededor del estado de operación, tenemos las siguientes

ecuaciones de estado y de salidas linealizadas.

X´ (t)= A(txt) + B(t)u(t)

Y (t)= C(t)x(t) + D(t)u(t)

En donde A(t) se denomina matriz de estado, B(t) matriz de entrada, C(t) matriz de

salida y D(t) matriz de transmisión directa. Un diagrama de bloques que representa

estas dos últimas ecuaciones se da a continuación.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 25

Electrónica Digital 26

Portafolio de evidencias

Si las funciones vectoriales f(x, u, t) y g(x, u, t) no involucran el tiempo “t”

explícitamente, el sistema se denomina sistema invariante con el tiempo. En este

caso, las ecuaciones se simplifican a:

X´ (t)= Ax(t) + Bu(t)

Y(t)= Cx(t) + Du(t)

En donde la primera ecuación es la ecuación de estado del sistema lineal e

invariante con el tiempo, y la segunda ecuación, es la ecuación de salida para el

mismo sistema.

ASINCRONO Y SINCRONO

SINCRONO

En un sistema de comunicación, el transmisor debe coordinarse con el receptor

antes de él envió de datos con frecuencia, la sincronización se maneja haciendo

que el hardware envié un pulso regular al no haber datos disponibles. El receptor

usa los pulsos para determinar el comienzo y el fin de los bits. Son procesos

síncronos los que dependen de un acontecimiento externo que lo dispara.

Fracción de tiempo: Intervalo fijo de tiempo que se asigna que se asigna a

cada usuario o programa en un sistema multitarea o de tiempo compartido.

Ranura de tiempo: Intervalo de tiempo continuo

Ente repetido o un periodo de tiempo en que dos dispositivos son capaces

de interconectarse.

Charla interactiva internet: protocolo mundial para conversaciones

simultáneas que permiten comunicarse por escrito entre sí a través de

ordenador a varias personas.

ASINCRONO

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 26

Electrónica Digital 27

Portafolio de evidencias

Que no tiene un intervalo de tiempo constante entre cada evento características de

comunicación en el que el transmisor puede enviar datos sin previo aviso. El

receptor debe estar preparado para aceptar datos en cualquier momento. El modo

asíncrono de transferencia, es una de las más nuevas tecnologías actuales que

prometen ser el futuro de telecomunicaciones involucrando información de muy

diferentes tipos, como audio, video y también forman la base para el B-ISDNO, o

Broatband – Integrated Services Digital Network.

La B-ISDN está diseñada para ser la red más inteligente, incorporando sistemas de

control que permite al proveedor iniciar una conexión dependiendo del tráfico de

señales, o el tipo de señales que están siendo transmitidas. Las implementaciones

de ATM pueden transmitir datos desde 25 hasta 622 Mbps ATM es una técnica de

transporte de telecomunicaciones y se diferencia en redes de transferencia

sincronizada en que no se transmite la información en paquetes de información

repetitiva y sincronizada con algún contador de tiempo. En una red ATM, las celdas

de información son nada más transmitidas cuando el usuario esta accesando o

manipulando la información al contrario de una red sincronizada que transmitiría

celdas todo el tiempo a veces vacía. Lo conveniente de las redes ATM es que

también pueden contener en sus celdas todo tipo de información. ATM ha surgido

porque la demanda de redes con aplicaciones de imágenes requiere de una

velocidad más rápida que la que es posible en redes actuales.

Lo que se busco fue una red capaz de brindar suficiente, y que fuera swicheado,

para que su costo fuera compartido. También ha existido la necesidad para

estructurar una red que responda más rápido, ya que la fluctuación de tipos de

información puede variar mucho en una red. Que tan grande es el paquete de

información. El número de interacciones entre las CPUs para que consiga una

respuesta el usuario. La demanda de aplicaciones integrados con audio, video-

telefonía y datos forman una red integrada. Todos los tipos de red de comunicación

de antaño han involucrado la orientación a circuitos; es decir, una conexión física y

única se establecía entre usuarios. Cuando surgieron los módems en los 80´s se

había formado, en efecto, la primera red integrada; ya obteniendo la conexión en el

circuito, se podía usar para transmitir datos o voz. Los sistemas asíncronos actúan

inmediatamente al aplicarles la señal al dispositivo. Los sistemas síncronos, la

señal, va siempre sincronizada con una señal de reloj. Hasta que el reloj no genere

un flanco de subida el dispositivo no hará caso a la señal de entrada.

Correo postal

Televisión

Contestador automático

Correo electrónico

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 27

Electrónica Digital 28

Portafolio de evidencias

Mensajes de texto

Servicios sociales de red

Definición, características y constitución de los circuitos secuenciales

CIRCUITOS SECUENCIALES.

Los circuitos secuenciales, de la misma forma que los combinacionales, están

constituidos por puertas lógicas, y como en estos últimos, la escala de integración

de la mayoría de los circuitos disponibles en catalogo es la MSI. Sin embargo,

presentan unas características muy singulares que describiremos a continuación.

A diferencia de los circuitos combinacionales, en los secuenciales, los valores de

las salidas en un momento dado no dependen exclusivamente de los valores

aplicados en las entradas en ese instante, sino también de los que estuviesen

presentes con anterioridad.

Puede ocurrir, por lo tanto, que para iguales valores en las entradas se puedan

obtener estados distintos en las salidas en momentos diferentes.

La respuesta de un circuito de estas características, frente a una secuencia de

valores aplicada a las entradas, depende de su constitución física.

Los circuitos secuenciales tienen capacidad para recordar o memorizar los valores

de las variables de entrada. Esta operación es imprescindible en los sistemas

automáticos construidos con circuitos digitales, sobre todo en los programables, de

los cuales nos ocuparemos más adelante.

El almacenamiento o memorización de la información presente en la puerta del

circuito se realiza gracias a la existencia de unas variables denominadas de estado

interno, cuyo valor se verá afectado por los cambios producidos en la combinación

binaria aplicada a la entrada.

Existen dos grandes tipos de circuitos secuenciales:

a) Máquina de Mealy. En este tipo de circuitos, las salidas dependen, en cada

instante de los valores de los elementos de memoria y de las entradas

presentes en ese instante.

Aquí, para cada estado, podemos tener tantas salidas como combinaciones

tengamos en las entradas.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 28

Electrónica Digital 29

Portafolio de evidencias

b) Máquina de Moore. Aquí las salidas en cada instante dependen

exclusivamente de los estados de los elementos de memoria, y no dependen

directamente de las entradas en ese instante. Los valores de las entradas,

sirven para modificar las diversas transiciones entre estados.

Otra importante división de los circuitos secuenciales es entre síncronos y

asíncronos

Los síncronos, requieren una señal de control procedente de un generador externo

al propio circuito, que funciona como llave, de modo que si no se aplica dicha señal

no se hacen efectivos los valores presentes en las entradas. Este método se emplea

cuando el sistema electrónico es complejo y los tiempos de conmutación de los

diversos dispositivos que lo constituyen son distintos. La señal de control, también

denominada reloj (Clock, o Clock Pulse en inglés), se aplica a las entradas del

mismo nombre de cada bloque integrado para sincronizar la transmisión de datos 0

información a través del sistema. La frecuencia de la señal eléctrica debe adaptarse

a la velocidad de conmutación del dispositivo más lento del circuito.

En cambio, los sistemas secuenciales asicronos no poseen entrada de reloj, y los

cambios en las variables de estado interno y en los valores de salida se producen,

sencillamente, al variar los valores de las entradas del circuito

Aquí nos vamos a centrar especialmente en el estudio de los biestables (los circuitos

secuenciales más elementales, capaces de almacenar, si no existe orden exterior

de cambio, la información en ellos contenida), junto con los contadores y registros

de desplazamiento, que, como observaremos, son también circuitos secuenciales

fonl1ados por una cadena de biestables. Todos estos dispositivos son de aplicación

general, y de importancia fundamental en cualquier sistema digital

1.2.-Biestables

Los biestables basculas o flip-flops, son circuitos secuenciales constituidos por

puertas lógicas capaces de almacenar un bit, que es la información binaria más

elemental.

Al igual que los circuitos secuenciales en general, los biestables también se pueden

clasificar en síncronos y asíncronos, como se muestra en la siguiente figura.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 29

Electrónica Digital 30

Portafolio de evidencias

Fig. 1: registro de desplazamiento de 4 bits

Un registro de desplazamiento es un circuito digital secuencial (es decir, que los

valores de sus salidas dependen de sus entradas y de los valores anteriores)

consistente en una serie de biestables, generalmente de tipo D, conectados en

cascada (Fig. 1), que basculan de forma sincrónica con la misma señal de reloj.

Según las conexiones entre ¡los biestables, se tiene un desplazamiento a la

izquierda o a la derecha de la información almacenada. Es de señalar que un

desplazamiento a la izquierda de un conjunto de bits, multiplica por 2, mientras Que

uno a la derecha, divide entre 2. Existen registros de desplazamiento

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 30

Electrónica Digital 31

Portafolio de evidencias

bidireccionales, que pueden funcionar en ambos sentidos. Los registros universales,

además de bidireccionales permiten la carga en paralelo.

En electrónica digital, Un contador (en inglés, counter) es un circuito secuencial

construido a partir de biestables y puertas lógicas capaz de almacenar y contar los

impulsos (a menudo relacionados con una señal de reloj), que recibe en la entrada

destinada a tal efecto, asimismo también actúa como divisor de frecuencia.

Normalmente, el cómputo se realiza en código binario, que con frecuencia será el

binario natural o el BCD natural (contador de décadas).

Según la forma en que conmutan los biestables, podemos hablar de

contadores síncronos (todos los biestables conmutan a la vez, con una señal

de reloj común) oasíncronos (el reloj no es común y los biestables conmutan

uno tras otro).

Según el sentido de la cuenta, se distinguen en ascendentes, descendentes

y UP-DOWN o bidireccionales (alterna en ascendentes o descendentes

según la señal de control).

Según la cantidad de números que pueden contar, se puede hablar de

contadores binarios de n bits (cuentan todos los números posibles de n bits,

desde 0 hasta 2" -1), contadores BCD (cuentan del 0 al 9).

Memoria

El número máximo de estados por los que pasa un contador se denomina módulo

del contador (Número MOD). Este número viene determinado por la expresión 2"n

donde indica el número de bits del contador. Ejemplo, un contador de módulo 4 pasa

por 4 estados, y contaría del 0 al 3. Si necesitamos un contador con un módulo

distinto de 2"n, lo que haremos es añadir un circuito combinacional.

La mayoría de los procesos lógicos en electrónica digital se encuentran constituidos

por sistemas que manipulan la información binaria para dar como resultado una o

varias salidas. En el proceso de manipular la información, los sistemas requieren

del almacenamiento temporal o permanente de los estados lógicos. Un ejemplo de

este tipo de sistemas son los microcomputadores, los cuales necesitan del

almacenamiento tanto de datos como de los programas que manipulan la

información. En este capítulo veremos los tipos de memorias que existen, sus

aplicaciones y algunos ejemplos de memorias de uso general disponibles en el

mercado. Aspectos Generales sobre Memorias Las unidades de memoria son

módulos conformados por un conjunto de cerrojos o condensadores agrupados de

tal forma que almacenan varias palabras binarias de n bits. Cada una de ellas tienen

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 31

Electrónica Digital 32

Portafolio de evidencias

la capacidad de almacenar un bit de información (1 o 0), y se conocen con el nombre

de celdas de memoria Las celdas 0 bits de memoria se ubican mediante la fila y la

columna en la que se encuentra…. En la figura 10.1.1 se observa como ubicar un

bit y una palabra dentro de una memoria. Figura 10.1.1. Ubicación de la información

en una memoria Las palabras binarias se identifican con una dirección la cual define

la ubicación dentro del arreglo y generalmente se designa con un número binario,

octal o hexadecimal. En la mayoría de las aplicaciones se asocian en grupos de

ocho unidades para formar bytes y el tamaño de las palabras en las memorias

actuales está entre 4 y 64 bits. El parámetro básico de una memoria es su

capacidad, la cual corresponde al total de unidades que puede almacenar. Como

ejemplo, la memoria de la figura 10.1.1 tiene una capacidad de 8n bits, que en otras

palabras representa n bytes. Regularmente estas memorias en la actualidad se

consiguen en tamaños del orden megabytes. El tiempo de acceso es otro parámetro

importante en las memorias. Este corresponde al tiempo que tarda la memoria en

acceder a la información almacenada en una dirección. Generalmente este tiempo

se designan como tacc en las fichas técnicas de estos dispositivos. En tabla 10.1.1

se indican los tiempos de acceso de las memorias en Circuito Integrado comparados

con los tiempos de otros tipos de memoria.

Operaciones básicas de una Memoria La función básica de las memorias es

almacenar información. Sin embargo las memorias tienen la función específica de

escribir y leer los datos en su interior. En la figura 10.1.2 se observa la estructura

básica de una memoria de 1K de 4 bits.

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 32

Electrónica Digital 33

Portafolio de evidencias

Memorias de Acceso Aleatorio Las memorias de Acceso Aleatorio son conocidas

como memorias RAM de la sigla en inglés Random Access Memory. Se caracterizan

por ser memorias de lectura/escritura y contienen un conjunto de Variables de

dirección que permiten seleccionar cualquier dirección de memoria de forma directa

e independiente de la posición en la que se encuentre. Estas memorias son

volátiles, es decir, que se pierde la información cuando no hay energía y se

clasifican en dos categorías básicas: la RAM estática y la RAM dinámica, las cuales

se describen en las siguientes dos secciones. Memoria RAM estática Este tipo de

memoria conocida como SRAM (Static Random Access Memory) se compone de

celdas conformadas por flip-flops construidos generalmente con transistores

MOSFET, aunque también existen algunas memorias pequeñas construidas con

transistores bipolares. En la figura 10.2.1 se observa la estructura típica de una

celda de memoria de una SRAM.

SRAM Sincrónica Al igual que en los sistemas sincrónicos, este tipo de memoria

tiene una entrada de reloj, la cual le permite operar en sincronía con otros

dispositivos. Esta característica no aporta mejores beneficios, sin embargo

simplifica enormemente el diseño de sistemas de alta prestaciones, ya que una

única señal controla todos los dispositivos involucrados. La ventaja de estas

memorias viene proporcionada por lo que se podría llamar su funcionamiento

automático, guiado por la señal de reloj, por lo que no es necesario ocuparse de

generar las señales de control. SRAM de Ráfaga Las memorias de ráfagas (burst)

son sincrónicas y se caracterizan por incluir un contador que permite que la memoria

genere internamente la dirección a la que debe acceder, consiguiendo de esta forma

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 33

Electrónica Digital 34

Portafolio de evidencias

accesos hasta cuatro posiciones de memoria con una sola dirección de referencia.

Esto permite acceder de forma más rápida a la información en memoria Vemos

cómo funciona este tipo de memoria. La CPU genera una dirección de memoria, la

cual se propaga a través del bus de direcciones hasta la memoria, decodificándose

y accediendo a la posición correspondiente. Si se ha configurado la memoria en

modo ráfaga, una vez obtenido el primer dato, incrementa la dirección y vuelve a

acceder. De esta forma se evita el tiempo de propagación de las señales por el bus

y el tiempo de decodificación de Ia dirección. El número de palabras Ieidas o escritas

en una ráfaga, viene limitado por el tamaño del contador interno de la memoria,

SRAM Pipeline 5 Con los dos tipos de memorias anteriores se consigue el acceso

a posiciones consecutivas de forma rápida. Para mantener esta velocidad cuando

se cambia de secuencia, las memorias pipeline incluyen un buffer para almacenar

la dirección y “los datos actuales proporcionados por la memoria. De esta forma, se

puede enviar la nueva dirección antes de terminar la lectura, consiguiendo así que

la CPU no espere la finalización del acceso a una posición de memoria para generar

la nueva dirección. Memoria RAM dinámica Este tipo de memoria conocida como

DRAM (Dinamic Random Access Memory), a diferencia de la memoria estática se

compone de celdas de memoria construidas con condensadores. Las celdas de

memoria son de fabricación más sencillas en comparación a las celdas a base de

transistores, lo cual permite construir memorias de gran capacidad. La figura 10.2.3

se observa la composición interna de una de estas celdas.

DISPOSITIVOS LÓGICOS PROGRAMABLES Un Dispositivo Lógico Programable

(PLD) es cualquier dispositivo "lógico cuya función esta especializada por el usuario,

después de fabricado el dispositivo. Se usan para reemplazar lógica SSI y MSI

ahorrando así en costo y tiempo en el diseño. Entre ellos, encontramos: Arrays

Lógioos Programables Un Array Lógico Programable (PLA), es un circuito PLD que

puede programarse para ejecutar una función compleja. Normalmente se utilizan

para implementar lógica combinacional, pero algunos PLA pueden usarse para

implementar diseños lógicos secuenciales. El PLA es una solución con un solo

circuito integrado a muchos problemas lógicos, que pueden tener muchas entradas

y muchas salidas. Se trata de una solución AND-OR de dos niveles combinacional

que puede programarse para realizar cualquier expansión lógica de suma de

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 34

Electrónica Digital 35

Portafolio de evidencias

productos, sujeta a las limitaciones del producto. Estas limitaciones son el número

de entradas, el número de salidas (m) y el número de términos productos (p). Se

puede describir como un "PLA n x m con p términos productos". Por tanto su utilidad

está limitada a funciones que puedan expresarse en forma de suma de productos

usando p o menos términos productos Un caso especial de PLA es el de uno de los

PLD's más populares, el PAL (Lógica de Array Programable). En este dispositivo

solo es programable la parte correspondiente a la AND, mientras que la OR es lija.

Otros dispositivos lógicos programables de interés son:

ROM, memoria de solo lectura

PROM, memoria de solo lectura programable

EPROM, memoria de solo lectura programable y borrable.

EEPROM, memoria de solo lectura programable y borrable electrónicamente

RAM, memoria de acceso aleatorio

SRAM, memoria de acceso aleatorio estática

DRAM, memoria de acceso aleatorio dinámica

VHDL es un lenguaje definido por el IEEE (Institute of Electrical and Electronics

Engineers) (ANSI/IEEE 1076-1993) usado por ingenieros para describir circuitos

digitales. VHDL es el acrónimo que representa la combinación de VHSIC y HDL

donde VHSIC es el acrónimo de Very High Speed Integrated Circuit y HDL es a su

vez el acrónimo de Hardware Description Language.

Aunque puede ser usado de forma general para describir cualquier circuito se usa

principalmente para programar PLD (Programable Logic Device Dispositivo Lógico

Programable), FPGA (Field Programmable Gate Array). ASIC y similares.

Otros métodos para diseñar circuitos son la captura de esquemas (con herramientas

CAD) y los diagramas de bloques, pero estos no son prácticos en diseños

complejos. Otros lenguajes para el mismo propósito son Verilog y ABEL

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 35

Electrónica Digital 36

Portafolio de evidencias

Instituto Tecnológico de Cd. Juárez.

Materia: Electrónica Digital

Proyecto Unidad 6

Titular de la materia: Ing. Armando Peinado Rentería.

Integrantes del equipo:

Nombres: No. Control Clave Carrera

Arellano Briones Dafne 15111565 4GF Mecatrónica

García Peña Paulina 15110633 4KE Eléctrica

García Santos Jonathan Ramón 15110655 4KE Eléctrica

Loya González Hiram Emmanuel 15110640 4KE Eléctrica

Naquid Ramírez Sergio Antonio 15110656 4KE Eléctrica

Salón: 128 Horario: 11:00-12:00

Fecha de realización: 15-Nov-17 Fecha de entrega: 01-Dic-17

Ing. Armando Peinado Renteria. Titular de la materia. Unidad 4: Página 36

You might also like

- Actividad 1. Circuitos Con DiodosDocument5 pagesActividad 1. Circuitos Con DiodosMaria FernandaNo ratings yet

- Práctica No. 10 Conversor Gray A BinarioDocument18 pagesPráctica No. 10 Conversor Gray A BinarioANAHI SOSA ROMERONo ratings yet

- Introducción a la Mecatrónica - Actividad #6: Características y aplicaciones del circuito integrado 7432Document5 pagesIntroducción a la Mecatrónica - Actividad #6: Características y aplicaciones del circuito integrado 7432Pedro LozanoNo ratings yet

- Computacion 2012 1Document7 pagesComputacion 2012 1PaIacios G GPalaciosNo ratings yet

- Ilovepdf MergedDocument7 pagesIlovepdf MergedEmmanuel Alejandro Piña TapiaNo ratings yet

- Procesamiento Digital de SeñalesDocument5 pagesProcesamiento Digital de SeñalesEduardo Lopez SalasNo ratings yet

- Syllabus PDS 2015 II V1Document3 pagesSyllabus PDS 2015 II V1Parco Camasca VidalNo ratings yet

- Practica #4 Sumador de 4 Bits Unidad 2Document6 pagesPractica #4 Sumador de 4 Bits Unidad 2AbrahamMejíaNo ratings yet

- Circuitos DigitalesDocument3 pagesCircuitos DigitalesJavier SolisNo ratings yet

- Laboratorio Digital2Document2 pagesLaboratorio Digital2Lujum Irt Mojam Urb0% (1)

- DIGITALES SillabusDocument3 pagesDIGITALES SillabusJESUS ANGEL CRUZ CAJANo ratings yet

- Circuitos CombinacionalesDocument196 pagesCircuitos Combinacionalesjavier132No ratings yet

- Práctica 1 - Control de Maquinas EléctricasDocument9 pagesPráctica 1 - Control de Maquinas EléctricasJOSE ISAI CHON GRIJALVANo ratings yet

- Curso de Electrónica RecreativaDocument27 pagesCurso de Electrónica Recreativamiguelon2009_4545No ratings yet

- Silabos Electronica InfDocument101 pagesSilabos Electronica InfJoseNo ratings yet

- Ciclo-05-Ie-Circuitos Digitales-MoscosoDocument2 pagesCiclo-05-Ie-Circuitos Digitales-MoscosoRomel Cárdenas JavierNo ratings yet

- Metodos Computacionales en Ingenieria IIDocument5 pagesMetodos Computacionales en Ingenieria IIJose OrtizNo ratings yet

- 4.5. Analisis y Diseño de Circuitos DigitalesDocument3 pages4.5. Analisis y Diseño de Circuitos DigitalesJuan Jose Nina CharajaNo ratings yet

- Formato Visita TécnicaDocument4 pagesFormato Visita TécnicaLoko Darwin D D FNo ratings yet

- Compuertas and or Semana 7Document7 pagesCompuertas and or Semana 7RickNo ratings yet

- Reporte Practica 8 Edgar Ulises Mendoza Salazar 20300602 5G PDFDocument5 pagesReporte Practica 8 Edgar Ulises Mendoza Salazar 20300602 5G PDFUlises MendozaNo ratings yet

- Reporte de Practica 1 OceaDocument7 pagesReporte de Practica 1 OceaLuis Gerardo Villarruel Ramirez 蛇No ratings yet

- M.A. Sensores y Acondicionamiento de Se AlesDocument36 pagesM.A. Sensores y Acondicionamiento de Se AlesRafael Villegas MetelinNo ratings yet

- Manual de Informatica Forense IDocument596 pagesManual de Informatica Forense IMarc75% (4)

- Sylabus Electricidad y Electrónica Industrial 2018-IIDocument3 pagesSylabus Electricidad y Electrónica Industrial 2018-IIJorge Arias AcevedoNo ratings yet

- Curso de ElectrónicaDocument73 pagesCurso de ElectrónicaMarcelo Nicolas VegaNo ratings yet

- Actividad 4 Sistemas DigitalesDocument2 pagesActividad 4 Sistemas DigitalesJeiner AnayaNo ratings yet

- Actividad 4 Sistemas DigitalesDocument2 pagesActividad 4 Sistemas DigitalesJeiner AnayaNo ratings yet

- Medición V-I salida AND DTLDocument19 pagesMedición V-I salida AND DTLJavier Antonio (Solis Valles)No ratings yet

- Silabo Tecnologia ElectronicaDocument5 pagesSilabo Tecnologia ElectronicaEddy TorresNo ratings yet

- Laboratorio Nº4 ContadoresDocument4 pagesLaboratorio Nº4 ContadoresJOSENo ratings yet

- Sensor InductivoDocument7 pagesSensor InductivoWalter ScaNo ratings yet

- Silabo MT127Document4 pagesSilabo MT127Alejo977xNo ratings yet

- Practicas de Electronica Analogica Parte 2 PDFDocument30 pagesPracticas de Electronica Analogica Parte 2 PDFfusfernandoNo ratings yet

- Fasciculo 03 - El Laboratorio de Electronica (1) - OCRDocument34 pagesFasciculo 03 - El Laboratorio de Electronica (1) - OCRLuis Angel Vazquez GonzalezNo ratings yet

- CarátulasDocument4 pagesCarátulasDaniel Moruco TalaveraNo ratings yet

- Horario de Grupo 4MT1Document1 pageHorario de Grupo 4MT1Oswaldo Sánchez HernándezNo ratings yet

- 3 Correlativas Licenciatura en Redes de Comunicaciones PDFDocument24 pages3 Correlativas Licenciatura en Redes de Comunicaciones PDFhernanraviolNo ratings yet

- Tesis Estrella ElectronicaDocument72 pagesTesis Estrella ElectronicajesuscantuariasNo ratings yet

- Ejemplos de Implementacion de Arduino Con SensoresDocument5 pagesEjemplos de Implementacion de Arduino Con SensoresMax Linder Villegas DiapizNo ratings yet

- 22 Valverde N. - Manual para La Optimizacion de Servicios Sobre DomoticaDocument60 pages22 Valverde N. - Manual para La Optimizacion de Servicios Sobre DomoticaJuanNo ratings yet

- Saldaña MD PDFDocument177 pagesSaldaña MD PDFInesitaAlmachiNo ratings yet

- CurriculumDocument6 pagesCurriculumarsenal997No ratings yet

- Silabo-Instrumentacion y Automatizacion (2020-A)Document5 pagesSilabo-Instrumentacion y Automatizacion (2020-A)Carlos AlvaNo ratings yet

- CircuitosProtoDocument2 pagesCircuitosProtoGustavo Renzo Meza Flores100% (1)

- Digi Silabo Ee635Document3 pagesDigi Silabo Ee635Aomine DaikiNo ratings yet

- Fieldbus LibroDocument120 pagesFieldbus LibroIsaac EliasNo ratings yet

- Tema 4 - Practicas Del 3 Al 6Document32 pagesTema 4 - Practicas Del 3 Al 6David Staser ToralNo ratings yet

- Int P5Document2 pagesInt P5Pedro Rodríguez AlvarezNo ratings yet

- Puente H control motor DCDocument3 pagesPuente H control motor DCEduardo CajasNo ratings yet

- Libros de Automatas ProgramablesDocument3 pagesLibros de Automatas ProgramablesPipe CastilloNo ratings yet

- Club 38 - TSE-E1-Lec3y4 PDFDocument75 pagesClub 38 - TSE-E1-Lec3y4 PDFantonio de jesus reyes luzardoNo ratings yet

- Roxana Flores CV ULASALLEDocument10 pagesRoxana Flores CV ULASALLEShagun Condori SacariNo ratings yet

- Lab07 OptoElectrónicaDocument11 pagesLab07 OptoElectrónicamakens pomaNo ratings yet

- Practica 7Document7 pagesPractica 7Pedro LozanoNo ratings yet

- Electrotecnia I (Cuestionario)Document4 pagesElectrotecnia I (Cuestionario)Alex Gerson Perez RojasNo ratings yet

- Reingeniería De Procesos De Manufactura Industrial: Colaboración Entre Cuerpos Académicos Tlaxcala Y Puebla (Enero 2021)From EverandReingeniería De Procesos De Manufactura Industrial: Colaboración Entre Cuerpos Académicos Tlaxcala Y Puebla (Enero 2021)Rating: 5 out of 5 stars5/5 (2)

- Arduino. Edición 2018 Curso prácticoFrom EverandArduino. Edición 2018 Curso prácticoRating: 4 out of 5 stars4/5 (15)

- Proyeto de IluminacionDocument12 pagesProyeto de IluminacionHiram LoyaNo ratings yet

- CiclosDocument2 pagesCiclosHiram LoyaNo ratings yet

- Dominio, URLDocument1 pageDominio, URLHiram LoyaNo ratings yet

- Practica Nro 3 HDocument6 pagesPractica Nro 3 HHiram LoyaNo ratings yet

- El Potencial de La Radiacion SolarDocument14 pagesEl Potencial de La Radiacion SolarHiram LoyaNo ratings yet

- Tarifas agrícolas México 2020Document5 pagesTarifas agrícolas México 2020Hiram LoyaNo ratings yet

- Parques eólicos en IndiaDocument5 pagesParques eólicos en IndiaHiram LoyaNo ratings yet

- Memoria Técnico DescriptivaDocument2 pagesMemoria Técnico DescriptivaHiram LoyaNo ratings yet

- Tarea 1 PLCDocument4 pagesTarea 1 PLCHiram LoyaNo ratings yet

- Practica PLCDocument14 pagesPractica PLCHiram LoyaNo ratings yet

- Practica PLCDocument14 pagesPractica PLCHiram LoyaNo ratings yet

- Presentacion sIMATIC S71200RDocument72 pagesPresentacion sIMATIC S71200RDiana Patricia Vélez GranadaNo ratings yet

- Evolución automatización industrial 70 añosDocument2 pagesEvolución automatización industrial 70 añoslloga77341No ratings yet

- Circuitos Secuenciales: Los 4 tipos básicos de Flip-FlopsDocument6 pagesCircuitos Secuenciales: Los 4 tipos básicos de Flip-FlopsHiram LoyaNo ratings yet

- Practica PLCDocument14 pagesPractica PLCHiram LoyaNo ratings yet

- Componenetes NeumaticosDocument5 pagesComponenetes NeumaticosHiram LoyaNo ratings yet

- Investigacion U 2Document23 pagesInvestigacion U 2Hiram LoyaNo ratings yet

- Metodo Transformada de LaplaceDocument12 pagesMetodo Transformada de LaplaceHiram LoyaNo ratings yet

- Redes de Aire ComprimidoDocument15 pagesRedes de Aire ComprimidoHiram LoyaNo ratings yet

- Prueba de Aislamiento de Un TransformadorDocument7 pagesPrueba de Aislamiento de Un TransformadorHiram LoyaNo ratings yet

- Trabajo de Investigación-Física ModernaDocument16 pagesTrabajo de Investigación-Física ModernaHiram LoyaNo ratings yet

- Analisis de Circuitos Con FourierDocument48 pagesAnalisis de Circuitos Con Fouriergabriel olivas50% (4)

- SexoDocument6 pagesSexoHiram LoyaNo ratings yet

- Modelos de Negociacion.Document6 pagesModelos de Negociacion.Hiram LoyaNo ratings yet

- SexoDocument4 pagesSexoHiram LoyaNo ratings yet

- Instrumentos Básicos de Medición EquipoDocument24 pagesInstrumentos Básicos de Medición EquipoHiram LoyaNo ratings yet

- practicanro6HCIRCUITOS 2Document9 pagespracticanro6HCIRCUITOS 2Hiram LoyaNo ratings yet

- Condensado de BoseDocument10 pagesCondensado de BoseHiram LoyaNo ratings yet

- Trabajo de Investigación-Física ModernaDocument16 pagesTrabajo de Investigación-Física ModernaHiram LoyaNo ratings yet

- Clase4Document15 pagesClase4holaNo ratings yet

- Hoja-Datos-Pce-Atp-1-Kit 2Document2 pagesHoja-Datos-Pce-Atp-1-Kit 2nicolas espinosaNo ratings yet

- Diapositiva Memoria SecundariaDocument4 pagesDiapositiva Memoria Secundariaedgar sebastian quispe berrocalNo ratings yet

- Modulo Multiusuario y en RedDocument56 pagesModulo Multiusuario y en RedzahidantoNo ratings yet

- Computaci̇on Pri̇mari̇a 456Document10 pagesComputaci̇on Pri̇mari̇a 456Leiny Ugaz BardalesNo ratings yet

- Actividad de La Unidad IV.Document5 pagesActividad de La Unidad IV.Araceli FrancoNo ratings yet

- El Software y HardwareDocument21 pagesEl Software y HardwarecontabilidadsabadoluisaNo ratings yet

- 060 SubrayadoDocument48 pages060 SubrayadoerNo ratings yet

- Introduccion A Los Sistemas MicroprocesadosDocument49 pagesIntroduccion A Los Sistemas MicroprocesadosFreddy Cantero ChicoNo ratings yet

- Tema 1. Fundamentos de HardwareDocument32 pagesTema 1. Fundamentos de HardwareIlyas BakchichNo ratings yet

- Simm CuadeSrnoDocument26 pagesSimm CuadeSrnokarensyluna1999No ratings yet

- Base de Datos DistribuidasDocument20 pagesBase de Datos DistribuidasDiego JoaquinNo ratings yet

- Tema 8 Introducción A Los Sistemas Operativos: ContenidoDocument19 pagesTema 8 Introducción A Los Sistemas Operativos: Contenidodvds_okNo ratings yet

- Dispositivos de AlmacenmientoDocument7 pagesDispositivos de AlmacenmientojmjmmosqueNo ratings yet

- Precio: $799.90: Sistema de Computadora Yoytec Exigente Incluye Teclado, Ratón Óptico y BocinasDocument2 pagesPrecio: $799.90: Sistema de Computadora Yoytec Exigente Incluye Teclado, Ratón Óptico y BocinasabrahamNo ratings yet

- Resumen Examen Final EstructuraDocument5 pagesResumen Examen Final EstructuraJoaqui RodriguezNo ratings yet

- 1.7 ControlDocument5 pages1.7 ControlAGLAE GUTIERREZ VELARDENo ratings yet

- Informe Tecnico InformaticaDocument3 pagesInforme Tecnico Informaticajeferson sotilloNo ratings yet

- Administrador Red Hat Fedora v2-6Document164 pagesAdministrador Red Hat Fedora v2-6oscarinsfranNo ratings yet

- Gestión memoria: jerarquía, caché, virtual, asignaciónDocument9 pagesGestión memoria: jerarquía, caché, virtual, asignaciónTau MinNo ratings yet

- Listado Ledacom 30 09 2020Document14 pagesListado Ledacom 30 09 2020Andres Felipe Gomez EcheverriNo ratings yet

- GrubDocument11 pagesGrubCERON203200732No ratings yet

- Eléctrónica Digital 2Document3 pagesEléctrónica Digital 2Wara TorrezNo ratings yet

- Diseño de Una Memoria CacheDocument4 pagesDiseño de Una Memoria CacheOLIVIA BURGOS BLANCONo ratings yet

- Inmovilizador ElectronicoDocument19 pagesInmovilizador ElectronicoRicardo Javier flores romeroNo ratings yet

- Computación MóvilDocument6 pagesComputación MóvilCitlalli Morales MartinezNo ratings yet

- Diseño Sistemas Información Medida NegocioDocument2 pagesDiseño Sistemas Información Medida NegocioRoly Mañuico FloresNo ratings yet

- 06 La Memoria Ram PDFDocument1 page06 La Memoria Ram PDFEduardo GarcíaNo ratings yet

- Manual de UsuariovigenteDocument48 pagesManual de UsuariovigentemarenaNo ratings yet

- Desensamble y Esamble de Computadoras Portatiles 1Document20 pagesDesensamble y Esamble de Computadoras Portatiles 1Alix ContrerasNo ratings yet