Professional Documents

Culture Documents

PDF Philips 26610

Uploaded by

ecsa tallerCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PDF Philips 26610

Uploaded by

ecsa tallerCopyright:

Available Formats

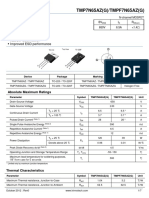

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

FEATURES SYMBOL QUICK REFERENCE DATA

• ’Trench’ technology d VDSS = 25 V

• Very low on-state resistance

• Fast switching ID = 75 A

• Low thermal resistance

• Logic level compatible g RDS(ON) ≤ 9.5 mΩ (VGS = 10 V)

RDS(ON) ≤ 10.5 mΩ (VGS = 5 V)

s

GENERAL DESCRIPTION

N-channel enhancement mode logic level field-effect power transistor in a plastic envelope using ’trench’ technology.

Applications:-

• High frequency computer motherboard d.c. to d.c. converters

• High current switching

The PHP87N03LT is supplied in the SOT78 (TO220AB) conventional leaded package.

The PHB87N03LT is supplied in the SOT404 (D2PAK) surface mounting package.

The PHD87N03LT is supplied in the SOT428 (DPAK)surface mounting package.

PINNING SOT78 (TO220AB) SOT404 (D2PAK) SOT428 (DPAK)

PIN DESCRIPTION tab

tab tab

1 gate

2 drain 1

2 2

3 source

1 23 1 3 1 3

tab drain

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 ˚C to 175˚C - 25 V

VDGR Drain-gate voltage Tj = 25 ˚C to 175˚C; RGS = 20 kΩ - 25 V

VGS Gate-source voltage (DC) - ± 15 V

VGSM Gate-source voltage (pulse Tj ≤ 150 ˚C - ± 20 V

peak value)

ID Drain current (DC) Tmb = 25 ˚C - 75 A

Tmb = 100 ˚C - 61 A

IDM Drain current (pulse peak Tmb = 25 ˚C - 240 A

value)

Ptot Total power dissipation Tmb = 25 ˚C - 142 W

Tj, Tstg Operating junction and - 55 175 ˚C

storage temperature

1 It is not possible to make connection to pin:2 of the SOT404 or SOT428 packages.

October 1999 1 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-mb Thermal resistance junction - - 1.05 K/W

to mounting base

Rth j-a Thermal resistance junction SOT78 package, in free air - 60 - K/W

to ambient SOT404 or SOT428 package, pcb - 50 - K/W

mounted, minimum footprint

AVALANCHE LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

WDSS Drain-source non-repetitive ID = 45 A; VDD ≤ 15 V; - 200 mJ

unclamped inductive turn-off VGS = 5 V; RGS = 50 Ω; Tmb = 25 ˚C

energy

ELECTRICAL CHARACTERISTICS

Tj= 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 25 - - V

voltage Tj = -55˚C 22 - - V

VGS(TO) Gate threshold voltage VDS = VGS; ID = 1 mA 1 1.5 2 V

Tj = 175˚C 0.5 - - V

Tj = -55˚C - - 2.3 V

RDS(ON) Drain-source on-state VGS = 5 V; ID = 25 A - 9 10.5 mΩ

resistance VGS = 10 V; ID = 25 A - 8.5 9.5 mΩ

VGS = 5 V; ID = 25 A; Tj = 175˚C - - 19.5 mΩ

gfs Forward transconductance VDS = 25 V; ID = 25 A 12 51 - S

IGSS Gate source leakage current VGS = ±5 V; VDS = 0 V - 10 100 nA

IDSS Zero gate voltage drain VDS = 25 V; VGS = 0 V; - 0.05 10 µA

current Tj = 175˚C - - 500 µA

Qg(tot) Total gate charge ID = 75 A; VDD = 15 V; VGS = 5 V - 39 - nC

Qgs Gate-source charge - 9 - nC

Qgd Gate-drain (Miller) charge - 18.5 - nC

td on Turn-on delay time VDD = 15 V; ID = 25 A; - 9 15 ns

tr Turn-on rise time VGS = 10 V; RG = 5 Ω - 54 70 ns

td off Turn-off delay time Resistive load - 136 160 ns

tf Turn-off fall time - 85 100 ns

Ld Internal drain inductance Measured tab to centre of die - 3.5 - nH

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

(SOT78 package only)

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 20 V; f = 1 MHz - 2304 - pF

Coss Output capacitance - 620 - pF

Crss Feedback capacitance - 448 - pF

October 1999 2 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current - - 75 A

(body diode)

ISM Pulsed source current (body - - 240 A

diode)

VSD Diode forward voltage IF = 25 A; VGS = 0 V - 0.85 1.2 V

IF = 40 A; VGS = 0 V - 0.9 -

trr Reverse recovery time IF = 20 A; -dIF/dt = 100 A/µs; - 109 - ns

Qrr Reverse recovery charge VGS = 0 V; VR = 25 V - 0.2 - µC

Peak Pulsed Drain Current, IDM (A)

Normalised Power Derating, PD (%) 1000

100

90

RDS(on) = VDS/ ID tp = 10 us

80

70 100

100 us

60

50

1 ms

40

10 D.C. 10 ms

30

100 ms

20

10

0

1

0 25 50 75 100 125 150 175 1 10 100

Mounting Base temperature, Tmb (C) Drain-Source Voltage, VDS (V)

Fig.1. Normalised power dissipation. Fig.3. Safe operating area

PD% = 100⋅PD/PD 25 ˚C = f(Tmb) ID & IDM = f(VDS); IDM single pulse; parameter tp

Transient thermal impedance, Zth j-mb (K/W)

Normalised Current Derating, ID (%) 10

100

90

80

1

70 D = 0.5

60

0.2

50

0.1

40 P D = tp/T

0.1 D tp

30 0.05

20 0.02

10 T

single pulse

0 0.01

0 25 50 75 100 125 150 175 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00

Mounting Base temperature, Tmb (C) Pulse width, tp (s)

Fig.2. Normalised continuous drain current. Fig.4. Transient thermal impedance.

ID% = 100⋅ID/ID 25 ˚C = f(Tmb); VGS ≥ 5 V Zth j-mb = f(t); parameter D = tp/T

October 1999 3 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

Drain Current, ID (A) Transconductance, gfs (S)

50 60

VGS = 10V 3V 2.8 V Tj = 25 C

Tj = 25 C VDS > ID X RDS(ON)

45 55

5V

50

40 2.6 V

4.5 V

45

35 175 C

40

30 35

2.4 V

25 30

20 25

20

15 2.2 V

15

10

2V 10

5 5

0 0

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 0 5 10 15 20 25 30 35 40

Drain-Source Voltage, VDS (V) Drain current, ID (A)

Fig.5. Typical output characteristics, Tj = 25 ˚C. Fig.8. Typical transconductance, Tj = 25 ˚C.

ID = f(VDS) gfs = f(ID)

Normalised On-state Resistance

Drain-Source On Resistance, RDS(on) (Ohms) 2

0.05 1.9

2V 2.2 V 2.4 V 2.6 V Tj = 25 C 1.8

0.045 1.7

1.6

0.04 1.5

1.4

0.035 1.3

1.2

0.03 1.1

1

0.025 0.9

2.8V 0.8

0.02

0.7

3V 0.6

0.015

0.5

0.01 4.5 V 0.4

0.3

0.005 0.2

VGS = 10V 0.1

5V

0 0

0 5 10 15 20 25 30 35 40 45 50 -60 -40 -20 0 20 40 60 80 100 120 140 160 180

Drain Current, ID (A) Junction temperature, Tj (C)

Fig.6. Typical on-state resistance, Tj = 25 ˚C. Fig.9. Normalised drain-source on-state resistance.

RDS(ON) = f(ID) a = RDS(ON)/RDS(ON)25 ˚C = f(Tj)

Threshold Voltage, VGS(TO) (V)

Drain current, ID (A) 2.25

50

VDS > ID X RDS(ON) 2

45

maximum

40 1.75

35 1.5

30 typical

1.25

25

1 minimum

20

0.75

15

10 175 C 0.5

Tj = 25 C

5 0.25

0

0

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 -60 -40 -20 0 20 40 60 80 100 120 140 160 180

Gate-source voltage, VGS (V) Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS) VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

October 1999 4 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

Drain current, ID (A)

1.0E-01

VDS = 5 V Gate-source voltage, VGS (V)

15

14 ID = 75A

1.0E-02

13 Tj = 25 C

12

11 VDD = 15 V

1.0E-03 10

9

8

minimum typical maximum

7

1.0E-04 6

5

4

1.0E-05 3

2

1

0

1.0E-06 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80

0 0.5 1 1.5 2 2.5 3 Gate charge, QG (nC)

Gate-source voltage, VGS (V)

Fig.11. Sub-threshold drain current. Fig.13. Typical turn-on gate-charge characteristics.

ID = f(VGS); conditions: Tj = 25 ˚C; VDS = VGS VGS = f(QG)

IF / A 9510-30

Capacitances, Ciss, Coss, Crss (pF)

100

10000

80

Ciss

60

Tj / C = 175 25

1000

40

Coss

Crss

20

100

0

0.1 1 10 100 0 0.5 1 1.5 2

Drain-Source Voltage, VDS (V) VSDS / V

Fig.12. Typical capacitances, Ciss, Coss, Crss. Fig.14. Typical reverse diode current.

C = f(VDS); conditions: VGS = 0 V; f = 1 MHz IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

October 1999 5 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220 SOT78

E A

P A1

q

D1

L2(1) L1

Q

b1

L

1 2 3

b c

e e

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT A A1 b b1 c D D1 E e L L1 L2 P q Q

max.

4.5 1.39 0.9 1.3 0.7 15.8 6.4 10.3 15.0 3.30 3.8 3.0 2.6

mm 2.54 3.0

4.1 1.27 0.7 1.0 0.4 15.2 5.9 9.7 13.5 2.79 3.6 2.7 2.2

Note

1. Terminals in this zone are not tinned.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT78 TO-220 97-06-11

Fig.15. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to mounting instructions for SOT78 (TO220AB) package.

3. Epoxy meets UL94 V0 at 1/8".

October 1999 6 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

MECHANICAL DATA

Plastic single-ended surface mounted package (Philips version of D2-PAK); 3 leads

(one lead cropped) SOT404

E A1

D1 mounting

base

HD

Lp

1 3

b c

e e Q

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

D

UNIT A A1 b c D1 E e Lp HD Q

max.

mm 4.50 1.40 0.85 0.64 11 1.60 10.30 2.54 2.90 15.40 2.60

4.10 1.27 0.60 0.46 1.20 9.70 2.10 14.80 2.20

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

98-12-14

SOT404

99-06-25

Fig.16. SOT404 surface mounting package. Centre pin connected to mounting base.

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to SMD Footprint Design and Soldering Guidelines, Data Handbook SC18.

3. Epoxy meets UL94 V0 at 1/8".

October 1999 7 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

MOUNTING INSTRUCTIONS

Dimensions in mm 11.5

9.0

17.5

2.0

3.8

5.08

Fig.17. SOT404 : soldering pattern for surface mounting.

October 1999 8 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

MECHANICAL DATA

Plastic single-ended surface mounted package (Philips version of D-PAK); 3 leads

(one lead cropped) SOT428

seating plane

y

A

E A A2

b2 A1 D1

mounting

base

E1

D

HE

L2

2

L1

L

1 3

b1 b w M A c

e

e1

0 10 20 mm

scale

DIMENSIONS (mm are the original dimensions)

A b1 D D1 E E1 HE L1 y

UNIT max. A1(1) A2 b b2 c e e1 L L2 w

max. max. max. max. min. max. min. max.

mm 2.38 0.65 0.89 0.89 1.1 5.36 0.4 6.22 4.81 6.73 10.4 2.95 0.7

4.0 2.285 4.57 0.5 0.2 0.2

2.22 0.45 0.71 0.71 0.9 5.26 0.2 5.98 4.45 6.47 9.6 2.55 0.5

Note

1. Measured from heatsink back to lead.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT428 98-04-07

Fig.18. SOT428 surface mounting package. Centre pin connected to mounting base.

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to SMD Footprint Design and Soldering Guidelines, Data Handbook SC18.

3. Epoxy meets UL94 V0 at 1/8".

October 1999 9 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

MOUNTING INSTRUCTIONS

Dimensions in mm

7.0

7.0

2.15 1.5

2.5

4.57

Fig.19. SOT428 : soldering pattern for surface mounting.

October 1999 10 Rev 1.600

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHP87N03LT, PHB87N03LT

Logic level FET PHD87N03LT

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

October 1999 11 Rev 1.600

You might also like

- Buk7514 55a - Buk7614 55aDocument9 pagesBuk7514 55a - Buk7614 55aHabacuc LopezNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Buk7508 Buk7608-55a 1Document9 pagesBuk7508 Buk7608-55a 1Habacuc LopezNo ratings yet

- Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataDocument8 pagesTrenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataNicki LarsonNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Trenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55ADocument9 pagesTrenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55AMotor CsillagNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- BUK 9575 - Interruptor de PotênciaDocument8 pagesBUK 9575 - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- Datasheet 6Document9 pagesDatasheet 6Ivanor Ipanaque CordovaNo ratings yet

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezNo ratings yet

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- Buk555 60a PDFDocument7 pagesBuk555 60a PDFGiraldoCarpioRamosNo ratings yet

- phn210 Doble MosfetDocument7 pagesphn210 Doble Mosfetmarino246No ratings yet

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 pagesStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55No ratings yet

- 16N50Document6 pages16N50Fábio Vitor MartinsNo ratings yet

- Description: N-Channel Enhancement Mode Field-Effect TransistorDocument13 pagesDescription: N-Channel Enhancement Mode Field-Effect Transistorzigmund zigmundNo ratings yet

- BUK 9609-75A - Interruptor de PotênciaDocument12 pagesBUK 9609-75A - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- STP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetDocument11 pagesSTP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetRyn YahuFNo ratings yet

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- MOSFETDocument7 pagesMOSFETjoswil21No ratings yet

- BUK92150-55A: 1. DescriptionDocument13 pagesBUK92150-55A: 1. DescriptionrenzoNo ratings yet

- Power Transistor: SPP11N60S5, SPB11N60S5 SPI11N60S5 Cool MOS™Document12 pagesPower Transistor: SPP11N60S5, SPB11N60S5 SPI11N60S5 Cool MOS™Abo AdamNo ratings yet

- Stp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetDocument7 pagesStp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetRadoslav RadoslavovNo ratings yet

- RTW50N20D/RTA50N20D 200V N-Channel MOSFET: General Description FeaturesDocument10 pagesRTW50N20D/RTA50N20D 200V N-Channel MOSFET: General Description FeaturesRaghunandan SubramanianNo ratings yet

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaNo ratings yet

- STD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetDocument13 pagesSTD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetJose luisNo ratings yet

- Data SheetDocument8 pagesData SheetSuyash SuyashNo ratings yet

- SPD09P06PL (Cabine FR)Document9 pagesSPD09P06PL (Cabine FR)Edson CostaNo ratings yet

- Product Profile: N-Channel Trenchmos Logic Level FetDocument12 pagesProduct Profile: N-Channel Trenchmos Logic Level FetTom TomNo ratings yet

- SPP11N60C3 SPI11N60C3, SPA11N60C3 Cool MOS™ Power TransistorDocument15 pagesSPP11N60C3 SPI11N60C3, SPA11N60C3 Cool MOS™ Power TransistorWilliam JimenezNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- Data Sheet: N-Channel Enhancement Mode MOS TransistorDocument8 pagesData Sheet: N-Channel Enhancement Mode MOS TransistorArgenis VeraNo ratings yet

- DatasheetDocument12 pagesDatasheetErwin Rolando EscobarNo ratings yet

- Datasheet 2Document4 pagesDatasheet 2Eligio VillalobosNo ratings yet

- PHP/PHB/PHD108NQ03LT: 1. Product ProfileDocument14 pagesPHP/PHB/PHD108NQ03LT: 1. Product Profilemiloud1911No ratings yet

- CRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedDocument10 pagesCRST045N10N, CRSS042N10N: 100% Avalanche Tested 100% Avalanche Tested 100% Avalanche TestedLuis FigueroaNo ratings yet

- 7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Document11 pages7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Sergio Daniel CaminoNo ratings yet

- BLF861ADocument16 pagesBLF861AK.S. BalasubramaniamNo ratings yet

- skst065n08n skss063n08nDocument10 pagesskst065n08n skss063n08nStefan IuscoNo ratings yet

- 17N40K-MT: Unisonic Technologies Co., LTDDocument5 pages17N40K-MT: Unisonic Technologies Co., LTDmanda fanoaNo ratings yet

- Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesNiko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorJulio Rafael GamboaNo ratings yet

- CRST065N08N Datasheet - Moto ElétricaDocument10 pagesCRST065N08N Datasheet - Moto ElétricaDenis OliveiraNo ratings yet

- CN48N78 Power MosfetDocument6 pagesCN48N78 Power MosfetAbbas MaghazehiNo ratings yet

- SPI80N04S2-H4 SPP80N04S2-H4, SPB80N04S2-H4 Power-Transistor: Product Summary FeatureDocument8 pagesSPI80N04S2-H4 SPP80N04S2-H4, SPB80N04S2-H4 Power-Transistor: Product Summary FeatureReymondJosuéArgüelloRojasNo ratings yet

- FDP8443Document7 pagesFDP8443Semut criminalsNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- CEP3205/CEB3205: N-Channel Enhancement Mode Field Effect Transistor FeaturesDocument4 pagesCEP3205/CEB3205: N-Channel Enhancement Mode Field Effect Transistor Featuresilian ivanovNo ratings yet

- Honda Fit PDFDocument1 pageHonda Fit PDFecsa taller100% (1)

- Diagrama Elctrico FH D13 2013 PDFDocument242 pagesDiagrama Elctrico FH D13 2013 PDFEduardo Pai Tocarlo93% (61)

- VTR250 Workshop Manual PDFDocument330 pagesVTR250 Workshop Manual PDFecsa tallerNo ratings yet

- Manual Servico TV Sony KDL 60W600B Chassis RB2G PDFDocument47 pagesManual Servico TV Sony KDL 60W600B Chassis RB2G PDFecsa tallerNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Micsig Oscilloscope Product IntroductionDocument12 pagesMicsig Oscilloscope Product Introductionecsa tallerNo ratings yet

- VFD-Variable Frequency Drive-Motor Speed ControlDocument126 pagesVFD-Variable Frequency Drive-Motor Speed Controlecsa taller0% (1)

- 2004 Toyota RAV4 2004 Toyota RAV4: System Wiring Diagrams System Wiring DiagramsDocument1 page2004 Toyota RAV4 2004 Toyota RAV4: System Wiring Diagrams System Wiring Diagramsecsa taller0% (1)

- ContactorsDocument68 pagesContactorsLaurentiu CatalinNo ratings yet

- Paper 4 - Energy Auditor - Set B Answer Key: General InstructionsDocument9 pagesPaper 4 - Energy Auditor - Set B Answer Key: General InstructionsArun KumarNo ratings yet

- Full - Retrofit and Reconditioning of 40T & 60T EOT CRANEDocument40 pagesFull - Retrofit and Reconditioning of 40T & 60T EOT CRANEKhalid Mustafa100% (1)

- Current Electricity For JEE Main - Advanced (Study Package For Physics) - Er. D. C. Gupta PDFDocument126 pagesCurrent Electricity For JEE Main - Advanced (Study Package For Physics) - Er. D. C. Gupta PDFPaathshala Education IT60% (5)

- JBL E150P Service ManualDocument28 pagesJBL E150P Service ManualMUHAMMAD SISWANTORO100% (4)

- NBCDO MC - 02 - s2015 PDFDocument4 pagesNBCDO MC - 02 - s2015 PDFEli NaguitNo ratings yet

- Chapter 1.0: Introduction: 1.1 Application of ResearchDocument74 pagesChapter 1.0: Introduction: 1.1 Application of ResearchUpul PrasangaNo ratings yet

- Crystal BatteryDocument22 pagesCrystal Batterygrewa153100% (1)

- Duresca: Dtoi RIP Bushings, 36 - 300kVDocument12 pagesDuresca: Dtoi RIP Bushings, 36 - 300kVKhalid AzmyNo ratings yet

- UntitledDocument13 pagesUntitledrejianbuNo ratings yet

- Model 2400 Series: Sourcemeter Quick Results GuideDocument53 pagesModel 2400 Series: Sourcemeter Quick Results GuidenomimanNo ratings yet

- Instruction Manual: A1Dcs-X On/Off Cyclic TimerDocument2 pagesInstruction Manual: A1Dcs-X On/Off Cyclic TimerAmaresh NayakNo ratings yet

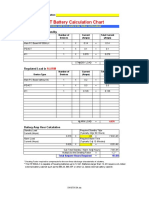

- FL-IPKIT Battery Calculation Chart: Regulated Load in StandbyDocument1 pageFL-IPKIT Battery Calculation Chart: Regulated Load in StandbyFire ChileNo ratings yet

- Gei 85803fDocument4 pagesGei 85803fMuhammad SalmanNo ratings yet

- PV SystemDocument21 pagesPV SystemAhmed SalemNo ratings yet

- Libros BMDocument55 pagesLibros BMMiguelNo ratings yet

- Magnetic FluxDocument21 pagesMagnetic FluxRanjan RanjanNo ratings yet

- GATE 2013 Syllabus For ECEDocument4 pagesGATE 2013 Syllabus For ECESmithNo ratings yet

- Steinmetz Circuit Influence On The Electric System Harmonic ResponseDocument8 pagesSteinmetz Circuit Influence On The Electric System Harmonic ResponseLuis Angel Garcia ReyesNo ratings yet

- 2017 Winter Model Answer Paper PDFDocument29 pages2017 Winter Model Answer Paper PDFshivani valivNo ratings yet

- SG Series UPS 10-500 KVA BrochureDocument12 pagesSG Series UPS 10-500 KVA BrochureGeorgeNo ratings yet

- Bravo Ocean Schematic ModificationsDocument2 pagesBravo Ocean Schematic ModificationsFernando CostaNo ratings yet

- JT-SB116EH-W-CA - Service Manual (U-132 - 0 - 2) PDFDocument46 pagesJT-SB116EH-W-CA - Service Manual (U-132 - 0 - 2) PDFNyeincham Cthu MgNo ratings yet

- Tps 54327Document29 pagesTps 54327Giovanni Carrillo VillegasNo ratings yet

- Ship Automation For Marine Engineers and ETOs A. YakimchukDocument223 pagesShip Automation For Marine Engineers and ETOs A. YakimchukRoma RoMaNo ratings yet

- LMV 932 NationalDocument19 pagesLMV 932 NationalAdam SchwemleinNo ratings yet

- Guidance Note 6 - Protection Against Overcurrent (IEE Guidence Notes) (No 6) (PDDocument2 pagesGuidance Note 6 - Protection Against Overcurrent (IEE Guidence Notes) (No 6) (PDbuddhika MadusankaNo ratings yet

- Manual de Partes C150 Con 6BTDocument82 pagesManual de Partes C150 Con 6BTGedeon100% (2)

- Optimal Coil Size Ratios For Wireless Power Transfer ApplicationsDocument4 pagesOptimal Coil Size Ratios For Wireless Power Transfer ApplicationseduardomaimaiNo ratings yet

- Caracteristicas Cable Utp Con MensajeroDocument2 pagesCaracteristicas Cable Utp Con MensajeroOsvaldo Riquelme FloresNo ratings yet