Professional Documents

Culture Documents

Digital Electronics Full Lab Manual

Uploaded by

Sayak MitraCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics Full Lab Manual

Uploaded by

Sayak MitraCopyright:

Available Formats

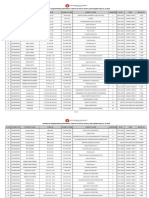

DIGITAL ELECTRONICS LAB (TIUECE-)

List of Experiments

Experiment No. Name of the Experiment Tentative Time to Complete

the Experiment (in

hours/days/weeks)

01. Familiarization with logic 2.5 hrs

gates such as Basic, Universal

and Exclusive gates

02. Realization of NOT, OR, 2.5 hrs

AND, XOR Gates Using

Universal Gates

03. A) Gray to Binary Conversion 2.5 hrs

& Vice-Versa.

B) Code Conversion between

BCD And Excess-3

04. A) Odd and Even Parity 2.5 hrs

Generation And Checking.

B) 4-Bit Comparator Circuit

External Expert HOD Registrar Dean VC

Experiment No. Name of the Experiment Tentative Time to Complete

the Experiment (in

hours/days/weeks)

05. Design of Combinational 2.5 hrs

Circuit To Drive Seven-

Segment Display

06. Design of Combinational 2.5 hrs

Circuits Using Multiplexer

07. A) Half-Adder Circuits & 2.5 hrs

Full-Adder Circuits Using

IC And/ Or Logic Gates.

B) Half-Subtractor Circuits

& Full- Subtractor Using

IC And/ Or Logic Gates

08. Realization Of S-R, J-K, And 2.5 hrs

D Flip Flops Using Universal

Logic Gates

09. Realization of Asynchronous 2.5 hrs

Up OR Down Counter

10. Realization of Synchronous 2.5 hrs

Mod-N Counter

External Expert HOD Registrar Dean VC

EXPERIMENT NO.1

NAME OF THE EXPERIMENT: Familiarization with logic gates such as Basic, Universal and

Exclusive gates

AIM & OBJECTIVE: Familiarization of Basic gates (NOT, AND ,OR), Universal gates (

NAND, NOR), Exclusive gates (XOR) and to verify their Truth Table.

Apparatus/ Components required: IC- 7404, 7408, 7432, 7400, 7402, 7486 and Digital

Lab Kit.

THEORY:

I. THE INVERTER /NOT GATE (IC- 7404):

The Inverter or the NOT gate performs the logic function of invertion/complementation. It changes

one logic level to opposite logic level, in terms of bits, it changes 1 to 0 and 0 to 1.

LOGIC- Y= , when Y is the output and A is the input.

LOGIC SYMBOL:

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins 1, 3, 5, 9, 11 & 13

and Outputs should be obtained from 2, 4, 6, 8, 10 & 12 respectively.

TRUTH TABLE:

Input Output

A Y

0 1

1 0

PROBLEM: Apply a pulse waveform to the inverter and determine the Output corresponding to the

input

External Expert HOD Registrar Dean VC

II. AND GATE (IC-7408):

The AND gate performs logical multiplication, more commonly known as AND operation. It is

composed of two or more inputs and a single output.

LOGIC- Y= A.B, where Y is the output and A and B are the input(for two input AND gate).

LOGIC SYMBOL:

PIN DIAGRAM:

External Expert HOD Registrar Dean VC

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins (1 & 2) or (4 & 5) or

(10 & 9) or (12 & 13) and Outputs should be obtained from 3, 6, 8 & 11 correspondingly.

TRUTH TABLE:

Inputs Output

A B Y

0 0 0

0 1 0

1 0 0

1 1 1

PROBLEM: Make the connection and verify the truth table of Two input AND gate.

III. OR GATE (IC-7432):

The OR gate performs logical addition, more commonly known as OR operation in digital

electronics. It is composed of two or more inputs and a single output.

LOGIC- Y= A + B, where Y is the output and A and B are the input(for two input OR gate).

LOGIC SYMBOL:

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins (1 & 2) or (4 & 5) or

(10 & 9) or (12 & 13) and Outputs should be obtained from 3, 6, 8 & 11 correspondingly.

TRUTH TABLE:

Inputs Output

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

PROBLEM: Make the connection and verify the truth table of Two input OR gate.

External Expert HOD Registrar Dean VC

IV. NAND GATE (IC-7400):

The term NAND is a contraction of NOT-AND and implies an AND function with a

complemented(inverted) output. The NAND gate is a very popular logic function because it is

"Universal" function; that is it can be used to construct an AND gate, OR gate and NOT gate or a

combination of these gates.

LOGIC- Y= A.B, where Y is the output and A and B are the input(for two input NAND gate).

LOGIC SYMBOL:

PIN DIAGRAM:

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins (1 & 2) or (4 & 5) or

(10 & 9) or (12 & 13) and Outputs should be obtained from 3, 6, 8 & 11 correspondingly.

External Expert HOD Registrar Dean VC

TRUTH TABLE:

Inputs Output

A B Y

0 0 1

0 1 1

1 0 1

1 1 0

PROBLEM: Make the connection and verify the truth table of Two input NAND gate.

V. NOR GATE (IC-7402):

The term NOR is a contraction of NOT-OR and implies an OR function with a

complemented(inverted) output. The NOR gate is a very popular logic function because it is

"Universal" function like NAND; that is it can be used to construct an AND gate, OR gate and NOT

gate or a combination of these gates.

LOGIC- Y= A + B, where Y is the output and A and B are the input(for two input NOR gate).

LOGIC SYMBOL:

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins (2 & 3) or (5 & 6) or

(8 & 9) or (12 & 11) and Outputs should be obtained from 1, 4, 10 & 13 correspondingly.

TRUTH TABLE:

Inputs Output

A B Y

0 0 1

0 1 0

1 0 0

1 1 0

PROBLEM: Make the connection and verify the truth table of Two input NOR gate.

External Expert HOD Registrar Dean VC

VI. XOR GATE (IC-7486):

The XOR gates gives a HIGH output when the inputs are at opposite logic levels. This is a widely

used gate because of its special arithmetic property.

LOGIC- = +

= , where Y is the output and A, B is the input of XOR gate.

LOGIC SYMBOL:

PIN DIAGRAM:

CIRCUIT CONNECTION:

Connect Pin 14 to VCC= +5V, pin 7 to Ground. Inputs should be feed to pins (1 & 2) or (4 & 5) or

External Expert HOD Registrar Dean VC

(10 & 9) or (12 & 13) and Outputs should be obtained from 3, 6, 8 & 11 correspondingly.

TRUTH TABLE:

Inputs Output

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

PROBLEM: Make the connection and verify the truth table of Two input XOR gate.

PROCEDURE:

RESULTS & ANALYSIS:

CONCLUSION:

ASSIGNMENT QUESTIONS (OPTIONAL):

External Expert HOD Registrar Dean VC

EXPERIMENT NO.2

NAME OF THE EXPERIMENT: Realization of basic logic gates using Universal gates.

AIM & OBJECTIVE: Realization of the function (NOT, AND ,OR, XOR, XNOR), Using

NAND gate and NOR gate and to verify their Truth Table.

Apparatus/ Components required: IC- 7400, 7402 and Digital Lab Kit.

THEORY:

The NAND and the NOR gates can be used to produce any logic function, that is why they are

referred as "universal gates".

All Boolean expressions consists of various combination of basic function like NOT, AND and OR,

however rather than using separate gates, all operation can be executed using only NAND or NOR

gate.

PIN DIAGRAM:

External Expert HOD Registrar Dean VC

LOGIC ANALYSIS OF XOR & XNOR:

I. XOR GATE:

=

= +

= + + +

= + . ( + )

TRUTH TABLE:

Inputs Output

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

II. XNOR GATE:

=

= +

= . ( )

= ( + ). ( + )

= +

External Expert HOD Registrar Dean VC

TRUTH TABLE:

Inputs Output

A B Y

0 0 1

0 1 0

1 0 0

1 1 1

LOGIC DIAGRAMS :

Use of NAND gate:

I. NOT using NAND

II. AND using NAND

External Expert HOD Registrar Dean VC

III. OR using NAND

IV. XOR using NAND

V. XNOR using NAND

External Expert HOD Registrar Dean VC

Use of NOR gate:

I. NOT using NOR

II. OR using NOR

III. AND using NOR

IV. XOR using NOR

External Expert HOD Registrar Dean VC

V. XNOR using NOR

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 3A

NAME OF THE EXPERIMENT: Gray to Binary conversion & vice-versa

AIM & OBJECTIVE: Design of basic logic circuit for Binary-to-Gray conversion & Gray-to-

Binary conversion.

Apparatus/ Components required: IC- 7486 and Digital Lab Kit.

THEORY:

BINARY-TO-GRAY CONVERSION:

1. The most significant digit(left most) in the Gray code is the same as the corresponding digit in

Binary number.

2. Going from left to right, add each adjacent pairs of Binary digits to get the next Gray code digit.

ignore the carries.

Conversion of Binary number 101102 to Gray:

External Expert HOD Registrar Dean VC

GRAY-TO-BINARY CONVERSION:

1. The most significant digit(left most) in the Binary code is the same as the corresponding digit in

Gray code.

2. Going from left to right, add each of Binary digits generated to the Gray code in the next adjacent

position. ignore the carries.

Conversion of Gray number 11011 to Binary:

LOGIC DIAGRAM:

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 3B

NAME OF THE EXPERIMENT: Code conversion between BCD & EXCESS-3

AIM & OBJECTIVE: Design of basic logic circuit to realize the code conversion BCD and

EXCESS-3.

Apparatus/ Components required: IC- 7483 and Digital Lab Kit.

THEORY:

The EXCESS-3 is a digital code that is delivered by adding +3 to each decimal digit and then

converting the value to four-bit Binary. For instance the EXCESS-3 code for 2 is

2

+3

5 01012

The EXCESS-3 code for decimal 9 is

9

+3

12 11002

TABLE:

External Expert HOD Registrar Dean VC

Notice that ten of possible 16 code combinations are used in EXCESS-3 code. The six nvalid

combinations are 0000, 0001, 0010, 1101, 1110 and 1111.

Self Complementing Property: The key feature of EXCESS-3 code is that it is self complementing.

That is the 1's complement of an EXCESS-3 number is the EXCESS-3 code for the 9's complement

of the corresponding decimal number.

for example: The EXCESS-3 code for decimal 4 is 0111, The 1's complement of this is 1000, which

is the EXCESS-3 code for decimal 5(5 is the 9's complement of 4).

PIN DIAGRAM:

CIRCUIT DIAGRAM:

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 4A

NAME OF THE EXPERIMENT: ODD & EVEN Parity checking and Generation.

AIM & OBJECTIVE: Design of basic logic circuit for ODD & EVEN Parity checking and

Generation .

Apparatus/ Components required: IC- 7486, 7404 and Digital Lab Kit.

THEORY:

Errors can occur as digital codes are being transferred from one point another within a digital

system or while codes are being transmitted from one system to another. The errors take the form of

undesired changes in the bits that make up the coded information; a 1 can change to 0 and vice

versa, due to component malfunction or electrical noise. Many systems however employ a parity bit

in order to detect an error. Binary information is normally handled by a group of bits called words.

A word always contains either a odd or even no, of 1-s. A parity bit is attached to the group of

information bits in order to make the total no, of 1-s always even or always odd. An even parity bit

makes total no, of 1-s even and odd parity bit makes total odd.

A given system operates with even or odd parity, but not both. For instance if a system operates

with even parity, a check is made on each group of bits received to make sure the total no, of 1-s in

the group is even. If there is an odd no, of 1-s an error has occurred.

Detecting an Error:

A parity bit provides for the detection of a single error. But cannot check for two errors. For

instance, let us assume that we wish to transmit the BCD code 0101. The code transmitted,

indicating the even parity bit is,

External Expert HOD Registrar Dean VC

Now let us assume a error occurs in the 3rd bit from the left(the 1 becomes a 0) as follows

When bit code is received the parity check circuitry determines that there is only a single 1(odd

number), when there should be an even no, of 1-s. Because a even no, of 1-s does not appear in the

code when it is received, an error is indicated.

Let us now consider a case for 2 bit errors occur as follows

When a check is made an even no, of 1-s appears, and although there are 2 errors, the parity check

indicates a correct code.

PIN DIAGRAM:

External Expert HOD Registrar Dean VC

LOGIC DIAGRAM:

External Expert HOD Registrar Dean VC

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 4B

NAME OF THE EXPERIMENT: 4-bit Magnitude Comparator

AIM & OBJECTIVE: To verify the truth table of a 4-bit Magnitude Comparator

Apparatus/ Components required: IC- 7485 and Digital Lab Kit.

THEORY:

The purpose of a Digital Comparator is to compare a set of variables or unknown numbers, for

example A (A1, A2, A3, . An, etc) against that of a constant or unknown value such as B (B1,

B2, B3, . Bn, etc) and produce an output condition or flag depending upon the result of the

comparison. For example, a magnitude comparator of two 1-bits, (A and B) inputs would produce

the following three output conditions when compared to each other.

Which means: A is greater than B, A is equal to B, and A is less than B

This is useful if we want to compare two variables and want to produce an output when any of the

above three conditions are achieved. For example, produce an output from a counter when a certain

count number is reached. Consider the simple 1-bit comparator below.

1-bit Digital Comparator Circuit

External Expert HOD Registrar Dean VC

Then the operation of a 1-bit digital comparator is given in the following Truth Table.

Digital Comparator Truth Table:

Inputs Outputs

B A A>B A=B A<B

0 0 0 1 0

0 1 1 0 0

1 0 0 0 1

1 1 0 1 0

4-Bit Comparator

It can be used to compare two four-bit words. The two 4-bit numbers are A = A3 A2 A1 A0 and B3

B2 B1 B0 where A3 and B3 are the most significant bits.

It compares each of these bits in one number with bits in that of other number and produces one of

the following outputs as A = B, A < B and A>B. The output logic statements of this converter are

If A3 = 1 and B3 = 0, then A is greater than B (A>B). Or

If A3 and B3 are equal, and if A2 = 1 and B2 = 0, then A > B. Or

If A3 and B3 are equal & A2 and B2 are equal, and if A1 = 1, and B1 = 0, then A>B. Or

If A3 and B3 are equal, A2 and B2 are equal and A1 and B1 are equal, and if A0 = 1 and B0

= 0, then A > B.

External Expert HOD Registrar Dean VC

4-bit Comparator Truth Table:

PIN DIAGRAM OF IC 7485:

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 6A

NAME OF THE EXPERIMENT: 8x1 Multiplexer circuit

AIM & OBJECTIVE: To verify the truth table of a 8x1 Multiplexer

Apparatus/ Components required: IC- 74151 and Digital Lab Kit.

THEORY:

A Multiplexer is a combinational circuit with more than one input lines, one output line and one or

more selection lines. A Multiplexer selects binary information present on any one of the input lines,

depending upon the logic status of the selection inputs, and sends it to the output line.

If there are n selection lines, then the number of maximum possible input lines is 2n and such

multiplexer is referred to as a 2n-to-1 or 2n x 1 Multiplexer, here we will study 8x1 multiplexer.

8x1 multiplexer : A 8-to-1 multiplexer(MUX) is a combinational circuit with 8 input lines, I0, I1, I2,

I3, I4, I5, I6 and I7 one output line, O and three selection lines, S2, S1 and S0. On receiving active low

enable input, mux is able to perform the intended function.

LOGIC DIAGRAM:

External Expert HOD Registrar Dean VC

Logical expression: O = 0 + 1 + 2 + 3 +

4 + 5 + 6 + 7

TRUTH TABLE:

INPUT OUTPUT

S2 S1 S0 O

1 X X X 0

0 0 0 0 I0

0 0 0 1 I1

0 0 1 0 I2

0 0 1 1 I3

0 1 0 0 I4

0 1 0 1 I5

0 1 1 0 I6

0 1 1 1 I7

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

In the above pin diagram of IC- 74151, D0 to D7 are the input lines , S2, S1, S0 are selection lines , Y

and are the output line and is the enable line.

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 6B

NAME OF THE EXPERIMENT: 1-to-8 line Demultiplexer circuit

AIM & OBJECTIVE: To verify the truth table of a 1-to-8 line Demultiplexer

Apparatus/ Components required: IC- 74138 and Digital Lab Kit.

THEORY:

A Demultiplexer is a combinational circuit with one input line, two or more output lines and one or

more select lines. A DeMUX routes binary info present on the input, to any one of the output lines.

The output line that receives info present in the input line is selected by the bit status of the

selection lines.

A DeMUX has a single input line, 2n output lines and n selection lines. A decoder is a kind of

DeMUX without a input line.

1-to-8 line Demultiplexer: A 1-to-8 DeMUX is a combinational circuit with one input line I and

eight output lines O0, O1, O2, O3, O4, O5, O6, O7 and three select lines , S2, S1 and S0

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

TRUTH TABLE:

INPUTS OUTPUTS

G2A G2B E S2 S1 S0 OO O1 O2 O3 O4 O5 O6 O7

0 0 0 X X X 1 1 1 1 1 1 1 1

0 0 1 0 0 0 0 1 1 1 1 1 1 1

0 0 1 0 0 1 1 0 1 1 1 1 1 1

0 0 1 0 1 0 1 1 0 1 1 1 1 1

0 0 1 0 1 1 1 1 1 0 1 1 1 1

0 0 1 1 0 0 1 1 1 1 0 1 1 1

0 0 1 1 0 1 1 1 1 1 1 0 1 1

0 0 1 1 1 0 1 1 1 1 1 1 0 1

0 0 1 1 1 1 1 1 1 1 1 1 1 0

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

In the above pin diagram of IC- 74138, G2A and G2B are the input lines. A , B and C are the

selection lines S2, S1, S0 respectively. O0, O1, O2, O3, O4, O5, O6, O7 are the output lines and is the

enable line.

External Expert HOD Registrar Dean VC

EXPERIMENT NO. 7A

NAME OF THE EXPERIMENT: Half Adder and Full Adder circuits

AIM & OBJECTIVE: To design a Half Adder and Full Adder circuits using basic gates and to

verify its truth table

Apparatus/ Components required: IC- 7486, 7432, 7408 and Digital Lab Kit.

THEORY:

In digital electronics adder is a circuit that adds binary numbers. Adders can be constructed to carry

out many numerical representation.

Half Adder: A Half Adder is a logical circuit that performs an addition operation on two binary

digits. The Half adder produces a sum and carry value which are both binary digits.

Sum = A B;

Carry= AB.

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

TRUTH TABLE:

Full Adder: A Full Adder is a logical circuit that performs an addition operation on three binary

digits. A Full Adder produces a Sum and Carry Values, which are both binary digits. It can be

combined with other Full adders or work on its own

Sum = (A B) Ci ;

COUT = (AB) + Ci . (A B),

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

TRUTH TABLE:

External Expert HOD Registrar Dean VC

Experiment No. 7B

Name of the experiment: Half Subtractor and Full Subtractor circuits

AIM & Objective: To design a Half Subtractor and Full Subtractor circuits using basic gates

and to verify its truth table

Apparatus/ Components required: IC- 7486, 7432, 7408, 7404 and Digital Lab Kit.

Theory:

To process numerical data, arithmetic operations are necessary. To perform arithmetic operations,

arithmetic circuits are required. To process the binary data, subtract operation needs to study.

Half Subtractor: Single-bit value is subtracted from another single bit value to produce difference

and borrow bits. Any borrow from second bit into first bit is known as borrow taken. Half

Subtractor circuit performs subtraction of single bit value from another single bit value and

produces single bit difference and borrows.

Difference = A B;

Borrow = B.

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

TRUTH TABLE:

Full Subtractor: Single bit value is subtracted from second single bit value considering previous

borrow to produce difference and borrow bits. Any borrow from second bit into first bit is known as

borrow. Full Subtractor circuit performs subtraction of single bit from another single bit value

considering borrow and produces single bit difference and borrow.

Difference = (A B) Bi;

Borrow = B + ( ).Bi.

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

TRUTH TABLE:

External Expert HOD Registrar Dean VC

Experiment No. 8

Name of the experiment: Realization of S-R, J-K, D and T Flip-Flops using universal

gates/IC

AIM & Objective: To design a S-R ,J-K, D & T Flip-Flop circuits using universal gates and to

verify its state table.

Apparatus/ Components required: IC- 7402, 7432, 7408, 7404,7476, 7474 and Digital

Lab Kit.

Theory:

Digital circuits are differentiated between combinational logic and sequential logic circuits. In

Sequential logic circuits the instantaneous outputs depend on the present inputs and also on the past

inputs or outputs. Thus circuit contains elements or memory that can store past info.

Flip-Flop: It is the basic element of sequential circuits, which is a bistable multivibrator and can

serve as a memory element. A Flip-Flop has two states 0 and 1, the output of a Flip-Flop can remain

in one of the two states indefinitely unless an external trigger is applied to change the state.

S-R Flip-Flop: It is known as Set and Reset Flip-Flop The characteristic is defined as

a) If R=0 ,S=0, i.e. in the absence of any trigger input, the output retains its state

obtained in immediately preceding operation i.e. output Y is either 0 or 1. This

state is known as No Change state.

b) If R=0 ,S=1, i.e. if any trigger input is applied , output Y is 1. This condition

is known as SET.

c) If R=1 ,S=0, i.e. if any trigger input is applied , output Y is 0. This condition

is known as RESET.

d) If R=1 ,S=1, i.e. If a trigger is applied, a problem arises since the output Y is

forced simultaneously to 0 and 1 . Thus this state is known as Forbidden State.

External Expert HOD Registrar Dean VC

LOGICAL DIAGRAM:

Nor gate realization of S-R Flip-Flop.

CHARACTERISTIC TABLE:

Qn S R Qn+1 OPERATION

0 0 0 0 NO

1 0 0 1 CHANGE

0 0 1 0 RESET

1 0 1 0

0 1 0 1 SET

1 1 0 1

0 1 1 X FORBIDDEN

1 1 1 X

External Expert HOD Registrar Dean VC

D Flip-Flop: The D stands for Delay type Flip-Flop. It overcomes the disadvantage of S-R Flip-

Flop. D Flip-Flop is not dependent on previous state. When ever a clock pulse is applied the current

input is transmitted over to the output.

LOGICAL DIAGRAM:

Nor gate realization of D Flip-Flop.

PIN DIAGRAM:

Pin configuration of dual D Flip-Flop IC- 7474.

External Expert HOD Registrar Dean VC

CHARACTERISTIC TABLE:

Qn D Qn+1

0 0 0

1 0 0

0 1 1

1 1 1

NOTE: while using the IC 7476 Set and Clear Inputs should be high i.e. 1.

J-K Flip-Flop: The main disadvantage of S-R Flip-Flop is its forbidden state but J-K Flip-Flop

overcomes this operation for both J=K= 1, The Output Toggles its previous states. Rest of the states

are same as S-R FF.

LOGICAL DIAGRAM:

Nor gate realization of J-K Flip-Flop.

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

Pin configuration of dual J-K Flip-Flop IC- 7476.

CHARACTERISTIC TABLE:

Qn J K Qn+1 OPERATION

0 0 0 0 NO

1 0 0 1 CHANGE

0 0 1 0 RESET

1 0 1 0

0 1 0 1 SET

1 1 0 1

0 1 1 1 TOGGLE

1 1 1 0

NOTE: while using the IC 7476 Preset and Clear Inputs should be high i.e. 1.

External Expert HOD Registrar Dean VC

Experiment No. 9

Name of the experiment: Asynchronous UP counter

AIM & Objective: To design an Asynchronous MOD-16 UP counter using J-K Flip-Flop and

to verify its state table.

Apparatus/ Components required: IC- 7476 and Digital Lab Kit.

Theory:

Counter is a clocked sequential circuit that goes through a predetermined sequence of atates upon

the application of input signals. Counters are designed using J-K or T Flip-Flops because these FFs

have Toggle States. A counter follows binary sequence is called n-bit binary counter, Binary

counter has n-FFs and possible number of states are 2n , which are passed through in the order

0,1,2,, 2n -1 and repeats from 0.

Asynchronous counter is also known as ripple counter,

serial or series counter, Here all the inputs are kept at logic state 1 and clock pulse is applied to the

LSB bit FF and each output servers as a clock input for the next FF.

LOGICAL DIAGRAM:

External Expert HOD Registrar Dean VC

PIN DIAGRAM:

Pin configuration of dual J-K Flip-Flop IC- 7476.

Timing Diagram of MOD-16 UP Counter:

External Expert HOD Registrar Dean VC

CHARACTERISTIC TABLE:

CLK J K Q3 Q2 Q1 Q0 Q3+ Q2+ Q1+ Q0 +

0 1 1 0 0 0 0 0 0 0 1

1

0 0 0 1 0 0 1 0

2 0 0 1 0 0 0 1 1

3

0 0 1 1 0 1 0 0

4 0 1 0 0 0 1 0 1

5

0 1 0 1 0 1 1 0

6

0 1 1 0 0 1 1 1

7

0 1 1 1 1 0 0 0

8

1 0 0 0 1 0 0 1

9

1 0 0 1 1 0 1 0

10

1 0 1 0 1 0 1 1

11

1 0 1 1 1 1 0 0

12 1 1 0 0 1 1 0 1

External Expert HOD Registrar Dean VC

13 1 1 0 1 1 1 1 0

14 1 1 1 0 1 1 1 1

15 1 1 1 1 0 0 0 0

External Expert HOD Registrar Dean VC

You might also like

- Lecture 1: Introduction: Bit 2319: Artificial IntelligenceDocument66 pagesLecture 1: Introduction: Bit 2319: Artificial IntelligenceMarl MwegiNo ratings yet

- ElectronicsDocument218 pagesElectronicsmohan100% (1)

- TTL Logic FamilyDocument32 pagesTTL Logic FamilyRamesh KumarNo ratings yet

- 11 PC World May 07Document91 pages11 PC World May 07techno_cop2100% (9)

- TransistorCookbook PDFDocument6 pagesTransistorCookbook PDFMario TodorovNo ratings yet

- Digital Fundamentals QB ODD 2021Document33 pagesDigital Fundamentals QB ODD 2021Hitesh PurswaniNo ratings yet

- Common Collector AmplifiersDocument6 pagesCommon Collector AmplifiersΜαρια ΡοδακοπουλουNo ratings yet

- Eclipse Fujitsu Ten Audio Visual Navigation System Product Brochure For Eclipse Fujitsu Ten Cd5030 Gps ReceiverDocument18 pagesEclipse Fujitsu Ten Audio Visual Navigation System Product Brochure For Eclipse Fujitsu Ten Cd5030 Gps ReceiverEnrique Ignacio PastenetNo ratings yet

- Electronics and Communication EngineeringDocument154 pagesElectronics and Communication EngineeringVinitha SankerNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- Network TheoremsDocument5 pagesNetwork TheoremsSandeep SarmahNo ratings yet

- Analog Vs Digital Circuits - What's The Difference Between Analog and Digital CircuitsDocument13 pagesAnalog Vs Digital Circuits - What's The Difference Between Analog and Digital CircuitsWolffang niño100% (1)

- Iot Cisco NotesDocument45 pagesIot Cisco NotesKenny O'brien100% (1)

- MonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDocument3 pagesMonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDawid MleczkoNo ratings yet

- EC6302 Digital Electronics 2 Marks With AnswersDocument18 pagesEC6302 Digital Electronics 2 Marks With AnswersBasky40% (5)

- Hand Gesture-Controlled Robotic Arm With All-Terrain Surveillance CarDocument7 pagesHand Gesture-Controlled Robotic Arm With All-Terrain Surveillance CarIJRASETPublicationsNo ratings yet

- ECE 327 Slides VHDL Verilog Digital Hardware DesignDocument705 pagesECE 327 Slides VHDL Verilog Digital Hardware DesignysakeunNo ratings yet

- t630 Elect Repair ManualDocument109 pagest630 Elect Repair ManualPopescu Stefan CatalinNo ratings yet

- Accelerometer Based Hand Gesture Controlled Robot Using ArduinoDocument10 pagesAccelerometer Based Hand Gesture Controlled Robot Using ArduinoRaj AryanNo ratings yet

- Eng TELE-satellite 1103Document164 pagesEng TELE-satellite 1103Alexander WieseNo ratings yet

- 32 MicroprocessorsDocument3 pages32 MicroprocessorsTilak Raj100% (1)

- Hand Gesture Controlled RobotDocument65 pagesHand Gesture Controlled RobotFaheem RaoNo ratings yet

- Chapter 2 BJT Biasing Ec b2 90 PDFDocument33 pagesChapter 2 BJT Biasing Ec b2 90 PDFpraveenkumar battulaNo ratings yet

- Electronic ProjectsDocument1 pageElectronic ProjectsSanthosh SanNo ratings yet

- IOT Arduino BoardDocument20 pagesIOT Arduino BoardPrabir dasNo ratings yet

- Cmos Funda Full CourseDocument365 pagesCmos Funda Full CourseKumar BsnspNo ratings yet

- Data Recovery Logical & Physicalshort Course Content Chapter WiseDocument4 pagesData Recovery Logical & Physicalshort Course Content Chapter WiseFalco de ZwartNo ratings yet

- Data Recovery Course Content 1120 NewDocument15 pagesData Recovery Course Content 1120 NewCristian TorrejonNo ratings yet

- NTA UGC NET Electronic Science SyllabusDocument3 pagesNTA UGC NET Electronic Science Syllabusgrk.elrNo ratings yet

- Basic Electronics XI PDFDocument118 pagesBasic Electronics XI PDFnimish ugemuge100% (1)

- CBM Repair ComputerDocument37 pagesCBM Repair Computermbp303No ratings yet

- Product Data: Battery-Powered CCLD Signal Conditioners: Type 1704-A-001, One-Channel, and Type 1704-A-002, Two-ChannelDocument4 pagesProduct Data: Battery-Powered CCLD Signal Conditioners: Type 1704-A-001, One-Channel, and Type 1704-A-002, Two-ChanneltiberiupazaraNo ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- A Complete 8-Bit Microcontroller in VHDLDocument29 pagesA Complete 8-Bit Microcontroller in VHDLSidney O. EbotNo ratings yet

- Advanced View Arduino Projects List - 1Document59 pagesAdvanced View Arduino Projects List - 1Wise TechNo ratings yet

- High-Speed Design TechniquesDocument28 pagesHigh-Speed Design TechniquesHemantkumarNo ratings yet

- Electronic Load and Other Circuit IdeasDocument6 pagesElectronic Load and Other Circuit Ideasanees_172000100% (1)

- Index: Optical Fiber Light Sources Light Detectors Packaging: Aseembly and Transceivers VcselDocument26 pagesIndex: Optical Fiber Light Sources Light Detectors Packaging: Aseembly and Transceivers VcselPooja Bhandari100% (1)

- DC Power Monitor With INA209 and ArduinoDocument57 pagesDC Power Monitor With INA209 and Arduinojp2udhaya100% (2)

- HomeDocument35 pagesHomeAbel kinfeNo ratings yet

- 2021-01-01 PC MagazineDocument150 pages2021-01-01 PC MagazineBora YüretNo ratings yet

- Odometry SensorsDocument20 pagesOdometry Sensorssunxing22No ratings yet

- Practical Mosfet Testing For Audio: by Nelson Pass, (C) 2003 Pass LaboratoriesDocument11 pagesPractical Mosfet Testing For Audio: by Nelson Pass, (C) 2003 Pass Laboratoriesanon-306355100% (1)

- PBG BCI RoboticsDocument5 pagesPBG BCI Roboticsbangalore2009No ratings yet

- Semiconductor Device and Physics ApplicationDocument336 pagesSemiconductor Device and Physics ApplicationNguyenPhucTruong100% (1)

- Poptronics 1973 12Document100 pagesPoptronics 1973 12PropostiExcel100% (1)

- 8051 Microcontroller FAQDocument160 pages8051 Microcontroller FAQkranthi633No ratings yet

- Iot Practical FileDocument42 pagesIot Practical Filenidhikumari03003No ratings yet

- Lab 4 - Lcds and AccelerometersDocument8 pagesLab 4 - Lcds and AccelerometersAlmahdiSalehNo ratings yet

- 8051 InterruptDocument48 pages8051 InterruptIMDAD HUSSAIN MAMUDNo ratings yet

- Seminar ReportDocument42 pagesSeminar Reportsammuel john100% (1)

- Bipolar Transistor Tutorial, The BJT TransistorDocument14 pagesBipolar Transistor Tutorial, The BJT TransistoraleyhaiderNo ratings yet

- ME-447 Lab Final Exam Paper BDocument7 pagesME-447 Lab Final Exam Paper BSaad RasheedNo ratings yet

- TinkerCAD - Intro To Ardunio - Official Module - StudentDocument51 pagesTinkerCAD - Intro To Ardunio - Official Module - StudentShukran Baki Bin IsmailNo ratings yet

- Capacitive TouchDocument104 pagesCapacitive TouchMoses SavariyarNo ratings yet

- Memory AllocationDocument6 pagesMemory AllocationgarivasNo ratings yet

- Working With Digital Filters PDFDocument9 pagesWorking With Digital Filters PDFDocNo ratings yet

- DLD Lab 01 - Getting Started With Tinkercad-EditedDocument23 pagesDLD Lab 01 - Getting Started With Tinkercad-Editedsyed mottaquiNo ratings yet

- 839 - Schedule For Supplementary Examinations, 2020 To Be Held in January, 2020 Updated Upto 21.12.2019 PDFDocument43 pages839 - Schedule For Supplementary Examinations, 2020 To Be Held in January, 2020 Updated Upto 21.12.2019 PDFSayak MitraNo ratings yet

- Friend S Sexy Wife Divya S NavelDocument8 pagesFriend S Sexy Wife Divya S NavelSayak MitraNo ratings yet

- Placed StudentsDocument3 pagesPlaced StudentsSayak MitraNo ratings yet

- EL - MR DuggalDocument5 pagesEL - MR DuggalSayak MitraNo ratings yet

- Protesus - Business Plan SummaryDocument3 pagesProtesus - Business Plan SummarySayak MitraNo ratings yet

- DSA Lab Assignment 4Document1 pageDSA Lab Assignment 4Sayak MitraNo ratings yet

- DSA Written AssignmentDocument2 pagesDSA Written AssignmentSayak Mitra100% (1)

- Application StartupDocument3 pagesApplication StartupSayak MitraNo ratings yet

- Tentative Programme Schedule 151117Document2 pagesTentative Programme Schedule 151117Sayak MitraNo ratings yet

- BCS2B PDFDocument1 pageBCS2B PDFSayak MitraNo ratings yet

- BCS2BDocument1 pageBCS2BSayak MitraNo ratings yet

- Batch 2 Model SeatingDocument45 pagesBatch 2 Model SeatingSayak MitraNo ratings yet

- Density Based Traffic Control System Using Video Processing (Hardware and Software Implementation)Document5 pagesDensity Based Traffic Control System Using Video Processing (Hardware and Software Implementation)Sayak MitraNo ratings yet

- 2nd Year MTA Schedule UpdatedDocument5 pages2nd Year MTA Schedule UpdatedSayak MitraNo ratings yet

- 2016 Department WiseDocument30 pages2016 Department WiseSayak MitraNo ratings yet

- TD1 (Digital Electronic)Document11 pagesTD1 (Digital Electronic)KEO PHEAKDEYNo ratings yet

- District of Carmona Milagrosa West Elementary 2 Periodical Test Mathematics Vi Name: Date: Grade/Section: TeacherDocument3 pagesDistrict of Carmona Milagrosa West Elementary 2 Periodical Test Mathematics Vi Name: Date: Grade/Section: TeacherMicah VideosNo ratings yet

- Ib Grade 9 Math Book Chapter1Document36 pagesIb Grade 9 Math Book Chapter1Fulya Mumtaz100% (1)

- ChekiDocument58 pagesChekiMARK SIMIYUNo ratings yet

- Mathematics10 - q1 - Melc8 - Performs Division of Polynomials Using Long Division and Synthetic Division - v1 1Document19 pagesMathematics10 - q1 - Melc8 - Performs Division of Polynomials Using Long Division and Synthetic Division - v1 1ro geNo ratings yet

- Binary Numbers and Computer ArithmeticDocument24 pagesBinary Numbers and Computer ArithmeticyezidNo ratings yet

- Quantitative Chapter 3 - Percentage, Profit and Loss, PartnershipDocument17 pagesQuantitative Chapter 3 - Percentage, Profit and Loss, PartnershipSWAGATAM BAZNo ratings yet

- Rounding NumbersDocument4 pagesRounding NumbersRia SafitriNo ratings yet

- Soalan Matematik Kertas 1 Tahun 4Document10 pagesSoalan Matematik Kertas 1 Tahun 4sasauballNo ratings yet

- Grade 6 First Periodical Test in MATHDocument6 pagesGrade 6 First Periodical Test in MATHTet Gomez96% (25)

- Real NumbersDocument5 pagesReal NumbersSarthak PithoriyaNo ratings yet

- Practicas de Sistemas de Informacion 2018 ADocument53 pagesPracticas de Sistemas de Informacion 2018 AJudith MachacaNo ratings yet

- TARGET: JEE (Main + Advanced) 2016 No. 4 To 6: Special DPP On "Number System"Document10 pagesTARGET: JEE (Main + Advanced) 2016 No. 4 To 6: Special DPP On "Number System"AAVANINo ratings yet

- Number-Theory-1 Exercises enDocument4 pagesNumber-Theory-1 Exercises enMohamed MNo ratings yet

- Revising Basics - DPP 02 - Lakshya JEE 2024Document2 pagesRevising Basics - DPP 02 - Lakshya JEE 2024Rishi SinghalNo ratings yet

- Am015 Chapter 3Document5 pagesAm015 Chapter 3Shanti GunaNo ratings yet

- Surds WorksheetDocument10 pagesSurds WorksheetKadane CoatesNo ratings yet

- Mathnd Mod World Mod 4Document5 pagesMathnd Mod World Mod 4erickson hernanNo ratings yet

- Periodical Tests 1st GradingDocument24 pagesPeriodical Tests 1st GradingAbegail De LunaNo ratings yet

- New Text DocumentDocument71 pagesNew Text DocumentAnonymous yfhY7LdpizNo ratings yet

- FALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Document2 pagesFALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Sachin KharelNo ratings yet

- t2 M 4009 Multiplying A Onedigit Number With A Decimal Using The Grid Method Template Activity Sheet Activity SheetDocument4 pagest2 M 4009 Multiplying A Onedigit Number With A Decimal Using The Grid Method Template Activity Sheet Activity SheetTimNo ratings yet

- Ieee Floating-Point Decimal NumberDocument12 pagesIeee Floating-Point Decimal NumberSiddharth SinghNo ratings yet

- Num Ans PDFDocument3 pagesNum Ans PDFAlisha NayakNo ratings yet

- Averages and RangeDocument10 pagesAverages and RangeMuaz MalikNo ratings yet

- Đề thi Violympic Toán Tiếng Anh lớp 5Document3 pagesĐề thi Violympic Toán Tiếng Anh lớp 5huong dinhNo ratings yet

- Solving Rational InequalityDocument67 pagesSolving Rational Inequalityjeremee balolongNo ratings yet

- N5Document18 pagesN5Aaditya BaidNo ratings yet

- MOAC Excel 2016 Core (058-100) PDFDocument43 pagesMOAC Excel 2016 Core (058-100) PDFDiana OstopoviciNo ratings yet

- Digital ElectronicsDocument386 pagesDigital ElectronicsShaily Goyal100% (1)