Professional Documents

Culture Documents

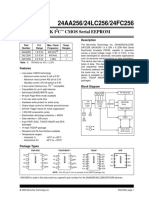

Bus Serial EEPROM

Uploaded by

MatiasCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bus Serial EEPROM

Uploaded by

MatiasCopyright:

Available Formats

25LC320

32K 2.5V SPI Bus Serial EEPROM

FEATURES PACKAGE TYPES

SPI modes 0,0 and 1,1 DIP/SOIC

3.0 MHz Clock Rate

Single supply with Programming Operation down CS 1 8 VCC

to 2.5V

25LC320

SO 2 7 HOLD

Low Power CMOS Technology

- Max Write Current: 5.0 mA WP 3 6 SCK

- Read Current: 1 mA at 5.5V, 3 Mhz

- Standby Current: 1 A typical VSS 4 5 SI

4096 x 8 Organization

32-Byte Page TSSOP

Sequential Read

CS 1 14 VCC

Self-timed ERASE and WRITE Cycles

25LC320

SO 2 13 HOLD

Block Write Protection NC 3 12 NC

NC 4 11 NC

- Protect none, 1/4, 1/2, or all of Array NC 5 10 NC

Built-in Write Protection WP 6 9 SCK

VSS 7 8 SI

- Power On/Off Data Protection Circuitry

- Write Enable Latch

- Write Protect Pin BLOCK DIAGRAM

High Reliability

- Endurance: 1M cycles (guaranteed) Status

HV Generator

- Data Retention: >200 years Register

- ESD protection: >4000V

8-pin PDIP/SOIC, 14-pin TSSOP

Temperature ranges supported

- Commercial (C): 0C to +70C EEPROM

- Industrial (I): -40C to +85C Memory X

I/O Control

Control Array

Logic

DESCRIPTION Logic Dec

The Microchip Technology Inc. 25LC320 is a 32K-bit

Page Latches

serial Electrically Erasable PROM (EEPROM). The

memory is accessed via a simple Serial Peripheral WP

Interface (SPI) compatible serial bus. The bus signals SI

required are a clock input (SCK) plus separate data in SO Y Decoder

(SI) and data out (SO) lines. Access to the device is

CS

controlled through a chip select (CS) input, allowing any

number of devices to share the same bus. SCK

Sense Amp.

HOLD

There are two other inputs that provide the end user R/W Control

with additional flexibility. Communication to the device Vcc

can be paused via the hold pin (HOLD). While the Vss

device is paused, transitions on its inputs will be

ignored, with exception of chip select, allowing the host

to service higher priority interrupts. Also write opera-

tions to the Status Register can be disabled via the

write protect pin (WP).

SPI is a trademark of Motorola.

1996 Microchip Technology Inc. Preliminary DS21158B-page 1

This document was created with FrameMaker 4 0 4

25LC320

1.0 ELECTRICAL FIGURE 1-1: AC TEST CIRCUIT

CHARACTERISTICS Vcc

1.1 Maximum Ratings*

2.25 K

VCC ........................................................................ 7.0V

All inputs and outputs w.r.t. VSS ....... -0.6V to VCC+1.0V SO

Storage temperature ............................ -65C to 150C

Ambient temperature under bias.......... -65C to 125C 1.8 K 100 pF

Soldering temperature of leads

(10 seconds) .................................................... +300C

ESD protection on all pins..................................... 4 kV

*Notice: Stresses above those listed under Maximum ratings 1.2 AC Test Conditions

may cause permanent damage to the device. This is a stress rat-

ing only and functional operation of the device at those or any AC Waveform:

other conditions above those indicated in the operational listings

of this specification is not implied. Exposure to maximum rating

VLO = 0.2V

conditions for extended period of time may affect device reliability VHI = Vcc - 0.2V (Note 1)

VHI = 4.0V (Note 2)

TABLE 1-1: PIN FUNCTION TABLE

Timing Measurement Reference Level

Name Function

Input 0.5 VCC

CS Chip Select Input Output 0.5 VCC

SO Serial Data Output Note 1: For VCC 4.0V

SI Serial Data Input 2: For VCC > 4.0V

SCK Serial Clock Input

WP Write Protect Pin

VSS Ground

VCC Supply Voltage

HOLD Hold Input

NC No Connect

TABLE 1-2: DC CHARACTERISTICS

Applicable over recommended operating ranges shown below unless otherwise noted:

VCC = 2.5V to 5.5V

Commercial (C): Tamb = 0C to +70C

Industrial (I): Tamb = -40C to +85C

Parameter Symbol Min Max Units Test Conditions

High level input voltage VIH1 2.0 VCC+1 V VCC 2.7V

VIH2 0.7 VCC VCC+1 V VCC< 2.7V

Low level input voltage VIL1 -0.3 0.8 V VCC 2.7V

VIL2 -0.3 0.3 VCC V VCC< 2.7V

Low level output voltage VOL 0.4 V IOL=2.1 mA

High level output voltage VOH VCC-0.5 V IOH=-400 A

Input leakage current ILI -10 10 A CS=VIH, VIN=GND to VCC

Output leakage current ILO -10 10 A CS=VIH, VOUT=GND to VCC

Internal Capacitance CINT 7 pF Tamb=25C, FCLK= 1.0 MHz,

(all inputs and outputs) VCC=5.5V (Note)

Operating Current ICC write 5 mA VCC=5.5V; SO=Open

3 mA VCC=2.5V; SO=Open

ICC read 1 mA VCC=5.5V; SO=Open, FCLK=3.0 MHz

500 A VCC=2.5V; SO=Open, FCLK=2.0 MHz

Standby Current ICCS 5 A CS=VCC=5.5V; VIN=Gnd or VCC

2 A CS=VCC=2.5V; VIN=Gnd or VCC

Note: This parameter is periodically sampled and not 100% tested.

DS21158B-page 2 Preliminary 1996 Microchip Technology Inc.

25LC320

FIGURE 1-2: SERIAL INPUT TIMING

tCSD

CS

tCSS tR tCLD

tF tCSH

SCK

tSU tHD

SI msb in lsb in

high impedance

SO

FIGURE 1-3: SERIAL OUTPUT TIMING

CS

tCSH

tHI tLO

SCK

tV tDIS

tHO

SO msb out lsb out

dont care

SI

FIGURE 1-4: HOLD TIMING

CS

tHS tHH tHS tHH

SCK

tHZ tHV

high impedance

SO n+2 n+1 n n n-1

tSU

dont care

SI n+2 n+1 n n n-1

HOLD

1996 Microchip Technology Inc. Preliminary DS21158B-page 3

25LC320

TABLE 1-3: AC CHARACTERISTICS

Applicable over recommended operating ranges shown below unless otherwise noted:

VCC = 2.5V to 5.5V

Commercial (C): Tamb = 0C to +70C

Industrial (I): Tamb = -40C to +85C

Symbol Parameter Min Max Units Test Conditions

fSCK Clock Frequency 3 MHz VCC=4.5V to 5.5V

2 MHz VCC=2.5V to 4.5V

tCSS CS Setup Time 100 ns VCC=4.5V to 5.5V

250 ns VCC=2.5V to 4.5V

tCSH CS Hold Time 100 ns VCC=4.5V to 5.5V

250 ns VCC=2.5V to 4.5V

tCSD CS Disable Time 250 ns VCC=4.5V to 5.5V

500 ns VCC=2.5V to 4.5V

tSU Data Setup Time 30 ns VCC=4.5V to 5.5V

50 ns VCC=2.5V to 4.5V

tHD Data Hold Time 50 ns VCC=4.5V to 5.5V

100 ns VCC=2.5V to 4.5V

tR CLK Rise Time 2 s (Note 1)

tF CLK Fall Time 2 s (Note 1)

tHI Clock High Time 150 ns VCC=4.5V to 5.5V

250 ns VCC=2.5V to 4.5V

tLO Clock Low Time 150 ns VCC=4.5V to 5.5V

250 ns VCC=2.5V to 4.5V

tCLD Clock Delay Time 50 ns

tV Output Valid from 150 ns VCC=4.5V to 5.5V

Clock Low 250 ns VCC=2.5V to 4.5V

tHO Output Hold Time 0 ns

tDIS Output Disable Time 200 ns VCC=4.5V to 5.5V (Note 1)

250 ns VCC=2.5V to 4.5V (Note 1)

tHS HOLD Setup Time 100 ns VCC=4.5V to 5.5V

100 ns VCC=2.5V to 4.5V

tHH HOLD Hold Time 100 ns VCC=4.5V to 5.5V

100 ns VCC=2.5V to 4.5V

tHZ HOLD Low to Output High-Z 100 ns VCC=4.5V to 5.5V (Note 1)

150 ns VCC=2.5V to 4.5V (Note 1)

tHV HOLD High to Output Valid 100 ns VCC=4.5V to 5.5V (Note 1)

150 ns VCC=2.5V to 4.5V (Note 1)

tWC Internal Write Cycle Time 5 ms (Note 2)

Endurance 1M E/W Cycles 25C, Vcc = 5.0V, Block Mode

(Note 3)

Note 1: This parameter is periodically sampled and not 100% tested.

2: tWC begins on the rising edge of CS after a valid write sequence and ends when the internal self-timed write

cycle is complete.

3: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific appli-

cation, please consult the Total Endurance Model which can be obtained on our BBS or website.

DS21158B-page 4 Preliminary 1996 Microchip Technology Inc.

25LC320

2.0 PRINCIPLES OF OPERATION 2.2 Read Status Register (RDSR)

The 25LC320 is a 4096 byte EEPROM designed to The RDSR instruction provides access to the status

interface directly with the serial peripheral interface register. The status register may be read at any time,

(SPI) port of many of todays popular microcontroller even during a write cycle. The status register is format-

families, including Microchips midrange PIC16CXX ted as follows:

microcontrollers. It may also interface with microcontrol-

lers that do not have a built-in SPI port by using dis- 7 6 5 4 3 2 1 0

crete I/O lines programmed properly with software. WPEN X X X BP1 BP0 WEL WIP

The 25LC320 contains an 8-bit instruction register. The The Write-In-Process (WIP) bit indicates whether the

part is accessed via the SI pin, with data being clocked 25LC320 is busy with a write operation. When set to a

in on the rising edge of SCK. If the WPEN bit in the Sta- 1 a write is in progress, when set to a 0 no write is in

tus Register is set, the WP pin must be held high to progress. This bit is read only.

allow writing to the non-volatile bits in the status regis- The Write Enable Latch (WEL) bit indicates the status

ter. of the write enable latch. When set to a 1 the latch

Table 2-1 contains a list of the possible instruction bytes allows writes to the array and status register, when set

and format for device operation. All instructions, to a 0 the latch prohibits writes to the array and status

addresses and data are transferred MSB first, LSB last. register. The state of this bit can always be updated via

the WREN or WRDI commands regardless of the state

Data is sampled on the first rising edge of SCK after CS

of write protection on the status register. This bit is read

goes low. If the clock line is shared with other peripheral

only.

devices on the SPI bus, the user can assert the

HOLD input and place the 25LC320 in HOLD mode. The Block Protection (BP0 and BP1) bits indicate

After releasing the HOLD pin, operation will resume which blocks are currently write protected. These bits

from the point when the HOLD was asserted. are set by the user issuing the WRSR instruction.

These bits are non-volatile.

2.1 Write Enable (WREN) and Write

The Write Protect Enable (WPEN) bit is a non-volatile

Disable (WRDI)

bit that is available as an enable bit for the WP pin. The

The 25LC320 contains a write enable latch. This latch Write Protect (WP) pin and the Write Protect Enable

must be set before any write operation will be (WPEN) bit in the status register control the

completed internally. The WREN instruction will set the programmable hardware write protect feature.

latch, and the WRDI will reset the latch. The following is Hardware write protection is enabled when WP pin is

a list of conditions under which the write enable latch low and the WPEN bit is high. Hardware write

will be reset: protection is disabled when either the WP pin is high or

Power-up the WPEN bit is low. When the chip is hardware write

WRDI instruction successfully executed protected, only writes to non-volatile bits in the status

WRSR instruction successfully executed register are disabled. See Table 2-2 for matrix of

WRITE instruction successfully executed functionality on the WPEN bit and Figure 2-1 for a

flowchart of Table 2-2. See Figure 3-5 for RDSR timing

sequence.

TABLE 2-1: INSTRUCTION SET

Instruction Name Instruction Format Description

WREN 0000 0110 Set the write enable latch (enable write operations)

WRDI 0000 0100 Reset the write enable latch (disable write operations)

RDSR 0000 0101 Read status register

WRSR 0000 0001 Write status register (write protect enable and block write protection bits)

READ 0000 0011 Read data from memory array beginning at selected address

WRITE 0000 0010 Write data to memory array beginning at selected address

TABLE 2-2: WRITE PROTECT FUNCTIONALITY MATRIX

WPEN WP WEL Protected Blocks Unprotected Blocks Status Register

0 X 0 Protected Protected Protected

0 X 1 Protected Writable Writable

1 Low 0 Protected Protected Protected

1 Low 1 Protected Writable Protected

X High 0 Protected Protected Protected

X High 1 Protected Writable Writable

1996 Microchip Technology Inc. Preliminary DS21158B-page 5

25LC320

FIGURE 2-1: WRITE TO STATUS REGISTER AND/OR ARRAY FLOWCHART

CS Returns High

Write No No

to Status Write To other

Reg? to array? Commands

Yes Yes

No No

WEL = 1? WEL = 1?

Yes Yes

No Write to the

WP is low? Unprotected Block

Yes

No Do not write to

WPEN = 1? Array

Yes

Write to

Status Register

Do not write to

Status Register

From other

Commands

Continue

2.3 Write Status Register (WRSR) TABLE 2-3: ARRAY PROTECTION

The WRSR instruction allows the user to select one of Array Addresses

four protection options for the array by writing to the BP1 BP0

Write Protected

appropriate bits in the status register. The array is

0 0 none

divided up into four segments. The user has the ability

to write protect none, one, two, or all four of the seg- 0 1 upper 1/4

ments of the array. The partitioning is controlled as illus- 0C00h - 0FFFh

trated in Table 2-3. 1 0 upper 1/2

0800h - 0FFFh

See Figure 3-6 for WRSR timing sequence.

1 1 all

0000h - 0FFFh

DS21158B-page 6 Preliminary 1996 Microchip Technology Inc.

25LC320

3.0 DEVICE OPERATION For the data to be actually written to the array, the CS

must be brought high after the least significant bit (D0)

3.1 Clock and Data Timing of the nth data byte has been clocked in. If CS is brought

high at any other time, the write operation will not be

Data input on the SI pin is latched on the rising edge of completed. Refer to Figure 3-3 and Figure 3-4 for more

SCK. Data is output on the SO pin after the falling edge detailed illustrations on the byte write sequence and the

of SCK. page write sequence respectively.

3.2 Read Sequence While the write is in progress, the status register may

be read to check the status of the WPEN, WIP, WEL,

The part is selected by pulling CS low. The 8-bit read BP1, and BP0 bits. A read attempt of a memory array

instruction is transmitted to the 25LC320 followed by location will not be possible during a write cycle. When

the 16-bit address, with the four MSBs of the address a write cycle is completed, the write enable latch is

being dont care bits. After the correct read instruction reset.

and address are sent, the data stored in the memory at

the selected address is shifted out on the SO pin. The 3.4 Data Protection

data stored in the memory at the next address can be

The following protection has been implemented to

read sequentially by continuing to provide clock pulses.

prevent inadvertent writes to the array:

The internal address pointer is automatically incre-

mented to the next higher address after each byte of The write enable latch is reset on power-up.

data is shifted out. When the highest address is A write enable instruction must be issued to set

reached (0FFFh) the address counter rolls over to the write enable latch.

address 0000h allowing the read cycle to be continued After a successful byte write, page write, or status

indefinitely. The read operation is terminated by setting register write, the write enable latch is reset.

CS high (Figure 3-1). CS must be set high after the proper number of

clock cycles to start an internal write cycle.

3.3 Write Sequence Access to the array during an internal write cycle

is ignored and programming is continued.

Prior to any attempt to write data to the 25LC320, the

write enable latch must be set by issuing the WREN 3.5 Power On State

instruction (Figure 3-2). This is done by setting CS low

and then clocking the proper instruction into the The 25LC320 powers on in the following state:

25LC320. After all eight bits of the instruction are trans- The device is in low power standby mode.

mitted, the CS must be brought high to set the write The write enable latch is reset.

enable latch. If the write operation is initiated SO is in high impedance state.

immediately after the WREN instruction without CS A low level on CS is required to enter active state.

being brought high, the data will not be written to the

array because the write enable latch will not have been

properly set.

Once the write enable latch is set, the user may pro-

ceed by setting the CS low, issuing a write instruction,

followed by the 16-bit address, with the four MSBs of

the address being dont care bits, and then the data to

be written. Up to 32 bytes of data can be sent to the

25LC320 before a write cycle is necessary. The only

restriction is that all of the bytes must reside in the

same page. A page address begins with XXXX XXXX

XXX0 0000 and ends with XXXX XXXX XXX1 1111. If

the internal address counter reaches XXXX XXXX

XXX1 1111 and the clock continues, the counter will roll

back to the first address of the page and overwrite any

data in the page that may have been written.

1996 Microchip Technology Inc. Preliminary DS21158B-page 7

25LC320

FIGURE 3-1: READ SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 21 22 23 24 25 26 27 28 29 30 31

SCK

instruction 16 bit address

SI 0 0 0 0 0 0 1 1 15 14 13 12 2 1 0

data out

high impedance

SO 7 6 5 4 3 2 1 0

FIGURE 3-2: WRITE ENABLE SEQUENCE

CS

0 1 2 3 4 5 6 7

SCK

SI 0 0 0 0 0 1 1 0

high impedance

SO

FIGURE 3-3: WRITE SEQUENCE

CS

Twc

0 1 2 3 4 5 6 7 8 9 10 11 21 22 23 24 25 26 27 28 29 30 31

SCK

instruction 16 bit address data byte

SI 0 0 0 0 0 0 1 0 15 14 13 12 2 1 0 7 6 5 4 3 2 1 0

high impedance

SO

DS21158B-page 8 Preliminary 1996 Microchip Technology Inc.

25LC320

FIGURE 3-4: PAGE WRITE SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 21 22 23 24 25 26 27 28 29 30 31

SCK

instruction 16-bit address data byte 1

SI 0 0 0 0 0 0 1 0 15 14 13 12 2 1 0 7 6 5 4 3 2 1 0

CS

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47

SCK

data byte 2 data byte 3 data byte n (32 max)

SI 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

FIGURE 3-5: READ STATUS REGISTER SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SCK

instruction

SI 0 0 0 0 0 1 0 1

data from status register

high impedance

SO 7 6 5 4 3 2 1 0

FIGURE 3-6: WRITE STATUS REGISTER SEQUENCE

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SCK

instruction data to status register

SI 0 0 0 0 0 0 0 1 7 6 5 4 3 2 1 0

high impedance

SO

1996 Microchip Technology Inc. Preliminary DS21158B-page 9

25LC320

4.0 PIN DESCRIPTIONS The WP pin function is blocked when the WPEN bit in

the status register is low. This allows the user to install

4.1 Chip Select (CS) the 25LC320 in a system with WP pin grounded and still

be able to write to the status register. The WP pin

A low level on this pin selects the device. A high level functions will be enabled when the WPEN bit is

deselects the device and forces it into standby mode. set high.

However, a programming cycle which is already in

progress will be completed, regardless of the CS input 4.6 Hold (HOLD)

signal. If CS is brought high during a program cycle, the

device will go into standby mode as soon as the pro- The HOLD pin is used to suspend transmission to the

gramming cycle is complete. As soon as the device is 25LC320 while in the middle of a serial sequence with-

deselected, SO goes to the high impedance state, out having to re-transmit entire sequence over at a later

allowing multiple parts to share the same SPI bus. A time. It should be held high any time this function is not

low to high transition on CS after a valid write sequence being used. Once the device is selected and a serial

is what initiates an internal write cycle. After power-up, sequence is underway, the HOLD pin may be pulled low

a low level on CS is required prior to any sequence to pause further serial communication without resetting

being initiated. the serial sequence. The HOLD pin must be brought

low while SCK is low, otherwise the HOLD function will

4.2 Serial Input (SI) not be evoked until the next SCK high to low transition.

The 25LC320 must remain selected during this

The SI pin is used to transfer data into the device. It sequence. The SI, SCK, and SO pins are in a high

receives instructions, addresses, and data to be written impedance state during the time the part is paused and

to the memory. Input is latched on the rising edge of the transitions on these pins will be ignored. To resume

serial clock. serial communication, HOLD must be brought high

It is possible for the SI pin and the SO pin to be tied while the SCK pin is low, otherwise serial communica-

together. With SI and SO tied together, two way tion will not resume.

communication of data can occur using only one

microcontroller I/O line.

4.3 Serial Output (SO)

The SO pin is used to transfer data out of the 25LC320.

During a read cycle, data is shifted out on this pin after

the falling edge of the serial clock.

It is possible for the SI pin and the SO pin to be tied

together. With SI and SO tied together, two-way

communication of data can occur using only one

microcontroller I/O line.

4.4 Serial Clock (SCK)

The SCK is used to synchronize the communication

between a master and the 25LC320. Instructions,

addresses, or data present on the SI pin are latched on

the rising edge of the clock input, while data on the SO

pin is updated after the falling edge of the clock input.

4.5 Write Protect (WP)

This pin is used in conjunction with the WPEN bit in the

status register to prohibit writes to the non-volatile bits

in the status register. When WP is low and WPEN is

high, writing to the non-volatile bits in the status register

is disabled. All other operations function normally.

When WP is high, all functions, including writes to the

non-volatile bits in the status register operate normally.

WP going low during a status register write sequence

will disable writing to the status register. If an internal

write cycle has already begun, WP going low will have

no effect on the write.

DS21158B-page 10 Preliminary 1996 Microchip Technology Inc.

25LC320

25LC320 Product Identification System

To order or to obtain information (e.g., on pricing or delivery), please use the listed part numbers, and refer to the factory or the listed

sales offices.

25LC320 - /P

Package: P = PDIP (300 mil Body), 8-lead

SN = SOIC (150 mil Body), 8-lead

ST = TSSOP (4.4 mm Body), 14-lead

Temperature Blank = 0C to +70C

Range: I = -40C to +85C

Device: 25LC320 32K SPI Bus Serial EEPROM

25LC320T 32K SPI Bus Serial EEPROM (Tape and Reel)

Sales and Support

Products supported by a preliminary Data Sheet may possibly have an errata sheet describing minor operational differences and

recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office (see next page)

2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

3. The Microchips Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

For latest version information and upgrade kits for Microchip Development Tools, please call 1-800-755-2345 or 1-602-786-7302.

1996 Microchip Technology Inc. Preliminary DS21158B-page 11

WORLDWIDE SALES & SERVICE

AMERICAS ASIA/PACIFIC EUROPE

Corporate Office Hong Kong United Kingdom

Microchip Technology Inc. Microchip Technology Arizona Microchip Technology Ltd.

2355 West Chandler Blvd. RM 3801B, Tower Two Unit 6, The Courtyard

Chandler, AZ 85224-6199 Metroplaza Meadow Bank, Furlong Road

Tel: 602 786-7200 Fax: 602 786-7277 223 Hing Fong Road Bourne End, Buckinghamshire SL8 5AJ

Technical Support: 602 786-7627 Kwai Fong, N.T. Hong Kong Tel: 44 1628 850303 Fax: 44 1628 850178

Web: http://www.microchip.com Tel: 852 2 401 1200 Fax: 852 2 401 3431 France

Atlanta India Arizona Microchip Technology SARL

Microchip Technology Inc. Microchip Technology Zone Industrielle de la Bonde

500 Sugar Mill Road, Suite 200B No. 6, Legacy, Convent Road 2 Rue du Buisson aux Fraises

Atlanta, GA 30350 Bangalore 560 025 India 91300 Massy - France

Tel: 770 640-0034 Fax: 770 640-0307 Tel: 91 80 526 3148 Fax: 91 80 559 9840 Tel: 33 1 69 53 63 20 Fax: 33 1 69 30 90 79

Boston Korea Germany

Microchip Technology Inc. Microchip Technology Arizona Microchip Technology GmbH

5 Mount Royal Avenue 168-1, Youngbo Bldg. 3 Floor Gustav-Heinemann-Ring 125

Marlborough, MA 01752 Samsung-Dong, Kangnam-Ku, D-81739 Muenchen, Germany

Tel: 508 480-9990 Fax: 508 480-8575 Seoul, Korea Tel: 49 89 627 144 0 Fax: 49 89 627 144 44

Chicago Tel: 82 2 554 7200 Fax: 82 2 558 5934 Italy

Microchip Technology Inc. Shanghai Arizona Microchip Technology SRL

333 Pierce Road, Suite 180 Microchip Technology Centro Direzionale Colleone Pas Taurus 1

Itasca, IL 60143 Unit 406 of Shanghai Golden Bridge Bldg. Viale Colleoni 1

Tel: 708 285-0071 Fax: 708 285-0075 2077 Yanan Road West, Hongiao District 20041 Agrate Brianza

Dallas Shanghai, Peoples Republic of China Milan Italy

Microchip Technology Inc. Tel: 86 21 6275 5700 Tel: 39 39 6899939 Fax: 39 39 689 9883

14651 Dallas Parkway, Suite 816 Fax: 011 86 21 6275 5060

JAPAN

Dallas, TX 75240-8809 Singapore

Microchip Technology Intl. Inc.

Tel: 972 991-7177 Fax: 972 991-8588 Microchip Technology

Benex S-1 6F

Dayton 200 Middle Road

3-18-20, Shin Yokohama

Microchip Technology Inc. #10-03 Prime Centre

Kohoku-Ku, Yokohama

Suite 150 Singapore 188980

Kanagawa 222 Japan

Two Prestige Place Tel: 65 334 8870 Fax: 65 334 8850

Tel: 81 45 471 6166 Fax: 81 45 471 6122

Miamisburg, OH 45342 Taiwan, R.O.C

Tel: 513 291-1654 Fax: 513 291-9175 Microchip Technology 11/7/96

Los Angeles 10F-1C 207

Microchip Technology Inc. Tung Hua North Road

18201 Von Karman, Suite 1090 Taipei, Taiwan, ROC

Irvine, CA 92612 Tel: 886 2 717 7175 Fax: 886 2 545 0139

Tel: 714 263-1888 Fax: 714 263-1338

New York

Microchip Technology Inc.

150 Motor Parkway, Suite 416

Hauppauge, NY 11788

Tel: 516 273-5305 Fax: 516 273-5335

San Jose

Microchip Technology Inc.

2107 North First Street, Suite 590

San Jose, CA 95131

Tel: 408 436-7950 Fax: 408 436-7955

Toronto

Microchip Technology Inc.

5925 Airport Road, Suite 200

Mississauga, Ontario L4V 1W1, Canada

Tel: 905 405-6279 Fax: 905 405-6253

All rights reserved. 1996, Microchip Technology Incorporated, USA. 11/96

Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No repre-

sentation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement

of patents or other intellectual property rights arising from such use or otherwise. Use of Microchips products as critical components in life support systems is not autho-

rized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and

name are registered trademarks of Microchip Technology Inc. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.

DS21158B-page 12 Preliminary 1996 Microchip Technology Inc.

You might also like

- FCS 5e - CHP 1 SlidesDocument30 pagesFCS 5e - CHP 1 SlidesDanielNo ratings yet

- The TabletDocument34 pagesThe TablettechnologizerNo ratings yet

- 24C320-EP MicrochipTechnologyDocument12 pages24C320-EP MicrochipTechnologyMateus CorrêaNo ratings yet

- 8K/16K 5.0V SPI Bus Serial EEPROM: Features Package TypesDocument12 pages8K/16K 5.0V SPI Bus Serial EEPROM: Features Package Typesrıdvan71No ratings yet

- Datasheet 25c040Document22 pagesDatasheet 25c040Perona PabloNo ratings yet

- 25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMDocument24 pages25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMHebertAlexMamaniSalomaNo ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- 25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMDocument11 pages25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMAndrey OliveiraNo ratings yet

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pages25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийNo ratings yet

- 25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMDocument22 pages25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMAgustin AndrokaitesNo ratings yet

- 25AA256/25LC256: 256K SPI Bus Serial EEPROMDocument32 pages25AA256/25LC256: 256K SPI Bus Serial EEPROMmelquisedecNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pages24AA02/24LC02B: 2KI C Serial EEPROMhanifNo ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFNicoli LourençoNo ratings yet

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pages25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoNo ratings yet

- 24AA52/24LCS52: 2K 2.2V I C Serial EEPROM With Software Write-ProtectDocument24 pages24AA52/24LCS52: 2K 2.2V I C Serial EEPROM With Software Write-Protecta4rfanNo ratings yet

- 24aa08 - 24lc08 Eeprom PDFDocument40 pages24aa08 - 24lc08 Eeprom PDFEdgar DauzonNo ratings yet

- MX25L8005 MxicDocument41 pagesMX25L8005 Mxicdanehcan graNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pages24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezNo ratings yet

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pages24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezNo ratings yet

- 25 LC 1024Document28 pages25 LC 1024hyd27No ratings yet

- 11aa02iud 1wire MicrochipDocument32 pages11aa02iud 1wire MicrochipManutenção eletrônicaNo ratings yet

- 25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMDocument28 pages25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMrudy pumacahuaNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMDocument45 pages24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMJuan Carlos CrespoNo ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaNo ratings yet

- At 25080Document21 pagesAt 25080sabNo ratings yet

- 93C66Document12 pages93C66Alex AlvarezNo ratings yet

- At25f512a 844895Document19 pagesAt25f512a 844895mirage0706No ratings yet

- TC58NS256DCDocument33 pagesTC58NS256DCFreddy AmayaNo ratings yet

- 22131c PDFDocument24 pages22131c PDFAdilsonAmorimNo ratings yet

- CAT 28256 - EepromDocument20 pagesCAT 28256 - EepromTiago LeonhardtNo ratings yet

- 24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638Document51 pages24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638ManunoghiNo ratings yet

- 24LC21 1K 2.5V Dual Mode I2C Serial EEPROMDocument12 pages24LC21 1K 2.5V Dual Mode I2C Serial EEPROMVictor TruccoNo ratings yet

- 24l1026i Memoria EEPROM 1024kDocument28 pages24l1026i Memoria EEPROM 1024kMarta_d_eNo ratings yet

- 24LC04B PDFDocument22 pages24LC04B PDFEddy RosarioNo ratings yet

- MCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDocument38 pagesMCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDaniel CortelettiNo ratings yet

- SST25VF016B: 16 Mbit SPI Serial FlashDocument30 pagesSST25VF016B: 16 Mbit SPI Serial Flashzigmund zigmundNo ratings yet

- Macronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryDocument46 pagesMacronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Eliteflash MemoryRoger Chavez PachasNo ratings yet

- 25L3205-MacronixInternationalDocument45 pages25L3205-MacronixInternationalRavi ChavhanNo ratings yet

- 24C32Document12 pages24C32SilviuCocoloșNo ratings yet

- 25 C 256Document10 pages25 C 256Драгиша Небитни ТрифуновићNo ratings yet

- 2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDocument12 pages2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDanielNo ratings yet

- 4 PDFDocument31 pages4 PDFAgus OrtizNo ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromDocument26 pages24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromcraponzelNo ratings yet

- 32K 5.0V I C Smart Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Smart Serial EEPROM: Features Package TypesRamon LopezNo ratings yet

- 25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMDocument26 pages25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMmuglanNo ratings yet

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Document39 pages25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiNo ratings yet

- 24aa515, 24LC515, 24FC515Document20 pages24aa515, 24LC515, 24FC515dorudNo ratings yet

- EEPROM 24LC256 - Microchip PDFDocument28 pagesEEPROM 24LC256 - Microchip PDFValdir DerlannNo ratings yet

- 24 LC 256Document38 pages24 LC 256johnNo ratings yet

- Ic PDFDocument36 pagesIc PDFdharamNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- Cat25128 DDocument18 pagesCat25128 Dalvinmpayikulu08No ratings yet

- CAT25256 EEPROM Serial 256-Kb SPI: DescriptionDocument22 pagesCAT25256 EEPROM Serial 256-Kb SPI: DescriptionPolinho DonacimentoNo ratings yet

- 32K 2.5V I C Serial EEPROM: Features Package TypesDocument12 pages32K 2.5V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pages8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahNo ratings yet

- SST25VF040B: 4 Mbit SPI Serial FlashDocument33 pagesSST25VF040B: 4 Mbit SPI Serial FlashDario EzequielNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument24 pages24AA02/24LC02B: 2KI C Serial EEPROMMayk OzNo ratings yet

- 24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738Document32 pages24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738İbrahim DemircioğluNo ratings yet

- 16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangesDocument22 pages16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangeshcarcaroNo ratings yet

- 24LC08 PDFDocument30 pages24LC08 PDFJaime BarrancoNo ratings yet

- MISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFDocument67 pagesMISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFMatiasNo ratings yet

- Current Loop (4-20 Ma) OUTPUT: SourceDocument1 pageCurrent Loop (4-20 Ma) OUTPUT: SourceMatiasNo ratings yet

- MISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFDocument67 pagesMISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFMatiasNo ratings yet

- MISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFDocument67 pagesMISC-04642 - Rev001 - 2018 - BSH US CATALOG-FINAL09July2018 - IA PDFMatiasNo ratings yet

- Manual V7Document174 pagesManual V7Alan UriasNo ratings yet

- Manual V7Document174 pagesManual V7Alan UriasNo ratings yet

- Media Guides Neptune MiniDocument18 pagesMedia Guides Neptune MiniMatiasNo ratings yet

- Mic 3Document18 pagesMic 3Gopinathan MNo ratings yet

- Lecture 4Document23 pagesLecture 4Tanmaya Tapaswini TripathyNo ratings yet

- Qsimavr: Graphical Simulation of An AVR Processor and PeripheryDocument71 pagesQsimavr: Graphical Simulation of An AVR Processor and PeripherySantiago Urueña PascualNo ratings yet

- Calisma SorulariDocument3 pagesCalisma SorulariSezer ErdoğanNo ratings yet

- Embedded Design TradeoffsDocument88 pagesEmbedded Design Tradeoffsabbazh rakhondeNo ratings yet

- Application Note AN118: Flash Programming of CC253x/4x DevicesDocument20 pagesApplication Note AN118: Flash Programming of CC253x/4x DevicesYuri PotapovichNo ratings yet

- 9608 w16 QP 11Document16 pages9608 w16 QP 11ratnaNo ratings yet

- R308 Optical Fingerprint Module User ManualDocument10 pagesR308 Optical Fingerprint Module User ManualCarlos Mas CarlosNo ratings yet

- Coa MCQDocument12 pagesCoa MCQAdithya R AnandNo ratings yet

- CACS101 CFA Unit 1Document14 pagesCACS101 CFA Unit 1Anjali KapoorNo ratings yet

- 22EC2106 - P&C LAB ManualDocument57 pages22EC2106 - P&C LAB ManualBaladitya VardhanNo ratings yet

- QtSPIM and MARS MIPS SimulatorsDocument27 pagesQtSPIM and MARS MIPS SimulatorsDon_TurboNo ratings yet

- B.tech CSE 2019 Scheme Syllabi v0.9Document29 pagesB.tech CSE 2019 Scheme Syllabi v0.9abhinav vermaNo ratings yet

- Hardware Software Co-Design ModelsDocument37 pagesHardware Software Co-Design ModelsbalakrishnaNo ratings yet

- PSM Veena Project 19-20 - 1Document69 pagesPSM Veena Project 19-20 - 1Atul KumarNo ratings yet

- Smart Card Reader For Student IDDocument43 pagesSmart Card Reader For Student IDSheshu technocrat100% (3)

- Chapter 3Document50 pagesChapter 3Abo Shaker HaboudalNo ratings yet

- MPMC Unit 3Document168 pagesMPMC Unit 3Vijaya KumarNo ratings yet

- CSC 102 Exam - 1-1Document75 pagesCSC 102 Exam - 1-1kayode oluwarotimiNo ratings yet

- HESCO Junior Engineer MCQs CollectionDocument6 pagesHESCO Junior Engineer MCQs CollectionmohsinNo ratings yet

- Parallel Computing PDFDocument138 pagesParallel Computing PDFUmesh Sah100% (1)

- Case Study - 8085 MicroprocessorDocument14 pagesCase Study - 8085 MicroprocessorChat MateNo ratings yet

- MKC ES Units 3&4 ARM 1Document105 pagesMKC ES Units 3&4 ARM 1Varun ChilukuriNo ratings yet

- Chapter 1 - Introduction To Computer Organization and ArchitectureDocument34 pagesChapter 1 - Introduction To Computer Organization and ArchitectureKhang NguyenNo ratings yet

- Chapter 02 BCODocument16 pagesChapter 02 BCOJeterine AriasNo ratings yet

- MPMCDocument6 pagesMPMCKodagala lalithaNo ratings yet

- ARM Instruction SetDocument3 pagesARM Instruction SetnhungdieubatchotNo ratings yet

- DEBUG - Assembly Debugger for Testing Executable ProgramsDocument15 pagesDEBUG - Assembly Debugger for Testing Executable ProgramsRed StreakNo ratings yet