Professional Documents

Culture Documents

Pingel Et Al PID

Uploaded by

Jay Rameshbhai ParikhCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pingel Et Al PID

Uploaded by

Jay Rameshbhai ParikhCopyright:

Available Formats

POTENTIAL INDUCED DEGRADATION OF SOLAR CELLS AND PANELS

S. Pingel, O. Frank, M. Winkler, S. Daryan, T. Geipel, H. Hoehne and J. Berghold

SOLON SE, Am Studio 16, 12489 Berlin, Germany

ABSTRACT

To better understand the cause of PID three different

Since solar energy generation is getting more and more levels system, panel and cell are separately

important worldwide PV systems and solar parks are investigated.

becoming larger consisting of an increasing number of

solar panels being serially interconnected. As a System level

consequence panels are frequently exposed to high

relative potentials towards ground causing High Voltage On system level the potential difference between ground

Stress (HVS). The effect of HVS on long term stability of and cell is the most important factor for PID. The system

solar panels depending on the leakage current between voltage depends in first order on the number of panels

solar cells and ground has been first addressed by NREL serially interconnected and the irradiation and in second

in 2005 [1]. This potential degradation mechanism is not order on the panel temperature. Depending on the

monitored by the typical PV tests listed in IEC 61215 [2]. configuration of the grounding the potential of a cell

Depending on the technology different types of Potential towards ground is negative or positive. Three different

Induced Degradation (PID) occur. This paper is focusing possibilities exist two of these are to ground one of the

on PID of wafer based standard p-type silicon technology system poles (PV-/PV+ grounding) then all cells/panels

aiming on increasing life times for solar panels once are positive or negative towards ground or if no pole is

exposed to external potentials in the field. A test setup is grounded the resulting potential is not fixed for which

presented for simulation of the PID in the lab and the reason it is called floating potential. In the latter case one

influence of cell properties on PID is demonstrated in part of the string has a negative and the other a positive

order to reveal the cell being the precondition for the PID. potential towards ground.

However, PID can also be stopped or minimized on panel

and system level as shown in the paper.

BACKGROUND

The most prominent case for PID in silicon solar cell

technology is Sunpowers polarization effect [4] but also

other technologies like a-Si and ribbon silicon have been

reported in the past to be prone to different types of PID

under certain circumstances either reversible e.g.

polarization or irreversible e.g. electro chemical corrosion

[3]. All known PID effects have one common characteristic

the degradation is depending on the polarity and

level/extent of the potential between cell and ground.

Different standards exist concerning the configuration of a

PV system. E.g. in Europe system voltages up to 1000V Figure 1 String potential, three grounding schemes

and for the US only up to 600V are allowed. Some PV+/PV- and no grounding (floating potential).

countries dictate or recommend PV system grounding

configurations others do not. Accordingly, inverters Panel level

technologies without transformer are commonly used in

Europe whereas in the US it is not common to use Environmental factors such as humidity and temperature

transformer less inverters since PV systems are usually influence leakage currents between ground and cell [1].

grounded.

It is the combination of several parameters such as high

potential towards ground and a PID prone solar cell

embedded in a standard panel configuration which can

cause significant power degradation in the field within a

panels life time. So the reduction of the PID of standard

H-pattern cells first identified in 2009 is a clear track

for life time extension of a solar panel and for the

reduction of the overall degradation of a panel after a Figure 2 PID setup (left) and leakage currents (right).

certain amount of time.

If water penetrates the solar panel the leakage current In case the potential is not floating but fixed in the way that

rises due increasing conductivity of the encapsulation the PV- pole of the string is grounded PID can be

(ENC) material. effectively prevented.

The interaction of ENC material, back sheet foil, glass,

and frame is resulting in certain leakage current paths as However, in the last years inverter development was

illustrated in figure 2. Additionally material properties resulting in higher efficient technologies partly due to the

production processes and panel layout do play a role for abandonment of transformers. As a consequence

the HV-durability of panels. grounding is not possible and PID has to be prevented

with another approach.

Cell level

Panel level

On cell level some process steps as well as the quality of

the base material have been identified to significantly Taking a closer look at the PID effect on the panel level as

contribute to the extent of PID tendency on cell level. In done in case of prone solar cells in a standard panel see

the result chapter we take a closer look at the different the following EL images before and after the PID test with

parameters that influence the PID. 1000V for 100hr. First in general the brightness of the

picture is decreasing (not visible here) and second single

cells are not uniformly affected. Some cells degrade

EXPERIMENTAL heavily and seem to be short circuited while others appear

to be stable. The reasons for this variation must be

For characterization of the cells and panels prior and after investigated on cell level as will be done in the next

the PID test a flash tester and a high resolution chapter.

electroluminescence (EL) camera is used.

A PID setup was built to test coupons (single cell

laminates) or standard panels consisting of sixty cells. The

glass on the sunny side is flooded with water or covered

with a wet blanket.

This conductive front cover is connected to the positive

pole and the panel contacts are connected to the negative

pole of a power supply in order to generate a typical bias

voltage of 1000V (maximum system voltage in Europe) for

standard p-type solar cells. Choosing the setup described

above a negative cell voltage versus ground as

occurring in the field - is simulated. A standard test is

taking 100 hours and afterwards the samples are retested

and the results are compared to the initial measurements.

To investigate the leakage currents from cell to ground an

ampere meter with data logger was used. In order to

evaluate the impact of environmental factors such as

temperature and humidity on the test panels were

placed in an environmental chamber under defined

conditions.

EXPERIMENTAL RESULTS

System level Figure 4 EL image of a panel before (upper) and after

(lower) 100hr 1000V PID test power loss was 32%.

The following example (fig.3) shows an EL image of a

floating system that is affected by PID. The arrow The influence of the material composition in the panel was

indicates the rising system voltage. When going from tested systematically with solar cells that are prone to PID.

negative potential (left) to positive potential (right) versus A crosscheck with non sensitive cells showed no PID for

ground. Degradation stops when the potential turns from all material combinations. In the material comparison it

negative to positive. turned out that an important factor to reduce PID in case

of prone solar cells is the type of ENC material. In the

following figure is shown the leakage current at 1000V as

PV- PV+ a function of time during a temperature ramp up from -

20C to 48C in a humid atmosphere (50% RH). It can be

Figure 3 EL image of a floating PID string with seen that two different ENC materials are causing the

degraded panels on the side with negative potential. peak leakage currents to differ by more than one order of

magnitude. The panel can be described here as a

capacitor being charged while the temperature is rising.

Finally the full capacity is reached and the current drops.

Figure 7 PID IV curve evolution (left) and

corresponding power degradation (right).

In case of PID shunt resistance as well as the reverse bias

current is affected first followed by FF. Finally Voc

decreases reflecting the junction to be less capable of

separating holes and electrons.

Figure 5 Leakage current for two panels with different

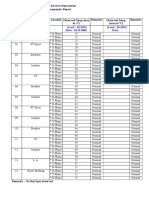

Time Uoc Isc P FF I(-12V) Rsh

ENC material during a temperature ramp from -20C t o

[hr] [V] [A] [W] % [A] ]

[

48C with 1000V applied voltage (RH 50%). 0 0,615 8,240 3,616 71,4 0,21 80,4

40 0,615 8,258 3,622 71,3 0,30 51,1

As a consequence of this significant difference in leakage 80 0,600 8,109 2,658 54,6 >10 0,5

current the PID results with varying ENC materials differs 100 0,572 7,882 1,746 38,7 >10 0,2

strongly as shown below for three materials in combination rel. PID -7% -4% -52% -46% - -100%

with prone solar cells. Table 1 Cell IV key parameter change during PID.

100,0

The Isc is the parameter that is least affected but with

advancing PID Isc also degrades. Depending on the

80,0 degree of PID the junction is loosing its blocking

characteristic under reverse bias or totally breaks down

(ohmic shunt). This phenomenon can be visualized by EL

relative PID in %

60,0

images taken during a PID test that are shown in the

upper row. After 40hr local shunts appear along the edge

40,0 of the cell that degrade further from diode to ohmic

behavior, as can be seen in the reverse bias image in the

20,0

lower row. First shunted areas appear bright but after

further PID evolution these areas do not emit any more

breakdown light [6]. Finally after 100hr both images are

0,0

Material A Material B Material C

dark because of dominating ohmic shunts.

Figure 6 PID comparison of three different ENC

materials in panels with prone solar cells.

In order to minimize or avoid PID on panel level and

therefore to increase life time and reliability the

appropriate material combination have to be found making

sure that solar cells prone to PID are combined with ENC

materials resulting in low leakage currents on panel level.

There are alternative materials to standard EVA better

performing in respect to PID but other criteria like price,

handling, long term stability issues and availability have to

be taken into account.

Figure 8 EL image of a cell during PID test (upper row)

So although it was shown that it is possible to suppress

and reverse bias (-12V) image (lower row).

PID in case of prone cells by switching the ENC material it

seems to be even more favorable to minimize or avoid PID

on cell level which is discussed in the following chapter. The leakage current in form of electrons or ions is

resulting in an increased charge concentration above the

Cell level solar cell in the ENC. These charges interact with the

emitter and depletion layer and disrupt their function. From

The following two graphs show the evolution of the IV semiconductor industry similar effects are known as (time

curve with ongoing PID and the corresponding power dependent) dielectric breakdown or surface inversion [5].

degradation over time. The electric field of these charge carriers is influencing the

p-n-junction in that way that junction gets more conductive In a typical process the emitter diffusion is the following

and the local shunt resistance drops. Sunpower applied a step and an influence was expected and also found during

transistor model to the polarization effect [4] on their n- the test.

type back contact cell. In the case of standard p-type cells

this model also works but the configuration needs to be

switched from npn- to pnp-transistor.

There are numerous factors on cell level being important

in respect to PID. In the following we present the

parameters indentified to have a significant impact.

Wafer material

In joint experiments with different cells suppliers SOLON

tested the influence of wafer material properties. The most

promising parameter that can be varied here is the base

resistivity.

Figure 10 Emitter sheet resistance dependence of PID.

Increasing the emitter sheet resistance leads to a higher

sensitivity for degradation of the solar cells.

This trend shows that the cell process optimizations like

increasing the emitter sheet resistances as was done in

the last years can lead to a higher tendency for PID.

Future trends like selective emitter technology must be

watched and tested closely. Inhomogeneous emitter

diffusion can also play an important role.

Figure 9 Base resistivity dependence of PID.

In two experiments base doping was varied by almost two

orders of magnitude. The result is that increasing the base

resistivity leads to more resistant solar cells concerning

PID since lower base doping leads to a wider depletion

region at the junction when the emitter doping is held

constant. Figure 11 Lateral variation of sheet resistance on a

mono crystalline wafer (four point probe).

Within different experiments with cell suppliers where cells

have been produced at constant cell processing In the image above the sheet resistance of a mono

parameters utilizing different wafer suppliers a significant crystalline wafer (measured with a four point probe after

batch dependence has been found. This could hint on POCL diffusion) is shown. The phases of the wafer show a

systematic variation of certain wafer properties relevant for higher sheet resistance and in general emitter doping is

PID. not totally constant over the whole area. Having in mind

Lower quality silicon or comparably high concentrations of our findings for the emitter sheet resistance local

crystal defects seem to increase PID but here results have variations can lead to higher PID sensitivity.

to be further verified.

Emitter back etching and edge isolation

Emitter diffusion

Some cell manufactures use emitter back etching methods

The cell process typically starts with a cleaning followed for edge isolation or for removal of the so called dead

by a texturization step depending on wafer type and layer of the emitter.

process acidic or alkaline textures are applied. Here the Depending on process parameters the sheet resistance

results do not show a clear trend. But for example if can be increased significantly and therefore PID can be

texturization is incomplete or residues are left on the increased corresponding to figure 10.

surface the following process steps can be affected and

hence also PID.

Besides the RI the layer thickness is important since these

two parameters must be well adjusted to reduce reflectivity

of the cell. The second result is that a reduction of layer

thickness is resulting in lower PID sensitivity (figure 13

thick and thin ARC method B). Going to thinner ARC

layers with higher Si/N ratio can be a feasible way of

reducing PID.

The third parameter having an impact here is the

Figure 12 Section of an EL (upper) and reverse bias homogeneity of the resulting SiN layer which is found to

image (lower) of a cell with chemical etch isolation be clearly different for various SiN deposition methods

during PID test (initial and after 20hr). see figure 13 process A&B. However, it can be stated that

a homogenous process lowers the risk for PID with

In figure 12 EL images and reverse bias images at -12V of standard thickness and RI.

a solar cell with wet chemical edge isolation before and

General remark on cell process

after a PID test step of 20hr are shown. In the EL image

the edge is turning dark while at reverse bias the edge

signal is getting more intense explainable by an Controlling PID at the end of the cell line by special sorting

insufficient edge isolation. criteria is not possible to our knowledge but adaption of

In this case described above edge isolation the emitter cell processes as well as process control and sensitive

was removed not only on the edge but on the surface as wafer material choice allows avoiding PID on cell level.

well resulting in an emitter with locally high sheet

resistance. This example shows that variations in the cell

RECOVERY METHODS

process which are thought to be of no relevance for later

application can lead to degradation when the cell is

Reverse potential

exposed to a potential in the field. Here the PID test

reveals potential weaknesses of a solar cell.

Provided that electrochemical corrosion is excluded

Anti-reflective coating laboratory test with at reverse polarity show that PID is

reversible also for standard solar cell similar to what was

found by Sunpower for their back contact technology [4].

The process step within cell production found most

important concerning PID is the anti reflective coating

(ARC) deposition. As shown by Sunpower this layer has a

significant influence on the PID effect for back contact

cells [4]. In case of typical standard cells this layer

consists of Si and N, the ratio of these elements, layer

thickness and the deposition technique define the

character of this layer.

In semiconductor industry a comparable phenomenon is

known as dielectric breakdown of passivation layers but

not all properties can be transferred to solar cells [5].

In the graph below the dependence of PID on the Si-N

ratio corresponding to the refractive index (RI) and

thereby to the optical characteristics is shown. PID rates

were determined on panel and coupon level.

First result: Si-rich layers tend to show lower degradation Figure 14 Panel PID and recovery by reverse potential.

than N-rich layers.

As a consequence grounding of the positive pole of the PV

system and thereby avoiding of harmful potentials leads to

regeneration of affected solar panels. This recovery

process takes time and the rate depends on the potential

and environmental factors such as humidity and

temperature.

Temperature

In the lab a similar behavior was found for the recovery of

PID panels by temperature, storing PID panels at around

100C for 10 hours lead to a recovery close to 100% but

Figure 13 AR-coating: RI, thickness and deposition the initial power was not reached after this time step.

method dependence of PID.

OUTLOOK

The scenarios investigated with the laboratory test are

simulating worst case conditions with high humidity and

constantly high voltage. At SOLON an experiment is going

on directly comparing laboratory results with outdoor data

at different SOLON test sites (Berlin, Tucson,

Carmignano) covering also the impact of different

environmental conditions [7].

ACKNOWLEDGEMENT

We would like to thank the cell suppliers for their fruitful

discussions and their contribution to this work.

Figure 15 PID recovery by temperature (~100C). REFERENCES

This test shows that temperature is not only leading to a [1] J.A. del Cueto, D. Trudell, and W. Sekulic, Capabilities

faster PID evolution (compare figure 5) because of of the High Voltage Stress Test System at the Outdoor

increased leakage currents but it also plays an important Test Facility, DOE Solar Energy Technologies Program

role in for regeneration processes in a panel. But this Review Meeting, NREL/CP-520-38955, 2005

recovery procedure at high temperature is not suitable as

standard treatment since high temperature is stressing the [2] IEC 61215, Crystalline Silicon Terrestrial Photovoltaic

panel materials and hence affects the long term stability. Modules Design Qualification and Type Approval

As shown the stability of the defect depends on the edition 2 (2005)

temperature. E.g. in [5] a similar semiconductor defect

(surface inversion) can be recovered by a high [3] R.G. Ross Jr., G.R. Mon, L.C. Wen and R.S. Sugimura,

temperature step. Measurement and characterization of voltage- and

Besides treatment on a hot plate or oven also other current-induced degradation of thin-film photovoltaic

sources of heat can at least partly recover the solar cell, modules, Solar Cells, Volume 27, Issues 1-4, 1989,

e.g. UV treatment, climatic chamber test or applying a Pages 289-298

reverse or forward bias voltage to the panels poles.

[4] Swanson et al., The surface polarization effect in high-

CONCLUSION efficiency silicon solar cells, 2005

This paper presented a degradation mechanism called [5] R. Blish, N. Durrant, Semiconductor device reliability

Potential Induced Degradation (PID) that is getting more failure models, International SEMATECH, 2000

important with growing PV system sizes going along with

higher system voltages. It was shown that although the [6] Kasemann et al., Spatially resolved silicon solar cell

origin of PID is on cell level it can be minimized or characterization using infrared imaging methods, 2008

avoided on all levels system, panel and cell. The

solution on system level is choosing an appropriate [7] M. Wittner, T. Weber, W. Richardson, B. Striner,

grounding scheme of the string poles while on panel level N. Baggio, Global test site network paves the way to

the properties of the encapsulation material determine the optimal site-related photovoltaic solution, this conference

height of leakage currents that can in case of prone solar

cells lead to PID.

On cell level many parameters influence the PID stability

of solar cells. Besides base material resistivity and emitter

sheet resistance the most important parameter was found

to be the anti-reflective coating since adaption of this layer

can avoid the effect of PID.

The PID effect can be reversed by switching the polarity

and also high temperatures support regeneration.

Taking these findings into account long term stability of

solar panels can be significantly improved by adapting

processes on all levels in order to minimize PID and

therefore optimize the energy output of the PV system

over a 25+ year life time.

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- 11 02 7UM62 enDocument39 pages11 02 7UM62 enJay Rameshbhai ParikhNo ratings yet

- DC Trace PDFDocument48 pagesDC Trace PDFJay Rameshbhai ParikhNo ratings yet

- HighPROTEC TechnicalDocument7 pagesHighPROTEC TechnicalJay Rameshbhai ParikhNo ratings yet

- Motor Protection RelayDocument21 pagesMotor Protection RelayJay Rameshbhai ParikhNo ratings yet

- DATE:25/02/07 Grid Islanding ReportDocument1 pageDATE:25/02/07 Grid Islanding ReportJay Rameshbhai ParikhNo ratings yet

- Light, Sound&forceDocument3 pagesLight, Sound&forceJay Rameshbhai ParikhNo ratings yet

- Insulation Testers: Users ManualDocument38 pagesInsulation Testers: Users ManualJay Rameshbhai ParikhNo ratings yet

- Thermography Tieline 10122005Document1 pageThermography Tieline 10122005Jay Rameshbhai ParikhNo ratings yet

- PV System Design For Power Plant - 28 09 11Document27 pagesPV System Design For Power Plant - 28 09 11Jay Rameshbhai ParikhNo ratings yet

- SND Z Q DQ PDFDocument42 pagesSND Z Q DQ PDFJay Rameshbhai ParikhNo ratings yet

- SUB: Install Import / Export Features in EM 3460 MetersDocument2 pagesSUB: Install Import / Export Features in EM 3460 MetersJay Rameshbhai ParikhNo ratings yet

- Protection Signal and Alarm Signal Checking ST 2Document10 pagesProtection Signal and Alarm Signal Checking ST 2Jay Rameshbhai ParikhNo ratings yet

- Cable Size Calculation of 125 KW LT MotorDocument5 pagesCable Size Calculation of 125 KW LT MotorJay Rameshbhai ParikhNo ratings yet

- Cigre PDFDocument18 pagesCigre PDFJay Rameshbhai Parikh100% (1)

- IGNOU Solved Question Paper of Openmat Entrance Test 2007Document6 pagesIGNOU Solved Question Paper of Openmat Entrance Test 2007Jay Rameshbhai ParikhNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Clugston PDFDocument295 pagesClugston PDFdangthutqmNo ratings yet

- Practical Guidelines For Identifying and Tuning PID Control Loops With Long Deadtime And/or Time ConstantsDocument32 pagesPractical Guidelines For Identifying and Tuning PID Control Loops With Long Deadtime And/or Time ConstantsManish RaiNo ratings yet

- 805-7 Press Synchronization: Installation and Operating ManualDocument27 pages805-7 Press Synchronization: Installation and Operating ManualĐứcPhạmNo ratings yet

- Mane2019Document6 pagesMane2019ChinhNo ratings yet

- AV300i ProduktinformationDocument16 pagesAV300i ProduktinformationgafscottNo ratings yet

- Ziegler-Nichols Controller Tuning ExampleDocument6 pagesZiegler-Nichols Controller Tuning ExampleChristine AvdikouNo ratings yet

- Product AMD Type/Series C/CP2000 Appl. Note Nr. C-CP2000 PID Set-Up Release Date April 11, 2016Document8 pagesProduct AMD Type/Series C/CP2000 Appl. Note Nr. C-CP2000 PID Set-Up Release Date April 11, 2016Martin SanabriaNo ratings yet

- Satchwell Product Catalog PDFDocument36 pagesSatchwell Product Catalog PDFimagex5No ratings yet

- Integration of An Autopilot For A Micro Air VehicleDocument19 pagesIntegration of An Autopilot For A Micro Air VehicleolafpalmerNo ratings yet

- CMC PresentationDocument34 pagesCMC PresentationSandeep Kumar Sinha100% (2)

- Imperialist Competitive Algorithm ICA Presentation SlidesDocument35 pagesImperialist Competitive Algorithm ICA Presentation SlidesicasiteNo ratings yet

- ATV310 Getting Started Parameters EN EAV96136 05Document2 pagesATV310 Getting Started Parameters EN EAV96136 05paulNo ratings yet

- Control of Mechatronic Systems PDFDocument218 pagesControl of Mechatronic Systems PDFDMH100% (3)

- Low-Cost Microcontroller-Based Hover Control Design of A QuadcopterDocument7 pagesLow-Cost Microcontroller-Based Hover Control Design of A QuadcopterDanny AlejandroNo ratings yet

- Vacon NX Quick Help Start-Up Wizard: Press EnterDocument6 pagesVacon NX Quick Help Start-Up Wizard: Press EnterVuong Duc TungNo ratings yet

- Asahi Gold Particle Test System-II (AGPTS-II)Document8 pagesAsahi Gold Particle Test System-II (AGPTS-II)mguisseNo ratings yet

- Temperature Control Water Bath System Using PID ControllerDocument5 pagesTemperature Control Water Bath System Using PID Controllerprapya pokharelNo ratings yet

- Pagv2 PDFDocument698 pagesPagv2 PDFRomani FahmiNo ratings yet

- NI Tutorial 13720 enDocument6 pagesNI Tutorial 13720 enIvan VillanevaNo ratings yet

- User's Manual User's ManualDocument128 pagesUser's Manual User's ManualfelipezambranoNo ratings yet

- PID + Fuzzy Logic Process Controller: C22/C62/C82/C83/C72/C42/R22 User ManualDocument131 pagesPID + Fuzzy Logic Process Controller: C22/C62/C82/C83/C72/C42/R22 User ManualGabriel PiticasNo ratings yet

- UCCNC Software Installation and User's GuideDocument82 pagesUCCNC Software Installation and User's GuideManuel RamírezNo ratings yet

- AGC 150 TrainingDocument71 pagesAGC 150 TrainingVinesh VineshbNo ratings yet

- HONEYWELL Corporate and Student Training ScheduleDocument20 pagesHONEYWELL Corporate and Student Training ScheduleSyed Salman AliNo ratings yet

- Experiment 1 Ziegler Nichols Tuning: 1 ObjectiveDocument6 pagesExperiment 1 Ziegler Nichols Tuning: 1 ObjectiveHEMANT KUMARNo ratings yet

- Chapitre N 3 Le Transformateur MonophaseDocument38 pagesChapitre N 3 Le Transformateur MonophaseZouhair IguerhzifenNo ratings yet

- F GaddyDocument7 pagesF GaddyspyeagleNo ratings yet

- Hitachi Inverter PID Control Users' GuideDocument16 pagesHitachi Inverter PID Control Users' GuideMirinhaeThiago RosárioNo ratings yet

- Proofs 1st - Radius of InvestigationDocument15 pagesProofs 1st - Radius of InvestigationSarkodie KwameNo ratings yet

- Drone Project: Physics 118 - Final ReportDocument13 pagesDrone Project: Physics 118 - Final ReportMahdi MiriNo ratings yet