Professional Documents

Culture Documents

Cap7 Compensacion

Uploaded by

David NasaelOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cap7 Compensacion

Uploaded by

David NasaelCopyright:

Available Formats

PLEV 2010

Diseo y Compensacin de Sistemas de

Control

M.Sc. Javier A. Muoz V. Eduardo E. Espinosa N.

Ingeniero Civil Electrnico Ingeniero Civil Electrnico

javiermunoz@udec.cl eespinosa@udec.cl

Universidad de Concepcin Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Contenido del Capitulo PLEV 2010

Diseo y Compensacin de Sistemas de Control

I. Introduccin

II. Compensacin en Adelanto para Sistemas Continuos.

III. Compensacin en Atraso para Sistemas Continuos.

IV. Compensacin con Redes de Primer Orden Discretas.

V. Compensacin Adelanto - Atraso.

VI. Compensador P.I.D. Anlogo.

VII. Compensador P.I.D. Discreto.

Universidad de Concepcin -2- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Introduccin PLEV 2010

Los anlisis y herramientas desarrollados hasta aqu son tiles para determinar el

controlador a utilizar en un esquema realimentado. Como se ha indicado, el controlador

deber asegurar caractersticas estticas (error en estado estacionario, etc.) y

dinmicas (sobrepaso, tiempo de asentamiento, etc.). En este captulo, se estudiarn

las redes ms difundidas como son las de adelanto, atraso y PID (continuos y discretos)

incluyendo el diseo de todas y cada una de sus componentes.

Universidad de Concepcin -3- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Introduccin PLEV 2010

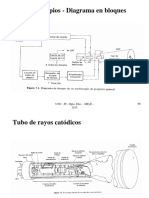

La estructura a estudiar se presenta en la Fig. 7.1, en donde deber determinarse el tipo de

controlador o combinacin de ellos y los parmetros de ste, para cumplir con requerimientos tales

como,

- Cero error en estado estacionario (yo = ydo),

- Estabilidad ( |y(t)| , t 0),

- Seguimiento ( yd(t) - y(t) = 0),

- Regulacin ( y(t) yd(t) ),

- Caractersticas dinmicas (sobrepaso, tiempo de asentamiento, margen de fase, de

ganancia,...)

- etc.

en plantas del tipo lineales, invariantes en el tiempo, continuas o discretas y/o hbridas, y SISO.

Fig. 7.1. Sistemas en L:C. a estudiar.

Universidad de Concepcin -4- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Introduccin PLEV 2010

La estructura del compensador podr ser una red de adelanto, red de atraso, una combinacin

adelanto-atraso o un P.I.D.. La mayor diferencia entre los compensadores es que a excepcin del

compensador P.I.D., todos son compensadores de primer orden. Como herramientas de anlisis y

diseo se emplearn el L.G.R., Diagrama de Bode, y Nyquist.

Universidad de Concepcin -5- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

El compensador es del tipo:

, h ( s ) = k 1 + sTc = k s + 1 Tc ,donde

1 + Tc s s + 1 Tc

c c c

debe cumplirse que el parmetro est en el

rango 0 < < 1. Una alternativa de

implementacin para este compensador se

muestra en la figura 7.2(a), donde se

eo ( s ) R4 R2 R1C1s + 1

encuentra hc ( s ) = = que

ei ( s ) R3 R1 R2C2 s + 1

, por lo tanto, Tc=R1C1, = (R2C2)/(R1C1),

kc=(R4C1)/(R3C2)

Fig. 7.2. Red de adelanto; (a) Circuito (b) L.G:R.

(c) Nyquist, (d)(e) Bode.

Universidad de Concepcin -6- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Caractersticas del Compensador en Adelanto

El L.G.R. del compensador, Fig. 7.2(b), indica un cero en s=-1/Tc y un polo en s=-1/(Tc), del

hc ( s ) s + 1 Tc

Nyquist de = ,Fig 7.2 (c), se aprecia que la mxima fase m cumple con la

kc s + 1 Tc

expresin sin m =

(1 ) 2 = 1 , por lo que, = 1 sin m y del bode, Fig 7.2(d) y (e), se obtiene

(1 + ) 2 1 + 1 + sin m

1 1 1 1

que log m = log + log , por lo que m = . Con estos antecedentes se puede

2 Tc Tc Tc

enunciar un procedimiento para el diseo de una red de adelanto.

Universidad de Concepcin -7- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Tcnicas de Compensacin de Adelanto Basadas en el L.G.R.

El procedimiento es el siguiente:

1.- Enumerar las especificaciones solicitadas a la respuesta del sistema en el tiempo. Traducir

stas a una ubicacin deseada para los polos dominantes.

2.- Dibujar el L.G.R. del sistema no compensado y determinar si es posible que la ganancia lleve

los polos del sistema en L.C. a la ubicacin deseada.

3.- Si el compensador es necesario, colocar el cero de la red de adelanto bajo la ubicacin de

los polos en L.C. deseadas.

4.- Determinar la ubicacin del polo restante de manera que cumpla con la condicin de ngulo.

5.- Calcular la ganancia del sistema en L.D. y as determinar la ganancia del controlador.

Calcular la ganancia de error esttico que corresponda (kp, kv, ka).

6.- Si la ganancia de error esttico fue especificada y no se cumple, ubicar el cero ms a la

izquierda del punto original del compensador y volver a 4.

Universidad de Concepcin -8- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Ejemplo 36

1

Se tiene: gr = y se desea =0.45 y n=4 ts=1 seg y kv=15

s ( s + 2)

Al utilizar una realimentacin unitaria con ganancia k, no se consigue llevar las races al lugar

deseado. Por lo tanto se propone una red de adelanto.

Paso 1.

=0.45 y n=4 s1,2=-4+-7.93j

Paso 2.

Dibujar L.G.R del sistema no compensado

Universidad de Concepcin -9- Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Ejemplo 36

Se tiene: gr = 1 y se desea =0.45 y n=4

s ( s + 2)

Paso 3.

Indica que 1/Tc =4

Paso 4.

Condicin de ngulo. p1 + p 2 + p 3 z1 = 180 p 3 = 49.11

7.93 7.93

tan p 3 = x = + 4 = 10.86

x4 tan p 3

Resumiendo, 1/(Tc)=10.86, Tc=0.25, =0.368, la ganancia es

( s + 1 Tc ) s s + 2 10.48

kc = ( ) = 8.888.17 = 95.87

( s + 1 Tc) s =4 + j 7.93

7.93

95.474

Con lo que kv = lm sgr ( s ) = = 17.65 por lo que el diseo es correcto.

s 0 10.862

Universidad de Concepcin - 10 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Tcnicas de Compensacin de Adelanto Basadas en el Diagrama de Bode.

Esta tcnica se justifica en el caso de tener sistemas con retardo, en cuyo caso el uso del

L.G.R. pasara indeclinablemente por una aproximacin de ste. El procedimiento es el siguiente:

1. Dibujar el diagrama de Bode para gr(s) con una ganancia tal que se satisfagan las condiciones

de error en S.S.

2. En el bode (1) determinar el M.F. del sistema no compensado. Calcular la fase necesaria a

introducir por el compensador, m. Agregar de un 10% a 30% como seguridad.

1

3. Utilizando sin m = , determinar = 1 sin m .

1+ 1 + sin m

4. Calcular la ganancia necesaria h(dB)=10 log.

5. Ubicar en el Bode de (1) la frecuencia m a la cual la atenuacin es de h(dB) y utilizando

m=1/Tc determinar Tc.

6. Dibujar el bode compensado, si las condiciones no se cumplen volver a (2) y utilizar otro margen

de seguridad.

Universidad de Concepcin - 11 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Adelanto para Sistemas Continuos. PLEV 2010

Ejemplo 37

k

Se tiene: g ( s ) = y se pide ess <10% para entrada rampa y un M.F.>30.

s ( s + 1)( s + 20 )

Paso 1.

Como se desea ess = 1/(k/20)=0.1, entonces k=200.

Bode Diagram

Gm = 6.44 dB (at 4.47 rad/sec) , Pm = 9.35 deg (at 3.07 rad/sec)

Paso 2 y 3 20

10

MF aprox. 10, por lo tanto,

Magnitude (dB)

0

m=20+8=28. Luego =0.361. -10

-20

Paso 4. -30

-135

H(db)=10 log =-4.34

Phase (deg)

-180

Paso 5.

m=4.05 y por lo tanto Tc=0.406. -225

0 1

10 10

Frequency (rad/sec)

Se hace notar que 200=200Kc Kc=2.71

Bode sistema sin compensar

Universidad de Concepcin - 12 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

El compensador es del tipo:

1 + sTc s + 1 Tc

hc ( s ) = kc = kc

1 + Tc s s + 1 Tc

donde debe cumplirse que el parmetro

>1. Una alternativa de implementacin para

este compensador se muestra en la figura

7.3 (a), donde se encuentra que

eo ( s ) R4 R2 R1C1s + 1

hc ( s ) = = ,

ei ( s ) R3 R1 R2C2 s + 1

R2C2 RC

con Tc = R1C1 , = y kc = 4 1

R1C1 R3C2

Fig. 7.3 Red de Atraso; (a) Circuito,

(b) L.G.R.,(c) Bode.

Universidad de Concepcin - 13 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

A. Caractersticas del Compensador en Atraso.

El L.G.R. del compensador, Fig 7.3(b), indica un cero en s=-1/Tc y un polo en s=-1/Tc, del

hc ( s ) s + 1 Tc

Nyquist de = , Fig 7.3 (c), se aprecia que la mxima fase m cumple con la

kc s + 1 Tc

expresin sin m =

( 1) 2 = 1 , por lo que 1 sin m

= (con m<0) y del bode, Fig 7.3 (d) y

( 1 + ) 2 1 + 1 + sin m

1

1

(e), se obtiene que log m = log + log 1 1 =

por lo que, m

. Con estos antecedentes

2 Tc Tc Tc

se puede enunciar un procedimiento para el diseo de una red de atraso.

Universidad de Concepcin - 14 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

B. Tcnicas de Compensacin para la Red de Atraso Utilizando L.G.R.

El procedimiento es el siguiente:

1.- Dibujar el L.G.R. para el sistema no compensado.

2.- Del comportamiento transitorio determinar la ubicacin deseada de los polos en L.C. Si el

sistema no pasa por el lugar deseado se deber emplear otra red de compensacin para que as

sea (p. ej. red de adelanto).

3.- Determinar la ganancia necesaria para obtener las races en el lugar deseado. Calcular la

constante de error esttico.

4.-Si la constante de error esttico no es suficiente, calcular el factor en que debe ser

aumentada. Este factor tambin corresponde al factor .

5.- Para asegurar que las races no se vean afectadas por el cero y polo del compensador, el

aporte neto de ngulo entre stos debe ser menor a 5. Es decir, | z comp-p comp|<5.

Universidad de Concepcin - 15 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

Ejemplo 38

k

Se tiene: g ( s ) = del cual se desea tener =0.45 y kv=7, disee un compensador

s ( s + 1)( s + 5 )

en atraso.

Root Locus

Paso 1. 3 System: sys

Gain: 4.16

Pole: -0.398 + 0.797i

2 Damping: 0.447

Overshoot (%): 20.8

Frequency (rad/sec): 0.891

Imaginary Axis 1

-1

-2

-3

-5 -4 -3 -2 -1 0 1

Real Axis

Paso 2 y 3 LGR sistema sin compensar.

k

Kv=7, como kv = lim sgr = = 7 k = 35

s 0 5

Universidad de Concepcin - 16 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

Ejemplo 38

Sin embargo, el polinomio caracterstico es k + ( s 2 + s ) ( s + 5 ) = s 3 + 6 s 2 + 5s + k y el polinomio

deseado es (s 2

+ 2n s + n2 ) ( s + a ) , con = 0.45, por lo que, ( s 2 + 0.9n s + n2 ) ( s + a ) = ...

... = s 3 + as 2 + 0.9n s 2 + 0.9n as + n2 s + n2 a = s 3 + s 2 ( 0.9n + a ) + s ( 0.9n a + n2 ) + n2 a, igualando

( )

trminos se tiene que, ( 0.9n + a ) = 6, 0.9n a + n2 = 5, n2 a = k , por lo que

a = 6 0.9n , 5 = ( 0.9n ( 6 0.9n )+ ) =

2

n

2

n + 5.4n 0.81n2 , donde n = 0.8976, y entonces

a = 5.192, n = 0.4, k = 4.183. Con estos resultados se tiene que kv=k/5=4.183/5=0.8366=kv N-C

=kv C-C / kv N-C = 8.37.

Sea Tc=10, por lo que 1/Tc=0.1, 1/Tc=0.012,

p comp = 90 +tg 1 ( ( 0.4 0.012 ) 0.8 ) = 115.87 z comp = 90 +tg 1 ( ( 0.4 0.01) 0.8 ) = 110.55

p comp z comp = 5.31

Universidad de Concepcin - 17 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

Ejemplo 38

En caso que los 5 deban ser exactos, se puede utilizar la siguiente expresin.

1 T

1

1 n 1 Tc

5 = tg n c

tg =

n 1 n 1

2 2

Entonces,

{ }

Tc2 { tg n2 } Tc n ( + 1) tg +n 1 2 ( 1) + tg = 0

Tc = 10.56

s + 0.0947

Finalmente en el compensador es

s + 0.0113

Universidad de Concepcin - 18 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

C. Tcnica de Compensacin para la Red de Atraso Utilizando el Diagrama de Bode

Al igual que en la red de adelanto, este procedimiento se justifica en el caso de tener sistemas

con retardo, en donde la utilizacin del L.G.R. como herramienta de diseo pasara

ineludiblemente por simplificaciones. El procedimiento es el siguiente:

1.- Dibujar el Bode del sistema sin compensador pero con la ganancia ajustada de manera de

cumplir con la premisa del coeficiente de error esttico, de donde se obtiene kc 1.

2.- Determinar el M.F. del sistema. Si no es suficiente, proceder de acuerdo a lo siguiente.

3.- Determinar del grfico la frecuencia (g) a la cual se generara un M.F. igual al deseado ms

5.

4.- Colocar el cero del compensador una dcada por debajo de g, es decir, 1/Tc = g/10.

5.- Medir la atenuacin necesaria en g y obtener kc de 20 log = | gr(j g)|.

Universidad de Concepcin - 19 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

Ejemplo 39

2500

Se tiene a gr ( s ) = y se desea un M.F.>45 y un ess para entrada rampa normalizada

s ( s + 25 )

< 0.01.

(1)Se desea

2500 2500 100

kc = 100kc kc = 1 gr ( s ) ' =

1 1 2500

kv = = = lim kc = =

ess 0.01 25 s ( s + 25 ) s ( s + 25 ) s ( 0.04s + 1)

(2)El nuevo sistema tiene un M.Fs-c=28 que no es suficiente por lo que se prosigue con el diseo.

Universidad de Concepcin - 20 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin en Atraso para Sistemas Continuos. PLEV 2010

Ejemplo 39

2500

Se tiene a gr ( s ) = y se desea un M.F.>45 y un ess para entrada rampa normalizada

s ( s + 25 )

< 0.01.

(1)g=21 (4) 1/Tc =g/10 Tc =0.47

s + 2.1

(5) 20 log = 14 dB, =3.98 kc=0.25, por lo que el compensador es hc ( s ) = 0.25

s + 0.52

Universidad de Concepcin - 21 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin con Redes de Primer Orden Discretas. PLEV 2010

Para continuar con la dualidad de las redes de primer orden continuas, se propone tambin

z + 1 Tc

estudiar la red de primer orden discreta del tipo hc ( z ) = kc . No es conveniente clasificar la

z + 1 Tc

red discreta en adelanto o atraso puesto que el signo de T y pueden ser negativos y/o positivos,

lo que dificulta la percepcin de aporte de fase. Es importante recordar la aparicin de un retardo

producto de la implementacin digital de este controlador, el que debe ser considerado a la hora de

su diseo. En este caso slo se revisa la utilizacin del L.G.R. como herramienta de diseo, puesto

que tambin permite cubrir casos con retardo, donde ste es mltiplo del tiempo de muestreo. El

procedimiento de diseo es como el explicado en el caso continuo; esto se debe a que las reglas

de construccin del L.G.R. son idnticas en ambos casos.

Universidad de Concepcin - 22 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin Adelanto-

Adelanto-Atraso. PLEV 2010

Este compensador combina ambas redes en un solo elemento. Sin embargo, el diseo de los

compensadores se realiza por separado y considerando los procedimientos antes expuestos. La

ecuacin del compensador total es,

1 + sTc1 1 + sTc 2

hc ( s ) = kc11 kc 2 2

1 + 1Tc1s 1 + 2Tc 2 s

con 1 < 1 y 2 > 1, por lo que para su diseo, se ajusta la red de adelanto (lo que modifica la

ubicacin de las races) y luego se ajusta la red de atraso para satisfacer las condiciones restantes.

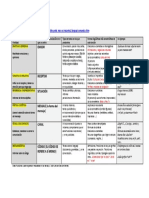

Al comparar las redes se tiene la Tabla 7.1.

Universidad de Concepcin - 23 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin Adelanto-

Adelanto-Atraso. PLEV 2010

Un circuito alternativo para la implementacin anloga es ilustrado en la Fig. 7.4. El circuito tiene

la F. de T.,

1 + sTc1 1 + sTc 2

hc ( s ) = kc11 kc 2 2

1 + 1Tc1s 1 + 2Tc 2 s

eo ( s ) R6 R4 ( R1 + R3 ) C1s + 1 R2C2 s + 1

hc ( s ) = = ,

ei ( s ) R5 R3 R1C1s + 1 ( R2 + R4 ) C2 s + 1

R1 R + R4 R R R + R3 R2

con Tc1 = ( R1 + R3 ) C1 , Tc 2 = R2C2 , 1 = , 2 = 2 y kc = 6 4 1

R1 + R3 R2 R5 R3 R2 + R4 R1

Notar que se cumple que 1 < 1 y 2 > 1.

Fig. 7.4 Circuito Compensador Adelanto-Atraso.

Universidad de Concepcin - 24 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo. PLEV 2010

Este compensador es uno de los ms difundidos en estrategias de control anlogas y discretas.

La F. de T. del compensador anlogo es,

u (s) 1

hc ( s ) = = k p 1 + + Td s ,

e(s) sTi

donde, kp: es la ganancia proporcional, Ti: el tiempo integral, y Td: el tiempo derivativo. Su

nombre P.I.D. es por proporcional, integrativo y derivativo. En el dominio del tiempo el controlador

es,. 1

t

d

u ( t ) = k p e ( t ) + e ( t ) + Td e ( t ) ,

Ti

dt

lo que en Laplace se puede escribir como,

u (s) k

hc ( s ) = = k p + i + kd s,

e(s) s

donde, kp: es la ganancia proporcional, ki: es la ganancia integral y kd: es la ganancia derivativa.

Un circuito tentativo para la implementacin del P.I.D. en forma anloga es el ilustrado en la Fig.

7.5 cuyas ecuaciones son,

Universidad de Concepcin - 25 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

eo ( s ) R4 R1C1 + R2C2

1 R1C1 R2C2

hc ( s ) = = 1 + + ,

ei ( s ) R3 ( 1 1

R1C2 R C + R 2 2)

C s R C

1 1 + R2 2

C

R R C + R2C2 RC R C

con k p = 4 1 1 , Ti = ( R1C1 + R2C2 ) y Td = 1 1 2 2

R3 R1C2 R1C1 + R2C2

El problema es cunto deben ser los parmetros de un P.I.D. si se considera que tiene un polo en

el origen y dos ceros ubicables arbitrariamente de acuerdo a la siguiente representacin

i d s + Ti s + 1

1 ki TT 2

hc ( s ) = k p 1 + + Td s = k p + + kd s = k p ,

sT i s Ti s

El problema tambin se conoce como sintonizacin del controlador. Para simplificar el problema

se estudian los modos de operacin del P.I.D.

Fig. 7.5 Circuito para Compensador P.I.D.

Universidad de Concepcin - 26 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

eo ( s ) R4 R1C1 + R2C2

1 R1C1 R2C2

hc ( s ) = = 1 + + ,

ei ( s ) R3 ( 1 1

R1C2 R C + R 2 2)

C s R C

1 1 + R2 2

C

R R C + R2C2 RC R C

con k p = 4 1 1 , Ti = ( R1C1 + R2C2 ) y Td = 1 1 2 2

R3 R1C2 R1C1 + R2C2

El problema es cunto deben ser los parmetros de un P.I.D. si se considera que tiene un polo en

el origen y dos ceros ubicables arbitrariamente de acuerdo a la siguiente representacin

i d s + Ti s + 1

1 ki TT 2

hc ( s ) = k p 1 + + Td s = k p + + kd s = k p ,

sT i s Ti s

El problema tambin se conoce como sintonizacin del controlador. Para simplificar el problema

se estudian los modos de operacin del P.I.D.

Fig. 7.5 Circuito para Compensador P.I.D.

Universidad de Concepcin - 27 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

Modos de Operacin

Proporcional

Ti, Td 0 hc ( s ) = k p ,

En una planta se ajusta kp para asegurar un ess o M.F. dados.

Proporcional-Integral.

(Td 0) 1 sTi + 1

hc ( s ) = k p 1 + = kp ,

sTi sTi

s +1 T c s +1 T c sT + 1

Es una red de atraso, kc , con > 1, con , kc = kc c

s + 1 T c s s

Proporcional-Derivativo (Ti )

hc ( s ) = k p {1 + Td s} ,

1 + sTc

kc , con < 1, con 0 : kc ' (1 + sTc )

Es una red de adelanto: 1 + sTc

Universidad de Concepcin - 28 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

Sintonizacin de un P.I.D.

Esta metodologa est basada en la determinacin de una manera prctica o emprica de los

parmetros kp, Ti y Td. Es decir, mediante experimentacin en la planta o sistema. Se distinguen

dos casos, el primero para sistemas que pueden operar en L.A. y el segundo para sistemas que

slo pueden operar en L.C. En este ltimo se distinguen entre sistemas que pueden oscilar en

forma sostenida y los que no lo pueden hacer.

Compensacin emprica en L.A. (Ziegler-Nichols en L.A.)

Se utiliza en sistemas que pueden operar en L.A. como son los sistemas estables. Los

parmetros del controlador se fijan en funcin de los parmetros de la respuesta de la planta en

L.A. a una entrada escaln que se asume de primer orden y con retardo, Fig. 7.6. En particular, se

escogen los parmetros de acuerdo a la Tabla 7.2.

Universidad de Concepcin - 29 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

Este diseo persigue que la respuesta en L.C. no tenga un sobrepaso mayor al 25% ante

entrada escaln. Ntese que este mtodo se aplica si la planta responde con una dinmica tipo s.

No se tiene esto cuando la planta tiene polos en el eje imaginario o es inestable. Para estos casos

se tienen las alternativas siguientes.

Fig. 7.6 Sintonizacin de un P.I.D. en L.A. (Ziegler-Nichols en L.A.).

Universidad de Concepcin - 30 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

Compensacin emprica en L.C. (Ziegler-Nichols en L.C.)

Este mtodo se utiliza en sistemas que no pueden operar en L.A., como por ejemplo los

sistemas que tienen polos en el origen (estanques). Adems se requiere que el sistema pueda

permanecer oscilando en L.C. en forma permanente para algn valor de la ganancia. Para

sintonizar el controlador se hace Ti y Td 0 y se incrementa kp hasta que el sistema oscile

en forma sostenida Fig. 7.7. Esta ganancia es denomina kcr y el perodo de oscilacin se

denomina Tcr. Con estos valores se utiliza la Tabla 7.3 para determinar los parmetros del

controlador P.I.D..

Fig. 7.7 Sintonizacin de un P.I.D. en L.C. (Ziegler- TABLA 7.3 Seleccin de parmetros de un PID

Nichols en L.C.). mediante Ziegler-Nichols en L.C..

Universidad de Concepcin - 31 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Anlogo PLEV 2010

Harriot

Si el sistema en L.C. nunca oscila en forma sostenida y no se puede operar en L.A., entonces se

puede llevar con Ti y Td 0 a una oscilacin amortiguada tal que la razn b/a (Fig. 7.8) sea

. En la oscilacin se define Tcr como el perodo de oscilacin y con este valor se ajustan Ti =

Tcr/6 y Td = Tcr/1.5, luego se hace operar el sistema en L.C. y se modifica kp tal que la razn b/a

sea nuevamente.

Fig. 7.8.Determinacin de Tcr en el mtodo de sintonizacin de Harriot

Universidad de Concepcin - 32 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Discreto. PLEV 2010

La popularidad y xito del control P.I.D. continuo ha motivado su utilizacin en sistemas discretos.

Sin embargo, la derivada como tal no existe en sistemas digitales por lo que se ha optado por

considerar a este controlador discreto como uno que tiene un integrador puro (un polo en 1) y dos

ceros.

P.I.D. Discreto Generalizado.

Se considera al controlador con un polo en 1 y dos ceros. As, los ceros y la ganancia podrn ser

asignados arbitrariamente y por tanto, para un caso particular, la problemtica se reduce a

determinar estos valores. Un controlador P.I.D. discreto es entonces,

hc ( z ) = k p

z 2 + b1 z + b0

= kp

( z + z1 )( z + z2 )

,

z 1 z 1

en donde kp, b1 y b0 son parmetros a determinar. Los procedimientos anteriores son vlidos

para su diseo en el caso de considerar un solo cero, pues entonces se tiene una red de primer

orden. Es importante destacar que la implementacin en un sistema digital de este controlador

como cualesquier controlador discreto agrega un retardo igual al tiempo de muestreo T, el cual

debe ser considerado a la hora del diseo.

Universidad de Concepcin - 33 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Discreto. PLEV 2010

P.I.D. Discreto Aproximado.

Una forma alternativa de determinar los coeficientes del controlador es mediante la aproximacin

del controlador continuo. Es decir, realizar el diseo del controlador P.I.D. continuo y luego

encontrar una aproximacin discreta. Sea el controlador P.I.D. continuo,

1

t

d

u ( t ) = k p e ( t ) + e ( t ) + Td dt e ( t ) ,

Ti

El que se puede aproximar por,

1 e ( kT ) + e ( kT T ) e ( kT ) + e ( kT T )

u ( kT ) = k p e ( kT ) + S ( kT T ) + T +

d T ,

T1 2 T

Donde S(kT-T) es la integral hasta el instante kT-T. Tambin se puede escribir,

1 e ( kT T ) + e ( kT 2T )

u ( kT T ) = k p e ( kT T ) + S ( kT T ) + Td ,

T1 T

Tomando u(kT)-u(kT-T) se tiene,

e ( kT ) e ( kT T ) +

T

2Ti

( e ( kT ) e ( kT T ) ) +

u ( kT ) u ( kT T ) = k p ,

( e ( kT ) 2e ( kT T ) + e ( kT 2T ) )

Td

T

Universidad de Concepcin - 34 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Discreto. PLEV 2010

P.I.D. Discreto Aproximado.

o bien,

T Td T 2Td Td

u ( kT ) u ( kT T ) = k p 1 + + e ( kT ) + 1 + e ( kT T ) + e ( kT 2T )

2Ti T 2Ti T T

y que corresponde a una frmula directamente implementable en un sistema digital. Sin embargo,

al tomar la T.Z. para determinar lo que se est agregando como controlador se tiene que,

T Td T 2Td 1 Td 2

u ( z ) z 1u ( z ) = k p 1 + + e ( z ) + 1 + z e ( z ) + z e ( z )

2Ti T 2Ti T T

O bien,

T Td 2 T 2Td Td

z 2u ( z ) zu ( z ) = k p 1 + + z e ( z ) + 1 + ( )

ze z + e ( )

z

2Ti T 2Ti T T

Lo que corresponde a la F.de T.

T Td 2 T 2Td Td

1 +

2T T + z + 1 + z +

u ( z) 2Ti T T

= kp i

e( z) z ( z 1)

Universidad de Concepcin - 35 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

Compensacin P.I.D Discreto. PLEV 2010

P.I.D. Discreto Aproximado.

Claramente, la F. de T. anterior aporta con dos ceros ubicables arbitrariamente, un polo en 1 y un

polo en el origen. Este ltimo no es parte de lo esperado del P.I.D. continuo y es producto del

retardo incluido por la aproximacin de su derivada. En efecto, si Td = 0, se tiene que la F. de T.

resultante es, T T

1 + z 2

+ 1 + z

u ( z) 2Ti 2Ti

= kp

e( z) ( z 1)

la que tiene un cero y un polo en 1. Ntese que para efectos de anlisis, todava debe agregarse

el retardo por clculo. Este agrega un polo ms en el origen el que sin dudas va en desmedro de

los ndices de estabilidad.

Universidad de Concepcin - 36 - Javier Muoz V.

Departamento de ingeniera Elctrica Eduardo Espinosa N.

You might also like

- Trabajo Practico 1 (Comunicaciones 2)Document9 pagesTrabajo Practico 1 (Comunicaciones 2)David NasaelNo ratings yet

- 21 - 06 - 2020 - Fuera de Juego - ServidorDocument18 pages21 - 06 - 2020 - Fuera de Juego - ServidorDavid NasaelNo ratings yet

- Cuando Algo Sale Mal TBuchDocument2 pagesCuando Algo Sale Mal TBuchDavid NasaelNo ratings yet

- Tablero de IndicadoresDocument1 pageTablero de IndicadoresDavid NasaelNo ratings yet

- IshikawaDocument2 pagesIshikawaDavid NasaelNo ratings yet

- Control Digital, Teoría y Práctica 2ed - Luis Eduardo García JaimesDocument427 pagesControl Digital, Teoría y Práctica 2ed - Luis Eduardo García JaimesGiovanny Alvarez94% (16)

- Trabajo Practico 2 (Comunicaciones 2)Document8 pagesTrabajo Practico 2 (Comunicaciones 2)David NasaelNo ratings yet

- Ley 19587 y Decreto 351-79Document65 pagesLey 19587 y Decreto 351-79Tongas99No ratings yet

- Mediciones Electricas - Juan Sabato PDFDocument151 pagesMediciones Electricas - Juan Sabato PDFDenis Van ZandwegheNo ratings yet

- Central Elementos 2013Document101 pagesCentral Elementos 2013David NasaelNo ratings yet

- Peligro y RiesgoDocument5 pagesPeligro y RiesgoDavid NasaelNo ratings yet

- QUÍMICADocument9 pagesQUÍMICADavid NasaelNo ratings yet

- El Sistema Legal ArgentinoDocument20 pagesEl Sistema Legal ArgentinoDavid NasaelNo ratings yet

- QUÍMICADocument9 pagesQUÍMICADavid NasaelNo ratings yet

- Cap7 MosfetDocument51 pagesCap7 MosfetAldo SalazarNo ratings yet

- SCC w7 CL 2Document22 pagesSCC w7 CL 2David NasaelNo ratings yet

- Teoria de Las Comunicaciones - Pedro E. DanizioDocument295 pagesTeoria de Las Comunicaciones - Pedro E. Daniziogonzalo100% (2)

- Calculo de Un AmplificadorDocument1 pageCalculo de Un AmplificadorDavid NasaelNo ratings yet

- ResistenciasDocument2 pagesResistenciasDavid NasaelNo ratings yet

- Notas Curso ElectricidadDocument53 pagesNotas Curso ElectricidadelectricistabuenoNo ratings yet

- 2011 Calculo de Circuitos RamalesDocument35 pages2011 Calculo de Circuitos Ramalesalguesi16No ratings yet

- 2 Osciloscopio2015Document35 pages2 Osciloscopio2015David NasaelNo ratings yet

- Simulación de Circuitos Con MultisimDocument22 pagesSimulación de Circuitos Con MultisimyemerNo ratings yet

- 1 - Medición de Parámetros Básicos2015Document29 pages1 - Medición de Parámetros Básicos2015David NasaelNo ratings yet

- Medidor NARDADocument17 pagesMedidor NARDADavid NasaelNo ratings yet

- Fusibles Lupo, CrossfoxDocument3 pagesFusibles Lupo, CrossfoxSebastian Sánchez83% (35)

- Medidor NARDADocument17 pagesMedidor NARDADavid NasaelNo ratings yet

- Homolog NQNDocument1 pageHomolog NQNDavid NasaelNo ratings yet

- MODULO 05 COAXIAL SR PDFDocument95 pagesMODULO 05 COAXIAL SR PDFAnderson NuñezNo ratings yet

- Evaluacion SeñalesDocument5 pagesEvaluacion SeñalesDavid NasaelNo ratings yet

- Historia de La Escuela Amable ArauzDocument2 pagesHistoria de La Escuela Amable ArauzMauricio Pilataxi67% (3)

- Felipe Morales - La Malla Conceptual de Sentido Común Sobre La ConscienciaDocument20 pagesFelipe Morales - La Malla Conceptual de Sentido Común Sobre La ConscienciaFelipe MoralesNo ratings yet

- UCIDocument30 pagesUCIÁngel Josué Aguirre Morán100% (1)

- Trabajo de Mi AmorcitoDocument3 pagesTrabajo de Mi AmorcitoZholNo ratings yet

- Acto Dia de La Tradición Turno MAÑANADocument3 pagesActo Dia de La Tradición Turno MAÑANALaura SalarNo ratings yet

- Microcurriculo HidraulicaDocument2 pagesMicrocurriculo HidraulicaAlexis ForeroNo ratings yet

- Formato SyllabusDocument4 pagesFormato SyllabusDianelis SanchezNo ratings yet

- EvangelizarDocument2 pagesEvangelizarRamiro Ortiz AlcocerNo ratings yet

- Carta Estudiante CI-1312 Iciclo2016Document5 pagesCarta Estudiante CI-1312 Iciclo2016Marcelo SolórzanoNo ratings yet

- Esquema de Las Funciones Del LenguajeDocument1 pageEsquema de Las Funciones Del LenguajeMari PérezNo ratings yet

- Epidemiología DescriptivaDocument8 pagesEpidemiología Descriptivaalfred martinezNo ratings yet

- PruebaLibro Mamire El Ultimo NiñoDocument4 pagesPruebaLibro Mamire El Ultimo NiñoLorenzoCortezAraya100% (2)

- Alicia Stolkiner. RedesDocument21 pagesAlicia Stolkiner. RedesNeelu BoettiNo ratings yet

- Triptico de CienciasDocument2 pagesTriptico de CienciasMArcos ARenas EUstaquioNo ratings yet

- Inciso A y H Internet de Las Cosas y Presentaciones de PowerpointDocument7 pagesInciso A y H Internet de Las Cosas y Presentaciones de PowerpointEduardo MatamorosNo ratings yet

- Rejilla LingualDocument8 pagesRejilla LingualPablo MezaNo ratings yet

- Confecciones LalangueDocument25 pagesConfecciones LalangueCarlos Porras LumbreNo ratings yet

- PLAN-2017 Horarios Verano 2019 - 2020Document6 pagesPLAN-2017 Horarios Verano 2019 - 2020Nelson Campos LauraNo ratings yet

- Cartillas DiocesanaDocument38 pagesCartillas DiocesanaDiego VillalbaNo ratings yet

- Levántate Alma CristianaDocument2 pagesLevántate Alma CristianaOmar OmarNo ratings yet

- Teleclase 16 OrtDocument14 pagesTeleclase 16 OrtRosaili RodríguezNo ratings yet

- Adverbio de Tiempo Lugar y ModoDocument4 pagesAdverbio de Tiempo Lugar y ModoGiovanni Sánchez100% (1)

- Confesiones de MCDocument8 pagesConfesiones de MCAlejandra GonzálezNo ratings yet

- El Nuevo Dardo en La Palabra.Document7 pagesEl Nuevo Dardo en La Palabra.Germ MartianNo ratings yet

- Cien Sonetos de AmorDocument1 pageCien Sonetos de AmorCjprNo ratings yet

- El ABC Emocional de Albert EllisDocument4 pagesEl ABC Emocional de Albert EllisJuan Pablo Zapata RamírezNo ratings yet

- Madurez EscolarDocument11 pagesMadurez EscolarMarce Caris100% (2)

- Circuitos Con Resistencias Eléctricas en Serie y ParaleloDocument9 pagesCircuitos Con Resistencias Eléctricas en Serie y ParaleloWalmer GutierrezNo ratings yet

- Planificacion Didactica TecnologiaDocument3 pagesPlanificacion Didactica TecnologiaKatherin Suley MartinezNo ratings yet

- El BautismoDocument2 pagesEl BautismoDaniel AbreuNo ratings yet