Professional Documents

Culture Documents

SR latch timing diagram solutions

Uploaded by

omairakhtar12345Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SR latch timing diagram solutions

Uploaded by

omairakhtar12345Copyright:

Available Formats

ENS2456 Digital Electronics

Tutorial 04

Solutions

1. Trace the behaviour of an SR latch for the following situation: Q, S, and R have been

0 for a long time, then S changes to 1 and stays 1 for a long time, then S changes

back to 0. Using a timing diagram, show the values that appear on wires S, R, Q, and

Q. Assume logic gates have a tiny nonzero delay.

S

0

R

0

Q

0

Q'

0

ENS2456 Solutions 4 Page 1

ENS2456 Digital Electronics

2. Trace the behaviour of a level-sensitive SR latch (see below) for the input pattern

in Figure 1. Assume S1, R1, and Q are initially 0. Complete the timing diagram,

assuming logic gates have a tiny but non-zero delay.

Figure 1.

ENS2456 Solutions 4 Page 2

ENS2456 Digital Electronics

3. Trace the behaviour of a D latch (see below) for the input pattern in Figure 2. Assume Q is

initially 0. Complete the timing diagram, assuming logic gates have a tiny but non-zero

delay.

Figure 2.

ENS2456 Solutions 4 Page 3

ENS2456 Digital Electronics

4. Create a circuit of three level-sensitive D latches connected in series (the output of one is

connected to the input of the next). Use a timing diagram to show how a clock with a long

high-time can cause the value at the input of the first D latch to trickle through more than

one latch during the same clock cycle.

5. Repeat problem 8 using edge-triggered D flip-flops, and use a timing diagram to show

how the input of the first D flip-flop does not trickle through to the next flip-flop no matter

how long the clock signal is high.

ENS2456 Solutions 4 Page 4

ENS2456 Digital Electronics

6. Design a synchronous MOD-8 binary up/down counter. Use D flip-flops.

The PRESENT state/NEXT state table for MOD-8 binary up/dn counter

MOD-8 Binary UP/DN Counter

PRESENT NEXT Flip-Flops

State State Control Inputs

DEC UP/DN C B A C B A DC DB DA

0 0 0 0 0 0 0 1 0 0 1

1 0 0 0 1 0 1 0 0 1 0

2 0 0 1 0 0 1 1 0 1 1

3 0 0 1 1 1 0 0 1 0 0

4 0 1 0 0 1 0 1 1 0 1

5 0 1 0 1 1 1 0 1 1 0

6 0 1 1 0 1 1 1 1 1 1

7 0 1 1 1 0 0 0 0 0 0

8 1 0 0 0 1 1 1 1 1 1

9 1 0 0 1 0 0 0 0 0 0

10 1 0 1 0 0 0 1 0 0 1

11 1 0 1 1 0 1 0 0 1 0

12 1 1 0 0 0 1 1 0 1 1

13 1 1 0 1 1 0 0 1 0 0

14 1 1 1 0 1 0 1 1 0 1

15 1 1 1 1 1 1 0 1 1 0

ENS2456 Solutions 4 Page 5

ENS2456 Digital Electronics

Boolean equation for the input of each D flip-flop

DC DB

B B

0 0 1 0 0 1 0 1

1 1 0 1

0 1 0 1

C

C

0 1 1 1 1 0 1 0

UP/DN UP/DN

1 0 0 0 1 0 1 0

A A

DC = UP/DNC'B'A' + UP/DNCA + DB = UP/DN'B'A + UP/DN'BA +

+ CBA' + UP/DN'CB' + UP/DN'C'BA + UP/DNB'A' + UP/DNBA

DA

B

1 0 0 1

1 0 0 1

C

1 0 0 1

UP/DN

1 0 0 1

A

DA = A'

Implementation

A B C

D Q D Q D Q

A B C

CLK Q Q Q

C'

C

B'

UP/DN B

A

A'

UP/DN

UP/DN'

ENS2456 Solutions 4 Page 6

ENS2456 Digital Electronics

7. Using the process for designing a controller, convert the FSM of figure below to a

controller, implementing the controller using a state register and logic gates.

Step 1 - Capture the FSM

The appropriate FSM is given above.

Step 2A - Set up the architecture

Step 2C - Fill in the truth table

ENS2456 Solutions 4 Page 7

ENS2456 Digital Electronics

Step 2D - Implement the combinational logic

n1 = s1s0a + s1s0a + s1s0a = s1s0a + s1s0

n0 = s1s0a + s1s0a + s1s0a + s1s0a = s1a + s1s0

y = s1s0a + s1s0a + s1s0a + s1s0a = s1s0 + s1s0 = s1 xor s0

8. Reverse engineer the behaviour of the sequential circuit shown in figure below.

For this problem, we carry out the controller design process in reverse. We already

have step 2D completed above, so we will begin with step 2C.

ENS2456 Solutions 4 Page 8

ENS2456 Digital Electronics

Step 2C - Fill in the truth table

Step 2B - Encode the states

We will name the encodings as states as follows: 00=A, 01=B, 10=C, and 11=D.

Step 2A- Set up the architecture

The architecture has already been defined

Step 1 - Capture the FSM

ENS2456 Solutions 4 Page 9

You might also like

- DLD HWDocument17 pagesDLD HWNấm LùnNo ratings yet

- Cost Estimating Manual for Pipelines and Marine Structures: New Printing 1999From EverandCost Estimating Manual for Pipelines and Marine Structures: New Printing 1999Rating: 5 out of 5 stars5/5 (2)

- Digital Electronics - Tutorial #1Document3 pagesDigital Electronics - Tutorial #1Dishawn NationNo ratings yet

- Experiment 2 SALAZARDocument9 pagesExperiment 2 SALAZARgerand salazarNo ratings yet

- Digital Design Lab ReportDocument7 pagesDigital Design Lab ReportJohn DoeNo ratings yet

- Lab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapDocument4 pagesLab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapInam Ur RehmanNo ratings yet

- Expt 06-1Document5 pagesExpt 06-1Aurongo NasirNo ratings yet

- MSU Fatima Campus Digital Design Projects on Sequential LogicDocument10 pagesMSU Fatima Campus Digital Design Projects on Sequential LogicJanus Rau CunananNo ratings yet

- Lab 3 Group 2 Haziq & AdamDocument16 pagesLab 3 Group 2 Haziq & AdamShamalen RajanNo ratings yet

- Experiment 7Document7 pagesExperiment 7Karan KumarNo ratings yet

- Tutorial 2 - Electronics (2018)Document3 pagesTutorial 2 - Electronics (2018)Pasindu PramodNo ratings yet

- Digital Electronics - Tutorial #4Document2 pagesDigital Electronics - Tutorial #4Dishawn NationNo ratings yet

- Chapter 7 - Shift RegisterDocument35 pagesChapter 7 - Shift RegisterHumna DubbiiNo ratings yet

- BI2002B - Circuitos LógicosDocument30 pagesBI2002B - Circuitos LógicosHéctor Vega SantamaríaNo ratings yet

- Assignment 1Document41 pagesAssignment 1Sai BharathNo ratings yet

- 37 DLD Lec 37 Design of Sequential Circuits Example Dated 09 Dec 2022 Lecture SlidesDocument18 pages37 DLD Lec 37 Design of Sequential Circuits Example Dated 09 Dec 2022 Lecture SlidesZuha FatimaNo ratings yet

- NOT/INVERTER Gate Lab ExerciseDocument5 pagesNOT/INVERTER Gate Lab ExerciseRicardo Edrell RiveraNo ratings yet

- Double Sequence Detector: Project ReportDocument26 pagesDouble Sequence Detector: Project Reportapi-26783388No ratings yet

- Lab 3Document7 pagesLab 32221634No ratings yet

- Circuit DesignDocument15 pagesCircuit DesignHafiezul HassanNo ratings yet

- Combinational Logic Gate Schematic and Truth TableDocument5 pagesCombinational Logic Gate Schematic and Truth TableFaisal HaroonNo ratings yet

- Lab 8 and 9 Group AssignmentDocument11 pagesLab 8 and 9 Group AssignmentMaryam KhalilNo ratings yet

- Name: Izaan Ahmed Khan STD ID: FA19-BSCS-0049 COURSE: DLD Theory Assignment # 03Document10 pagesName: Izaan Ahmed Khan STD ID: FA19-BSCS-0049 COURSE: DLD Theory Assignment # 03Izaan Ahmed KhanNo ratings yet

- Chapter 4Document17 pagesChapter 4haiqa suhailNo ratings yet

- FDDGDocument3 pagesFDDGaliffpadziNo ratings yet

- Digital Circuits-I LAB: Jadavpur UniversityDocument15 pagesDigital Circuits-I LAB: Jadavpur UniversityIron PatriotNo ratings yet

- Combinational Circuit DesignDocument12 pagesCombinational Circuit DesignMuhammad WasiNo ratings yet

- 3-bit up/down counter design with direction control using D flip-flopsDocument3 pages3-bit up/down counter design with direction control using D flip-flopsCeline Fernandez CelociaNo ratings yet

- Lab Rep 3-4Document7 pagesLab Rep 3-4Muhammad Hamza TariqNo ratings yet

- Assignment 1 DGEN245 Digital ElectronicDocument3 pagesAssignment 1 DGEN245 Digital ElectronicAja AzizNo ratings yet

- LAB 1 - Basic Logic Gates - BERMUDEZ. - BSECE-3ADocument18 pagesLAB 1 - Basic Logic Gates - BERMUDEZ. - BSECE-3AJenny A. BermudezNo ratings yet

- PCB Reprt (1) FinalDocument8 pagesPCB Reprt (1) FinalShamma SNo ratings yet

- RIVERA LOGICS - Lab 6Document4 pagesRIVERA LOGICS - Lab 6Ricardo Edrell RiveraNo ratings yet

- Designs of Sequential CircuitsDocument20 pagesDesigns of Sequential CircuitsPrecious Lovely CustodioNo ratings yet

- Car Security System-Recitation ExampleDocument3 pagesCar Security System-Recitation ExamplePRaed AliNo ratings yet

- Logic Lab#4Document9 pagesLogic Lab#4Enver Kaan ÇabukNo ratings yet

- Rajshahi University of Engineering & Technology: Heaven's Light Is Our GuideDocument38 pagesRajshahi University of Engineering & Technology: Heaven's Light Is Our GuideNafis HasanNo ratings yet

- EEE 180.1 Lab3Document4 pagesEEE 180.1 Lab3Enrico PonceNo ratings yet

- 15.3 Hardware Cambridge CS A2Document5 pages15.3 Hardware Cambridge CS A2chirantha150No ratings yet

- AnswersDocument167 pagesAnswersmilindpaladugu01No ratings yet

- Experiment 3 - CSC 204 LabDocument7 pagesExperiment 3 - CSC 204 Lab2221634No ratings yet

- Digital DesignDocument4 pagesDigital DesignHasan CanarslanNo ratings yet

- Taller Chapter 3 Sistemas DigitalesDocument4 pagesTaller Chapter 3 Sistemas DigitalesCristian PuentesNo ratings yet

- DLD Assignment#2Document3 pagesDLD Assignment#2Muhammad AliNo ratings yet

- Task 1: Make The Circuit of 2-Bit Magnitude Comparator and Fill The Truth Table. Solution: Truth TableDocument4 pagesTask 1: Make The Circuit of 2-Bit Magnitude Comparator and Fill The Truth Table. Solution: Truth Tablewaleed infoNo ratings yet

- Counter Circuits: ObjectivesDocument9 pagesCounter Circuits: ObjectivesRuhul Amin Khalil100% (1)

- Guia Lab 2Document3 pagesGuia Lab 2Electro NICNo ratings yet

- CELOCIA 3-bit up/down counterDocument3 pagesCELOCIA 3-bit up/down counterCeline Fernandez CelociaNo ratings yet

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- Efficient 11-person voting system using full and parallel addersDocument4 pagesEfficient 11-person voting system using full and parallel addersRayan syedNo ratings yet

- 271 HW5 SolutionsDocument6 pages271 HW5 Solutionsg1191059No ratings yet

- Application of Boolean Algebra and Discrete Maths ConceptsDocument18 pagesApplication of Boolean Algebra and Discrete Maths Conceptsraneem koutahNo ratings yet

- 20bsc1017 Sukhman Exp 2Document7 pages20bsc1017 Sukhman Exp 2Prabh deepNo ratings yet

- DLD ExamDocument1 pageDLD Examhanzila farukeNo ratings yet

- Combinational Logic CircuitsDocument5 pagesCombinational Logic CircuitsChristian Allan LumakinNo ratings yet

- Digital Logic Circuit Design Experiemnet 8Document8 pagesDigital Logic Circuit Design Experiemnet 8fahadNo ratings yet

- EGEE 448: Digital Systems Design With FPGA Summer 2019Document15 pagesEGEE 448: Digital Systems Design With FPGA Summer 2019vrgohilNo ratings yet

- School of Engineering and Physics EE222 Lab 5Document9 pagesSchool of Engineering and Physics EE222 Lab 5Alvish NaiduNo ratings yet

- Lecture 5 - Spread Spectrum, Demodulation, EqualizerlDocument22 pagesLecture 5 - Spread Spectrum, Demodulation, Equalizerlomairakhtar12345No ratings yet

- Seminar 4 Power TransformersDocument57 pagesSeminar 4 Power Transformersomairakhtar12345No ratings yet

- Lecture 6 - Multiple Access in Wireless CommunicationDocument22 pagesLecture 6 - Multiple Access in Wireless Communicationomairakhtar12345No ratings yet

- Tutorial 5 - Channel Coding, Error Control - MEngDocument3 pagesTutorial 5 - Channel Coding, Error Control - MEngomairakhtar12345No ratings yet

- ENS6146 Project Report TemplateDocument6 pagesENS6146 Project Report Templateomairakhtar12345No ratings yet

- ENS5253 Control Systems Quiz 1Document3 pagesENS5253 Control Systems Quiz 1omairakhtar12345No ratings yet

- Problem 9.22: SolutionDocument1 pageProblem 9.22: Solutionomairakhtar12345No ratings yet

- 8-Element Array Beam Steering to 60° Below BroadsideDocument1 page8-Element Array Beam Steering to 60° Below Broadsideomairakhtar12345No ratings yet

- Problem 9.34: SolutionDocument1 pageProblem 9.34: Solutionomairakhtar12345No ratings yet

- Quality Assurance and Quality ControlDocument17 pagesQuality Assurance and Quality Controltraslie0% (1)

- Tutorial-SOLUTIONS-Feedback Control Systems March2017Document13 pagesTutorial-SOLUTIONS-Feedback Control Systems March2017omairakhtar12345No ratings yet

- Chairman of Pakistan Cotton Ginners AssociationDocument20 pagesChairman of Pakistan Cotton Ginners Associationomairakhtar12345No ratings yet

- 9 15Document2 pages9 15omairakhtar12345No ratings yet

- ENS5253 Chapter-3 Review Questions - Quiz-3Document3 pagesENS5253 Chapter-3 Review Questions - Quiz-3omairakhtar12345No ratings yet

- ENS5253 Control Systems Quiz 1Document3 pagesENS5253 Control Systems Quiz 1omairakhtar12345No ratings yet

- Seminar 1 Electric Power IndustryDocument81 pagesSeminar 1 Electric Power Industryomairakhtar12345No ratings yet

- Resume FormatDocument5 pagesResume Formatomairakhtar12345No ratings yet

- LalanaDocument12 pagesLalanaomairakhtar12345No ratings yet

- Training PresentationDocument80 pagesTraining Presentationomairakhtar12345No ratings yet

- Lecture2 DCNDocument18 pagesLecture2 DCNkartheek32777No ratings yet

- Seminar 1 Electric Power IndustryDocument81 pagesSeminar 1 Electric Power Industryomairakhtar12345No ratings yet

- Write UpewrewrDocument1 pageWrite Upewrewromairakhtar12345No ratings yet

- Solar Cooker SolutionsDocument2 pagesSolar Cooker Solutionsomairakhtar12345No ratings yet

- Solar Cooker CalculationsDocument1 pageSolar Cooker Calculationsomairakhtar12345No ratings yet

- Date: 25-Jun-2014 Fateh Jhang Center Observations For Improvement of Battery Backup TimeDocument2 pagesDate: 25-Jun-2014 Fateh Jhang Center Observations For Improvement of Battery Backup Timeomairakhtar12345No ratings yet

- VLSI Design (MOSFET Structure) : Waqar AhmadDocument46 pagesVLSI Design (MOSFET Structure) : Waqar Ahmadomairakhtar12345No ratings yet

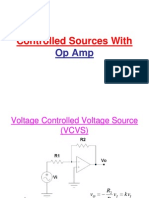

- Topic 3 Controlled SourcesDocument16 pagesTopic 3 Controlled Sourcesomairakhtar12345No ratings yet

- Ecture: Vlsi DDocument44 pagesEcture: Vlsi Domairakhtar12345No ratings yet

- Lecture 3Document79 pagesLecture 3omairakhtar12345No ratings yet

- MCQDocument6 pagesMCQShamara RodrigoNo ratings yet

- SpecimenDocument31 pagesSpecimenSerge DemirdjianNo ratings yet

- 6 Noise and Multiple Attenuation PDFDocument164 pages6 Noise and Multiple Attenuation PDFFelipe CorrêaNo ratings yet

- Ejercicos Mentales Volumen 13Document10 pagesEjercicos Mentales Volumen 13Luis TorresNo ratings yet

- Ee361 Mid2 Sp2021-3Document6 pagesEe361 Mid2 Sp2021-3Seb SebNo ratings yet

- Anees Abdul MFSslidesDocument46 pagesAnees Abdul MFSslidesjoseNo ratings yet

- Assignment 1 - Simple Harmonic MotionDocument2 pagesAssignment 1 - Simple Harmonic MotionDr. Pradeep Kumar SharmaNo ratings yet

- Y V - J MVJ B - J ° - ) : 4.2. The Huron-Vidal (Hvo) ModelDocument8 pagesY V - J MVJ B - J ° - ) : 4.2. The Huron-Vidal (Hvo) ModelBruno Luiz Leite MartinsNo ratings yet

- ΔΣ Modulator with Low power Using Charge- Pump Based Switched-Capacitor IntegratorDocument5 pagesΔΣ Modulator with Low power Using Charge- Pump Based Switched-Capacitor IntegratorIPASJNo ratings yet

- Monthly Reference 5Document22 pagesMonthly Reference 5Nurul AbrarNo ratings yet

- Mongo DBDocument22 pagesMongo DBBalaji Mani100% (1)

- Writing Scientific NotationDocument2 pagesWriting Scientific NotationkolawoleNo ratings yet

- SPUD 604 ManualDocument37 pagesSPUD 604 ManualfbarrazaisaNo ratings yet

- Centrifugal ForceDocument9 pagesCentrifugal ForcecataiceNo ratings yet

- 1ST Unit Test (2023-24)Document1 page1ST Unit Test (2023-24)Ansh ThakurNo ratings yet

- Instructional Module: Republic of The Philippines Nueva Vizcaya State University Bayombong, Nueva VizcayaDocument14 pagesInstructional Module: Republic of The Philippines Nueva Vizcaya State University Bayombong, Nueva VizcayaMary Jane BugarinNo ratings yet

- A Comparison of Subspace Methods For Sylvester Equations: Mathematics InstituteDocument9 pagesA Comparison of Subspace Methods For Sylvester Equations: Mathematics InstituteDurga SivakumarNo ratings yet

- Mastering Sequences & SeriesDocument2 pagesMastering Sequences & SeriesCristina CotraNo ratings yet

- Association Rule MiningDocument50 pagesAssociation Rule MiningbhargaviNo ratings yet

- Transcripts Moi UniversityDocument4 pagesTranscripts Moi UniversityMelanie GaksNo ratings yet

- Tabel Distribuzi Normal Z-Harus 0.5 Dikurangi PDFDocument1 pageTabel Distribuzi Normal Z-Harus 0.5 Dikurangi PDFLisna L. PaduaiNo ratings yet

- Poisson's and Laplace Equations ExplainedDocument19 pagesPoisson's and Laplace Equations ExplainedMnskSaroNo ratings yet

- Mock Test Paper 2013 (Answers)Document84 pagesMock Test Paper 2013 (Answers)Varun GuptaNo ratings yet

- Astrophysics and Mathematics With The Constant V 9.209.Document16 pagesAstrophysics and Mathematics With The Constant V 9.209.Mars PartyNo ratings yet

- Workshop User Guide of GrafcetDocument150 pagesWorkshop User Guide of GrafcetJames HabibNo ratings yet

- Uranian PlanetsDocument12 pagesUranian PlanetsPongwuthNo ratings yet

- Chapter 3. Drag Force and Its CoefficientDocument47 pagesChapter 3. Drag Force and Its Coefficientsmyeganeh100% (1)

- Mathematics Standard 1: NSW Education Standards AuthorityDocument34 pagesMathematics Standard 1: NSW Education Standards AuthorityPoonam SinghNo ratings yet

- Factorials Permutations and Combinations Answer KeyDocument4 pagesFactorials Permutations and Combinations Answer KeyAlrian Jay SampalayNo ratings yet

- Statistical Non Parametric Mapping ManualDocument47 pagesStatistical Non Parametric Mapping ManualKrishna P. MiyapuramNo ratings yet