Professional Documents

Culture Documents

Bob-09579-Isd1900 - Modulo de Voz PDF

Uploaded by

betodias30Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bob-09579-Isd1900 - Modulo de Voz PDF

Uploaded by

betodias30Copyright:

Available Formats

ISD1900

32 ISD1900

33 SINGLE-CHIP, MULTIPLE-MESSAGE

34 VOICE RECORD/PLAYBACK DEVICE

Publication Release Date: Jan 5, 2009

1 Revision 0.51

ISD1900

TABLE OF CONTENTS

1. GENERAL DESCRIPTION ...............................................................................................................................3

2. FEATURES.......................................................................................................................................................3

2.1. Address Mode........................................................................................................................................... 3

2.2. Direct Mode............................................................................................................................................... 4

3. BLOCK DIAGRAM ............................................................................................................................................5

4. PIN CONFIGURATION.....................................................................................................................................6

5. PIN DESCRIPTION ..........................................................................................................................................8

6. FUNCTIONAL DESCRIPTION .......................................................................................................................11

6.1. Address Mode......................................................................................................................................... 11

6.1.1 Record (REC

¯¯¯¯) Operation................................................................................................................. 12

6.1.2 Edge-triggered Playback (PlayE

¯¯¯¯¯) Operation................................................................................... 14

6.1.3 Level-triggered Playback (¯¯¯¯¯)

PlayL Operation................................................................................... 14

6.1.4 Playback (Supersedes Record) Operation...................................................................................... 15

6.1.5 XCLK Feature .................................................................................................................................. 16

6.2. Direct Mode............................................................................................................................................. 16

6.3. Other Operations .................................................................................................................................... 19

6.3.1 Rosc Operation................................................................................................................................ 19

6.3.2 LED Operation ................................................................................................................................. 20

6.3.3 Feed-Through mode Operation....................................................................................................... 20

6.3.4 Power-On Playback Operation........................................................................................................ 20

6.3.5 Automatic Single Message Playback .............................................................................................. 20

6.3.6 Power is interrupted Abruptly .......................................................................................................... 20

7. ABSOLUTE MAXIMUM RATINGS [1]..............................................................................................................21

7.1. Operating Conditions .............................................................................................................................. 21

8. ELECTRICAL CHARACTERISTICS ..............................................................................................................22

8.1. DC Parameters ....................................................................................................................................... 22

8.2. AC Parameters ....................................................................................................................................... 23

9. TYPICAL APPLICATION CIRCUIT ................................................................................................................24

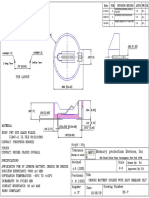

10. PACKAGING...................................................................................................................................................26

10.1. 28-Lead 300-Mil Plastic Small Outline Integrated Circuit (SOIC) ....................................................... 26

11. ORDERING INFORMATION ..........................................................................................................................27

12. VERSION HISTORY.......................................................................................................................................28

Publication Release Date: Jan 5, 2009

2 Revision 0.51

ISD1900

1. GENERAL DESCRIPTION

0

Nuvoton’s ISD1900 ChipCorder® Series is a single-chip multiple-message record/playback device with dual

operating modes and wide operating voltage ranging from 2.4V to 5.5V. The sampling frequency can be

selected from 4 to 12 kHz via an external resistor, which also determines the duration. The device is designed

for mostly standalone applications, and of course, it can be manipulated by a microcontroller, if necessary.

The two operating modes are Address Mode and Direct Mode. While in Address Mode, both record and

playback operations are manipulated according to the start address and end address specified through the start

address and end address pins. In Direct Mode, the device can configure the memory up to as many as eight

similar duration messages, pending upon the fixed message configuration settings. With the record or

playback feature being pre-selected, each message can be randomly accessed via its message control pin.

The device has a selectable differential microphone input with AGC feature or single-ended analog input, AnaIn,

under feed-through mode. The audio output is either a differential Class-D PWM direct-drive or a single-ended

voltage output (AUX out), depending on the derivative selected.

2. FEATURES

1

The ISD1900 is a multiple messages record/playback device with two operational modes: Address Mode and

Direct Mode.

• Supply voltage: 2.4V to 5.5V.

• External resistor, Rosc, selects sampling frequency and duration.

Sampling Frequency 12 kHz 8 kHz 6.4 kHz 5.3 kHz 4 kHz

Rosc 53.3 KΩ 80 KΩ 100 KΩ 120 KΩ 160 KΩ

ISD1916 10.6 sec 16 sec 20 sec 24 sec 32 sec

ISD1932 21.3 sec 32 sec 40 sec 48 sec 64 sec

ISD1964 42.6 sec 64 sec 80 sec 96 sec 128 sec

• Mic+/Mic-: differential microphone inputs.

• AGC: automatic gain control for microphone preamp circuit.

• FT

¯¯: feed-through the AnaIn signal to the speaker outputs while AnaIn is converted from MIC+.

• When both FT¯¯ and recording are active, device will record AnaIn signal into memory with AnaIn signal output

to speaker simultaneously.

• SP+/SP-: Class-D PWM differential speaker drivers or single-ended voltage output, depending on the

derivative selected.

• ¯¯¯¯:

LED LED is on during recording.

• Automatically power down after each operation cycle.

• Playback takes precedence over the recording operation.

y Temperature option: -40°C to +85°C (Industrial)

y Packaging: available in SOIC only

2.1. ADDRESS MODE

12

Publication Release Date: Jan 5, 2009

3 Revision 0.51

ISD1900

• While in Address Mode, flexible message duration is defined by start address and end address.

• Utilize four start address pins (S0, S1, S2 & S3) and four end address pins (E0, E1, E2 & E3) to specify

the message duration.

• ¯¯¯¯:

REC Level-hold or Edge-trigger (toggle on-off) recording from start to end addresses.

• ¯¯¯¯¯:

PlayE Edge-trigger playback from start to end address and stops at EOM marker, if EOM is prior to

end address. Toggle on-off.

• ¯¯¯¯¯:

PlayL Level-hold playback from start to end address. Also, if constantly Low, device will loop

playback from start to end address.

2.2. DIRECT MODE

13

• While Direct Mode is active, utilizing the configuration pins, FMC1, FMC2 & FMC3, to define up to eight

similar duration messages for random access.

• The control pins are: M1¯¯ ~ M8

¯¯ (message activation) and ¯¯/P

R (record or playback selection).

• The record or playback operation is pre-defined by the ¯¯/P

R pin.

• Each message can be randomly accessed via its message control pin (M1 ¯¯ ~ M8

¯¯ ) and the desired

operation is facilitated accordingly.

Publication Release Date: Jan 5, 2009

4 Revision 0.51

ISD1900

3. BLOCK DIAGRAM

2

Rosc Clock Control

SP + /

MIC+ /

Non-Volatile AUX

AnaIn Pre- Antialiasing Smoothing

Amp Multi Level Storage Amp

MIC- / Amp Filter Filter SP - /

Array

NC NC

Automatic

AGC Gain Control Switch

(AGC)

Device & Address Control Power Conditioning

Address Mode: Addr LED FT PlayE PlayL REC S0 S1 S2 VCCA VSSA VCCD VSSD VCCp VSSP1 VSSP2

XCLK S3 E0 E1 E2 E3

Direct Mode: Drct LED FT FMC3 FMC2 FMC1 R/P M1 M2 M3 M4 M5 M6 M7 M8

Figure 3-1 Block Diagram

Publication Release Date: Jan 5, 2009

5 Revision 0.51

ISD1900

4. PIN CONFIGURATION

3

VSSD 1 28 VCCD

S0 / M1 2 27 Addr / Drct

S1 / M2 3 26 FT

S2 / M3 4 25 XCLK / FMC3

S3 / M4 5 24 REC / R/P

PlayL / FMC1 6 23 PlayE / FMC2

E0 / M5 7 22 LED

ISD1900

VSSA 8 21 VCCA

E1 / M6 9 20 Rosc

E2 / M7 10 19 Mic-_NC

E3 / M8 11 18 Mic+_AnaIn

VSSP2 12 17 AGC

SP- 13 16 VSSP1

VCCP 14 15 SP+

Figure 4-1 Pin Configuration

Publication Release Date: Jan 5, 2009

6 Revision 0.51

ISD1900

VSSD 1 28 VCCD VCC VSSD 1 28 VCCD

Addr 2 27 Drct

S0 2 27 M1

S1 3 26 FT M2 3 26 FT

S2 4 25 XCLK M3 4 25 FMC3

S3 5 24 REC M4 5 24 R/P

PlayL 6 23 PlayE FMC1 6 23 FMC2

E0 7 22 LED M5 7 22 LED

ISD1900 ISD1900

VSSA 8 21 VCCA VSSA 8 21 VCCA

E1 9 20 Rosc M6 9 20 Rosc

E2 10 19 Mic-_NC M7 10 19 Mic-_NC

E3 11 18 Mic+_AnaIn M8 11 18 Mic+_AnaIn

VSSP2 12 17 AGC VSSP2 12 17 AGC

SP- 13 16 VSSP1 SP- 13 16 VSSP1

VCCP 14 15 SP+ VCCP 14 15 SP+

Figure 4-2 Pin Configuration – Address Mode Figure 4-3 Pin Configuration – Direct Mode

Publication Release Date: Jan 5, 2009

7 Revision 0.51

ISD1900

5. PIN DESCRIPTION

4

PIN NAME PIN # I/O FUNCTION

VSSD 1 I Digital Ground: Ground path for digital circuits.

S0/M1

¯¯ 2 I

S0[1] : In Address Mode, Start Address Bit 0.

¯¯ : When Direct Mode is active, low active operation on 1st Message.

M1

Internal pull-up & debounce existed.

S1/M2

¯¯ 3 I

S1[1] : In Address Mode, Start Address Bit 1.

¯¯ : When Direct Mode is active, low active operation on 2nd Message.

M2

Internal pull-up & debounce existed.

S2/M3

¯¯ 4 I

S2[1] : In Address Mode, Start Address Bit 2.

¯¯ : When Direct Mode is active, low active operation on 3rd Message.

M3

Internal pull-up & debounce existed.

S3/M4

¯¯ 5 I

S3[1] : In Address Mode, Start Address Bit 3.

¯¯ : When Direct Mode is active, low active operation on 4th Message.

M4

Internal pull-up & debounce existed.

¯¯¯¯¯/FMC1

PlayL 6 I

¯¯¯¯¯:

PlayL In Address Mode, low active input, Level-hold playback start to end

addresses, debounce & internal pull-up existed. Holding ¯¯¯¯¯

PlayL Low

constantly will perform looping playback function from start to end

addresses with insignificant dead time between messages regardless of

sampling frequencies.

FMC1: When Direct Mode is active, FMC1, together with FMC2 & FMC3,

setup various fixed-message configurations.

E0/M5

¯¯ 7 I

E0[1] : In Address Mode, End Address Bit 0.

¯¯ : When Direct Mode is active, low active operation on 5th Message.

M5

Internal pull-up & debounce existed.

VSSA 8 I Analog Ground: Ground path for analog circuits.

E1/M6

¯¯ 9 I

E1[1] : In Address Mode, End Address Bit 1.

¯¯ : When Direct Mode is active, low active operation on 6th Message.

M6

Internal pull-up & debounce existed.

E2/M7

¯¯ 10 I

E2[1] : In Address Mode, End Address Bit 2.

¯¯ : When Direct Mode is active, low active operation on 7th Message.

M7

Internal pull-up & debounce existed.

E3/M8

¯¯ 11 I

E3[1] : In Address Mode, End Address Bit 3.

¯¯ : When Direct Mode is active, low active operation on 8th Message.

M8

Internal pull-up & debounce existed.

VSSP2 12 I Ground: Ground for negative PWM speaker driver.

SP- 13 O SP-: Negative signal of the differential Class-D PWM speaker outputs. This

output, together with the SP+, is used to drive an 8Ω speaker directly.

VCCP 14 I Speaker Power Supply: Power supply for PWM speaker drivers.

Publication Release Date: Jan 5, 2009

8 Revision 0.51

ISD1900

PIN NAME PIN # I/O FUNCTION

SP+ 15 O Depending on the derivative selected, it could be:

SP+: Positive signal of the differential Class-D PWM speaker outputs. This

output, together with the SP-, is used to drive an 8Ω speaker directly.

Or,

AUX out: single-ended voltage output.

VSSP1 16 I Ground: Ground for positive PWM speaker driver.

AGC 17 I Automatic Gain Control (AGC): The AGC adjusts the gain of the

preamplifier dynamically to compensate for the wide range of microphone

input levels. The AGC allows the full range of signals to be recorded with

minimal distortion. The AGC is designed to operate with a nominal

capacitor of 4.7 µF connected to this pin.

Connecting this pin to ground (VSSA) provides maximum gain to the

preamplifier circuitry. Conversely, connecting this pin to the power supply

(VCCA) provides minimum gain to the preamplifier circuitry.

MIC+ / AnaIn 18 I

MIC+: Non-inverting input of the differential microphone signal.

AnaIn: When FT ¯¯ is selected, the MIC+ input is configured to a single-ended

input with 1Vp-p maximum input amplitude and feed-through to the speaker

outputs.

MIC- / NC 19 I MIC-: Inverting input of the differential microphone signal. While FT ¯¯ is

enabled, MIC- pin is disabled and must be floated.

Rosc 20 I Oscillator Resistor: Connect an external resistor from this pin to VSSA to

select the internal sampling frequency.

VCCA 21 I Analog Power Supply: Power supply for analog circuits.

¯¯¯¯

LED 22 O LED output: During recording, this output is Low. Also, ¯¯¯¯LED pulses Low

momentarily at the end of playback.

¯¯¯¯¯/FMC2

PlayE 23 I

¯¯¯¯¯:

PlayE In Address Mode, low active input, edge-trigger playback from start

to end addresses & toggle on-off. Debounce & internal pull-up existed.

FMC2: When Direct Mode is active, FMC2, together with FMC1 & FMC3,

setup various fixed-message configurations.

¯¯¯¯/

REC ¯¯/P

R 24 I

¯¯¯¯:

REC In Address Mode, level-hold (after 1 sec holding) or edge-trigger

(toggle on-off), low active, recording from start to end addresses. Debounce

& internal pull-up existed.

¯¯/P

R ( When Direct Mode is active):

• When ¯¯/P

R is set to Low, level-hold record operation is selected.

When ¯¯/P

R is set to High, edge-trigger & toggle on-off playback operation is

selected.

¯¯¯¯¯/FMC3

XCLK 25 I

External Clock: In Address Mode, low active and level-hold input. As ¯¯¯¯¯

XCLK

activated, Rosc pin accepts external clock input signal, provided resistor at

Rosc must be removed. Connecting this pin to High enables device running

on internal clock via Rosc resistor. If not used, ¯¯¯¯¯

XCLK must be at high level.

When Direct Mode is active, FMC3, together with FMC1 & FMC2, setup

various fixed-message configurations.

FT

¯¯ 26 I Feed-Through: Low active input, Level-hold, debounce & Internal pull-up

required. When FT¯¯ is selected, the MIC+ input is configured to a single-

ended input with 1Vp-p maximum input amplitude and feed-through to the

speaker outputs.

Publication Release Date: Jan 5, 2009

9 Revision 0.51

ISD1900

PIN NAME PIN # I/O FUNCTION

Addr/¯¯¯¯

Drct 27 I

Level-hold input.

Addr: When set to High, the device operates under Address Mode.

Level-hold input.

¯¯¯¯:

Drct When set to Low, the device operates under Direct Mode. The

device reconfigures its pin definitions to fit various fixed-message

configurations utilizing FMC1 , FMC2 & FMC3 pins as below table.

FMC3 FMC2 FMC1 # of fixed messages

0 0 0 1

0 0 1 2

0 1 0 3

0 1 1 4

1 0 0 5

1 0 1 6

1 1 0 7

1 1 1 8

VCCD 28 I Digital Power Supply: Power supply for digital circuits.

Notes: [1] : Address bits S0, S1, S2, S3, E0, E1, E2 & E3 are used to access the memory location.

Publication Release Date: Jan 5, 2009

10 Revision 0.51

ISD1900

6. FUNCTIONAL DESCRIPTION

5

There are two operational modes: Address Mode and Direct Mode. After a new condition is selected on

Addr/¯¯¯¯,

Drct the power must be cycled to enable it.

6.1. ADDRESS MODE

14

The start address pins (S0, S1, S2 & S3) and end address pins (E0, E1, E2 & E3) are used to access the

memory location and they can divide the memory into a maximum of 16 slots. They are defined as

follows:

S3 S2 S1 S0 Row # I1916

( E3 ) ( E2 ) ( E1 ) ( E0 ) Duration [s]

0 0 0 0 0 0

0 0 0 1 8 1.0

0 0 1 0 16 2.0

0 0 1 1 24 3.0

0 1 0 0 32 4.0

0 1 0 1 40 5.0

0 1 1 0 48 6.0

0 1 1 1 56 7.0

1 0 0 0 64 8.0

1 0 0 1 72 9.0

1 0 1 0 80 10.0

1 0 1 1 88 11.0

1 1 0 0 96 12.0

1 1 0 1 104 13.0

1 1 1 0 112 14.0

1 1 1 1 120 15.0

S3 S2 S1 S0 Row # I1932

( E3 ) ( E2 ) ( E1 ) ( E0 ) Duration [s]

0 0 0 0 0 0

0 0 0 1 16 2.0

0 0 1 0 32 4.0

0 0 1 1 48 6.0

0 1 0 0 64 8.0

0 1 0 1 80 10.0

0 1 1 0 96 12.0

0 1 1 1 112 14.0

1 0 0 0 128 16.0

1 0 0 1 144 18.0

1 0 1 0 160 20.0

1 0 1 1 176 22.0

1 1 0 0 192 24.0

1 1 0 1 208 26.0

1 1 1 0 232 28.0

1 1 1 1 240 30.0

Publication Release Date: Jan 5, 2009

11 Revision 0.51

ISD1900

S3 S2 S1 S0 Row # I1964

( E3 ) ( E2 ) ( E1 ) ( E0 ) Duration [s]

0 0 0 0 0 0

0 0 0 1 32 4.0

0 0 1 0 64 8.0

0 0 1 1 96 12.0

0 1 0 0 128 16.0

0 1 0 1 160 20.0

0 1 1 0 192 24.0

0 1 1 1 224 28.0

1 0 0 0 256 32.0

1 0 0 1 288 36.0

1 0 1 0 320 40.0

1 0 1 1 352 44.0

1 1 0 0 384 48.0

1 1 0 1 416 52.0

1 1 1 0 464 56.0

1 1 1 1 480 60.0

Below is an example:

Given sampling rate set to 6.4 kHz, using the ISD1916 to record four messages: three messages of 2.5 seconds

and one message of 12.5 seconds, then the memory can be assigned as follows:

S3, S2, S1, S0 E3, E2, E1, E0

Message 1 (2.5 seconds) 0 0 0 0 0 0 0 1

Message 2 (2.5 seconds) 0 0 1 0 0 0 1 1

Message 3 (2.5 seconds) 0 1 0 0 0 1 0 1

Message 4 (12.5 seconds) 0 1 1 0 1 1 1 1

6.1.1 21 Record (REC

¯¯¯¯) Operation

• Low active input:

o level-hold for level-trigger or

o falling edge for edge-trigger with debounce required.

• For 8kHz sampling frequency, if ¯¯¯¯

REC is held at Low for a period equal to 1 sec or more, then level

recording is activated. However, if ¯¯¯¯ REC is pulsed Low for less than 1 sec, then edge-trigger

recording is initiated.

• For 6.4kHz sampling frequency, if ¯¯¯¯

REC is held at Low for a period equal to 1.25 sec or more, then level

recording is activated. However, if ¯¯¯¯

REC is pulsed Low for less than 1.25 sec, then edge-trigger

recording is initiated.

• Recording begins from the start address to end address and ¯¯¯¯

LED is on.

• Recording ceases whenever:

¯¯¯¯

REC returns to High in level-hold mode or

a subsequent low-pulse appears while in edge-trigger mode or

when end address is reached.

Publication Release Date: Jan 5, 2009

12 Revision 0.51

ISD1900

o Then an EOM marker is written at the end of message. And ¯¯¯¯ LED is off.

o Then the device will automatically power down.

• This pin has an internal pull-up device.

• Once ¯¯¯¯

REC is active, input on FT

¯¯, Addr/¯¯¯¯,

Drct S0, S1, S2, S3, E0, E1, E2 or E3 is illegal.

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold

REC

TDeb

LED

TStop1

TErs

Mic+/-

or AnaIn

End Address

Figure 6-1 Record–Level (REC

¯¯¯¯) function till end address

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold TASet TAHold

REC Start Stop Start

TDeb TDeb TSettle1 TDeb

LED

TStop1

Mic+/- TErs TErs

or AnaIn

End Address

Figure 6-2 Record–Level (¯¯¯¯

REC ) function with start and stop actions

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold TASet TAHold

REC Start Start

Stop

TDeb TDeb TSettle1 TDeb

LED

TStop1

Mic+/- TErs TErs

or AnaIn

End Address

Figure 6-3 Record–Edge (¯¯¯¯

REC ) function with on-off

Publication Release Date: Jan 5, 2009

13 Revision 0.51

ISD1900

6.1.2 22 Edge-triggered Playback (PlayE

¯¯¯¯¯) Operation

• Low active input, edge-trigger, toggle on-off, debounce required.

• Playback begins from the start address to end address or EOM, whichever occurrs first.

• At the end of message, ¯¯¯¯

LED pulses Low momentarily.

o Then device will automatically power down.

• During playback, a subsequent trigger terminates the playback operation. If EOM marker is not encountered,

then ¯¯¯¯

LED will not pulses Low momentarily.

• This pin has an internal pull-up device.

• Once ¯¯¯¯¯

PlayE is active, input on ¯¯¯¯¯,

PlayL ¯¯¯¯,

REC FT ¯¯, Addr/¯¯¯¯,

Drct S0, S1, S2, S3, E0, E1, E2 or E3 is

banned.

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold TASet TAHold

PlayE Start Start

Stop TEOM

TDeb TDeb TSettle2 TDeb

LED

End of

Sp+ Message

Sp-

Figure 6-4 Playback–Edge (¯¯¯¯¯

PlayE) function

6.1.3 23 Level-triggered Playback (PlayL

¯¯¯¯¯) Operation

• Low active input, Level-hold, debounce required.

• Once active, playback begins from the start address and stops whenever ¯¯¯¯¯

PlayL returns to High.

When an EOM is encountered, ¯¯¯¯ LED pulses Low momentarily.

o Then device will automatically power down.

• This pin has an internal pull-up device.

• Once ¯¯¯¯¯

PlayL is active, input on ¯¯¯¯¯,

PlayE ¯¯¯¯,

REC FT¯¯, Addr/¯¯¯¯,

Drct S0, S1, S2, S3, E0, E1, E2 or E3 is

prohibited.

Publication Release Date: Jan 5, 2009

14 Revision 0.51

ISD1900

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold TASet TAHold

PlayL Start Stop Start

TEOM

TDeb TDeb TSettle2 TDeb

LED

Part of

Message End of

Message

Sp+

Sp-

Figure 6-5 Playback–Level (¯¯¯¯¯

PlayL ) function

• Holding ¯¯¯¯¯

PlayL Low constantly will perform looping playback function, without power down, from start

address to end address.

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold

PlayL

TDeb TEOM TEOM

LED

Sp+

Sp-

Figure 6-6 Looping playback function via ¯¯¯¯¯

PlayL

6.1.4 24 Playback (Supersedes Record) Operation

• Playback takes precedence over the Recording operation.

• If either ¯¯¯¯¯

PlayE or ¯¯¯¯¯

PlayL is activated during a recording cycle, the recording immediately ceases with

an EOM marker attached, and without power down, playback of the just-recorded message performs

accordingly. Then device powers down.

Publication Release Date: Jan 5, 2009

15 Revision 0.51

ISD1900

Addr/Drct

<S3:S0>

<E3:E0>

TASet TAHold

REC

TEOM

TDeb

LED

Mic+/- TErs

or AnaIn

PlayE TSettle1 TSettle3

TDeb

SP+

SP-

Figure 6-7 An example of Playback supersedes Record

6.1.5 25 XCLK Feature

• When precision sampling frequency is required, external clock mode can be activated by setting ¯¯¯¯¯

XCLK

to Low. Under such condition, the resistor at Rosc pin must be removed and the external clock signal

must be applied to the Rosc pin. These conditions must be satisfied prior to any operations.

• However, when internal clock is used, ¯¯¯¯¯

XCLK must be linked to High.

• The external clock frequencies required for various sampling frequencies are listed in below table.

Sampling Freq [kHz] 12 8 6.4 5.3 4

¯¯¯¯¯

XCLK [MHz] 3.072 2.048 1.638 1.356 1.024

6.2. DIRECT MODE

15

• The Direct Mode is selected by the ¯¯¯¯

Drct pin. Once chosen, the supply voltage must be reset to allow

the device to construct itself to the appropriate configuration by re-defining the function on the related

control pins. Also, the mode change is only allowed while the device is in power down state and is

inhibited when an operation is in progress.

• Once Direct Mode is activated, FMC1, FMC2 & FMC3 are utilized to select various (1 to 8) fixed

message configurations [1]. Pending upon the arrangement on FMC1, FMC2 & FMC3, each divided

message has approximate equal length of duration, which is related to the number of rows assigned as

in tables below.

• The record or playback operation is pre-defined by the ¯¯/P

R pin. Setting this pin to Low allows record

operation while setting it to High enables playback operation.

• Each message can be randomly accessed via its message control pin (M1 ¯¯ ~ M8¯¯ ) and the desired

operations are facilitated accordingly. Non-configured pins are automatically disabled and must be

floated.

Publication Release Date: Jan 5, 2009

16 Revision 0.51

ISD1900

[1]

Notes: : Number of fixed message arrangement with respect to FMC1, FMC2 & FMC3.

FMC3 FMC2 FMC1 # of fixed messages [1]

0 0 0 1

0 0 1 2

0 1 0 3

0 1 1 4

1 0 0 5

1 0 1 6

1 1 0 7

1 1 1 8

[2]

: Number of memory row arrangement with respect to different number of fixed messages

for ISD1916 (128 Rows). The non-configured Message control pins (Mx) will be disabled.

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 128

2 64 64

3 44 42 42

4 32 32 32 32

5 26 26 26 26 24

6 23 21 21 21 21 21

7 20 18 18 18 18 18 18

8 16 16 16 16 16 16 16 16

for ISD1932 (256 Rows)

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 256

2 128 128

3 86 85 85

4 64 64 64 64

5 52 51 51 51 51

6 43 43 43 43 42 42

7 37 37 37 37 36 36 36

8 32 32 32 32 32 32 32 32

for ISD1964 (512 Rows)

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 512

2 256 256

3 172 170 170

4 128 128 128 128

5 103 103 102 102 102

6 86 86 85 85 85 85

7 74 73 73 73 73 73 73

8 64 64 64 64 64 64 64 64

Publication Release Date: Jan 5, 2009

17 Revision 0.51

ISD1900

[3]

: The durations for various fixed message configurations on I1916 device at 8 kHz

sampling frequency are shown in below table.

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 16

2 8 8

3 5.5 5.25 5.25

4 4.0 4.0 4.0 4.0

5 3.25 3.25 3.25 3.25 3.0

6 2.875 2.625 2.625 2.625 2.625 2.625

7 2.50 2.25 2.25 2.25 2.25 2.25 2.25

8 2.0 2.0 2.0 2.0 2.0 2.0 2.0 2.0

for ISD1932 (256 Rows)

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 32

2 16 16

3 10.62 10.62

10.75 5 5

4 8.0 8.0 8.0 8.0

5 6.5 6.375 6.375 6.375 6.375

6 5.375 5.375 5.375 5.375 5.25 5.25

7 4.625 4.625 4.625 4.625 4.5 4.5 4.5

8 4.0 4.0 4.0 4.0 4.0 4.0 4.0 4.0

for ISD1964 (512 Rows)

# of

Msg M1 M2 M3 M4 M5 M6 M7 M8

1 64

2 32 32

3 21.5 21.25 21.25

4 16.0 16.0 16.0 16.0

5 12.87 12.87

5 5 12.75 12.75 12.75

6 10.62 10.62 10.62 10.62

10.75 10.75 5 5 5 5

7 9.25 9.125 9.125 9.125 9.125 9.125 9.125

8 8.0 8.0 8.0 8.0 8.0 8.0 8.0 8.0

Publication Release Date: Jan 5, 2009

18 Revision 0.51

ISD1900

35 Example of four Fixed-Message Configuration:

Addr/Drct

FM3

FM2

FM1

TFSet

R/P

Stop

Start

M1 ~ M4 Start TSettle1

TDeb TDeb

LED TDeb TStop1

End of Duration

TErs TErs

Mic+/-

or AnaIn

Figure 6-8 Record Operation under FMC mode

Addr/Drct

FM3

FM2

FM1

R/P TFSet

Start Stop Start

M1 ~ M4 TEOM

LED

TDeb TDeb TSettle2 TDeb

End of Message

Sp+

Sp-

Figure 6-9 Playback Operation under FMC mode

6.3. OTHER OPERATIONS

16

6.3.1 26 Rosc Operation

• When the ROSC varies from 53.3 KΩ to 160 KΩ, the sampling frequency changes from 12 to 4 kHz

accordingly.

• When ROSC resistor value is changed during playback, the tone of a recorded message will alter either

faster or slower.

• If the ground side of ROSC resistor is floated or tied to VCC, then the current operation will be freezed.

• The operation will resume when the resistor is connected back to ground.

Publication Release Date: Jan 5, 2009

19 Revision 0.51

ISD1900

6.3.2 27 LED Operation

• ¯¯¯¯

LED turns on during recording. Also, ¯¯¯¯LED pulses Low at the end of message. The Low period

must be sufficiently greater than debounce time.

6.3.3 28 Feed-Through mode Operation

• As FT

¯¯ is held Low, the Mic+ pin will be reconfigured as AnaIn input, and the AnaIn signal will be

transmitted to the speaker outputs. Under this mode, Mic- pin is not used (must be floated).

• After FT

¯¯ is enabled, If ¯¯¯¯

REC is triggered, then AnaIn signal will be recorded into memory while the

Feed-Through path remains on.

• If FT

¯¯ is already enabled, activating either ¯¯¯¯¯

PlayE or ¯¯¯¯¯

PlayL will first disable the FT path and then play the

recorded message. Once playback completes, FT path will be resumed.

• During an operation, activating the FT

¯¯ pin is not allowed.

6.3.4 29 Power-On Playback Operation

• If ¯¯¯¯¯

PlayE is kept at Low during power turns on, the device plays message once, then powers down.

• If ¯¯¯¯¯

PlayL is held at Low during power turns on and constantly maintained at Low, the device will play

the message repeatedly, with insignificant dead time between messages regardless of sampling

frequencies. This status will sustain unless power is turned off or ¯¯¯¯¯

PlayL somehow returns to High.

6.3.5 30 Automatic Single Message Playback

• If ¯¯¯¯

LED is connected to ¯¯¯¯¯,

PlayE once ¯¯¯¯¯

PlayE is triggered, the device plays message repeatedly without

power down between the looping playback. However, if ¯¯¯¯¯ PlayE is triggered again during playback,

then playback will stop.

6.3.6 31 Power is interrupted Abruptly

• During the device is in operation, it is strongly recommended that the supply power cannot be

interrupted. Otherwise, it may cause the device to become malfunctioning.

Publication Release Date: Jan 5, 2009

20 Revision 0.51

ISD1900

7. ABSOLUTE MAXIMUM RATINGS [1]

6

ABSOLUTE MAXIMUM RATINGS

CONDITION VALUE

Junction temperature 150°C

Storage temperature range -65°C to +150°C

Voltage applied to any pins (VSS – 0.3V) to (VCC + 0.3V)

Voltage applied to Input pins (current limited to +/-20 mA) (VSS – 1.0V) to (VCC + 1.0V)

Voltage applied to output pins (current limited to +/-20 mA) (VSS – 1.0V) to (VCC + 1.0V)

VCC – VSS -0.3V to +7.0V

[1]

Stresses above those listed may cause permanent damage to the device. Exposure to the absolute

maximum ratings may affect device reliability and performance. Functional operation is not implied at these

conditions.

7.1. OPERATING CONDITIONS

17

OPERATING CONDITIONS

CONDITION VALUE

Operating temperature range 0°C to +50°C

[1]

Operating voltage (VCC) +2.4V to +5.5V

[2]

Ground voltage (VSS) 0V

[1]

VCC = VCCA = VCCD

[2]

VSS = VSSA = VSSD

Publication Release Date: Jan 5, 2009

21 Revision 0.51

ISD1900

8. ELECTRICAL CHARACTERISTICS

7

8.1. DC PARAMETERS

18

PARAMETER SYMBOL MIN[2] TYP[1] MAX[2] UNITS CONDITIONS

Input Low Voltage VIL 0.3xVcc V

Input High Voltage VIH 0.7xVcc V

Output Low Voltage VOL 0.3xVcc V IOL = 4.0 mA[3]

Output High Voltage VOH 0.7xVcc V IOH = -1.6 mA[3]

[4] [5]

Standby Current ISTBY 1 10 µA

Record Current IREC 20 30 mA VCC = 5.5V [4] [5]

Playback Current IPLAY 20 30 mA VCC = 5.5V, no load [4] [5]

Pull-up device for ¯¯¯¯

REC , ¯¯¯¯¯

PlayE , RPU1 600 kΩ

¯¯¯¯¯

PlayL , FT

¯¯ & M1 ¯¯ ~ M8

¯¯ pins

MIC+ Input Resistance RMICP 18 KΩ

MIC- Input Resistance RMICN 18 KΩ

AnaIn Input Resistance RANAIN 42 KΩ

MIC Differential Input VIN1 15 300 mV Peak-to-peak

AnaIn Input VIN2 1 V Peak-to-peak

Gain from MIC to SP+/- AMSP 6 40 dB VIN = 15~300 mVp-p,

AGC = 4.7 µF,

VCC = 2.4V~5.5V

Gain from AnaIn to SP+/- AASP 0 dB VCC = 2.4V~5.5V

Output Load Impedance RSPK 8 Ω Speaker load

Speaker Output Power Pout 670 mW VDD = 5.5 V 1Vp-p,

313 mW VDD = 4.4 V 1 kHz sine

wave at

117 mW VDD= 3 V

AnaIn. RSPK

49 mW VDD= 2.4 V =8Ω

Speaker Output Voltage VOUT1 VDD V RSPK = 8Ω Speaker,

Typical buzzer

Total Harmonic Distortion THD 1 % 15 mV p-p 1 kHz sine

wave, Cmessage

weighted

Notes: [1] Typical values @ VCC = 5.5V, TA = 25° and sampling frequency (Fs) at 8 kHz, unless stated.

[2]

Not all specifications are 100 percent tested. All Min/Max limits are guaranteed by Nuvoton via design, electrical testing

and/or characterization.

[3]

LED output during recording.

[4]

VCCA, VCCD and VCCP are connected together. Also, VSSA, VSSD, VSSP1 and VSSP2 are linked together.

[5]

All required control pins must be at appropriate status. External components are biased under a separated power

supply.

Publication Release Date: Jan 5, 2009

22 Revision 0.51

ISD1900

8.2. AC PARAMETERS

19

CHARACTERISTIC [1] SYMBOL MIN[2] TYP MAX[2] UNIT CONDITIONS

S

[3]

Sampling Frequency Fs 4 12 kHz

[3]

Record / Playback TREC / TPLAY 10.6 32 sec

Duration (ISD1916)

[3]

Record / Playback TREC / TPLAY 21.3 64 sec

Duration (ISD1932)

[3]

Record / Playback TREC / TPLAY 42.6 128 sec

Duration (ISD1964)

[3] [4]

Debounce Time TDeb 225k/Fs msec

Address Setup Time TASet 30 nsec

[3] [4]

Address Hold Time TAhold 225k/Fs msec

MRN = message row #

Erase Time TErs 1.25MR msec

N

FMC Setup Time TFset 30 nsec

[3] [4]

Record Settle Time TSettle1 32k/Fs msec

[3] [4]

Play Settle Time TSettle2 256k/F msec

s

[3] [4]

Delay from Record to Play TSettle3 128k/F msec

s

Record Stop Time TStop1 30 nsec

[3] [4]

LED Pulse Low Time TEOM 256k/F msec

s

Notes:

[1]

Conditions are VCC = 5.5V, TA = 25°C and sampling frequency (FS) at 8kHz, unless specified.

[2]

Not all specifications are 100 percent tested. All Min/Max limits are guaranteed by Nuvoton via design, electrical

testing and/or characterization.

[3]

When different FS is applied, the value will change accordingly. Also, stability of internal oscillator may vary as much

as +10% over the operating temperature and voltage ranges.

[4]

k = 1000.

Publication Release Date: Jan 5, 2009

23 Revision 0.51

ISD1900

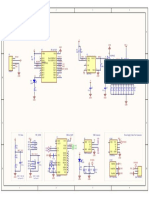

9. TYPICAL APPLICATION CIRCUIT

8

The following typical application examples on ISD1900 series are for references only. They make no

representation or warranty that such applications shall be suitable for the use specified. It’s customer’s

obligation to verify the design in its own system for the functionalities, voice quality, current consumption,

and etc.

In addition, the below notes apply to the following application examples:

• The suggested values are for references only. Depending on system requirements, they can be adjusted

for functionalities, voice quality and degree of performance.

It is important to have a separate path for each ground and power back to the related terminals to minimize

the noise. Besides, the power supplies should be decoupled as close to the device as possible.

Also, it is crucial to follow good audio design practices in layout and power supply decoupling. See

recommendations in Application Notes from our websites.

Example #1: Operations via start and end address under Address Mode.

REC Addr

D1

1 KΩ

PLAYE LED Vcc Gnd

PLAYL XCLK VCCA

VCCD

S3 VCCD VCCP

S2 VCCD

S1 0.1μ F 10 μ F*

To switches or VSSD

S0

address I/Os E3 VCCA

VCC VCCA

E2 ISD1900 0.1μ F 10 μ F*

4.7 k Ω∗ E1 VSSA

E0 VCCP

4.7μ F* VCCP

4.7 k Ω∗ 0.1μ F

FT VSSP1 10 μ F*

0.1 μ F* 10 μ F*

Mic+_AnaIn 0.1μ F

0.1 μ F* VSSP2

Mic-

4.7 μ F*

4.7 k Ω∗

AGC SP+/AUX Speaker

Rosc*

Rosc SP-/NC

Publication Release Date: Jan 5, 2009

24 Revision 0.51

ISD1900

Example #2: Fixed Message Configuration Operations under Direct Mode.

VCC

D1

1 kΩ

Vcc Gnd

R/P LED

M1 Drct VCCA

VCCD

M2 FMC3 VCCP

M3 FMC2

M4 FMC1 VCCD

M5 VCCD

0.1μ F 10 μ F*

M6

VSSD

VCC M7

VCCA

M8 ISD1900 VCCA

4.7 k Ω∗

0.1μ F 10 μ F

VSSA

4.7μ F*

4.7 k Ω∗ FT VCCP

VCCP

0.1 μ F* 0.1μ F

Mic+_AnaIn 10 μ F*

VSSP1

0.1 μ F* 10 μ F*

Mic- 0.1μ F

4.7 μ F* VSSP2

4.7 kΩ∗ AGC

Rosc* SP+/AUX Speaker

Rosc

SP-/NC

36 Good Audio Design Practices

Nuvoton’s ChipCorder are very high-quality single-chip voice recording and playback devices. To ensure the

highest quality voice reproduction, it is important that good audio design practices on layout and power supply

decoupling are followed. See Application Information links below for details.

Good Audio Design Practices

http://www.Nuvoton-usa.com/products/isd_products/chipcorder/applicationinfo/apin11.pdf

Single-Chip Board Layout Diagrams

http://www.Nuvoton-usa.com/products/isd_products/chipcorder/applicationinfo/apin12.pdf

It is strongly recommended that before any design or layout project starts, the designer should contact Nuvoton

Sales Rep for the most update technical information and layout advice.

Publication Release Date: Jan 5, 2009

25 Revision 0.51

ISD1900

10. PACKAGING

9

10.1. 20 28-LEAD 300-MIL PLASTIC SMALL OUTLINE INTEGRATED CIRCUIT (SOIC)

28 27 26 25 24 23 22 21 20 19 18 17 16 15

1 2 3 4 5 6 7 8 9 10 11 12 13 14

A

G

C

B

D

E F H

Plastic Small Outline Integrated Circuit (SOIC) Dimensions

INCHES MILLIMETERS

Min Nom Max Min Nom Max

A 0.701 0.706 0.711 17.81 17.93 18.06

B 0.097 0.101 0.104 2.46 2.56 2.64

C 0.292 0.296 0.299 7.42 7.52 7.59

D 0.005 0.009 0.0115 0.127 0.22 0.29

E 0.014 0.016 0.019 0.35 0.41 0.48

F 0.050 1.27

G 0.400 0.406 0.410 10.16 10.31 10.41

H 0.024 0.032 0.040 0.61 0.81 1.02

Note: Lead coplanarity to be within 0.004 inches.

Publication Release Date: Jan 5, 2009

26 Revision 0.51

ISD1900

11. ORDERING INFORMATION

10

Product Number Descriptor Key

I19 xxxxxxxx

Product Name: Output Type:

I = ISD Blank = PWM

01 = AUX out

Product Series:

Tape & Reel:

19 = 1900

Blank = None

Duration: R = Tape & Reel

16 : 10.6 – 32 secs

32 : 21.3 – 64 secs Temperature:

I = Industrial (-40°C to +85°C)

64 : 42.6 – 128 secs

Package Type:

S = Small Outline Integrated Circuit

(SOIC) Package Lead-Free:

Y = Lead-Free

When ordering ISD1900 devices, please refer to the above ordering scheme. Contact the local Nuvoton Sales

Representatives for any questions and the availability.

For the latest product information, please contact the Nuvoton Sales/Rep or access

Nuvoton’s worldwide web site at http://www.Nuvoton-usa.com

Publication Release Date: Jan 5, 2009

27 Revision 0.51

ISD1900

12. VERSION HISTORY

11

VERSION DATE DESCRIPTION

0 Aug 11, 2007 Initial revision

0.1 Oct 10, 2007 Update block diagram

0.2 Oct 16, 2007 Update description

0.3 July 23, 2008 Generalize for different derivatives.

0.4 Aug 15, 2008 Update timing and application diagrams.

0.41 Aug 21, 2008 Add description of AGC.

0.51 Jan 5, 2009 Rename Norm/Mode

¯¯¯¯ to Addr/¯¯¯¯.

Drct

Publication Release Date: Jan 5, 2009

28 Revision 0.51

ISD1900

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment

intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation

instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or

sustain life. Furthermore, Nuvoton products are not intended for applications wherein failure of Nuvoton products could

result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully

indemnify Nuvoton for any damages resulting from such improper use or sales.

The contents of this document are provided only as a guide for the applications of Nuvoton products. Nuvoton makes no

representation or warranties with respect to the accuracy or completeness of the contents of this publication and

reserves the right to discontinue or make changes to specifications and product descriptions at any time without notice.

No license, whether express or implied, to any intellectual property or other right of Nuvoton or others is granted by this

publication. Except as set forth in Nuvoton's Standard Terms and Conditions of Sale, Nuvoton assumes no liability

whatsoever and disclaims any express or implied warranty of merchantability, fitness for a particular purpose or

infringement of any Intellectual property.

The contents of this document are provided “AS IS”, and Nuvoton assumes no liability whatsoever and disclaims any

express or implied warranty of merchantability, fitness for a particular purpose or infringement of any Intellectual

property. In no event, shall Nuvoton be liable for any damages whatsoever (including, without limitation, damages for

loss of profits, business interruption, loss of information) arising out of the use of or inability to use the contents of this

documents, even if Nuvoton has been advised of the possibility of such damages.

Application examples and alternative uses of any integrated circuit contained in this publication are for illustration only

and Nuvoton makes no representation or warranty that such applications shall be suitable for the use specified.

The 100-year retention and 100K record cycle projections are based upon accelerated reliability tests, as published in

the Nuvoton Reliability Report, and are neither warranted nor guaranteed by Nuvoton. This product incorporates

SuperFlash®.

Information contained in this ISD® ChipCorder® datasheet supersedes all data for the ISD ChipCorder products

published by ISD® prior to August, 1998.

This datasheet and any future addendum to this datasheet is(are) the complete and controlling ISD® ChipCorder®

product specifications. In the event any inconsistencies exist between the information in this and other product

documentation, or in the event that other product documentation contains information in addition to the information in

this, the information contained herein supersedes and governs such other information in its entirety. This datasheet is

subject to change without notice.

Copyright© 2005, Nuvoton Electronics Corporation. All rights reserved. ChipCorder® and ISD® are trademarks of

Nuvoton Electronics Corporation. SuperFlash® is the trademark of Silicon Storage Technology, Inc. All other trademarks

are properties of their respective owners.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

Publication Release Date: Jan 5, 2009

29 Revision 0.51

You might also like

- Isd4004 + Pic16f877aDocument38 pagesIsd4004 + Pic16f877aSteven Howard100% (1)

- 1:1 Digital Interface Transceiver With PLL: Description FeaturesDocument66 pages1:1 Digital Interface Transceiver With PLL: Description FeaturesAENo ratings yet

- Ds Isd1700 Datasheet en Rev2.3Document26 pagesDs Isd1700 Datasheet en Rev2.3faujohnNo ratings yet

- STA321MPL1: Scalable Digital Microphone ProcessorDocument80 pagesSTA321MPL1: Scalable Digital Microphone ProcessorUday KrishnaNo ratings yet

- Yaesu FT-1900R Operating ManualDocument90 pagesYaesu FT-1900R Operating ManualpaknuxNo ratings yet

- BG25Q40A Datasheet PDFDocument62 pagesBG25Q40A Datasheet PDFMircea HarjauNo ratings yet

- Service Manual: ModelDocument44 pagesService Manual: Modelsupertiger15No ratings yet

- DSR 9500/9510 Digital Satellite Receiver User ManualDocument35 pagesDSR 9500/9510 Digital Satellite Receiver User Manualanon_712132859No ratings yet

- ISD4004 12MEIR Winbond PDFDocument28 pagesISD4004 12MEIR Winbond PDFFredrickNo ratings yet

- Sony Str-k685 (ET)Document52 pagesSony Str-k685 (ET)TanzellaNo ratings yet

- Fluke PM3380B Reference ManualDocument133 pagesFluke PM3380B Reference ManualDRF254No ratings yet

- Sony MZ-B100 Service ManualDocument52 pagesSony MZ-B100 Service Manualbenjie_cobillaNo ratings yet

- Ion M 7P7PDocument3 pagesIon M 7P7Pjd_mccloskeyNo ratings yet

- WTV020 SD ManualDocument26 pagesWTV020 SD Manualfcuenca_acunaNo ratings yet

- Icom IC-706 Operators ManualDocument60 pagesIcom IC-706 Operators ManualpetecadmusNo ratings yet

- TrademarksDocument39 pagesTrademarksjokot42No ratings yet

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesDocument84 pagesMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesAntonioNo ratings yet

- AKG - UM - Perception 420Document28 pagesAKG - UM - Perception 420Jorge O. RamosNo ratings yet

- TP 02i User's ManualDocument68 pagesTP 02i User's ManualVi JäìNo ratings yet

- ISD25120PDocument0 pagesISD25120PParrandero LaraNo ratings yet

- Rev 2 STA1052: DSP/MCU System For CD-DA, CD-CA, CD-ROM PlayerDocument15 pagesRev 2 STA1052: DSP/MCU System For CD-DA, CD-CA, CD-ROM PlayerLeoNo ratings yet

- Coolmay MX2N PLC Programming ManualDocument32 pagesCoolmay MX2N PLC Programming ManualAbel G AbelNo ratings yet

- Teac Ad-600 PDFDocument50 pagesTeac Ad-600 PDFAnonymous Pr8IgKeNo ratings yet

- FT 90rDocument64 pagesFT 90rGuinness88DrinkerNo ratings yet

- HCD N455Document72 pagesHCD N455Rodrigo Cieza0% (1)

- Anritsu S332C Maintenaince ManualDocument28 pagesAnritsu S332C Maintenaince Manualcarlosf_6No ratings yet

- ISD1700A Series: AdvancedDocument31 pagesISD1700A Series: Advancedhba_aymen2537No ratings yet

- D1 SKM SpecSheet EnglishDocument2 pagesD1 SKM SpecSheet EnglishgomesmediaNo ratings yet

- Wireless Components: 7 X 5 Video Matrix Switch TDA 6920 Version 1.0Document28 pagesWireless Components: 7 X 5 Video Matrix Switch TDA 6920 Version 1.0MPIMLACNo ratings yet

- GRAF-SYTECO. Manual. AT1-series. Document - H114A2. Published - June SYsteme TEchnischer CommunicationDocument33 pagesGRAF-SYTECO. Manual. AT1-series. Document - H114A2. Published - June SYsteme TEchnischer CommunicationАнтон Коннов0% (1)

- STA309A: Multi-Channel Digital Audio Processor With DDX®Document67 pagesSTA309A: Multi-Channel Digital Audio Processor With DDX®ListenNo ratings yet

- Yaesu Ft250 Manual eDocument44 pagesYaesu Ft250 Manual eMatheus Delamare100% (1)

- CM6327A Datasheet v2.0Document25 pagesCM6327A Datasheet v2.0mircammNo ratings yet

- User'S Manual: WWW - Zemicusa.infoDocument42 pagesUser'S Manual: WWW - Zemicusa.infoSergio ValadezNo ratings yet

- M24C16-W M24C16-R M24C16-F: 16-Kbit Serial I C Bus EEPROMDocument42 pagesM24C16-W M24C16-R M24C16-F: 16-Kbit Serial I C Bus EEPROMKhalil AwawdaNo ratings yet

- 1M/512K SPI NOR Flash Memory Chip Features and SpecificationsDocument46 pages1M/512K SPI NOR Flash Memory Chip Features and Specificationsmirage0706No ratings yet

- Gemini XG 3001 Operation Manual 8Document8 pagesGemini XG 3001 Operation Manual 8michael de la rosaNo ratings yet

- VV5411 & VV6411: Mono and Colour Digital Video CMOS Image SensorsDocument113 pagesVV5411 & VV6411: Mono and Colour Digital Video CMOS Image Sensorsmunche_wowcoreNo ratings yet

- Programmatore Digitale Digital Programmed / Programmeur Digital / DigitalprogrammerDocument19 pagesProgrammatore Digitale Digital Programmed / Programmeur Digital / DigitalprogrammerSting EyesNo ratings yet

- Lis2Dh: MEMS Digital Output Motion Sensor: Ultra Low-Power High Performance 3-Axis "Femto" AccelerometerDocument49 pagesLis2Dh: MEMS Digital Output Motion Sensor: Ultra Low-Power High Performance 3-Axis "Femto" AccelerometerRITESH PatelNo ratings yet

- STA309A: Multi-Channel Digital Audio Processor With DDXDocument67 pagesSTA309A: Multi-Channel Digital Audio Processor With DDXGuilherme De Faria MiguelNo ratings yet

- Mb25 Service ManualDocument78 pagesMb25 Service Manualfox7878No ratings yet

- F70 Service ManualDocument42 pagesF70 Service ManualReegen GuiseNo ratings yet

- BK1086-88 Datasheet v1.0Document30 pagesBK1086-88 Datasheet v1.0BradMorseNo ratings yet

- Electronic Emission Notices: Federal Communications Commission (FCC) StatementDocument16 pagesElectronic Emission Notices: Federal Communications Commission (FCC) StatementfostechNo ratings yet

- Ie BusDocument92 pagesIe BusMino MaraNo ratings yet

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesDocument81 pagesMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesalfredosnNo ratings yet

- PCpartner MVP3BS7p954 ManualDocument20 pagesPCpartner MVP3BS7p954 ManualMarc Homs100% (1)

- Sta 339 BwsDocument79 pagesSta 339 Bwsnahdson2No ratings yet

- SID-2CM-S Automatic Synchronizer Configuration and ConnectionsDocument26 pagesSID-2CM-S Automatic Synchronizer Configuration and ConnectionsSuresh Chandra Padhy100% (1)

- LS07 Chassis Service ManualDocument33 pagesLS07 Chassis Service ManualnaughtybigboyNo ratings yet

- PCM 7040Document91 pagesPCM 7040Christophe MorinNo ratings yet

- M24sr64-Ymn6t 2 PDFDocument87 pagesM24sr64-Ymn6t 2 PDFcarlos rodriguezNo ratings yet

- Hitachi 32hb4t62 32290dlbn Chassis 17mb110 17ips62-R4 SMDocument85 pagesHitachi 32hb4t62 32290dlbn Chassis 17mb110 17ips62-R4 SMPredrag NemcicNo ratings yet

- ST92F124/ST92F150/ST92F250Document429 pagesST92F124/ST92F150/ST92F250Daniel Norberto DemariaNo ratings yet

- Ft90r ManualDocument64 pagesFt90r ManualChris GillespieNo ratings yet

- ICANTEK MyDVR1640Document52 pagesICANTEK MyDVR1640TecnoSmart100% (1)

- M24C01/02-W M24C01/02-R M24C02-F: 1-Kbit and 2-Kbit Serial I C Bus EepromsDocument42 pagesM24C01/02-W M24C01/02-R M24C02-F: 1-Kbit and 2-Kbit Serial I C Bus EepromsxinwubianNo ratings yet

- A1324 5 6 DatasheetDocument12 pagesA1324 5 6 DatasheetJuan Pablo Merck SifontesNo ratings yet

- Ah49e 1317872Document11 pagesAh49e 1317872betodias30No ratings yet

- BS-7-Suporte CR2032Document1 pageBS-7-Suporte CR2032betodias30No ratings yet

- NOUVEAucPIC PDFDocument684 pagesNOUVEAucPIC PDFbabiloneNo ratings yet

- USB power supply monitoring and control systemDocument1 pageUSB power supply monitoring and control systembetodias30No ratings yet

- DECODING HT6P20 WITH Attachinterrupt Arduino Forum PDFDocument6 pagesDECODING HT6P20 WITH Attachinterrupt Arduino Forum PDFbetodias30No ratings yet

- An826 - Sold Pads Vishay RecommendationDocument40 pagesAn826 - Sold Pads Vishay Recommendationbetodias30No ratings yet

- DataSheet SKN 20 02234940Document3 pagesDataSheet SKN 20 02234940Engenheiro TeslandoNo ratings yet

- Infineon AN2016 10 CIPOS Mini Technical Description An v02 41 enDocument45 pagesInfineon AN2016 10 CIPOS Mini Technical Description An v02 41 enbetodias30No ratings yet

- VSE-DB0069-1009 NTC Thermistors - INTERACTIVE PDFDocument141 pagesVSE-DB0069-1009 NTC Thermistors - INTERACTIVE PDFbetodias30No ratings yet

- 3000 Problemas de CircuitosDocument768 pages3000 Problemas de Circuitosbetodias30No ratings yet

- Measuring Speed and Position With A Quadrature EncoderDocument3 pagesMeasuring Speed and Position With A Quadrature Encoderbetodias30No ratings yet

- Chip NTC Thermistor Specification SheetDocument10 pagesChip NTC Thermistor Specification Sheetbetodias30No ratings yet

- Status ReportDocument1 pageStatus Reportbetodias30No ratings yet

- Infineon Ikcm20l60ga Ds v02 03 enDocument17 pagesInfineon Ikcm20l60ga Ds v02 03 enbetodias30No ratings yet

- AN650 - Max038 PDFDocument15 pagesAN650 - Max038 PDFbetodias30No ratings yet

- 1724-Motion Detection - Dual AnalogueDocument2 pages1724-Motion Detection - Dual Analoguebetodias30No ratings yet

- Altium - Creating Library ComponentsDocument32 pagesAltium - Creating Library Componentseaa603100% (1)

- En - cd00296680 PWM Stm8sDocument7 pagesEn - cd00296680 PWM Stm8sbetodias30No ratings yet

- Debugger stm8 PDFDocument23 pagesDebugger stm8 PDFbetodias30No ratings yet

- Gu0104 Shortcut KeysDocument16 pagesGu0104 Shortcut Keysbetodias30No ratings yet

- Display 20x4 TC2004A-01Document2 pagesDisplay 20x4 TC2004A-01betodias30No ratings yet

- HD44780Document60 pagesHD44780nzltfNo ratings yet

- MAX038Document17 pagesMAX038Brane PetkoskiNo ratings yet

- An185 - Thermal Management Using Heat SinksDocument9 pagesAn185 - Thermal Management Using Heat Sinksbetodias30No ratings yet

- An-1215 - Iram256-1067aDocument28 pagesAn-1215 - Iram256-1067abetodias30No ratings yet

- Manual Altium 2014 PDFDocument630 pagesManual Altium 2014 PDFbetodias30No ratings yet

- Primer Curso AlltiumDocument82 pagesPrimer Curso AlltiumMiguel JardinezNo ratings yet

- Display 20x4 TC2004A-01 PDFDocument18 pagesDisplay 20x4 TC2004A-01 PDFbetodias30No ratings yet

- MDP Cnvecad enDocument76 pagesMDP Cnvecad enbetodias30No ratings yet

- HIP4080A, 80V High Frequency H-Bridge Driver: Application Note December 11, 2007 AN9404.3Document13 pagesHIP4080A, 80V High Frequency H-Bridge Driver: Application Note December 11, 2007 AN9404.3Natalia González RoggetNo ratings yet

- Automated Pothole Filling MachineDocument5 pagesAutomated Pothole Filling MachineIJRASETPublicationsNo ratings yet

- PVG Valve Training: Proportional Valve FundamentalsDocument146 pagesPVG Valve Training: Proportional Valve Fundamentalsjose manuel barroso pantoja100% (7)

- GE OHV AC Control System Events For 17KG537 and Counters - ProlfilesDocument74 pagesGE OHV AC Control System Events For 17KG537 and Counters - ProlfilesFrancisco Tello Montero100% (1)

- Communication Systems OverviewDocument199 pagesCommunication Systems Overviewshreya namanaNo ratings yet

- A3941 DatasheetDocument21 pagesA3941 Datasheetsoft4gsmNo ratings yet

- Supply Voltage: Download Full-Size ImageDocument7 pagesSupply Voltage: Download Full-Size ImageDharanNo ratings yet

- Mn103sa5k Lsi User's ManualDocument554 pagesMn103sa5k Lsi User's ManualvietthufetNo ratings yet

- Grid-Forming Converters An Overview of Control Approaches and Future TrendsDocument8 pagesGrid-Forming Converters An Overview of Control Approaches and Future Trendsshaban sattiNo ratings yet

- LED Blinking Lab Manual ChapterDocument30 pagesLED Blinking Lab Manual Chapterराजस करंदीकरNo ratings yet

- Iskra Motor Selection GuideDocument21 pagesIskra Motor Selection GuideShruthi MadhuNo ratings yet

- LB 11961Document7 pagesLB 11961Ayala Eduardo La San RamonNo ratings yet

- Lab Viva SolvedDocument8 pagesLab Viva SolvedMuhammad Umair100% (2)

- CX/CXL/CXS Frequency Converters Brake Chopper and Resistor GuideDocument16 pagesCX/CXL/CXS Frequency Converters Brake Chopper and Resistor Guideaehque04No ratings yet

- 500w Power Amplifier Circuit DiagramDocument6 pages500w Power Amplifier Circuit DiagramJoão Alberto0% (1)

- KT 5198aDocument5 pagesKT 5198asrinu149No ratings yet

- Opm 40 KvaDocument103 pagesOpm 40 Kvarajabharath12No ratings yet

- TM Inverter Systems and Motors - 04-2008Document655 pagesTM Inverter Systems and Motors - 04-2008brainz2use86% (7)

- Holonomic Implementation of Three Wheels Omnidirectional Mobile Robot Using DC MotorsDocument7 pagesHolonomic Implementation of Three Wheels Omnidirectional Mobile Robot Using DC MotorsVinay PatilNo ratings yet

- A - Series of Pneumatic Glass-Wall Cleaning RobotDocument11 pagesA - Series of Pneumatic Glass-Wall Cleaning Robotrsbisht2010100% (1)

- uP6103 Synchronous Buck Controller Datasheet SummaryDocument15 pagesuP6103 Synchronous Buck Controller Datasheet SummarySelmar CavalcantiNo ratings yet

- Fuzzy LogicDocument9 pagesFuzzy LogicrakeshNo ratings yet

- HVPD Longshot PD Mapping System User Manual Sep 2009Document37 pagesHVPD Longshot PD Mapping System User Manual Sep 2009navi_0403100% (1)

- Microchip dsPIC30F2020 SMPS DatasheetDocument286 pagesMicrochip dsPIC30F2020 SMPS DatasheetMarlon MoscosoNo ratings yet

- Uninterruptible Power Supply System Selection PDFDocument139 pagesUninterruptible Power Supply System Selection PDFrajpre1213100% (1)

- AC PWM Dimmer For Arduino (With Pictures)Document17 pagesAC PWM Dimmer For Arduino (With Pictures)Gustavo CircelliNo ratings yet

- KA5M0965Q: Fairchild Power Switch (SPS)Document14 pagesKA5M0965Q: Fairchild Power Switch (SPS)Jose Angel TorrealbaNo ratings yet

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- Matlab Simulation of DrivesDocument24 pagesMatlab Simulation of DrivessabrahimaNo ratings yet

- Emini4310: Display ControllerDocument2 pagesEmini4310: Display ControllerLeonardusNo ratings yet