Professional Documents

Culture Documents

An58304 001-58304 0G V

Uploaded by

mark363Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An58304 001-58304 0G V

Uploaded by

mark363Copyright:

Available Formats

AN58304

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Author: Mark Hastings

Associated Project: No

Associated Part Family: All PSoC 3 and PSoC 5LP parts

Software Version: NA

Related Application Notes: None

AN58304 provides an overview of the analog routing matrix in PSoC 3 and PSoC 5LP. This matrix is used to

interconnect analog blocks and GPIO pins. A good understanding of the analog routing and pin connections can help

the designer make selections to achieve the best possible analog performance. Topics such as LCD and CapSense

routing are not covered in this application note.

Contents PSoC 3 and PSoC 5LP Internal Analog

PSoC 3 and PSoC 5LP Internal Analog Routing ...............1 Routing

Best Analog Ports .........................................................2 Prior to discussing which pins are better than others for a

Analog Mux Bus (AMUXBUS) ......................................4 particular operation or application, it is best to understand

Analog Globals (AGs) ...................................................4 the underlying analog structure of the PSoC 3 and

GPIO Connection to Analog Busses ............................5 PSoC 5LP parts. This application note will help the reader

understand how the basic analog structure works when

Optimizing Routing Resources .....................................5

adding a signal path between two points or placing an

Analog Local Bus (abus) ..............................................6 analog mux. PSoC Creator will do a good job routing most

Routing Example ..........................................................6 designs, but with some assistance from the designer, better

Direct Routes to GPIO Pins ..........................................6 performance can be achieved. Tools are provided in PSoC

IDAC Pin Selection .......................................................6 Creator to allow the user to validate and to make changes to

the internal analog routing of a design if needed.

Opamp Pin Selection ....................................................7

Reference Voltage Pins ................................................7 This application note focuses on connections between the

Separating Analog and Digital Signals .........................8 analog blocks and GPIO pins. Digital routing, SIO, USB, and

pins used for connecting the external crystals are not

Analog Device Editor .........................................................9

discussed.

Summary ......................................................................... 10

About the Author ............................................................. 10 PSoC 3 and PSoC 5LP can be divided into an analog and

digital section. The top section of the silicon is mostly analog

Worldwide Sales and Design Support ............................. 12

and the bottom section is digital. The analog section

consists of several analog blocks such as a Delta-Sigma

ADC (DSM), comparators, DACs, and SC/CT blocks. The

digital section contains the CPU, RAM, ROM, DMA, UDBs,

Clocks, and so on.

The entire chip is surrounded by pins. Most of these pins are

general purpose I/O or GPIO pins. The GPIO pins can be

configured for eight different modes: seven digital and one

analog input/output mode. This application note

concentrates only on the analog mode for these pins.

www.cypress.com Document No. 001-58304 Rev. *G 1

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Analog globals (AG) and analog mux buses (AMUXBUS) Figure 1. PSoC 3 and PSoC 5LP Analog/Digital Layout

provide analog connectivity between GPIOs and the various

analog blocks. As shown in Figure 1, there are 16 AGs that

Vddio0 AGL[7:4] AGR[7:4] Vddio3

are divided between four quadrants. Each quadrant contains

Upper Left Quadrant

GPIO GPIO

four analog globals: (AGR[7:4], AGR[3:0], AGL[7:4], and

Upper Right Quadrant

P0[7:0] P3[7:0]

AGL[3:0]). The analog mux bus may be connected to any of

GPIO SIO

the GPIO pins and most of the analog block inputs and P4[7:0] P12[1:0]

outputs. It may be divided between the left and right half of Analog

the chip or configured as a single bus that wraps around the SIO GPXT

P12[3:2]

Section P15[1:0]

entire chip. Together, the analog mux bus and analog

globals provide up to 18 paths between the analog blocks GPIO

P15[3:2]

and GPIO pins. Additionally, there are about 20 dedicated

paths between GPIOs and analog blocks. The dedicated

AMUXBUSR

routes provide low resistive paths between GPIOs and GPIO GPIO

AMUXBUSL

P6[7:0] P1[7:0]

devices such as current DACs and uncommitted opamps

Lower Right Quadrant

Lower Left Quadrant

(operational amplifiers). GPIO GPIO

P2[7:0] Digital P5[7:0]

Best Analog Ports GPIO Section SIO

P15[5:4] P12[7:6]

The largest parts of the PSoC 3 and PSoC 5LP families

have more than seven full 8-pin ports or 56 GPIOs that can SIO USB IO

P12[5:4] P15[7:6]

be used for analog input and output. Of these seven ports,

three have a slight analog performance advantage P0[7:0], Vddio2 AGL[3:0] AGR[3:0] Vddio1

P3[7:0], and P4[7:0]. These ports reside in the analog

upper portion of the chip. The analog globals, AGL[7:4] and

AGR[7:4] that connect to these ports, also reside only in the

upper analog section of the part, which give these ports a

slight signal-to-noise ratio advantage.

www.cypress.com Document No. 001-58304 Rev. *G 2

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Figure 2. PSoC 3 and PSoC 5LP Analog Diagram

Vdda

Vssa

Vcca

Vssd

* * * *

Vddio0

Vddio3

P15[3]

P15[2]

P12[1]

P12[0]

P12[3]

P12[2]

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

P3[7]

P3[6]

P0[3]

P0[2]

P0[1]

P0[0]

P4[1]

P4[0]

SIO

SIO

SIO

SIO

* * * * * * * *

swinn swinp

AMUXBUSL AMUXBUSR

* *

AGL[4] AGR[4]

AGL[5] AGR[5]

AGL[6] AGR[6]

AMUXBUSL

AGL[7] AGR[7]

AGL[4]

AGL[5]

AGL[6]

AGL[7]

ExVrefL ExVrefL2

ExVrefL1 swinp

opamp0 opamp2

opamp3 opamp1 GPIO

swinp 01 2 3 4 56 7 0123 3210 76543210 P3[5]

GPIO swfol

swinn

GPIO

*

swfol swfol swfol

P0[4]

swinp P3[4]

swinn

GPIO

GPIO

*

P0[5]

swinn P3[3]

GPIO in0 LPF in1

* i0 abuf_vref_int

swout swout

abuf_vref_int GPIO

P0[6] (1.024V)

out0 out1

(1.024V) ExVrefR

GPIO

swin swin

P3[2]

* i2 + comp0 comp1 + GPIO

P0[7] - - i3 P3[1]

refbufr_

refbufl_

cmp1_vref

cmp1_vref

cmp

cmp

cmp0_vref COMPARATOR cmp0_vref

GPIO

(1.024V) (1.024V) i1 P3[0]

GPIO + +

cmp_muxvn[1:0] - comp2 comp3 - GPXT

vref_cmp1

P4[2] (0.256V)

bg_vda_res_en

cmp1_vref

*P15[1]

GPIO Vdda bg_vda_swabusl0

GPXT

P4[3]

Vdda/2

refbuf_vref1 (1.024V) out CAPSENSE out refbuf_vref1 (1.024V)

*P15[0]

refbuf_vref2 (1.2V) ref ref refbuf_vref2 (1.2V)

GPIO in refbufl refbufr in

P4[4] refsel[1:0] refsel[1:0]

AGR[7]

AGR[6]

AGR[5]

AGR[4]

AMUXBUSR

GPIO vssa sc0 sc1 Vssa

P4[5] Vin Vin

GPIO sc0_bgref Vref Vref sc1_bgref

(1.024V) out out (1.024V) *

P4[6] sc2_bgref

SC/CT sc3_bgref Vccd

GPIO (1.024V)

Vin Vin (1.024V)

Vref Vref *

P4[7] Vssd

* out out

Vccd sc2 sc3 *

* Vddd

Vssd ABUSL0 ABUSR0

ABUSL1 ABUSR1

ABUSL2 ABUSR2

ABUSL3 ABUSR3

*

Vddd v0 v1 USB IO

DAC0 DAC1

i0 i1

GPIO * P15[7]

P6[0] VIDAC USB IO

v2

GPIO i2

DAC2 DAC3

v3

i3

* P15[6]

P6[1] GPIO

dac_vref (0.256V)

GPIO P5[7]

vcmsel[1:0] + GPIO

P6[2]

GPIO vssd

dsm0_vcm_vref1 (0.8V) vssa

-

DSM0

DSM P5[6]

P6[3] dsm0_vcm_vref2 (0.7V) vcm refs GPIO

GPIO qtz_ref P5[5]

dsm0_qtz_vref2 (1.2V) vref_vss_ext

P15[4] dsm0_qtz_vref1 (1.024V) GPIO

GPIO Vdda/3

Vdda/4 ExVrefL ExVrefR P5[4]

P15[5] refmux[2:0]

SIO

PSoC 5LP Only Vp (+) (+) Vp

GPIO P12[7]

Vn (-) SAR0 SAR1 (-) Vn

P2[0] Vrefhi_out Vrefhi_out SIO

GPIO SAR_vref1 (1.024V) refs refs SAR_vref1 (1.024V) P12[6]

P2[1]

SAR_vref2 (1.2V)

SAR ADC SAR_vref2 (1.2V)

GPIO

GPIO Vdda

Vdda/2

en_resvda ExVrefL1 ExVrefL2 en_resvda

Vdda

Vdda/2

*P1[7]

P2[2] refmux[2:0] refmux[2:0] GPIO

GPIO AMUXBUSL 01 23456 7 0123 3210 76543210 AMUXBUSR *P1[6]

P2[3] * ANALOG ANALOG

GLOBALS

ANALOG ANALOG

BUS BUS GLOBALS

GPIO

AMUXBUSR

AGR[0]

AGR[3]

AGR[2]

AGR[1]

P2[4] * TS

VBE

:

AMUXBUSL

* Vss ref

Vddio2 ADC

AGL[1]

AGL[2]

AGL[3]

AGL[0]

LPF

AGL[3] AGR[3]

AGL[2] AGR[2]

AGL[1] AGR[1]

AGL[0] AGR[0]

AMUXBUSL AMUXBUSR

* * * * *

*

*

Mux Group * * *

Vddio1

P12[4]

P12[5]

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

P5[0]

P5[1]

P5[2]

P5[3]

P1[0]

P1[1]

P1[2]

P1[3]

P1[4]

P1[5]

P2[5]

P2[6]

P2[7]

P6[4]

P6[5]

P6[6]

P6[7]

Switch Group

SIO

SIO

Connection

* * * * *

Switch Resistance Notes:

Vboost

XRES

Vssb

Vssd

Vbat

Small ( ~500 to 700 Ohms ) * Denotes pins on all packages

Ind

Large ( ~200 - 350 Ohms)

LCD signals are not shown. Rev #62

X- Large ( ~50 Ohms)

26-Mar-2013

www.cypress.com Document No. 001-58304 Rev. *G 3

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

PSoC Creator routes the analog signals for the user. on the same side. Analog globals can be used as single

However, the designer can dictate a preferred route by ended or differential signal paths.

selecting a preferred GPIO for a given signal manually.

This can be accomplished in the Pins section of the The globals on the left and right half may operate

Design Wide Resource Editor in PSoC Creator. independently or they may be joined through the switches

that are shown at the top and bottom. The analog globals

The PSoC 3 and PSoC 5LP Analog Diagram in Figure 2 is AGL[3:0] and AGR[3:0] are routed down and around the

a detailed view of the analog section. This diagram shows digital blocks. The other busses AGL[7:4] and AGR[7:4]

all possible analog routes and switches between analog stay up in the analog section where there is likely to be

blocks and GPIOs. It is important to take the time to less digital switching noise and the paths are shorter (less

understand the basic interconnection between the GPIO resistive). In the Analog Diagram, each analog block is

pins and the internal analog blocks to be able to get the capable of connecting to various analog busses. These

most out of your design. connections form an analog connection matrix between

analog blocks and GPIO pins. Analog blocks may be

Each package has a different combination of GPIO pins interconnected to each other or to GPIOs. The small

available to the user. Table 1 below lists the available pin circles indicate switches that connect the paths that

for each of the packages available for PSoC 3 and intersect. The On resistance of the switches colored red is

PSoC 5LP. about 200 to 350 ohms. The On resistance of the white

switches is about 500 to 700 ohms. Note that the

Table 1. GPIOs per package connection between the pins and analog globals or

100-pin 68-pin 48-pin 48-pin AMUXBUS is with the lower resistance switches.

Ports TQFP QFN QFN SSOP Most of the switches can be addressed individually, which

Port 0 P0[7:0] P0[7:0] P0[7:0] P0[7:0] means that any combination of switches can be connected

Port 1 P1[7:0] P1[7:0] P1[7:0] P1[7:0] at any time. Not all analog block connections are

Port 2 P2[7:0] P2[7:0] P2[7:3] P2[7:3] connected to every analog bus. Although this would

Port 3 P3[7:0] P3[7:0] NA NA provide the most routing flexibility, it would significantly

Port 4 P4[7:0] NA NA NA impact both the performance, due to added capacitance,

Port 5 P5[7:0] NA NA NA and the cost because of the additional size.

Port 6 P6[7:0] NA NA NA

To achieve a good tradeoff between cost, performance

Port 12 P12[7:0] P12[7:0] P12[3:0] P12[3:0] and routing, analog global bus connections between

Port 15 P15[7:0] P15[7:0] P15[7:6], P15[7:6], GPIOs and some analog block terminals are not fully

[3:0] [3:0] populated. The connection patterns to the analog buses

often alternate between adjacent blocks and GPIOs. For

example, in Figure 3, the negative input to the two

Analog Mux Bus (AMUXBUS) comparators connects to a different set of analog globals.

There are two AMUXBUS routes in PSoC 3 and The negative input to comparator 0 connects to the odd

PSoC 5LP devices. The AMUXBUSL may be connected to analog globals and comparator 2 connects to the even

any of the GPIOs on the left side. The AMUXBUSR can analog globals.

connect to all GPIOs on the right side of the device. The Figure 3. Comparator Connections

left and right AMUXBUS may be shorted together with an Analog Globals

abus1

abus2

abus3

abus0

analog switch to create a single bus that can be connected 01 2 3 4 56 7

to all GPIO pins. It is possible to use the AMUXBUS to + comp0 comp1 +

connect all GPIOs to a single analog block such as the - -

AMUXBUSL

Delta-Sigma ADC. COMPARATOR

+ +

- comp2 90 comp3 -

Analog Globals (AGs)

The PSoC 3 and PSoC 5LP devices are divided into four

quadrants as shown in Figure 1. The analog global bus

has eight routes on each side: AGL[7:0] on the left and

AGR[7:0] on the right. Within each side, the bus is divided

into two groups: AGR[3:0] and AGR[7:4] for the right side

and AGL[3:0] and AGL[7:4] for the left side. The lower four

globals on each side are routed to the GPIO in the lower

half of the part and the upper four globals on each side are

routed to the GPIO in the upper half of the device. All eight

analog globals on each side get routed to analog blocks

www.cypress.com Document No. 001-58304 Rev. *G 4

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Figure 6. Example 1 Internal Routing

GPIO Connection to Analog Busses

AMUXBUSL

Each GPIO pin may be connected to an analog global, the

AMUXBUS, or both simultaneously. Two pins of each port

AGL[7]

AGL[5]

AGL[4]

AGL[6]

share the same analog global connection. Figure 4

illustrates in two examples how the GPIOs are actually

connected to the analog global busses. PSoC Creator

makes these connections for the user when analog wires

and muxes are placed between analog blocks and GPIOs. GPIO

P4[4]

Figure 4. GPIO Connection to AG[n] and AMUXBUS GPIO

P4[5]

Lower Quad Upper Quad

GPIO

P4[6]

GPIO GPIO

P2[0] P0[0] GPIO

GPIO GPIO P4[7]

P2[1] P0[1] ADC

GPIO GPIO

P2[2] P0[2] If the same schematic is used, but a different combination

GPIO GPIO of pins (P0[2], P0[6], P4[2], P4[6]) selected we get a

P2[3] P0[3] different result. See Figure 7.

GPIO GPIO

P2[4] P0[4] Figure 7. Example 2 Schematic

GPIO GPIO

P2[5] P0[5] AMux ADC

GPIO GPIO

P2[6] P0[6]

GPIO GPIO

P2[7] P0[7]

AMUXBUS

AMUXBUS

AGL[1]

AGL[2]

AGL[3]

AGL[0]

AGL[5]

AGL[6]

AGL[7]

AGL[4]

This time a much more efficient use of internal routing

Optimizing Routing Resources resources are used as shown in Figure 8. Notice that only

Although PSoC 3 and PSoC 5LP contain much more one analog global, AGL[6] is used, leaving three analog

analog routing resources than previous families, there is globals to route other signals. This relatively small change

still a finite set of analog routes. Making the right pin in pin selection could easily make the difference between

assignments can mean the difference between a design a design fitting in the part or running out of routing

fitting into a particular part and not having sufficient routing resources.

resources. Take the following example in Figure 5 where Figure 8. Example 2 Internal Routing

an analog mux is used to connect four signals to the ADC.

AMUXBUSL

Figure 5. Example 1 Schematic

AGL[7]

AGL[5]

AGL[4]

AGL[6]

AMux ADC

GPIO

P0[2]

GPIO

P0[6]

With the pins P4[3:0] selected, Figure 6 is an example of GPIO

how the signals may be routed. Notice that all four of the P4[2]

analog globals AGL[7:4] are used. No other signals can be

GPIO

routed in that section using these globals. P4[6]

ADC

These two simple examples demonstrate the power of

understanding the internal routing diagram.

www.cypress.com Document No. 001-58304 Rev. *G 5

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Analog Local Bus (abus) Direct Routes to GPIO Pins

Internal to the analog section, there are eight additional Several direct routes bypass the amuxbus, analog globals,

analog local bus (abus) routes, four in the left half and the analog local bus to connect analog blocks directly

abusl[3:0] and four in the right half abusr[3:0] as shown in to GPIOs. The opamps and VIDACs both have direct

the Analog Diagram. These are local routes for connections that are used to maximize performance.

interconnecting analog blocks but not to GPIOs. They help Figure 12 is a simplified section of the analog routing

to save the analog globals to route to GPIOs. The left and diagram that shows some of these direct connections.

right sides may be shorted together with four analog

switches, as see in Figure 9. Figure 12. Dedicated GPIO Connections

GPIO

GPIO

GPIO

GPIO

P0[3]

P0[2]

P0[1]

P0[0]

Figure 9. Left and Right abus Interconnect

AMUXBUSL

AGL[4]

AGL[5]

AGL[6]

AMUXBUSL

AGL[7]

opamp0

AGL[4]

AGL[5]

AGL[6]

AGL[7]

1.024V

opamp2

GPIO abusl

Routing Example P0[4]

01 2 3

GPIO

Figure 10 and Figure 11 illustrate a PSoC Creator P0[5]

Schematic and one possible route. Analog Global AGL[7]

is used to connect GPIO P4[3] to the input of TIA_1 and i0 v0

DAC0 DAC1

v1

the negative input to the ADC_DelSig_1. Analog bus GPIO i0 i1

abusl0 connects the output of TIA_1 to the positive input P0[6] VIDAC

GPIO v2

DAC2 DAC3

v3

to ADC_DelSig_1. One of the analog globals AGL[6,4,2,0] P0[7] i2 i2 i3

could have been used instead of abusl0, but these are

most valuable routing signals to and from GPIOs.

IDAC Pin Selection

Figure 10. Example Signal Path Schematic

Each IDAC (current DAC) output may be routed to a GPIO

TIA_1 in several ways. Using the analog globals or the analog

mux bus works fine as long as the maximum current is

ADC_DelSig_1 limited to the two lower ranges of 32 A or 255 A. When

Vin

using the high current range of 2 mA, the resistance in the

path and analog switches may cause an excessive voltage

drop and limit the compliance voltage of the current source

at the pin. A path through the analog globals can be

500 ohms or more. To minimize the voltage drop, make

sure that one of the pins listed in Table 2 is used to

connect the output of the IDAC. This dedicated route is

Figure 11. Example of Signal Path Route

less than 100 ohms from IDAC to GPIO. PSoC Creator

AGL[7]

selects the appropriate IDAC to make sure that connection

abusl0

abusl3

is made. Using these dedicated pins also frees up routing

abusl1

abusl2

GPIO

Vin

P4[3] resources that can be used for other parts of the design.

sc0 sc1 These dedicated pins can be used no matter what IDAC

Vin Vin

sc0_bgref Vref Vref range is used. Therefore, you can use the dedicated pins

(1.024V) out out any time an IDAC is used to maximize routing resources.

sc2_bgref

(1.024V)

Vin

SC/CT Vin Figure 12 shows these dedicated routes for DAC0 and

Vref Vref Vref DAC2.

out out

sc2 TIA_1 sc3

Table 2. Dedicated IDAC Connections

+ IDAC GPIO Pin

-

DSM0

DSM DAC0 P0[6]

AMUXBUSL

DAC1 P3[0]

ADC_DelSig_1

DAC2 P0[7]

01234567 DAC3 P3[1]

AGL[7:0]

www.cypress.com Document No. 001-58304 Rev. *G 6

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Opamp Pin Selection Pins P0[2] and P0[4] are used to attach these capacitors

to the SAR ADCs references.

The opamps are connected to the GPIOs in such a way

that they can be used without any internal analog global Table 4 is a summary of all the dedicated routes to GPIO

busses, See Figure 12. If all connections to the opamp are pins on ports 0 and 3. It is a good idea to keep this list in

external through the GPIOs, it is a good idea to use the mind when selecting GPIO connections to an IDAC and

dedicated pins. In many cases, the opamp may be used opamp, or when required to connect a bypass capacitor to

as a buffer to an internally generated signal, such as a an ADC reference. If you look close, the analog diagram in

buffer to a VDAC output. In this case the dedicated opamp Figure 2 details each of these connections.

input pins may be ignored and used for another purpose.

After the opamp is enabled, the dedicated output GPIO Table 4. GPIO Direct Routes

will always be driven by the output of the opamp. This Port Description

GPIO is now dedicated to the opamp output and cannot

be used for another signal. Even if this signal is only used P0[0] Opamp2 output

internally, the dedicated output pin will be driven by the P0[1] Opamp0 output

opamp. This guarantees that the resistance between the

opamp and GPIO pin is low, about 5 ohms. If you must P0[2] Opamp0 non-inverting input

use a different pin for the output, the dedicated output pin ExVrefL2 SAR ADC reference input

still outputs the signal. If the opamp is not used, it has no

affect on the GPIOs directly connected to it. These GPIO P0[3] Opamp0 inverting input

pins operate as any of the other GPIOs when the opamp ExVrefL DCM (DelSig ADC) reference input

is disabled. The dedicated GPIO connections to the Internal Reference bypass capacitor

opamps are summarized in Table 3.

P0[4] Opamp2 non-inverting input

Table 3. Dedicated Opamp Connections ExVrefL1 SAR ADC reference input

OPAMP GPIO Pin GPIO Pin GPIO Pin P0[5] Opamp2 inverting input

(Non-inverting) (Inverting) (Output) P0[6] VIDAC0 current sink/source connection

Opamp0 P0[2] P0[3] P0[1] P0[7] VIDAC2 current sink/source connection

Opamp1 P3[5] P3[4] P3[6] P3[0] VIDAC1 current sink/source connection

Opamp2 P0[4] P0[5] P0[0] P3[1] VIDAC3 current sink/source connection

Opamp3 P3[3] P3[2] P3[7] P3[2] Opamp3 inverting input

ExVrefL DCM (DelSig ADC) reference input

Internal Reference bypass capacitor

Reference Voltage Pins

P3[3] Opamp3 non-inverting input

External references can be used to enhance the accuracy

or change the range of the ADCs. There are connections P3[4] Opamp1 inverting input

for external references for both the Delta-Sigma and SAR P3[5] Opamp1 non-inverting input

ADCs. The SAR ADC is only available in the PSoC 5LP

families. The internal reference is accurate up to 0.1% P3[6] Opamp1 output

over the operating temperature range depending on the P3[7] Opamp3 output

device selected. An external reference can increase the

accuracy beyond 0.1%. For the Delta-Sigma ADC, either

pins P0[3] or P3[2] may be used for an external reference.

Pins P0[2] and P0[4] can be used to used to provide an

external reference for the two SAR ADCs found in the

PSoC 5 and PSoC 5LP parts.

Pin P0[3] or P3[2] can also be used to attach an external

bypass capacitor to the internal Delta-Sigma ADC

reference to help filter out any internal low frequency

noise. This capacitor value should be in the range of 1 F

to 10 F.

When using a SAR ADCs in PSoC 5LP with a sample rate

above 100 Ksps or at the same time as the Delta-Sigma

ADC is used, external bypass capacitors should be used.

www.cypress.com Document No. 001-58304 Rev. *G 7

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Separating Analog and Digital Signals Figure 13. Ideal Analog and Digital Separation

Depending on the sensor or source, many if not most Analog Pins

analog signals tend to be relatively high impedance, at AGL[7:4] AGR[7:4]

times as high as several megaohms. Digital signals on the

other hand are usually low impedance on the order of 10 GPIO GPIO

P0[7:0] P3[7:0]

to 50 ohms with fast edge times of tens of nanoseconds or

faster. GPIO SIO

P4[7:0] P12[1:0]

When these two signals are placed in close proximity on a Analog

circuit board, or are on adjacent pins, the fast rise and fall SIO GPXT

times of the digital signal can easily be capacitively P12[3:2]

Section P15[1:0]

coupled to the analog signal. Therefore, when selecting

pins for analog and digital functions, it is recommended GPIO

that analog and high speed digital signals be kept away P15[3:2]

from each other when possible. This coupling can occur

AMUXBUSR

both internal to the chip at the I/O pads and on the circuit

GPIO GPIO

board traces. Isolating these signals by at least one pin

AMUXBUSL

P6[7:0] P1[7:0]

reduces this coupling both internally and externally. If

possible it is good design practice to keep analog and GPIO GPIO

digital signals on opposite sides of the chip. This also P2[7:0] Digital P5[7:0]

helps when it is time to lay out the circuit board.

GPIO Section SIO

A few easy steps can be used to plan a pinout for optimal P15[5:4] P12[7:6]

analog performance.

SIO USB IO

Design Steps P12[5:4] P15[7:6]

1. Determine how many analog pins/ports are required AGL[3:0] AGR[3:0]

for a given design.

2. Determine which signals can or should use the Digital Pins

dedicated routes between the analog block and the

GPIO pin. Make these pin assignments first.

Sometimes a design may have a mix of precision analog,

3. Start with port 0 and work out in both directions to port low resolution analog, low speed digital, and high speed

4 and port 3 and select the analog GPIO pins needed digital. The low precision and low speed digital can be

for the design. used to isolate the precision analog and high speed digital.

4. Draw a line between the analog GPIO pins selected See Figure 14 for an example.

and the rest of the pins required for the design. Connecting to the Sigma_Delta ADC

5. Keep all analog GPIOs on one side of the line and all The analog blocks are equally distributed between the left

digital GPIOs on the other. and right sides of the chip. Currently, there is just one

Follow these simple steps to isolate the analog and digital Delta-Sigma ADC, which is placed on the left side and

signals on both the chip and your circuit board. Figure 13 only has direct connections to the routing resources on the

shows an ideal separation between analog and digital left side. Signals may be routed from the right side of the

ports. part, but only by connecting the left and right analog

globals together. When pins from the right side of the part

must connect to the ADC, the analog globals on the right

side must be connected to the corresponding analog

globals on the left side. For example, if pin P3[7] needs to

be routed to the ADC, the pin is first connected to AGR[7].

Then AGL[7] must then be connected to AGR[7] to route

to the ADC. However, if pin P0[7] is selected, then only

analog global AGL[7] is used instead of both AGR[7] and

AGL[7]. (See the top section Analog Diagram for clarity).

All of the left analog globals (AGL[7:0]) may be connected

to the corresponding right analog globals (AGR[7:0]). See

Figure 15.

www.cypress.com Document No. 001-58304 Rev. *G 8

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Figure 14. Three Signal Sections Analog Device Editor

PSoC Designer 2.0 and higher added a new feature that

allows the user to validate the actual routing paths for all

Precision Analog Pins signals in the schematic. This tool not only allows the user

AGL[7:4] AGR[7:4] to view the routes, but also change the routes as well.

GPIO GPIO This Analog Device Editor tool can be found in the Design

P0[7:0] P3[7:0] Wide Resource section in the Analog tab. Figure 16

shows an example of the Analog Device Editor window.

GPIO SIO

P4[7:0] P12[1:0] Figure 16. Example view of Analog Device Editor

Analog

SIO GPXT

P12[3:2]

Section P15[1:0]

Mixed low speed Digital GPIO

P15[3:2]

and low resolution Analog

AMUXBUSR

GPIO GPIO

AMUXBUSL

P6[7:0] P1[7:0]

GPIO GPIO

P2[7:0] Digital P5[7:0]

GPIO Section SIO

P15[5:4] P12[7:6]

SIO USB IO

P12[5:4] P15[7:6]

AGL[3:0] AGR[3:0]

Digital Pins

Figure 15. DelSig ADC Analog Connections

AMUXBUSL AMUXBUSR

GPIO

P0[7:0]

AGL[7:4] AGR[7:4] GPIO

P3[7:0] A full description of the Analog Device Editor and how to

GPIO

P4[7:0]

use it can be found in the PSoC Creator Document

DSM0

DelSig Manager. To find this document, click on the Help menu

GPIO ADC GPIO and select Document Manager. See Figure 17.

P6[7:0] P5[7:0]

GPIO GPIO

Figure 17. Document Manager location

P2[7:0] AGL[3:0] AGR[3:0] P1[7:0]

www.cypress.com Document No. 001-58304 Rev. *G 9

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

In the Document Manager, select PSoC Creator Help Summary

under the Contents tab and navigate down to Using

Design Entry Tools/Design-Wide Resources/Analog Because there are sufficient analog routing resources for

Device Editor. This section of the help manual will show most applications, designers should not be concerned with

you how to examine and to edit your circuits analog. See getting the most efficient hardware usage. For those cases

Figure 18. where most analog resources are used or maximum

Figure 18. Analog Device Editor Documentation analog performance is required, the topics discussed in

this application note will help to optimize the design. The

single most important thing that will help to improve your

design, is to understand the PSoC 3 and PSoC 5LP

analog architecture shown in Figure 2, and make pin

selections based on this knowledge. Take advantage of

the Analog Device Editor and review your analog routes to

verify that they have been routed as expected and make

changes if needed.

All GPIO pins work fine for analog input, but ports P0[7:0],

P3[7:0], and P4[7:0] may provide a measurable advantage

in signal-to-noise performance than the remaining ports.

Care should always be taken to keep digital signals away

from sensitive analog signals, both on the PSoC and on

the PCB.

About the Author

Name: Mark Hastings

Title: Applications Engineer MTS

Some Analog Device Editor features include: Background: Mark Hastings graduated from

Washington State University in 1984.

View actual signal paths For most of the last twenty five years,

Examine Analog Mux routing and configuration he has been involved in embedded

and mixed signal designs. During his

Measure the resistance of a signal path free time he can be found hiking and

climbing in the Cascade Mountains of

Locking components to a specific analog block Washington State.

Change which analog blocks are used for a given Contact: meh@cypress.com

component

Re-routing signal paths and analog mux routes

View individual switch resistance

Display individual switch control register address

and mask value

www.cypress.com Document No. 001-58304 Rev. *G 10

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Document History

Document Title: PSoC 3 and PSoC 5LP Pin Selection for Analog Designs - AN58304

Document Number: 001-58304

Revision ECN Orig. of Submission Description of Change

Change Date

** 2828695 MEH 12/15/2009 New application note.

*A 2991540 SRIH 07/22/2010 Fixed branding discrepancies

*B 3371422 MEH 09/14/2011 Rewrite of several paragraphs and added or updated Figures, 2,

5,6,7,8,13

*C 3655552 MEH 06/26/2012 Updated PSoC 3 and PSoC 5 Internal Analog Routing.

Updated Summary.

Updated in new template.

*D 3812768 MEH 11/15/2012 Updated Associated Part Family as All PSoC 3 and PSoC 5LP parts.

Replaced PSoC 5 with PSoC 5LP in all instances across the document.

*E 3941625 MEH 04/01/2013 Update of the analog diagram. Several minor changes. Added reference

to PSoC Creator Analog Editor.

*F 4391233 MEH 05/28/2014 Fixed error in Figures 1, 13 and 14 that labeled USB pins incorrectly

*G 4573140 MEH 11/18/2014 Sunset Update

www.cypress.com Document No. 001-58304 Rev. *G 11

PSoC 3 and PSoC 5LP Pin Selection for Analog Designs

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturers representatives, and distributors. To find

the office closest to you, visit us at Cypress Locations.

Products PSoC Solutions

Automotive cypress.com/go/automotive psoc.cypress.com/solutions

Clocks & Buffers cypress.com/go/clocks PSoC 1 | PSoC 3 | PSoC 5LP

Interface cypress.com/go/interface

Cypress Developer Community

Lighting & Power Control cypress.com/go/powerpsoc

cypress.com/go/plc Community | Forums | Blogs | Video | Training

Memory cypress.com/go/memory

Technical Support

PSoC cypress.com/go/psoc

cypress.com/go/support

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/usb

Wireless/RF cypress.com/go/wireless

PSoC is a registered trademark of Cypress Semiconductor Corp. PSoC Creator is a trademark of Cypress Semiconductor Corp.All other trademarks or

registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor Phone : 408-943-2600

198 Champion Court Fax : 408-943-4730

San Jose, CA 95134-1709 Website : www.cypress.com

Cypress Semiconductor Corporation, 2009-2014. The information contained herein is subject to change without notice. Cypress Semiconductor

Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any

license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or

safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as

critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The

inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies

Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide

patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a

personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative

works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress

integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source

Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT

NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the

right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or

use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a

malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress product in a life-support systems

application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

www.cypress.com Document No. 001-58304 Rev. *G 12

You might also like

- Economical 3 D Printer Using F DMDocument6 pagesEconomical 3 D Printer Using F DMmark363No ratings yet

- Tan-005Document9 pagesTan-005mark363No ratings yet

- Cypress Intro To BLE System DesignDocument93 pagesCypress Intro To BLE System Designmark363No ratings yet

- BC848 SerDocument12 pagesBC848 Sermark363No ratings yet

- R999000202 Step Into The Future With Hagglunds CBM AE 2013-06Document4 pagesR999000202 Step Into The Future With Hagglunds CBM AE 2013-06mark363No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Tutorial Nodal AnalysisDocument11 pagesTutorial Nodal Analysisazizi abdullahNo ratings yet

- 300w PA Using A MRF300AN Transistor by Sergey EX8MLE The Four Metres Website - 1625828700391Document6 pages300w PA Using A MRF300AN Transistor by Sergey EX8MLE The Four Metres Website - 1625828700391Jeannot BopendaNo ratings yet

- Uc3844 PDFDocument14 pagesUc3844 PDFAco ZekiriNo ratings yet

- ENSC 225 Operational Amplifier LabDocument15 pagesENSC 225 Operational Amplifier LabaaaaaaNo ratings yet

- MZ15-RN Input Module Schems PDFDocument47 pagesMZ15-RN Input Module Schems PDFMarcos MesquitaNo ratings yet

- Unit 2 - Logic Gate Devices Characteristics (DBV30023)Document68 pagesUnit 2 - Logic Gate Devices Characteristics (DBV30023)Abd Kadir JailaniNo ratings yet

- BJT Characteristics: ObjectiveDocument8 pagesBJT Characteristics: ObjectiveAbhishek MouryaNo ratings yet

- Module Descriptor For Digital ElectronicsDocument4 pagesModule Descriptor For Digital ElectronicsTashi DendupNo ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- Latch-Up Prevention in CMOS Logics - Team VLSIDocument13 pagesLatch-Up Prevention in CMOS Logics - Team VLSIKaifeng LiuNo ratings yet

- Experiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierDocument5 pagesExperiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierSajawal AliNo ratings yet

- Esercizi ElettronicaDocument6 pagesEsercizi Elettronicapignatti.lucreziaNo ratings yet

- Experiment No Astable Multivibrator Using Op AmpDocument24 pagesExperiment No Astable Multivibrator Using Op AmpUnique ProNo ratings yet

- ECEN720: High-Speed Links Circuits and Systems Spring 2021: Lecture 5: Termination, TX Driver, & Multiplexer CircuitsDocument66 pagesECEN720: High-Speed Links Circuits and Systems Spring 2021: Lecture 5: Termination, TX Driver, & Multiplexer Circuits陈晨No ratings yet

- Ch5 Power Supplies Voltage Regulator Pp15aDocument38 pagesCh5 Power Supplies Voltage Regulator Pp15aeddyonnNo ratings yet

- DC Circuits 2 ExamDocument3 pagesDC Circuits 2 ExamBatalla, Frencee Shine A.No ratings yet

- Lab 2: Common Source Amplifier With Resistor Load and Source DegenerationDocument28 pagesLab 2: Common Source Amplifier With Resistor Load and Source DegenerationceferinotanNo ratings yet

- Application Examples: Vishay SemiconductorsDocument6 pagesApplication Examples: Vishay SemiconductorsdraNo ratings yet

- MC14016B Quad Analog Switch/ Quad Multiplexer: PDIP-14 P Suffix CASE 646Document12 pagesMC14016B Quad Analog Switch/ Quad Multiplexer: PDIP-14 P Suffix CASE 646VinhNo ratings yet

- VLSIDESIGN MTECH2021-23 ANALOGICDESIGNLAB ASSIGNMENT05Document15 pagesVLSIDESIGN MTECH2021-23 ANALOGICDESIGNLAB ASSIGNMENT05Rutvik PatelNo ratings yet

- 051790F0Document19 pages051790F0Rohmad FauziNo ratings yet

- 11.6 A Multi-Channel Neural-Recording Amplifier System With 90Db CMRR Employing Cmos-Inverter-Based Otas With CMFB Through Supply Rails in 65Nm CmosDocument3 pages11.6 A Multi-Channel Neural-Recording Amplifier System With 90Db CMRR Employing Cmos-Inverter-Based Otas With CMFB Through Supply Rails in 65Nm CmosLuật TrầnNo ratings yet

- LYNX Audio Amplifier 275W 4 OhmiDocument11 pagesLYNX Audio Amplifier 275W 4 OhmiDanut777750% (2)

- LDR Automatic Street Light ControlDocument24 pagesLDR Automatic Street Light ControlAbhinandan GogoiNo ratings yet

- Analog Communication Lab ManualDocument59 pagesAnalog Communication Lab Manualsasa_sag100% (2)

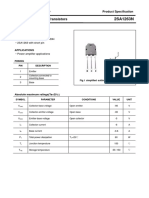

- Silicon PNP Power Transistors: Inchange Semiconductor Product SpecificationDocument4 pagesSilicon PNP Power Transistors: Inchange Semiconductor Product SpecificationRuben MapaloNo ratings yet

- Op To CouplerDocument5 pagesOp To CouplersamponNo ratings yet

- Const. K HP FilterDocument14 pagesConst. K HP FilterRavi KantNo ratings yet

- A 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierDocument9 pagesA 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierSampoornaGonellaNo ratings yet