Professional Documents

Culture Documents

Exafeb 08

Uploaded by

Dgm Cb Gfm DgOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exafeb 08

Uploaded by

Dgm Cb Gfm DgCopyright:

Available Formats

Ampliacin de Arquitecturas de Computadoras

Examen de febrero (28/01/8) Teora y problemas

Durante el examen no se permiten apuntes ni nada encima de la mesa. El tiempo para la realizacin de este

ejercicio es de 1 hora y 30 minutos. En caso de duda escribe en el examen tu suposicin y contina.

1. (3 puntos) Se tiene una mquina vectorial con registros de 64 elementos, una unidad

funcional de cada tipo (ADDV, SUBV, MULTV y DIVV) y un cauce de lectura (LV) y otro

de escritura (SV) con la memoria. Cada registro vectorial tiene dos cauces de lectura y uno

de escritura. Los tiempos de arranque son 12 para LV y SV; 6 para ADDV y SUBV; 7 para

MULTV; y 16 para DIVV. El tiempo de bucle es de 15 ciclos y la frecuencia de reloj es de

850 MHz. Dado el siguiente cdigo vectorial (parte interna de un bucle):

LV V1,R1

MULTV V2,V1,V1

SUBV V6,V2,V1

ADDV V2,V2,V3

SUBV V1,V2,V4

SV R1,V2

MULTV V3,V3,V1

SV R2,V3

Calcula R (MFLOPS) y N1/2 suponiendo primero que la mquina no soporta

encadenamiento y luego que s que lo soporta. Debe incluirse el cdigo con la representacin

de la separacin de las instrucciones en convoyes y los tiempos de arranque.

2. Disea y dibuja una memoria entrelazada con 4 mdulos de manera que se acceda a ella

en el doble de la velocidad de acceso al mdulo y con suficiente tolerancia a fallos para

deshabilitar una parte de la memoria sin degradar el sistema. (Debe representarse el bus de

datos, direcciones, control, etc.) Pon un ejemplo de acceso a dicha memoria en el que se

muestre el peor caso, es decir, que no se alcance la mxima velocidad. Qu velocidad se

obtendra en el peor caso antes reseado?

3. Se tienen un procesador vectorial con registros vectoriales de 64 elementos y un

procesador matricial con registros de 8 elementos (como el Cell por ejemplo). Suponiendo

que el tiempo de bucle fuera despreciable y que ambos tienen la misma frecuencia de reloj,

calculad en ambos casos el tiempo de ejecucin de una suma vectorial de 64 elementos con 6

ciclos de tiempo de arranque. Qu mquina es la ms rpida de las dos en este caso?

Pon un ejemplo de operacin en la que ocurra justo al revs y justifcalo.

4. Supongamos una conmutacin de tipo lombriz en la cual los W primeros flits de un

paquete con L+W flits, contiene cada uno de ellos el canal a tomar para ir al siguiente nodo

por orden. Suponiendo que cada uno de estos flits se van descartando cada vez que se

atraviesa un nodo (como en Myrinet por ejemplo), calcula la expresin de la latencia de un

paquete sin bloqueos hasta llegar a su destino. Dibuja el diagrama de tiempos.

5. (1 punto) Describe algortmicamente, con seudo-lenguaje, un algoritmo de

encaminamiento completamente adaptativo y libre de interbloqueos basado en el protocolo

de Duato para mallas de 3 dimensiones.

You might also like

- Instrucciones Pla de Contingència FAMILIASDocument10 pagesInstrucciones Pla de Contingència FAMILIASDgm Cb Gfm DgNo ratings yet

- ANEXO III Manifiesto PDFDocument1 pageANEXO III Manifiesto PDFDgm Cb Gfm DgNo ratings yet

- Instalación de Certificado Digital en Fichero Firefox 56 o SuperiorDocument4 pagesInstalación de Certificado Digital en Fichero Firefox 56 o SuperiorFrancisco Buendía Del MolinoNo ratings yet

- Vamos A Multiplicar - HeladosDocument12 pagesVamos A Multiplicar - HeladosDgm Cb Gfm Dg100% (2)

- Mi Libro de Letras PDFDocument31 pagesMi Libro de Letras PDFDgm Cb Gfm DgNo ratings yet

- Febrero0304v1 PDFDocument4 pagesFebrero0304v1 PDFDgm Cb Gfm DgNo ratings yet

- Agenda 20 21 6horas PDFDocument151 pagesAgenda 20 21 6horas PDFDgm Cb Gfm DgNo ratings yet

- Aguacate Papaya 2017Document1 pageAguacate Papaya 2017Dgm Cb Gfm DgNo ratings yet

- Evinic 3ep CLDocument12 pagesEvinic 3ep CLIreneNo ratings yet

- Tema 10: Transmisión de Datos en Redes ATM y Frame RelayDocument37 pagesTema 10: Transmisión de Datos en Redes ATM y Frame RelayDgm Cb Gfm DgNo ratings yet

- Mod 145 2015Document2 pagesMod 145 2015nachete60No ratings yet

- Febrero0304v2 PDFDocument4 pagesFebrero0304v2 PDFDgm Cb Gfm DgNo ratings yet

- Programación modular con subprogramas CDocument3 pagesProgramación modular con subprogramas CDgm Cb Gfm DgNo ratings yet

- Aec 520Document21 pagesAec 520Agustin Duarte OrozcoNo ratings yet

- Boletin Huerto 165Document2 pagesBoletin Huerto 165Dgm Cb Gfm DgNo ratings yet

- AED Tema 08 Cuestiones PDFDocument3 pagesAED Tema 08 Cuestiones PDFDgm Cb Gfm DgNo ratings yet

- FuncionesDocument10 pagesFuncionesRoberto HumerezNo ratings yet

- AED Tema 06 Cuestiones PDFDocument3 pagesAED Tema 06 Cuestiones PDFDgm Cb Gfm DgNo ratings yet

- Lac p7Document2 pagesLac p7Dgm Cb Gfm DgNo ratings yet

- Aic T5 1Document2 pagesAic T5 1Dgm Cb Gfm DgNo ratings yet

- Ex MP PDFDocument3 pagesEx MP PDFDgm Cb Gfm DgNo ratings yet

- Ejer Adicionales Temas 1 y 2Document4 pagesEjer Adicionales Temas 1 y 2Dgm Cb Gfm DgNo ratings yet

- FFI BandasDocument1 pageFFI BandasDgm Cb Gfm DgNo ratings yet

- C 18 UsbDocument83 pagesC 18 UsbArmando Antonio PerezNo ratings yet

- Analisis LexicoDocument25 pagesAnalisis LexicoVictor M ArenasNo ratings yet

- Exajul04 PDFDocument2 pagesExajul04 PDFDgm Cb Gfm DgNo ratings yet

- Exajul04 PDFDocument2 pagesExajul04 PDFDgm Cb Gfm DgNo ratings yet

- Exafeb 10Document1 pageExafeb 10Dgm Cb Gfm DgNo ratings yet

- Exafeb 09Document1 pageExafeb 09Dgm Cb Gfm DgNo ratings yet

- NTC 5385 Cda V2Document33 pagesNTC 5385 Cda V2hermodiazNo ratings yet

- Reacción álcali-agregado: causas y efectos del deterioro del concretoDocument5 pagesReacción álcali-agregado: causas y efectos del deterioro del concretomelanyNo ratings yet

- Tecnologías emergentes refrigeración alimentosDocument12 pagesTecnologías emergentes refrigeración alimentosMiriam EncinasNo ratings yet

- LevitasDocument25 pagesLevitasNelson Alguinzones100% (1)

- Seguridad en Internet Con Los Certificados SSL y HTTPSDocument7 pagesSeguridad en Internet Con Los Certificados SSL y HTTPSJuan Carlos SchincariolNo ratings yet

- Lesiones Tendon Aquiles AbelDocument19 pagesLesiones Tendon Aquiles AbelaquijadaNo ratings yet

- Carnicos Mapa Mental Mireles Rocha XimenaDocument4 pagesCarnicos Mapa Mental Mireles Rocha XimenaXimena RochaNo ratings yet

- Efectos Adversos de Los Medicamentos AntipsicóticosDocument6 pagesEfectos Adversos de Los Medicamentos AntipsicóticosFlor DuclosNo ratings yet

- Asesoria de Familia Pedido FormularioDocument1 pageAsesoria de Familia Pedido FormularioFlorencia De SantisNo ratings yet

- Sugerencias para Alumnos Sordos e Hipoacúsicos - Docx (Celeste Stefanolo)Document3 pagesSugerencias para Alumnos Sordos e Hipoacúsicos - Docx (Celeste Stefanolo)Celeste StefanoloNo ratings yet

- Prueba 2015Document23 pagesPrueba 2015Gema PcNo ratings yet

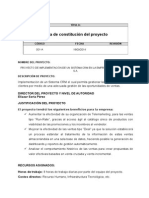

- Acta de ConstitucionDocument3 pagesActa de ConstitucionerickNo ratings yet

- Programación Camp Next Level DefinitvoDocument4 pagesProgramación Camp Next Level Definitvomariajota2009No ratings yet

- Evaluacion de Defensa Pae 2023Document1 pageEvaluacion de Defensa Pae 2023Digita OZNo ratings yet

- Geografia HumanaDocument20 pagesGeografia HumanaFrias NelsonNo ratings yet

- Monografía sobre Filipenses 2:1-11Document17 pagesMonografía sobre Filipenses 2:1-11Claudia Patricia Montes BolañosNo ratings yet

- Ficha Uso Del TiempoDocument4 pagesFicha Uso Del Tiempoluis212121No ratings yet

- Resumen ComercialDocument67 pagesResumen ComercialDAVID STIVEN AGUDELO BOLANOSNo ratings yet

- Gtic U3 A2 NaggDocument3 pagesGtic U3 A2 NaggNallely García75% (4)

- Proyecto de Elaboración de Humus NuevoDocument25 pagesProyecto de Elaboración de Humus NuevoFidel100% (2)

- Tarea 7 Semana 8Document2 pagesTarea 7 Semana 8Luis Alberto MendozaNo ratings yet

- Genetic Diversity ESPDocument11 pagesGenetic Diversity ESPBetty VelardeNo ratings yet

- Agroproductividad V 2015Document88 pagesAgroproductividad V 2015Cordero VeintiséisNo ratings yet

- Procedimiento Del Divorcio Por Incompatibilidad de Caracteres Con Domicilio Desconocido de La EsposaDocument22 pagesProcedimiento Del Divorcio Por Incompatibilidad de Caracteres Con Domicilio Desconocido de La EsposaJose AracenaNo ratings yet

- Foda Sana SanaDocument5 pagesFoda Sana SanaSTEVEN SENEN MUÑOZ PINCAYNo ratings yet

- NORMA Oficial Mexicana NOM-016-SSA3-2012Document73 pagesNORMA Oficial Mexicana NOM-016-SSA3-2012Alejandro García Rivera33% (3)

- Mal de Ojo EspañaDocument17 pagesMal de Ojo EspañaPaul Velecela MartínezNo ratings yet

- Responsabilidad Social Leismar LucenaDocument1 pageResponsabilidad Social Leismar LucenaleismarNo ratings yet

- Recursos AdministrativosDocument7 pagesRecursos AdministrativosJenny Hendrick GonzalesNo ratings yet

- I. Los Orígenes Del Derecho de La CristiandadDocument53 pagesI. Los Orígenes Del Derecho de La CristiandadJorge Andrés Calderón MongeNo ratings yet