Professional Documents

Culture Documents

Eee572 L10

Uploaded by

Jack SquatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Eee572 L10

Uploaded by

Jack SquatCopyright:

Available Formats

EEE342/ETE418_L10

Control Engineering

Dr. Abdur Razzak

Lecture 10

Discrete

Control

Systems

Objectives

To learn & study

the modeling & designing of

discrete control systems

EEE342/ETE418_L10

Discrete control system - example

Dr. Abdur Razzak

Fig: Digital antenna azimuth position control system

EEE342/ETE418_L10

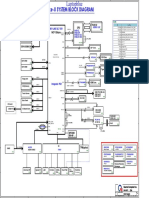

Discrete control system block diagram

Dr. Abdur Razzak

Fig: (a) placement of the digital computer within the loop; (b) detailed block

diagram showing placement of A/D and D/A converters

EEE342/ETE418_L10

Advantages & Disadvantages

Dr. Abdur Razzak

Advantages

Improved sensitivity - high sensitivity can pick up low energy signals

better

Use digital components - less sensitive to noise

Flexibility in response to design changes - can easily change

parameters in algorithms to modify / adjust behavior

Many systems inherently digital - radar, satellite systems, etc. send info

in pulses

Reduced cost - in industry, a single digital computer can replace

numerous analog controllers thereby reducing the cost

Disadvantages

Develop complex math algorithms - time consuming and difficult to get

algorithm right

Lose information during conversions - quantization error, loss of

information between samples

EEE342/ETE418_L10

Continuous vs discrete controller

Dr. Abdur Razzak

EEE342/ETE418_L10

Digital to analog converter

Dr. Abdur Razzak

Digital-to-analog conversion is simple and effectively

instantaneous. Properly weighted voltages are summed together

to yield the analog output.

For example, in figure, three weighted voltages are summed. The

three-bit binary code is represented by the switches.

Thus, if the binary

number is 1102, the

bottom and center

switches are on, and

the analog output is

6 volts. In actual

use, the switches

are electronic and

are set by the input

binary code.

EEE342/ETE418_L10

Analog to digital conversion

Dr. Abdur Razzak

Analog-to-digital (A/D) conversion is a two-step process and is not

instantaneous (there is a delay between the analog input and digital

output: the analog signal is first converted to a sampled signal and then

converted to a sequence of binary numbers, the digital signal.

The sampling rate (Nyquist sampling rate) must be at least twice the

bandwidth of the signal, otherwise there will be distortion.

Analog signal sampled at periodic intervals and held over the sampling

interval by a device called a zero-order sample-and-hold (z.o.h.) that

yields a staircase approximation to the analog signal.

After sampling and holding, the dynamic range of the analog signal's

voltage is divided into discrete levels, and each level is assigned a

digital number.

The difference between levels is M/2n volts, where n is the number of

binary bits used for the analog-to-digital conversion.

EEE342/ETE418_L10

Analog to digital conversion (contd.)

Dr. Abdur Razzak

Fig: Steps in analog to digital

conversion: a. analog signal; b.

analog signal after sample-and-hold;

c. conversion of samples to digital

numbers

EEE342/ETE418_L10

Modeling the discrete controller

Dr. Abdur Razzak

If we are to analyze and design feedback control systems with

digital computers, we must be able to model the digital computer

and associated digital-to-analog and analog-to-digital converters.

Our goal is to represent the computer as a transfer function

similar to that for any subsystem.

In order to model digital control systems, we must come up with

a mathematical representation of sample-and-hold process.

1. Modeling the sampler

2. Modeling the zero-order hold

Represent D/A converter by zero-order hold equivalent

Samples input level and holds for sampling period T

Zero-order hold circuit represented by continuous system transfer

function in s-domain

EEE342/ETE418_L10

Modeling the sampler

Dr. Abdur Razzak

Model 1:

A switch turning on and off

at a uniform sampling rate

Model 2:

A product of the

time waveform to

be sampled, f(t)

and a sampling

function, s(t)

EEE342/ETE418_L10

Modeling the sampler (contd..)

Dr. Abdur Razzak

EEE342/ETE418_L10

Modeling the sampler (contd..)

Dr. Abdur Razzak

Thus, the sampler is divided into two parts: (1) an ideal sampler described by

the portion of above equation (the sum) that is not dependent upon the

sampling waveform characteristics, and (2) the portion dependent upon the

sampling waveform's characteristics, TW.

EEE342/ETE418_L10

Modeling the zero order hold

Dr. Abdur Razzak

Following figure summerizes the zero-order-hold which is to

hold the last sampled value of f(t).

If we assume an ideal sampler (TW = 1), then f*(t) is represented

by a sequence of delta functions.

EEE342/ETE418_L10

Modeling the zero order hold (contd..)

Dr. Abdur Razzak

The zero-order hold yields a staircase approximation to f(t).

Hence, the output from the hold is a sequence of step functions

whose amplitude is f(t) at the sampling instant, or f(kT).

The Laplace transform of a unit impulse or delta function input is

unity. Since a single impulse from the sampler yields a step over

the sampling interval, the Laplace transform of this step, Gh(s),

which is the impulse response of the zero-order hold, is the

transfer function of the zero-order hold.

Using an impulse at zero time, the transform of the resulting step

that starts at t = 0 and ends at t = T is

1 e Ts

Gh (s ) =

s

EEE342/ETE418_L10

Modeling the zero order hold (contd..)

Dr. Abdur Razzak

1 e Ts

Gh (s ) =

s

EEE342/ETE418_L10

The z-transform

Dr. Abdur Razzak

We have

f * (t ) =

f (kT ) (t kT )

k =

Taking the Laplace

F * (s ) = f (kT )e kTs

k =0

Then, the z-transform

F ( z ) = f (kT )z k

*

k =0

Relationship b/w s-plane and z-plane

z=e

sT

EEE342/ETE418_L10

Example-1

Dr. Abdur Razzak

Find the z-transform of f (kT ) = u (kT )

F ( z ) = f (kT )z k

k =0

= z k

k =0

( )

= z

1 k

k =0

1

1 z 1

z

=

z 1

=

Example-2

EEE342/ETE418_L10

Dr. Abdur Razzak

Find the z-transform of f (kT ) = kT

F ( z ) = f (kT )z

k =0

= kTz

k =0

= T z 1 + 2 z 2 + 3 z 3 +

= T kz k

k =0

zF ( z ) = T 1 + 2 z 1 + 3 z 2 +

(1)

(2)

Subtract (1) from (2)

zF ( z ) F ( z ) = T 1 + z 1 + z 2 +

=>

(z 1)F (z ) = T (1 + z

=>

Tz

Tz

=

F (z ) =

(z 1)(z 1) (z 1)2

+z

T

+ =

1 z 1

EEE342/ETE418_L10

Some common z-transform

Dr. Abdur Razzak

EEE342/ETE418_L10

Inverse z-transform

Dr. Abdur Razzak

Find the inverse z-transform of F (z ) =

0.5 z

(z 0.5)(z 0.7 )

0. 5

F (z )

=

(z 0.5)(z 0.7 )

z

2.5

2.5

=

(z 0.7 ) (z 0.5)

F (z ) =

2.5 z

2. 5 z

(z 0.7 ) (z 0.5)

f (kT ) = Z 1 [F ( z )] = 2.5(0.7 ) 2.5(0.5)

k

EEE342/ETE418_L10

Sampled data system

Dr. Abdur Razzak

Continuous

Sampled

input

Sampled

input & output

EEE342/ETE418_L10

Example-3

Dr. Abdur Razzak

Find the sampled data transfer function for the cascaded system. Given that T=0.5.

1 e Ts

Gh (s ) =

s

s+2

s +1

1 e Ts s + 2

s+2

Ts

= 1 e

G (s ) =

= G1 (s ) G2 (s )

s

s +1

s (s + 1)

z 1

G1 (z ) = 1 z =

z

1

1

2

kT

t

g 2 (t ) = L[G2 (s )] = L

=

e

2

(

)

=>

g

kT

=

2

e

2

s s + 1

2z

z

z

z

z ( z 0.213)

=

G2 ( z ) = Z [g 2 (kT )] =

T

0.5

(z 1)(z 0.6)

z 1 z e

z 1 z e

z 0.213

G ( z ) = G1 ( z )G2 ( z ) =

z 0.6

EEE342/ETE418_L10

Block diagram reduction

Dr. Abdur Razzak

EEE342/ETE418_L10

Example-4

Dr. Abdur Razzak

Find the z-transform of the system shown in Figure below.

Solution:

EEE342/ETE418_L10

Example-4 (contd..)

Dr. Abdur Razzak

EEE342/ETE418_L10

Stability

Dr. Abdur Razzak

In s-domain, system is stable if poles lie in left-hand plane.

In z-domain, system is stable if poles enclosed by unit circle.

Example-5

EEE342/ETE418_L10

Dr. Abdur Razzak

Determine the range of sampling interval, T, that will make the

system shown in figure stable.

Solution:

1 e Ts 10

G (s ) =

= 10 1 e Ts

s

s +1

z

z 1 z

z

z

z 1 z e T = 10 z z 1 z e T

( )

10(1 e )

=

G ( z ) = 10 1 z

z e T

1

1

s s + 1

EEE342/ETE418_L10

Example-5 (contd..)

Dr. Abdur Razzak

G(z )

10 1 e T

Closed loop transfer function: T ( z ) =

=

1 + G ( z ) z 11e T 10

Pole of the system:

11e T 10

For stability the poles of T(z) will be inside the unit circle.

For 11e T 10 = +1 , T = 0

T

For 11e 10 = 1 , T = 0.2

Therefore for stable system the range of sampling interval will be

0 < T < 0.2

EEE342/ETE418_L10

References

Dr. Abdur Razzak

1. Norman S Nise, Control System Engineering, John Wiley &

Sons, 5th Ed., pp. 692749.

EEE342/ETE418_L10

Next.

Good Luck

To

Final Exam

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Cny 17Document9 pagesCny 17Krista TranNo ratings yet

- i5/OS Commands ExplainedDocument18 pagesi5/OS Commands Explainedrachmat99No ratings yet

- How To Encipher and Decipher Codes Using The Hill 2-CipherDocument17 pagesHow To Encipher and Decipher Codes Using The Hill 2-CipherHaftamuNo ratings yet

- Stability Study With SAP Quality ManagementDocument48 pagesStability Study With SAP Quality ManagementRahulNo ratings yet

- E Business, E Commerce and M CommerceDocument19 pagesE Business, E Commerce and M CommerceMonir BhuiyanNo ratings yet

- ZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFDocument48 pagesZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFSebastian StanacheNo ratings yet

- Rony Das CV New E-MailDocument3 pagesRony Das CV New E-Mailrony_27No ratings yet

- Data WarehousingDocument24 pagesData Warehousingkishraj33No ratings yet

- Apollo Training Guidance and Control 02-10-67Document176 pagesApollo Training Guidance and Control 02-10-67sn_crowley9661No ratings yet

- NT 7G Med 11 2021 GB JED1Xy9Document12 pagesNT 7G Med 11 2021 GB JED1Xy9Ricardo LangerNo ratings yet

- Riaz Ahmad: Advisory Software Engineer (Oracle EBS) at Systems LimitedDocument9 pagesRiaz Ahmad: Advisory Software Engineer (Oracle EBS) at Systems Limitedriazahmad82No ratings yet

- Neural Network in MATLABDocument52 pagesNeural Network in MATLABBang Kosim100% (6)

- BUMA 30063 Fundamentals of Descriptive Analytics: Compiled By: Mr. Rogene C. EsguerraDocument62 pagesBUMA 30063 Fundamentals of Descriptive Analytics: Compiled By: Mr. Rogene C. EsguerraJuliana Maaba Tay-isNo ratings yet

- Cisco VPN Client Administrator GuideDocument226 pagesCisco VPN Client Administrator GuideLong NguyễnNo ratings yet

- High Performance Hmi Scada Improves Efficiency Ge DecemberDocument53 pagesHigh Performance Hmi Scada Improves Efficiency Ge DecemberAnh Tuan Nguyen100% (1)

- HOCHIKI UL CatalogueDocument16 pagesHOCHIKI UL Cataloguearyan sharmaNo ratings yet

- Merchandise Distribution - EN - CUST - V147Document51 pagesMerchandise Distribution - EN - CUST - V147gergoNo ratings yet

- AG-HMR10 Operating ManualDocument106 pagesAG-HMR10 Operating ManualbrittanylbrothersNo ratings yet

- 1997 Vol 23 No 2 1001 AbstractDocument1 page1997 Vol 23 No 2 1001 AbstractFatih KantaşNo ratings yet

- Mobile Cloud ToolsDocument11 pagesMobile Cloud ToolsRomarMroNo ratings yet

- Activity-Based Costing: Questions For Writing and DiscussionDocument42 pagesActivity-Based Costing: Questions For Writing and DiscussionMaria Sarah SantosNo ratings yet

- Arduboy API ReferenceDocument72 pagesArduboy API ReferencejossjxmNo ratings yet

- ZTE Cam PDFDocument2 pagesZTE Cam PDFmarsudi.kisworo7533No ratings yet

- Cryptography Networks and Security SystemsDocument42 pagesCryptography Networks and Security Systemspokemonlover14116666No ratings yet

- 01 - Failure Analysis of A Special Vehicle Engine Connecting RodDocument12 pages01 - Failure Analysis of A Special Vehicle Engine Connecting RodBima SorayaNo ratings yet

- Making a Python list of namesDocument14 pagesMaking a Python list of namesSoniaNo ratings yet

- Cisco Aironet 1140 Series Getting Started GuideDocument34 pagesCisco Aironet 1140 Series Getting Started GuideDmitryNo ratings yet

- Manual Técnico Micros ES Raa033benDocument264 pagesManual Técnico Micros ES Raa033benrafael amancioNo ratings yet

- Invoice ApprovalDocument54 pagesInvoice ApprovalHamada Asmr AladhamNo ratings yet

- ColdFusion11 DevelopingDocument2,080 pagesColdFusion11 DevelopingApopii DumitruNo ratings yet