Professional Documents

Culture Documents

Vlsi Deg 2016-Hout

Uploaded by

Gibin GeorgeCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vlsi Deg 2016-Hout

Uploaded by

Gibin GeorgeCopyright:

Available Formats

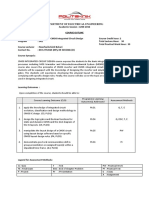

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

(PILANI, KK BIRLA GOA & HYDERABAD CAMPUS)

INSTRUCTION DIVISION

FIRST SEMESTER 2016-2017

Course Handout

Date: 01/08/2016

In addition to Part I (General Handout for all courses appended to the time table) this portion gives further

specific details regarding the course.

Course No.

: MEL G621

Course Title

: VLSI DESIGN

Instructors

: S.Gurunarayanan, Soumya J Pravin Mane,

Instructor (Practical)

: Kavindra Kandpal

1.

Scope and Objective of the Course:

The objective of this course is to understand different design principles used in the Design of Digital

VLSI Circuits & Systems using nMOS and CMOS with emphasis on for high performance

computing. VLSI design activity will be understood by Synthesis and then Analysis at several

successive levels of design abstraction.

The broad topics of coverage includes Principles of operations of CMOS transistors used as a digital

switch and various other topologies used in Digital VLSI Design, Logic implementation strategies and

performance characterization of the VLSI circuits, Low Power Design, different clocking strategies,

symbolic layout systems, CMOS subsystems design and Memory modules.

2.

Student Learning Outcomes.

Design digital blocks using CMOS logic through static logic and dynamic logic design

approaches.

Compare different Digital VLSI Design methods using set of Performance metrics.

Create Layouts of Different functional blocks

Extraction of Interconnect Parasitic and iterate the design to meet the defined performance

metrics.

Design of Digital subsystem and Memory modules

3.

Text Books

(a) Essential of VLSI Circuits and Systems

Author: Kamaran Esharaghian, Dauglas A, Puecknell Sholen Eshraghian Publisher: PHI.2009

(b) CMOS Digital Integrated Circuit, Analysis and Design, Sung-Mo Kang and Yusuf Leblebici,

Publisher: McGraw- Hill Companies, Inc.2003

4.

Reference Books

(a) Digital Integrated Circuits: A Design Perspective Author: Jan Rabey , Prentice Hall, 2005

5.

Course Plan

No of

Lect.

Topic To be Covered

Learning Objectives

Introduction

Overview of Digital VLSI Design

Methodologies

Introduction to MOS Physics

Basic Electrical Properties of MOS

Devices

Ref. to Text

Book

Chapter-I (T2)

2.2(T1),

3.1,

3.2, 3.3(T2)

5.

2.1,

2.3(T1);3.4(T2)

Device Characteristics

Understanding Drain-to-Source Current

versus Voltage relationships

Static NMOS/CMOS inverter:

voltage-transfer characteristics

Voltage Transfer Characteristics of

CMOS Inverters; Performance measure

of CMOS Inverters

MOS Capacitances, Dynamic

Behavior of MOS Inverters

Capacitances associated with CMOS

devices and switching characteristics of

CMOS inverters

4.6;4,7(T1)

Chapter 6 (T2)

CMOS Process Technology ,

Layout and Design Rules

CMOS Fabrication steps, Stick

Diagrams and Layout Design rules

Chapter 3 ( T1)

2

1

Scaling of MOS Devices

Constant Voltage Scaling; Full Scaling;

Short channel and narrow channel

effects

Chapter 5 (T1)

Combinational CMOS logic

circuit :staticlogic ; optimisation

for speed, method of logical

effort ; Euler diagrams ; Ratioed

logic, pseudo-NMOSlogic; Pass

transistor logic

Building blocks for combinational

logic; Examples of structured logic

design; Different Design styles;

subsystem design

6.2-6.4,(T1)

Chapter 7( T2);

InterConnect Parasitics

Understanding Interconnect

Capacitances, Resistance, Delay

models

4.2-4.10(T1)

6.5-6.7 ( T2)

CMOS

Design:,

Design of Flip-flops; Latches &

registers

Dynamic and Domino Logic

Design

Dynamic CMOS Circuit techniques;

Dynamic latches & Registers; NORA

logic, Pipelining Approach.

Clocking Strategies

Synchronous design, timing metrics,

PLDs and FPGA based design

PAL and PLA design, Blocks of FPGAs

Adder architectures

Adders, Multipliers & Shifter Design

8.4-8.5(T1);

Chapter 11( R1)

Aspects of Memory design

Design of SRAM, DRAM, decoders,

sense amplifiers

Chapter 9 (T1);

Chapter 10(T2)

Chip I/O Circuits

ESD Protection Circuits, Input Output

circuits

Chapter13(T2)

VLSI Lab

Sequential

logic

2.4; 2.6; 2.10

(T1), Chapter 4

(T2), Chapter 5

( R1)

6.5-6.6(T1)

Chapter 7(R1)

6.6 ( T1)

Chapter 7(R1)

Chapter 9 ( T2)

11.5(T1); 10.110.2(R1)

Study Material

Topics

No of Cycles (3hr/cycle)

Circuit Simulation

Schematic Entry

Circuit Extraction

Layout Design

DRC, LVS, Parasitic extraction

Post Layout Simulation

3

2

1

2

2

Note: Course project involves complete implementation of a block designed for minimum area and

delay while meeting a set of defined constraints (noise margins and capacitances etc)

6. Evaluation Schedule

Component

Mid semester Test

Duration

90 min

Marks

20

Date & Time

To be announced

Class

Assignments/Lab/

Design Project

Weekly

schedule will

be announced

40

Comp. Exam

3 Hours

40

Spread across the

semester.

Details will be

announced.

03/12/16,

9AM 12 noon

Total

Venue

To be

announced

Remarks

CB

-

--

To be

announced

CB/OB

100

7. Chamber consultation hour: Will be announced

8. Notices: EEE Notice Boards in respective campuses..

(Instructor-in charge)

MEL G621

You might also like

- 100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and AnswersDocument12 pages100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and AnswersSharanya50% (2)

- MA5694 & MA5698 V800R313C00 Product DescriptionDocument44 pagesMA5694 & MA5698 V800R313C00 Product Descriptiongold kingNo ratings yet

- Fundamentals of CMOS VLSI (Complete Notes) PDFDocument214 pagesFundamentals of CMOS VLSI (Complete Notes) PDFENG18EC0062-MD TANVEERNo ratings yet

- 05 MSOFTX3000 Local Office Data Configuration ISSUE 1.2Document45 pages05 MSOFTX3000 Local Office Data Configuration ISSUE 1.2Amin100% (8)

- Lpvlsi Full TBDocument417 pagesLpvlsi Full TBKandikattu Abhilash100% (3)

- Modeling and Simulation Support for System of Systems Engineering ApplicationsFrom EverandModeling and Simulation Support for System of Systems Engineering ApplicationsLarry B. RaineyNo ratings yet

- VLSI Design Syllabus - 2018 SchemeDocument2 pagesVLSI Design Syllabus - 2018 SchemeShivansh BhartiNo ratings yet

- Vlsi PT 1st Year SyllabusDocument17 pagesVlsi PT 1st Year SyllabusMANGAL KUMAR MOHAPATRANo ratings yet

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Document2 pagesEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaNo ratings yet

- Syllabus VLSI Technology ApplicationsDocument2 pagesSyllabus VLSI Technology ApplicationsPrajwalAgarwalNo ratings yet

- 17ec63 Vlsi Design SyllabusDocument2 pages17ec63 Vlsi Design SyllabusKulandaivel MurugeshNo ratings yet

- BECE303LDocument3 pagesBECE303LKAVIYA DIASNo ratings yet

- Syllabus Vls Technology ApplicationsDocument2 pagesSyllabus Vls Technology ApplicationsPrajwalAgarwalNo ratings yet

- Scope and Objective of The CourseDocument3 pagesScope and Objective of The CourseNitu SharmaNo ratings yet

- VLSI DesignDocument1 pageVLSI Designडाँ सूर्यदेव चौधरीNo ratings yet

- VLSI DesignDocument4 pagesVLSI DesignHacraloNo ratings yet

- Course Plan VLSI Design July 2013Document4 pagesCourse Plan VLSI Design July 2013HacraloNo ratings yet

- VLSI ModulesDocument28 pagesVLSI Modulessai_karthik89No ratings yet

- 18EC 7th Semester SylabusDocument54 pages18EC 7th Semester Sylabusneelambika nsNo ratings yet

- Ecsyll 2018 Schmeme 7&8 SemDocument42 pagesEcsyll 2018 Schmeme 7&8 Semvadla77No ratings yet

- Instructor-in-Charge: (Section - 1)Document70 pagesInstructor-in-Charge: (Section - 1)ravi3192No ratings yet

- Vlsi SyllabusDocument2 pagesVlsi SyllabusAkhil NameirakpamNo ratings yet

- Low-Power VLSI Circuits and SystemsDocument33 pagesLow-Power VLSI Circuits and SystemsSYAMALANo ratings yet

- Vlsi DesignDocument2 pagesVlsi DesignShribala NagulNo ratings yet

- CoursePlan EEE4025 SJDocument3 pagesCoursePlan EEE4025 SJShahid JamanNo ratings yet

- Vlsi DesignDocument3 pagesVlsi DesignGokulNo ratings yet

- 21ec503 Vlsi Design Unit 1Document110 pages21ec503 Vlsi Design Unit 1santhoshiniNo ratings yet

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 pagesNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNo ratings yet

- EC NotesDocument2 pagesEC Noteshanumantha12No ratings yet

- Fundamentals of CMOS VLSI 10EC56Document214 pagesFundamentals of CMOS VLSI 10EC56Santhos KumarNo ratings yet

- VLSI Technology and DesignDocument2 pagesVLSI Technology and DesignJigar PatelNo ratings yet

- UTM Course SynopsesDocument14 pagesUTM Course SynopsesSaravanan KerishnanNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument122 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- Gujarat Technological University: W.E.F. AY 2018-19Document3 pagesGujarat Technological University: W.E.F. AY 2018-19bakoliy218No ratings yet

- UntitledDocument2 pagesUntitledDr. M Kiran KumarNo ratings yet

- Syllabus 5th SemDocument17 pagesSyllabus 5th Semsayan.transcuratorsNo ratings yet

- Applied Electronics and InstrumentationDocument192 pagesApplied Electronics and InstrumentationSHINUMMNo ratings yet

- SIDDUDocument7 pagesSIDDUboogeyman19980No ratings yet

- ME8791 Mechatronics Course FileDocument22 pagesME8791 Mechatronics Course FileRajasekaran RNo ratings yet

- Me Vlsi Sem IiDocument12 pagesMe Vlsi Sem IiRockymoorthiNo ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- Ece MT SylDocument79 pagesEce MT Sylpermiable permissionNo ratings yet

- EC6601 VLSI Lesson PlanDocument7 pagesEC6601 VLSI Lesson PlanDsce CoimbatoreNo ratings yet

- Ec 544Document2 pagesEc 544Surbhi SinghNo ratings yet

- Ec6601 Vlsi DesignDocument1 pageEc6601 Vlsi DesignBABU MNo ratings yet

- ME (Updated)Document2 pagesME (Updated)AanjanayshatmaNo ratings yet

- Analog & Digital VLSI Design Handout - RevisedDocument3 pagesAnalog & Digital VLSI Design Handout - RevisedB Naresh Kumar ReddyNo ratings yet

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedDocument37 pagesVTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedAshik PadmanabhaNo ratings yet

- 6th Sem SyllabusDocument13 pages6th Sem SyllabusAbhishek GuptaNo ratings yet

- DEE6113 Course Outline Jun2016Document4 pagesDEE6113 Course Outline Jun2016FonzBahariNo ratings yet

- Pw1 Cmos Daniel f1070Document9 pagesPw1 Cmos Daniel f1070iskandardaniel0063No ratings yet

- Question Bank - 6thsem: Mission and Vision of The DepartmentDocument28 pagesQuestion Bank - 6thsem: Mission and Vision of The Department1232023No ratings yet

- 3-2 Syllabus (1) - MergedDocument14 pages3-2 Syllabus (1) - Mergededucational9hubNo ratings yet

- Nirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VDocument15 pagesNirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VPragya jhalaNo ratings yet

- VLSI Technology and DesignDocument3 pagesVLSI Technology and DesignSachin JoshiNo ratings yet

- Department of Computer Science Vidyasagar University: Paschim Medinipur - 721102Document26 pagesDepartment of Computer Science Vidyasagar University: Paschim Medinipur - 721102Venkat GurumurthyNo ratings yet

- Digital SystemsDocument390 pagesDigital SystemsKetan PandeyNo ratings yet

- Signature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009Document48 pagesSignature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009vickyskarthikNo ratings yet

- Vlsi SyllabusDocument3 pagesVlsi SyllabusmadhurNo ratings yet

- EC8095-VLSI Design - 01 - by WWW - LearnEngineering.inDocument134 pagesEC8095-VLSI Design - 01 - by WWW - LearnEngineering.inDelphin ShibinNo ratings yet

- 7.pyaar Toh Andha HaiDocument1 page7.pyaar Toh Andha HaiKiran KumarNo ratings yet

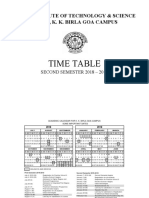

- Time Table Semester II 2018-19-4 Jan 19Document50 pagesTime Table Semester II 2018-19-4 Jan 19Gibin GeorgeNo ratings yet

- Xup Building Basic Elements LabDocument18 pagesXup Building Basic Elements LabGibin GeorgeNo ratings yet

- Mtech Embedded SyllabusDocument6 pagesMtech Embedded SyllabusGibin GeorgeNo ratings yet

- An 10441Document7 pagesAn 10441Anonymous EaHxdJwNo ratings yet

- I2C Bus Pullup Resistor CalculationDocument5 pagesI2C Bus Pullup Resistor Calculationalaki1000No ratings yet

- Atmega162 CompDocument1 pageAtmega162 CompGibin GeorgeNo ratings yet

- Nano CatalogDocument55 pagesNano CatalogGibin GeorgeNo ratings yet

- Atmega162 BotDocument1 pageAtmega162 BotGibin GeorgeNo ratings yet

- GSM Based Automatic LPG Ordering System With Leakage AlertDocument3 pagesGSM Based Automatic LPG Ordering System With Leakage AlertInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Design and Construction of A GSM Based Gas Leak Alert SystemDocument6 pagesDesign and Construction of A GSM Based Gas Leak Alert SystemGibin GeorgeNo ratings yet

- Data Benchmarking: (RF) Connection Accessibility Task RetainabilityDocument2 pagesData Benchmarking: (RF) Connection Accessibility Task RetainabilityBonar SianiparNo ratings yet

- Binary & Logic OperationDocument16 pagesBinary & Logic OperationEssamNo ratings yet

- EV ProSound Speaker and Electronics FullCatalog - LR-spreadDocument40 pagesEV ProSound Speaker and Electronics FullCatalog - LR-spreadgreggles69No ratings yet

- Accessories: Test and Training Set Switchgear SimulatorDocument4 pagesAccessories: Test and Training Set Switchgear SimulatorJoseph KrauseNo ratings yet

- Motherboard ASUS IPIBL-SIDocument24 pagesMotherboard ASUS IPIBL-SIZen_JLNo ratings yet

- Mi Bluetooth Speaker enDocument1 pageMi Bluetooth Speaker enWeronika DeNo ratings yet

- MEC522 PBL - ArduinoDC - MotorEncoder - Close LoopDocument3 pagesMEC522 PBL - ArduinoDC - MotorEncoder - Close Loopzaiful hakimNo ratings yet

- LTE Network Architecture - BasicDocument9 pagesLTE Network Architecture - BasicTELECOM INJINIYANo ratings yet

- T89C51CC01 CAN Bus Programming and Simulation APNT - 165: Application NoteDocument10 pagesT89C51CC01 CAN Bus Programming and Simulation APNT - 165: Application NoteDeena DayalanNo ratings yet

- Mindwave Mobile & ArduinoDocument12 pagesMindwave Mobile & ArduinoMuhammad Shafiq Abdul KarimNo ratings yet

- Linksys Spa9000 Solution GuideDocument9 pagesLinksys Spa9000 Solution GuideJuan Carlos LunaNo ratings yet

- Module-Hands Free C1Document2 pagesModule-Hands Free C1Halit KorpeNo ratings yet

- Um IcrDocument78 pagesUm Icrklx12No ratings yet

- LNA DesignDocument10 pagesLNA Designkrishnak_ece7077No ratings yet

- Technical Product Guide: Tricon SystemsDocument78 pagesTechnical Product Guide: Tricon SystemsAngela FasuyiNo ratings yet

- 02 - 202-203 DC ContactorDocument2 pages02 - 202-203 DC Contactorshailesh284No ratings yet

- 02-02 The Benefits of SAN and NAS Storage PDFDocument18 pages02-02 The Benefits of SAN and NAS Storage PDFJosecriz DalmacioNo ratings yet

- JVC Kw-nx7000 Series Navigation DVD Receiver SMDocument81 pagesJVC Kw-nx7000 Series Navigation DVD Receiver SMsmesh555100% (1)

- How PLC Reads The Data From Field TransmittersDocument5 pagesHow PLC Reads The Data From Field TransmitterslampfievNo ratings yet

- Pioneer 1005 SMDocument22 pagesPioneer 1005 SMe2140r03No ratings yet

- Lab Manual: Electric Circuit Analysis I EEE-121Document22 pagesLab Manual: Electric Circuit Analysis I EEE-121earn moneyNo ratings yet

- Getting Started Wp-8xx7Document199 pagesGetting Started Wp-8xx7Pedro BortotNo ratings yet

- DHI-KTA02: Video Intercom KitDocument2 pagesDHI-KTA02: Video Intercom KitÁngel GóticoNo ratings yet

- AN15932AADocument1 pageAN15932AARicardo Banegas ValleNo ratings yet

- General Purpose 6-Pin Photodarlington Optocouplers: 4N29 4N30 4N31 4N32 4N33Document8 pagesGeneral Purpose 6-Pin Photodarlington Optocouplers: 4N29 4N30 4N31 4N32 4N33Millenium AssisNo ratings yet

- Vibro-Acoustic Method For OLTC TestingDocument15 pagesVibro-Acoustic Method For OLTC TestingWisnu DewaNo ratings yet

- Mantra Product CatalogueDocument2 pagesMantra Product CatalogueMearish ThomasNo ratings yet