Professional Documents

Culture Documents

Phase Locked Loop Based On Adaptive Observer

Uploaded by

ロサレスアヤラ キンOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Phase Locked Loop Based On Adaptive Observer

Uploaded by

ロサレスアヤラ キンCopyright:

Available Formats

International Review of Electrical Engineering (I.R.E.E.), Vol. xx, n.

Phase Locked Loop based on adaptive observer.

R. C. Martnez-Montejano1, R. Castillo Meraz2, R.E. Lozoya-Ponce3, I. Campos-Cantn4,

M.F. Martnez-Montejano5, R.O. Lozoya Ponce6.

Abstract A phase Locked Loop is a control system that generates an alternating signal with a

bounded phase respect to an input signal, a feedback loop makes a comparison between these two

signals and modifies its output signal frequency. This paper presents a PLL scheme which is aimed

to estimate the angular frequency of the input voltage as well as a low pass filter function for

cleaning this distorted signal. A prototype based on operational amplifiers has been built and

simulations and experimental results are presented to prove its performance. Copyright 2014

Praise Worthy Prize S.r.l. - All rights reserved.

Keywords: adaptive law, harmonic oscillator, Lyapunov approach, PLL, operational amplifier.

Nomenclature

PLL

AC

VCO

Op. Amp.

S

0

Phase locked loop

Alternating Current

Voltage controller oscillator

Operational amplifier

A proportional signal is produced from the difference

between 1 and 2 signals, by the phase comparator,

Utility voltage

Fundamental frequency

and

Auxiliary signal

Square of the fundamental frequency

Positive design parameter

Adaptation gain

Infinite norm

Signal reconstruction of

Estimate of

Estimate of

Estimate of

S S

Error signal given by

Error signal given by

Error signal given by

Quadratic storage function of Lyapunov

I.

Fig. 1. PLL general diagram.

Introduction

In general, a phase locked loop (PLL) is a control

system that generates an AC signal, usually a sinusoidal

signal, coming out of an oscillator, which is compared to

a reference signal with the idea of locking both frequency

and phase shift. The general scheme is depicted in Fig. 1.

Manuscript received January 2014

is generated by a VCO. The VCO input comes

from the amplified phase comparator output signal and a

voltage c . Finally the VCO produces a linearly varying

output regarding

c .

PLL is a fundamental component for several

applications in the areas of signal processing at

communication systems, instrumentation, automatic

control, power electronics, electronic machines and

power systems [1]. The most of power electronics

applications demand synchronization with respect to the

utility voltage phase angle and normally is estimated by

PLL algorithms [2]-[7]. The phase, amplitude and

frequency detection of the utility grid are critical

information for the control of distributed generation and

storage systems, flexible AC transmission systems,

power line conditioners, uninterruptible power supplies,

[8]-[9], and other grid connected power conditioning

equipments.

Many phase angle and/or frequency detection

algorithms have been proposed for synchronizing the

PLL output signals with respect to the fundamental

component of the single phase utility voltage [10]-[14].

Regardless of the PLL technique used in system

detection, the amplitude and the phase must be fast and

accurately obtained, even if the utility voltage is

distorted.

In this paper a PLL scheme is presented which is

aimed to estimate the angular frequency of the utility

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

R.C. Martnez-Montejano, R. Castillo-Meraz, R.E. Lozoya-Ponce

voltage as well as a cleaned version of the distorted input

voltage. The proposed scheme delivers the estimates of

both angular frequency and utility voltage and the time

derivative of the voltage; these signals are useful in many

applications. The mathematical model based on adaptive

observer is presented on section two; then in section

three, simulations via PSCAD and MULTISIM were

depicted; section four, physical implementation through

the op. amp. is shown, and finally on section five the

conclusions are given.

II.

Mathematical Model

Where

The idea behind of the proposed PLL design consists

in:

1) Propose a model that accurately reproduces the

utility voltage. For this purpose is considered the

model of the input signal as a harmonic oscillator

in which is assumed that only the parameter

S (t ) , as a time varying signal, is available.

2) Based on the proposed model, an estate estimator is

designed to reconstruct S and its time

derivative. The estate estimator is built as a copy

of the model with an additional damping.

3) As the estimator expression involves the angular

frequency, an adaptation law is proposed

following the Lyapunov approach.

Consider that the generator of the input signal is a

harmonic oscillator with the following form:

S 0

S

Where

(1)

represents the fundamental frequency,

is a time varying signal, and

(8)

S S S ; S

, respectively;

and

are estimates of

is the estimate of

parameter; and is a positive design parameter used to

introduce the required damping.

Following a Lyapunov approach [15]-[16], an

adaptive law is proposed to reconstruct involved in

(7). For this purpose the following quadratic storage

function [17], is proposed:

S2 2

2

V

2

2 2

(9)

Where , , and 0 is the

adaptation gain.

Its time derivative along the trajectories of the error

model is made negative semi-definite by proposing the

adaptive law:

(10)

(11)

V S2

(12)

is an auxiliary signal

S 0

S

The model that describes the signal generator

and

(7)

S .

It is convenient to define 0 , out of which:

2

0

S

S

(2)

which is in quadrature with respect to

be rewritten using

adaptive estimator, a cleaned version of the grid voltage

can be obtained as well as a fundamental frequency

estimate.

The proposed estimator consists of a copy of the

system model (5) and (6), and a damping term is added,

that is:

(3)

(4)

S , can

, as follows:

S

S

(5)

(6)

Based on (5) and (6), the objective consists in

designing an estate estimator for the variables S and

, and adaptive law to reconstruct parameter (the

square of the fundamental frequency). Out of this

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

This yields:

The stability and convergence study of the proposed

scheme can be completed using Barbalats arguments, or

using the signal properties as follows: from the proposed

adaptive law, all error signals are bounded, i.e. S L ,

L , L ,

equivalently all estimates are

bounded as well, i.e.,

S L , L , L . This

implies that the time derivative of the error is bounded as

well, i.e.,

S L

(or equivalently

S L ). As S

is

continuous and bounded, and based on the fact that

S L2

L , then S 0 and S 0 as t .

0 as

(or equivalently ) go to

This implies, in their turn, that

t and thus and

and

International Review of Electrical Engineering, Vol. xx, n.

x

R.C. Martnez-Montejano, R. Castillo-Meraz, R.E. Lozoya-Ponce

constant values. Considering

S 0 ,

then from the

error model, , however, is a time

varying periodic signal, and thus the only point where

is a constant is at

0 , and 0

as well,

then 0 and , and if 0 then 0 .

Summarizing, the proposed PLL consists of the

estimator (5) and (6), plus the adaptive law (10) and (11).

A block diagram of the proposed PLL algorithm is

depicted in Fig. 2.

Fig. 2. PLL block diagram.

III. Numerical Results

Fig. 4 PLL response when the utility is a square signal.

The PLL algorithm developed can be implemented

through the op. amp., across adder inverter, inverter

integrator, logarithmic and exponential configurations, as

shown in Fig 5, where the Multiplier block consist of the

sum of two logarithmic configurations and then apply the

exponential configuration, in order to obtain

multiplication of the signals. Simulations were carried

out on MULTISIM, in Fig. 6 the input-output signal

when the utility is a sinusoidal signal of 1 V amplitude

with change from 60 to 150 Hz is shown.

In order to validate the PLL algorithm, numerical

results using PSCAD 3.0 have been carried out, where

S is a sinusoidal signal of 120V amplitude. On Fig. 3

the response input-output when the utility is changed in

step from 120 to 60 Hz is depicted.

Fig 5. PLL block diagram with Op. Amp.

Fig 6. PLL response when utility is change from 60 to 150 Hz.

Fig. 3. PLL response when utility frequency is changed.

Then in Fig. 7 the input versus output is depicted to

prove the similarity between these two signals when the

utility is a 60 Hz sinusoidal signal of 1 V amplitude.

Then in Fig. 4 the input-output response with a zoom

is shown, when S is changed for a 5V square signal

with a frequency of 60 Hz.

Fig. 7. Input versus Output signal.

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

International Review of Electrical Engineering, Vol. xx, n.

x

R.C. Martnez-Montejano, R. Castillo-Meraz, R.E. Lozoya-Ponce

IV. Experimental results.

The proposed PLL algorithm was implemented

physically across basic components as op. amps,

resistors, capacitors and diodes.

A Rigol signal generator was used as the input signal,

in Fig. 8 the output signal when the input is changed

from 120 to 60 Hz utilizing a Rigol oscilloscope is

observed. The PLL algorithm proves to correctly follow

the signal instantaneously, despite the change of

frequency.

Fig 10. Circuit performance when the input is contaminated with

noise.

Finally the Fig 11 depicts the XY plot of the input

signal versus the output signal. The response observed in

the figure shows the similarity between the two signals.

Fig 8. PLL response when the input is change from 120 to 60 Hz.

Then, in figure 9, the PLL response when the input

signal goes from sinusoidal signal to a square signal, is

depicted. The PLL algorithm proposed shows a good

synchronization under an abrupt change of signal.

Fig 11. The XY plot of input signal versus output signal.

V.

Conclusions

In this paper a PLL scheme was presented, which was

aimed to estimate the fundamental frequency, and both

source voltage and its time derivative. The design

process considered the model of the input signal as a

harmonic oscillator in which it was assumed that only the

signal S (t ) was available. Based on the proposed

Fig 9. PLL response when the input signal goes from sinusoidal

signal to square signal.

The Fig. 10 shows the circuit performance when a 100

mV sinusoidal signal with 20 mV noise amplitude is used

as the input signal. The PLL response, exhibit a clean

version of the input signal and proves its performance as

a filter.

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

model, a state estimator was designed to reconstruct a

copy of such input signal. The state estimator was built

as a copy of the model with additional damping. An

adaptation law was incorporated to reconstruct the

angular frequency.

Numerical results were carried out in which were

shown robustness of the PLL scheme under frequency

changes and square input signal.

Then the proposed PLL scheme was implemented

physically through the op. amp. to prove the circuit

International Review of Electrical Engineering, Vol. xx, n.

x

R.C. Martnez-Montejano, R. Castillo-Meraz, R.E. Lozoya-Ponce

performance. The system exhibit the capacity to lock the

frequency and follow a signal even if is disturbed.

The implementation with Op. Amp. can carry some

problems such as limited bandwidth by frequency

response. Besides exists the possibility of saturation in

the control gains on both digital and analog way, limiting

the response of PLL algorithm proposed. The gain can

become very large and saturates the integrator.

Acknowledgements

[14] S. A. O. Silva, R. Novochadlo, R. A. Modesto, Single Phase PLL

Structure Using Modifies p-q Theory for Utility Connected

Systems, Proceedings of IEEE Power Electronics Specialists

Conference, 2008, pp. 4706-4711.

[15] M. Hamouda, F. Fnaiech, K. Al-Haddad, Modeling and Adaptive

Control of Two-Stage Matrix Converters, International Review of

Electrical Engineering, IREE, vol. 3, 2008, pp. 83-92.

[16] M. Ovassaid, M. Moaroufi, M. Cherkaovi, Decentralized

Nonlinear Adaptive Control and Stability Analysis of

Multimachine Power System, International Review of Electrical

Engineering, IREE, vol. 5, 2010, pp. 2754-2763.

[17] Fang Shi, Jie Wang, Hamilton Energy Theory based Coordinated

Control of Generator Excitation and TCSC, International Review

of Electrical Engineering, IREE , vol. 7, 2012, pp. 3401-3407.

This work was supported by CONACyT through

scholarship of Ph.D. 290783.

References

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

M. Karimi-Ghartemani, Linear and Pseudolinear Enhanced

Phased-Locked Loop (EPLL) Structures, IEEE Transactions on

Industrial Electronics, vol. 61, n. 3,March 2014, pp. 1464-1474.

S. A. Oliveira da Silva, V. D. Bacon, L. B. Garca-Campanhol, B.

A. Anglico, An Adaptive Phase-Locked Loop Algorithm for

Single-Phase Utility Connected System, Power Electronics and

Applications (EPE), September 2013, pp. 1-10.

L. Wang, Q. Jiang, L. Hong, C. Zhang, Y. Wei, A novel PhaseLocked Loop Based on Frequency Detector and Initial Phase

Angle Detector, IEEE Transactions on Industrial Electronics, vol.

28, n. 10, October 2013, pp. 4538-4549.

J. He, Y. W. Li, F. Bllabjerg, X. Wang, Active Harmonic Filtering

Using Current-Controlled Grid-Connected DG Units With

Closed-Loop Power Control, IEEE Transactions on Industrial

Electronics, vol. 49, n. 2, February 2014, pp. 642-653.

K. J. Lee, J. P. Lee, D. S. Dong-Wook Yoo, H. J. Kim, A novel

Grid Synchronization PLL Method Based on Adaptive Low Pass

Notch Filter for Grid-Connected PCS, IEEE Transactions on

Industrial Electronics, vol. 61, n. 1, January 2014, pp. 292-301.

L. Hadjidemetriou, E. Kyriakides, F. Blaabjerg, An Adaptive

Phase-Locked Loop Algorithm for Faster Fault Ride Throuh

Performance of Interconnected Renewable Energy-Sources,

Energy Conversion Congress and Exposition (ECCE), September

2013.

Y. Park, S. K. Sul, W. C. Kim, H. Y. Lee, Phase Locked Loop

Based on an Observer for Grid Synchronization, IEEE

Transactions on Industry Applications, March 2013.

M. Chichowlas, M. Malinowski, D. L. Szobczuk, M. P.

Kazmierkowski, P. Rodrguez, J. Pou, Active filtering function of

three phase PWM boost rectifier under different line voltage

conditions, IEEE Transactions on Industrial Electronics, vol. 52,

n. 2, April 2005, pp. 410-419.

R. Teodorescu, F. Blaabjerg, Flexible control of small wind

turbines with grid failure detection operating in stand-alone and

grid-connected mode, IEEE Transactions on Power Electronics,

vol. 9, n. 5, September 2004, pp. 1323-1332.

M. Karimi-Ghartamani, M. R. Iravani, A Nonlinear Active Filter

for Online Signal Analysis in Power Systems: Applications, IEEE

Transactions on Power Delivery, vol. 17, n. 2, 2002, pp. 617-622.

S. M. Silva, B. M. Lopes, B. J. Cardoso-Filho, R. P. Campana, W.

C. Boaventura, Performance Evaluation of PLL Algorithms for

Single-Phase Grid-connected systems, Proceedings of 39th

Industry Applications Society Annual Meeting, 2004, pp. 22592263.

R. M. Santos-Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres,

A. F. Souza, Comparison of Three Single-Phase PLL Algortihms

for UPS Applications, IEEE Transactions on Industrial

Electronics, vol. 55, n. 8, 2008, pp. 2923-2932.

S. A. O. Silva, A. Goedtel, C. F. Nascimento, L. B. G.

Campanhol, D. Paiao, A comparative Analysis of p-PLL

Algorithms fos Single-Phase Utility Connected Systems,

Proceedings 13th European Conference on Power Electronics and

Applications, 2009.

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

Authors information

1

Universidad Autnoma de San Luis Potos, rc.montejano@gmail.com

Universidad Autnoma de San Luis Potos.

3

Universidad Autnoma de San Luis Potos.

4

Universidad Autnoma de San Luis Potos.

5

Research and Development Department of Alstom Power.

6

Universidad Autnoma de San Luis Potos.

2

Roberto Carlos Martnez Montejano was

born on San Luis Potos on October of 1988.

He received B.Sc. degree on Electronics

Engineer from Universidad Autnoma de San

Luis Potos (UASLP) on 2010. The M.Sc.

degree from Instituto de Investigacion en

Comunicacin ptica (IICO) in 2012. He

becomes student of Ph.D. in Instituto de

Investigacin en Comunicacin ptica (IICO), with the thesis

"Cogeneration Electric energy with solar systems and multilevel

converters".

He has given several national conferences about electronics and

renewable energy and has won some local competitions about research

projects on rebewable energies. His research includes power

electronics, mathematical modelling and multilevel converters.

M.Sc. Martnez is an IEEE member.

Ral Castillo Meraz was born on San Luis

Potos on November of 1984. He received

B.Sc. degree on Electronics Engineer from

Universidad Autnoma de San Luis Potos

(UASLP) on 2010. The M.Sc. degree from

Instituto de Investigacion en Comunicacin

ptica (IICO) in 2012. He becomes student of

Ph.D. in Instituto de Investigacin en

Comunicacin ptica (IICO), with the thesis "Multilevel inverters in

eolic, photovoltaic and thermal application".

He has been a speaker on national conferences about electronics and

renewable energy and has participated in some local competitions about

research projects on rebewable energies. His research includes

renewable energy systems, power systems and power electronics.

Ricardo Eliu Lozoya Ponce was born on San

Luis Potos on April of 1986. He received

B.Sc. degree on Electronics Engineer from

Universidad Autnoma de San Luis Potos

(UASLP) on 2008. The M.Sc. degree from

Instituto de Investigacion en Comunicacin

ptica (IICO) in 2010. He becomes student of

Ph.D. in Instituto de Investigacin en

Comunicacin ptica (IICO), with the thesis "Model and Design of

reconfigurable circuits using Op-Amp".

International Review of Electrical Engineering, Vol. xx, n.

x

R.C. Martnez-Montejano, R. Castillo-Meraz, R.E. Lozoya-Ponce

His current research interest is in behavioral modeling and simulation

of linear and nonlinear circuits and systems, electronic implementation

of flexible structures applied to logic gates and reconfigurable systems.

Isaac Campos Cantn was born on Mrida,

Yucatn on December of 1968. He received

B.Sc. degree on Electronics Engineer from

Universidad Autnoma de San Luis Potos

(UASLP) on 1992. The M.Sc. degree from

Universidad Nacional Autnoma de Mxico

(UNAM) on 1996. He receives Ph.D. degree

on Instituto de Investigacin en Comunicacin

ptica (IICO), on 2009.

His current research is with the electronic circuits with nonlinear

behavior and complex networks.

Dr. Campos is member of Sociedad Mexicana de Fsica, and an IEEE

member.

Misael Francisco Martnez Montejano was

born on San Luis Potos on March of 1981. He

received B.Sc. degree on Electronics Engineer

from Universidad Autnoma de San Luis

Potos (UASLP) on 2002. The M.Sc. degree

from Instituto Potosino de Investigacin

Ciencia y Tecnologa (IPICyT) on 2004. He

receives Ph.D. degree on Instituto Potosino de

Investigacin Ciencia y Tecnologa (IPICyT), on 2009.

He obtained the best student award of the generation 1998-2002. He is

currently in the Research and Development Department of Alstom

Power, Switzerland. His research includes mathematical modeling,

application of non-linear control techniques (such as passivity, adaptive

control, linearization by state feedback, sliding modes, etc.), power

electronic systems, multilevel converters, active power filters,

renewable energy systems, and power plants.

Rogelio Osvaldo Lozoya Ponce was born on

San Luis Potos on March of 1985. He received

B.Sc. degree on Electronics Engineer from

Universidad Autnoma de San Luis Potosi

(UASLP) on 2006. The M.Sc. degree from

Instituto de Investigacin en Comunicacin

ptica (IICO), in 2010. He becomes student of

Ph.D. in Instituto de Investigacin en

Comunicacin ptica (IICO), with the thesis "Reconfigurable Cellular

Automata.

His current research consists in modeling and simulation of cellular

automata, electronica implementation, using reconfigurable systems

using logical circuits for electronic implementation.

Copyright 2014 Praise Worthy Prize S.r.l. - All rights reserved

International Review of Electrical Engineering, Vol. xx, n.

x

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Samsung SMART Signage - PHF - PMF Series Datasheet - WWDocument12 pagesSamsung SMART Signage - PHF - PMF Series Datasheet - WWsorin_tvNo ratings yet

- Practica 5 Tutorial CSTDocument13 pagesPractica 5 Tutorial CSTMontse SalviaNo ratings yet

- USB To RS-232 ConverterDocument11 pagesUSB To RS-232 Converteryeateshwarrior100% (1)

- The Story of BAHUBALI & Xilinx FPGAsDocument2 pagesThe Story of BAHUBALI & Xilinx FPGAsRakib HasanNo ratings yet

- Configuracion MD110Document85 pagesConfiguracion MD110Yusmely Noraima Perdomo MorenoNo ratings yet

- Sony Kv-14lm1e Fe-2 PDFDocument42 pagesSony Kv-14lm1e Fe-2 PDFAbel GaunaNo ratings yet

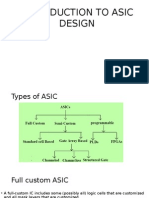

- Different Types of ASICDocument21 pagesDifferent Types of ASICParth Shah100% (1)

- Electric Vehicle Charging Station With An Energy Storage Stage For Split-Dc Bus Voltage BalancingDocument3 pagesElectric Vehicle Charging Station With An Energy Storage Stage For Split-Dc Bus Voltage BalancingJohn AjishNo ratings yet

- SMP 4000 en SDocument8 pagesSMP 4000 en SZainal AbidinNo ratings yet

- Rife Medic SupportDocument4 pagesRife Medic SupportEdward KrielNo ratings yet

- Unit - 8 A Generic Digital Switching System ModelDocument16 pagesUnit - 8 A Generic Digital Switching System ModelLavanya R GowdaNo ratings yet

- Chapter - 24-By DR Sajid Ali Ansari 2021Document34 pagesChapter - 24-By DR Sajid Ali Ansari 202175wpt82qvyNo ratings yet

- Project ProposalDocument4 pagesProject ProposalSushrut BhatNo ratings yet

- Magnetic Lock CE EMC Test Report E160510426Document36 pagesMagnetic Lock CE EMC Test Report E160510426Moraru PANo ratings yet

- OFC Assignment QuestionsDocument9 pagesOFC Assignment QuestionsPrashant SangulagiNo ratings yet

- NTP Server m600Document14 pagesNTP Server m600kisturscribdNo ratings yet

- What's The Difference Between IEEE 802.11af and 802.11ah - PDFDocument10 pagesWhat's The Difference Between IEEE 802.11af and 802.11ah - PDFsorinproiecteNo ratings yet

- C 1 6 7 C R C 1 6 7 S R: 16-Bit Single-Chip MicrocontrollerDocument75 pagesC 1 6 7 C R C 1 6 7 S R: 16-Bit Single-Chip MicrocontrollervictorNo ratings yet

- Cap Round 1Document5 pagesCap Round 1Harshad ThiteNo ratings yet

- Elektor USA - November 2014 PDFDocument92 pagesElektor USA - November 2014 PDFJean-Pierre DesrochersNo ratings yet

- Cable GuideDocument154 pagesCable GuideeftamargoNo ratings yet

- UDGC Instructions V1Document16 pagesUDGC Instructions V1Orlando MarucaNo ratings yet

- Review of Basic Circuit ConceptsDocument52 pagesReview of Basic Circuit ConceptsIsmail kabirNo ratings yet

- Chf100a Manual v1.0 enDocument153 pagesChf100a Manual v1.0 enHao LambaNo ratings yet

- Co4 Part 1 Ask FSK PSK QPSK Qam MSKDocument41 pagesCo4 Part 1 Ask FSK PSK QPSK Qam MSKsuresh Namgiri0% (1)

- Eee 312 8Document3 pagesEee 312 8sabitavabiNo ratings yet

- 1SS355Document3 pages1SS355Barton EletronicsNo ratings yet

- Power Transistors PDFDocument4 pagesPower Transistors PDFsupriyaNo ratings yet

- Fully Integrated LDO Linear Voltage RegulatorDocument15 pagesFully Integrated LDO Linear Voltage RegulatorAram ShishmanyanNo ratings yet

- Single Electron TransistorDocument11 pagesSingle Electron TransistorHarsha VardhanNo ratings yet