Professional Documents

Culture Documents

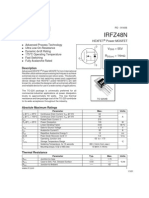

IRFZ48 55V-64A 140W-N-channelenhancemenT PDF

Uploaded by

ZxdIaminxXzlovewithzxXzyouzxOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IRFZ48 55V-64A 140W-N-channelenhancemenT PDF

Uploaded by

ZxdIaminxXzlovewithzxXzyouzxCopyright:

Available Formats

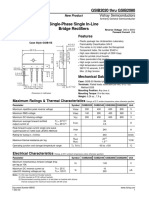

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

GENERAL DESCRIPTION

N-channel enhancement mode

standard level field-effect power

transistor in a plastic envelope using

trench technology. The device

features very low on-state resistance

and has integral zener diodes giving

ESD protection up to 2kV. It is

intended for use in switched mode

power supplies and general purpose

switching applications.

PINNING - TO220AB

PIN

IRFZ48N

QUICK REFERENCE DATA

SYMBOL

PARAMETER

VDS

ID

Ptot

Tj

RDS(ON)

Drain-source voltage

Drain current (DC)

Total power dissipation

Junction temperature

Drain-source on-state

resistance

VGS = 10 V

PIN CONFIGURATION

MAX.

UNIT

55

64

140

175

16

V

A

W

C

m

SYMBOL

DESCRIPTION

tab

gate

drain

source

tab

drain

1 23

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

VDS

VDGR

VGS

ID

ID

IDM

Ptot

Tstg, Tj

Drain-source voltage

Drain-gate voltage

Gate-source voltage

Drain current (DC)

Drain current (DC)

Drain current (pulse peak value)

Total power dissipation

Storage & operating temperature

RGS = 20 k

Tmb = 25 C

Tmb = 100 C

Tmb = 25 C

Tmb = 25 C

-

- 55

55

55

20

64

45

210

140

175

V

V

V

A

A

A

W

C

MIN.

MAX.

UNIT

kV

TYP.

MAX.

UNIT

1.1

K/W

60

K/W

ESD LIMITING VALUE

SYMBOL

PARAMETER

CONDITIONS

VC

Electrostatic discharge capacitor

voltage, all pins

Human body model

(100 pF, 1.5 k)

THERMAL RESISTANCES

SYMBOL

PARAMETER

CONDITIONS

Rth j-mb

Thermal resistance junction to

mounting base

Thermal resistance junction to

ambient

Rth j-a

February 1999

in free air

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

IRFZ48N

STATIC CHARACTERISTICS

Tj= 25C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

V(BR)DSS

Drain-source breakdown

voltage

Gate threshold voltage

VGS = 0 V; ID = 0.25 mA;

VGS(TO)

Tj = -55C

VDS = VGS; ID = 1 mA

Tj = 175C

Tj = -55C

IDSS

Zero gate voltage drain current

VDS = 55 V; VGS = 0 V;

IGSS

Gate source leakage current

VGS = 10 V; VDS = 0 V

V(BR)GSS

Gate-source breakdown

voltage

Drain-source on-state

resistance

IG = 1 mA;

RDS(ON)

Tj = 175C

Tj = 175C

VGS = 10 V; ID = 25 A

Tj = 175C

MIN.

TYP.

MAX.

UNIT

55

50

2

1

16

3.0

0.05

0.02

-

4.0

4.4

10

500

1

20

-

V

V

V

V

V

A

A

A

A

V

12

-

16

30

m

m

MIN.

TYP.

MAX.

UNIT

DYNAMIC CHARACTERISTICS

Tmb = 25C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

gfs

Forward transconductance

VDS = 25 V; ID = 25 A

39

Ciss

Coss

Crss

Input capacitance

Output capacitance

Feedback capacitance

VGS = 0 V; VDS = 25 V; f = 1 MHz

2200

500

200

2900

600

270

pF

pF

pF

Qg(tot)

Qgs

Qgd

Total gate charge

Gate-source charge

Gate-drain (Miller) charge

ID = 50 A; VDD = 44 V; VGS = 10 V

85

19

37

nC

nC

nC

td on

tr

td off

tf

Turn-on delay time

Turn-on rise time

Turn-off delay time

Turn-off fall time

VDD = 30 V; ID = 25 A;

VGS = 10 V; RG = 10

Resistive load

18

35

45

30

26

85

60

45

ns

ns

ns

ns

Ld

Internal drain inductance

3.5

nH

Ld

Internal drain inductance

4.5

nH

Ls

Internal source inductance

Measured from contact screw on

tab to centre of die

Measured from drain lead 6 mm

from package to centre of die

Measured from source lead 6 mm

from package to source bond pad

7.5

nH

February 1999

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

IRFZ48N

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

IDR

IDRM

VSD

Continuous reverse drain

current

Pulsed reverse drain current

Diode forward voltage

trr

Qrr

Reverse recovery time

Reverse recovery charge

MIN.

TYP.

MAX.

UNIT

64

IF = 25 A; VGS = 0 V

IF = 65 A; VGS = 0 V

0.95

1.0

210

1.2

-

A

V

V

IF = 65 A; -dIF/dt = 100 A/s;

VGS = -10 V; VR = 30 V

57

0.14

ns

C

MIN.

TYP.

MAX.

UNIT

200

mJ

AVALANCHE LIMITING VALUE

SYMBOL

PARAMETER

CONDITIONS

WDSS

Drain-source non-repetitive

unclamped inductive turn-off

energy

ID = 65 A; VDD 25 V;

VGS = 10 V; RGS = 50 ; Tmb = 25 C

120

Normalised Power Derating

PD%

120

110

110

100

100

90

90

80

80

70

70

60

60

50

50

40

40

30

30

20

20

10

10

0

0

20

40

60

80 100

Tmb / C

120

140

160

180

Fig.1. Normalised power dissipation.

PD% = 100PD/PD 25 C = f(Tmb)

February 1999

Normalised Current Derating

ID%

20

40

60

80 100

Tmb / C

120

140

160

180

Fig.2. Normalised continuous drain current.

ID% = 100ID/ID 25 C = f(Tmb); conditions: VGS 5 V

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

IRFZ48N

RDS(ON)/mOhm

SOAX514

30

1000

VGS/V =

ID / A

tp =

1 us

10 us

RDS(ON) = VDS/ID

100

7

8

9

10

15

1 ms

DC

10

10 ms

100 ms

1

6.5

20

100 us

10

10

100

55

10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85 90 95 100

ID/A

VDS / V

Fig.3. Safe operating area. Tmb = 25 C

ID & IDM = f(VDS); IDM single pulse; parameter tp

1E+01

25

Fig.6. Typical on-state resistance, Tj = 25 C.

RDS(ON) = f(ID); parameter VGS

100

BUKX514-55

Zth / (K/W)

ID/A

80

1E+00

0.5

1E-01

60

0.2

0.1

0.05

PD

0.02

tp

D=

tp

T

40

20

1E-02

0

1E-03

1E-07

1E-05

1E-03

t/s

1E-01

1E+01

Fig.4. Transient thermal impedance.

Zth j-mb = f(t); parameter D = tp/T

100

8

7.5

16

10

ID/A

VGS/V =

Tj/C =

25

175

5

VGS/V

Fig.7. Typical transfer characteristics.

ID = f(VGS) ; conditions: VDS = 25 V; parameter Tj

40

gfs/S

35

80

30

6.5

25

60

20

6

40

15

5.5

10

20

5

0

4.5

4

0

VDS/V

10

Fig.5. Typical output characteristics, Tj = 25 C.

ID = f(VDS); parameter VGS

February 1999

20

40

ID/A

60

80

100

Fig.8. Typical transconductance, Tj = 25 C.

gfs = f(ID); conditions: VDS = 25 V

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

2.5

BUK959-60

IRFZ48N

Rds(on) normlised to 25degC

3.5

3

Thousands (pF)

1.5

2.5

Ciss

2

1.5

1

5

0.5

-100

-50

50

Tmb / degC

100

150

0

0.01

200

Fig.9. Normalised drain-source on-state resistance.

a = RDS(ON)/RDS(ON)25 C = f(Tj); ID = 25 A; VGS = 5 V

VGS(TO) / V

0.1

Coss

Crss

100

10

VDS/V

Fig.12. Typical capacitances, Ciss, Coss, Crss.

C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

12

BUK759-60

VGS/V

max.

10

VDS = 14V

4

typ.

VDS = 44V

3

6

min.

2

1

2

0

-100

-50

50

Tj / C

100

150

200

Fig.10. Gate threshold voltage.

VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

10

20

30 QG/nC 40

50

60

Fig.13. Typical turn-on gate-charge characteristics.

VGS = f(QG); conditions: ID = 50 A; parameter VDS

100

Sub-Threshold Conduction

1E-01

IF/A

80

1E-02

2%

1E-03

typ

60

98%

Tj/C =

175

25

40

1E-04

20

1E-05

0

1E-06

Fig.11. Sub-threshold drain current.

ID = f(VGS); conditions: Tj = 25 C; VDS = VGS

February 1999

0.2

0.4

0.6

0.8

VSDS/V

1.2

1.4

Fig.14. Typical reverse diode current.

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

120

IRFZ48N

WDSS%

110

100

VDD

RD

90

VDS

80

70

VGS

60

50

40

RG

T.U.T.

30

20

10

0

20

40

60

80

100

120

Tmb / C

140

160

180

Fig.17. Switching test circuit.

Fig.15. Normalised avalanche energy rating.

WDSS% = f(Tmb); conditions: ID = 75 A

VDD

L

VDS

VGS

-ID/100

T.U.T.

0

RGS

R 01

shunt

Fig.16. Avalanche energy test circuit.

WDSS = 0.5 LID2 BVDSS /(BVDSS VDD )

February 1999

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

IRFZ48N

MECHANICAL DATA

Dimensions in mm

4,5

max

Net Mass: 2 g

10,3

max

1,3

3,7

2,8

5,9

min

15,8

max

3,0 max

not tinned

3,0

13,5

min

1,3

max 1 2 3

(2x)

0,9 max (3x)

2,54 2,54

0,6

2,4

Fig.18. SOT78 (TO220AB); pin 2 connected to mounting base.

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Refer to mounting instructions for SOT78 (TO220) envelopes.

3. Epoxy meets UL94 V0 at 1/8".

February 1999

Rev 1.000

Philips Semiconductors

Product specification

N-channel enhancement mode

TrenchMOSTM transistor

IRFZ48N

DEFINITIONS

Data sheet status

Objective specification

This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification

This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

February 1999

Rev 1.000

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Datasheet BUK7508-55Document9 pagesDatasheet BUK7508-55Luis PerezNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 pagesN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Buk 456 60HDocument7 pagesBuk 456 60HkleephNo ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Buk564-60h Powermos Transistor FetDocument7 pagesBuk564-60h Powermos Transistor FetOlga PlohotnichenkoNo ratings yet

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesFrom EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesRating: 4.5 out of 5 stars4.5/5 (7)

- N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DatathedrodNo ratings yet

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Buk453 100aDocument7 pagesBuk453 100amicrowave440No ratings yet

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 pagesN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNo ratings yet

- 01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyDocument9 pages01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyPuti Benny LakraNo ratings yet

- BUK436-200A PowerMOS TransistorDocument8 pagesBUK436-200A PowerMOS TransistorZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Smart Lowside Power Switch: Hitfet II - Generation BSP 77Document11 pagesSmart Lowside Power Switch: Hitfet II - Generation BSP 77Roozbeh BahmanyarNo ratings yet

- Buk455 200aDocument8 pagesBuk455 200athecrabforyouNo ratings yet

- IRFZ48NDocument8 pagesIRFZ48NLuay IssaNo ratings yet

- FDP5N50U / FDPF5N50UT: Ultra FRFETDocument10 pagesFDP5N50U / FDPF5N50UT: Ultra FRFETtecnologo456No ratings yet

- D13N03LTDocument12 pagesD13N03LTmarquitos550bNo ratings yet

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDocument9 pagesFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloNo ratings yet

- FDD8780Document6 pagesFDD8780Cadena CesarNo ratings yet

- Fet 60NF06Document9 pagesFet 60NF06Anh Nguyễn HoàngNo ratings yet

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument11 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiNo ratings yet

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDocument10 pagesFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezNo ratings yet

- Irfz 48 VDocument8 pagesIrfz 48 VZoltán HalászNo ratings yet

- Buk9237 55aDocument13 pagesBuk9237 55aOlga PlohotnichenkoNo ratings yet

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNo ratings yet

- "Omnifet Ii": Fully Autoprotected Power Mosfet: VNS3NV04DDocument14 pages"Omnifet Ii": Fully Autoprotected Power Mosfet: VNS3NV04DDan EsentherNo ratings yet

- Pmv65Xp: 1. Product ProfileDocument12 pagesPmv65Xp: 1. Product Profilealoksharma20No ratings yet

- Mosfet FDPS 2p102aDocument6 pagesMosfet FDPS 2p102aAssiseletroNo ratings yet

- Dual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Document16 pagesDual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Benny RoyNo ratings yet

- BUK951R6-30E: 1. Product ProfileDocument13 pagesBUK951R6-30E: 1. Product ProfileTom BeanNo ratings yet

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDocument11 pagesFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateNo ratings yet

- FDN335NDocument5 pagesFDN335NFernando YanoNo ratings yet

- Datasheet 53315Document30 pagesDatasheet 53315Bladimir AngamarcaNo ratings yet

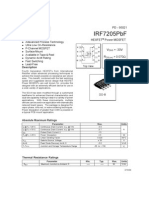

- Irf7205pbf Datasheet MosfetDocument9 pagesIrf7205pbf Datasheet Mosfetnithinmundackal3623No ratings yet

- IRF740B/IRFS740B: 400V N-Channel MOSFETDocument11 pagesIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldNo ratings yet

- K4143Document8 pagesK4143eddy54No ratings yet

- Buk555 100aDocument8 pagesBuk555 100aDiego AliasNo ratings yet

- 2SK3053Document9 pages2SK3053Иегҵ ГемасснеNo ratings yet

- FDMC86240 DatasheetDocument7 pagesFDMC86240 DatasheetYiannis PapadopoulosNo ratings yet

- BUK7511-55A BUK7611-55A: 1. DescriptionDocument15 pagesBUK7511-55A BUK7611-55A: 1. DescriptionziminautaNo ratings yet

- FDL100N50FDocument8 pagesFDL100N50FthanhluanbkNo ratings yet

- Qfet Qfet Qfet Qfet: FQP55N10Document8 pagesQfet Qfet Qfet Qfet: FQP55N10andreanuovoNo ratings yet

- PHB 55n03lta Logic Level FetDocument15 pagesPHB 55n03lta Logic Level FetyusufwpNo ratings yet

- BUK7508-55A: 1. Product ProfileDocument14 pagesBUK7508-55A: 1. Product Profilejalvarez_385073No ratings yet

- 8N80Document7 pages8N80niainaeloi_842256206No ratings yet

- Irl 1004Document9 pagesIrl 1004Luiz RvNo ratings yet

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDocument10 pagesFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarNo ratings yet

- Fdw2503N: Dual N-Channel 2.5V Specified Powertrench MosfetDocument6 pagesFdw2503N: Dual N-Channel 2.5V Specified Powertrench MosfetUlises Juan Huancapaza MachucaNo ratings yet

- AF4920NDocument6 pagesAF4920NJuan CoronelNo ratings yet

- Sss7n60b (7n60b) MosfetDocument11 pagesSss7n60b (7n60b) MosfetCamilo AldanaNo ratings yet

- PHD 98 N 03Document14 pagesPHD 98 N 03Kevin TateNo ratings yet

- CD22100 - DataSheetDocument10 pagesCD22100 - DataSheetHao ChungNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : STD70N02L STD70N02L-1Document17 pagesObsolete Product(s) - Obsolete Product(s) : STD70N02L STD70N02L-1Venkatesh SubramanyaNo ratings yet

- Irf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsDocument6 pagesIrf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsnewmailsNo ratings yet

- IRF450Document7 pagesIRF450Viet Hoang LeNo ratings yet

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDocument9 pagesFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57No ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- GSIB 2080 Bridge Rectifiers 20A 200-800VDocument2 pagesGSIB 2080 Bridge Rectifiers 20A 200-800VZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Vishay Telefunken: D M D M M D DDocument6 pagesVishay Telefunken: D M D M M D DZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- How To Create A Ddns Account and A Free Hostname For Your Dynamic Ip, Using ServiceDocument8 pagesHow To Create A Ddns Account and A Free Hostname For Your Dynamic Ip, Using ServiceZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Zener 1n4727... 49 PDFDocument6 pagesZener 1n4727... 49 PDFZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Vishay Telefunken: D M D M M D DDocument6 pagesVishay Telefunken: D M D M M D DZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- K14A55D ToshibaDocument6 pagesK14A55D ToshibaZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- HRF3205 100A, 55V, 0.008 Ohm, N-Channel, PowerDocument9 pagesHRF3205 100A, 55V, 0.008 Ohm, N-Channel, PowerZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Ixyh50N120C3D1: V 1200V I 50A V T 43Ns 1200V XPT Igbt Genx3 W/ DiodeDocument7 pagesIxyh50N120C3D1: V 1200V I 50A V T 43Ns 1200V XPT Igbt Genx3 W/ DiodeZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- BUK436-200A PowerMOS TransistorDocument8 pagesBUK436-200A PowerMOS TransistorZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- GSIB 2080 Bridge Rectifiers 20A 200-800VDocument2 pagesGSIB 2080 Bridge Rectifiers 20A 200-800VZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- 40 N60 300wDocument6 pages40 N60 300wZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- MANUal Bluetooth J20H066Document9 pagesMANUal Bluetooth J20H066ZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Tl2843 PWM ControllersDocument27 pagesTl2843 PWM ControllersZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- LG Ht355sd Sh35sd SMDocument61 pagesLG Ht355sd Sh35sd SMZxdIaminxXzlovewithzxXzyouzx67% (3)

- CodeDocument72 pagesCodeKushal BajracharyaNo ratings yet

- Relay and Contactor in DetailDocument12 pagesRelay and Contactor in DetailSafen Bakr SiwailyNo ratings yet

- BA Maxicat-GB Juni 2015 PDFDocument14 pagesBA Maxicat-GB Juni 2015 PDFKheiro BelhadiaNo ratings yet

- JV33-130 160BS Operation D201887-V1.6Document206 pagesJV33-130 160BS Operation D201887-V1.6sergeiyossarianNo ratings yet

- TALEXXdriver LCA 120W 350-1050ma One4all C PRE OTD enDocument9 pagesTALEXXdriver LCA 120W 350-1050ma One4all C PRE OTD enAlex FilipovicNo ratings yet

- Speech Recognition System Using Ic Hm2007Document21 pagesSpeech Recognition System Using Ic Hm2007Nitin Rawat100% (1)

- Cable TRAY VER.1.1Document22 pagesCable TRAY VER.1.1ahmed samyNo ratings yet

- Camry Solara SEV6Document13 pagesCamry Solara SEV6arturmikieNo ratings yet

- A Review Pof Power Converters Topologies For Wind GeneratorsDocument8 pagesA Review Pof Power Converters Topologies For Wind GeneratorsGabriel VilknNo ratings yet

- Standard Recovery Diodes: JZZX860D (U) .. SeriesDocument3 pagesStandard Recovery Diodes: JZZX860D (U) .. SeriesJose Castro100% (1)

- Design and Implementation of Simple As Possible Computer (SAP-1)Document52 pagesDesign and Implementation of Simple As Possible Computer (SAP-1)Muhammad Anas 484-FET/BSEE/F18No ratings yet

- Air Inlet ServomotorDocument1 pageAir Inlet Servomotorhidakota hidakotaNo ratings yet

- Lely Welger AP 530 Manual deDocument94 pagesLely Welger AP 530 Manual deJimmy ZettenbergNo ratings yet

- MAKER List OF MATERIAL & EQUIPMENTS - LONGLINEDocument7 pagesMAKER List OF MATERIAL & EQUIPMENTS - LONGLINETri HariyNo ratings yet

- Sandvik RD285 TY280 PartsListDocument3 pagesSandvik RD285 TY280 PartsListGiovanni Aliaga MariscalNo ratings yet

- Propeller Shaft Univ JointDocument7 pagesPropeller Shaft Univ JointGoutham ReddyNo ratings yet

- Electrical ElectronicsDocument92 pagesElectrical ElectronicstechNo ratings yet

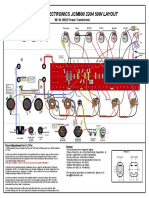

- Triode Electronics Jcm800 2204 50W LayoutDocument1 pageTriode Electronics Jcm800 2204 50W LayoutDimce BusinoskiNo ratings yet

- 7 Steps To Publishing in A Scientific JournalDocument53 pages7 Steps To Publishing in A Scientific JournalZAHID HUSSAIN AMEERNo ratings yet

- Company ProfileDocument24 pagesCompany ProfilebaabNo ratings yet

- Brosur Meja OperasiDocument8 pagesBrosur Meja OperasikartikaNo ratings yet

- Fiber Optic Installation and MaintenanceDocument5 pagesFiber Optic Installation and MaintenanceGhayas Ud-din Dar100% (2)

- Motherboard The Common MOSFET (FET) Substitution TableDocument3 pagesMotherboard The Common MOSFET (FET) Substitution TableDhruv Gonawala100% (3)

- Z - Wave ReportDocument25 pagesZ - Wave Reportqwerty123890No ratings yet

- EasyPact MVS - MVS08H3MF2LDocument3 pagesEasyPact MVS - MVS08H3MF2Ldyan emejasNo ratings yet

- A750EDocument1 pageA750EPedroMecanicoNo ratings yet

- Schema Sursa ATX 305w PsuDocument42 pagesSchema Sursa ATX 305w Psupetrosani2005No ratings yet

- Design and Research On Parameter of LCL Filter in Three-Phase Grid-Connected InverterDocument4 pagesDesign and Research On Parameter of LCL Filter in Three-Phase Grid-Connected InverterDucSyHoNo ratings yet

- 2N 2646Document2 pages2N 2646Sankar NayagamNo ratings yet

- Universiti Teknologi Mara Final Examination: Instructions To CandidatesDocument4 pagesUniversiti Teknologi Mara Final Examination: Instructions To CandidatesTomorrow PavingNo ratings yet