Professional Documents

Culture Documents

Ee 5164

Uploaded by

Saurabh ChaubeyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee 5164

Uploaded by

Saurabh ChaubeyCopyright:

Available Formats

To Study and Simulate the Electrical Characteristics of Silicon Nanowire

Transistors (SNWTs) in Analog and Digital Circuits

Saurabh Chaubey, ID no - 4877517

Final Project Report, Semiconductor Properties and Devices II, EE-5164

AbstractThis work explores the present day advancement in

the field of Silicon Nanowire Transistors (SNWTs) for sub 10nm

channel length. We show that these types of structures solve the

fundamental problem of short channel devices i.e gate control.

These structures enhance the gate control by having Gate All

Around (GAA) strategy with ultra low parasitics. We will show

that these structures will have an impressive Ion /Iof f . We will

study the electrical characteristics of the SNWTs and related

exotic structures. Also for the first time, I am trying to use the

models developed by the latest works [1-4] of these devices to

apply on basic analog and digital building blocks. I present a

basic and simple framework to predict the future performances

(in coming years) of analog and digital circuits based on these

SNWTs. I am also exploring the impact of parasitic capacitances

and resistances on the circuit performances using these devices.

According to the SPICE circuit simulations, we find that the basic

SNWT can have an instrisic DC gain of 35dB and bandwidth

of 11 GHz with a Gain-Bandwidth product of 347 GHz. The

Ft(frequency at which the transistor ceases to be an amplifier)

is found to be 1.18 THz. The digital delay (of a minimum size

inverter) is 1.3 pSec. It should be noted that the models used in

SPICE for these simulations are abstract and simplified versions

of the detailed model developed in literatures like of those [25] and are of very basic and just indicative of the performance

trends.

(a)

KeywordsSilicon Nanowire Transistors, Gate All Around,

Gate control, Analog Circuit Performances, Digital Circuit Performances, Process Mismatch, Parasitic

I.

I NTRODUCTION

Conventional scaling of gate oxide thickness, source/drain

extension (SDE), junction depths, and gate lengths have enabled MOS gate dimensions to be reduced from 10mm in the

1970s to a present day size of 0.1mm. To enable transistor

scaling into the 21st century, new solutions such as high

dielectric constant materials for gate insulation and shallow,

ultra low resistivity junctions need to be developed. In this

paper, for the first time, key scaling limits are quantified

for MOS transistors . We show that traditional SiO2 gate

dielectrics will reach fundamental leakage limits, due to tunneling, for an effective electrical thickness below 2.3 nm.

Experimental data and simulations are used to show that although conventional scaling of junction depths is still possible,

increased resistance for junction depths below 30 nm results

in performance degradation. Because of these limits, it will

not be possible to further improve short channel effects. This

will result in either unacceptable off-state leakage currents or

strongly degraded device performance for gate lengths below

100um. MOS transistor limits will be reached for 0.13mm

process technologies in production during 2002. Because of

these problems, new solutions will need to be developed for

continued transistor scaling. The fundamental problems and

issues of MOSFETs beyond sub-10nm channel length are the

(b)

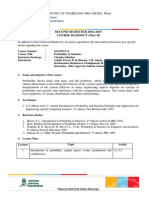

Fig. 1. (a) International Technology Roadmap for Semiconductors (ITRS)

based technology trends for scaling of MOSFETs for higher performances.

(b) Conventional scaling of MOSFETs till 2011 without use of exotic FET

structures and using standard CMOS processes.

electrostatic limits, source-to-drain tunneling, carrier mobility

degradation, process variations, and static leakage. The trend

towards ultra-short gate length MOSFETs requires a more and

more effective control of the channel by the gate leading to

new device architecture. Diverse device structures have been

recently proposed and explored, and have found better characteristics than that of single gate metal oxide semiconductor

field effect transistors (MOSFETs). For example, the double

gate MOSFETs can suppress the short-channel effects (SCEs)

and have high transconductance and ideal subthreshold swing

(SS). In order to further lower the SCEs, promising device

structure the so-called surrounding-gate nanowire FinFET were

fabricated and demonstrated fascinating device characteristic in

recent literatures. However, these structures face difficulties in

fabrication with advanced fabrication processes.

Multi-gate MOSFETs based on the concept of volume

Cross-section of Modern exotic FET structure cadidates for sub 10nm

Gate-Metal

(a)

(b)

(c)

Channel-Silicon

(d)

(e)

(f)

Fig. 2. (a) Early Intel FINFEts (b) Trigate (c) Omega-Gate (d) Pi- Gate (e)

Gate All Around (GAA) (d) Crosssection of Nanowire FET (SNWTs)

inversion are widely recognized as one of the most promising

solutions for meeting the ITRS roadmap requirements. A wide

variety of multi-gate architectures, including Double-Gate

(DG), Gate-All-Around (GAA), Pi-FET and Fin Field-Effect

Transistors (FinFETs), rectangular or cylindrical nanowire

MOSFETs have been proposed in common academic/scientific

literatures. In all cases, these structures exhibit a superior

control of short channel effects resulting from an exceptional

electrostatic coupling between the conduction channel and the

surrounding gate electrode. The nanowire (NW) transistors

can be seen as the ultimate integration of the innovative

nanodevices and is one of the candidates which have gained

significant attention from both the device and circuit developers because of its potential for building highly dense

and high performance electronic circuits. Recent advances in

nanoscale fabrication techniques have shown that semiconductor nanowires may become the candidate for next generation

technologies. Si and Ge nanowire transistors are also important

because of their compatibility with the CMOS technology.

Fig. 3.

Design issues with GAA based SNWTs

Fig. 4.

Ballistic transport mechanism as explained in [7]

II.

L ITERATURE S URVEY AND C OMPARISON OF

CANDIDATE STRUCTURES

Fig.1 shows the the advancements in conventional MOSFET designs till 2001-2012. Fig.1 (a) shows the International

Technology Roadmap for Semiconductors (ITRS) based technology trends for scaling of MOSFETs for higher performances. ITRS predicts the future of industries technology for

commercial purposes. From this we can see that the industry

is expected to use MOSFETs of channel lengths of 14nm by

the end of this year (2016). Also it predicts that by year 2020

commercial requirements will be of sub-10nm MOSFETs. So

the research in the field these exotic sub 10nm devices are

very much needed. Fig 1(b) shows some the latest technology

advancements to the present day from Intel using almost

standard CMOS processes and convectional FET geometries.

Fig. 2 presents different possible candidates for short

channel MOSFETs in near future. Fig.2(a) represents the

convectional intel FINFET developed in 2008-09. This has

dual gates on the sides of the channel. Devices based this

structures are being commercially manufactures in technology

nodes of TSMC 28nm and INTEL 22nm. Fig.2(b) shows a

slight variation of FINFET called tri-gate having three gate

(along the tree sides). This has a better Gate control than

conventional FINFETs. Fig.2(c)-(d) represents the omega and

pi structures to have even better gate control and less parasitic

[6]. Finally Fig.2(d-e) show the GAA strategy for Nanowire

MOSFETs (SNWTs). Fig.3 shows the various design issues

with a modern small channel SNWTs.

We will begin by reviewing the present and popular candidates for sub-10 nm transistors. We will explore the pros and

cons of each of them. After the literature survey we will move

towards the structural details of the GAA based nano-wire

SNWTs in section III. We will see the latest research work in

the field of GAA fabrication, transport mechanism, parasitics,

noise and variability. Then we will move the abstraction of

the equations developed in earlier sections in terms of verilogA modelling. We simulated the SNWTs in both analog and

digital sub-blocks. Using the simulations I tried to predict the

circuit performance of the conventional blocks in future (when

SNWTs will be used commercially).

A. Transport Mechanism

The basic carrier transport mechanism of the nano-wire

SNWTs is fundamentally different than FINFETs. According

to [7] we see the mechanism for the channel formed under the

GAA (Gate All Around) is ballistic transport behaviour. Fig 4

shows the illustration.

As devices are scaled to the nano-scale dimension, ballistic

transport of carriers becomes increasingly important. It is

possible that the channel length is shorter than the mean

free path such that the channel carriers will not suffer from

any scattering events. However, in the quasi-ballistic regime

Vout

Ft is freq at which

(Iout/Iin)VD=0 =1

Iout Ft=Gm/(2*pi*CG)

Vin

RDS =

dIDS

dt

-1

Intrinsic Gain = GmRDS

Gm:Transconductance

M3

M4

IInd Gain Stage

Iin

Intrinsic drain

capacitor, CD

Current Biasing Resistor

Intrinsic Gate

capacitor, CG

M1

Fig. 5.

M2

Definition of basic analog parameters to be calculated

(LG=(10nm,100nm)) the channel length would be larger than

the mean-free-path, and the possibility of ballistic-transport for

carriers will decrease. Therefore, in this regime, conventional

transport mechanism also plays a major role. The drain current

for a device is governed by:

IDsat = Qef f .Vinj .Bsat .(VGS VT H )

M5

INPUT Differential Stage

Fig. 6.

Circuit test bench

(1)

Vin

Vin

where Vinj and Bsat are the injection velocity and ballistic

efficiency. Eq.(1) describes how fast carriers are injected from

the source-Vinj, and how efficiently carriers will be transported

through the channel-Bsat. The more the carriers are reflected,

e.g., rc, the lower the Bsat is, as shown in Fig. 1, where rc

is the reflection coefficient, and the correlation between Bsat

and rc can be given by:

Bsat =

(1 rc )

(1 + rc )

In this work, we use a simple yet accurate approach VD,sat

method based on velocity saturation concept. From VD,sat

method, Bsat can be expressed by a compact form,

Bsat,q =

1 VD,sat

(VGS VT H )

(3)

Summary of the equations used for ID vs VD are presented

in Fig.4 right.

III.

C IRCUIT S IMULATIONS

We used the circuit parameters defined above to simulate

both analog and digital blocks. Fig 5 shows the basic performance parameter for analog circuits. Left shows the calculation

process for Ft (Transition frequency) and right shows the

calculation for DC (low frequency) gain.

Circuit topology used to the analog simulations is shown

in Fig. 6. Also Fig. 7 shows the definition of digital circuit

parameters used to simulate the values.

(Current break-up @ 0.8V, 27C)

Simulated

Value

parameters

RDS,on

620 ohm/um-radius

DC-Gain

30dB

FT

1.18 THz

Gain

Bandwidth 347 GHz

Product

Digital Delay

2.34 pSec

Power delay product 4.56 uA-Psec

CG

CD

CD

CD

Inverter

Fan-Out of 4

Definition of basic digital parameters to be calculated

IV.

(2)

CD

CD

CG

Fig. 7.

CD

Vout

Vout

C ONCLUSION

We investigated different structures for sub nanometer

transistors. This work explores the present day advancement

in the field of Silicon Nanowire Transistors (SNWTs) for sub

10nm channel length. We show that these types of structures

solve the fundamental problem of short channel devices i.e gate

control. These structures enhance the gate control by having

Gate All Around (GAA) strategy with ultra low parasitics.

R EFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

N. Singh et al., High-performance fully depleted silicon nanowire

(diameter /spl les/ 5 nm) gate-all-around CMOS devices, in IEEE

Electron Device Letters, vol. 27, no. 5, pp. 383-386, May 2006.

Jing Wang, A. Rahman, A. Ghosh, G. Klimeck and M. Lundstrom, On

the validity of the parabolic effective-mass approximation for the I-V

calculation of silicon nanowire transistors, in IEEE Transactions on

Electron Devices, vol. 52, no. 7, pp. 1589-1595, July 2005.

A. Dixit, A. Kottantharayil, N. Collaert, M. Goodwin, M. Jurczak and

K. De Meyer, Analysis of the parasitic S/D resistance in multiple-gate

FETs, in IEEE Transactions on Electron Devices, vol. 52, no. 6, pp.

1132-1140, June 2005.

Sung Dae Suk et al., High performance 5nm radius Twin Silicon

Nanowire MOSFET (TSNWFET) : fabrication on bulk si wafer, characteristics, and reliability, IEEE InternationalElectron Devices Meeting,

2005. IEDM Technical Digest., Washington, DC, 2005

S. Mittal et al., Epitaxially Defined FinFET: Variability Resistant

and High-Performance Technology, in IEEE Transactions on Electron

Devices, vol. 61, no. 8, pp. 2711-2718, Aug. 2014.

T. Park et al., PMOS body-tied FinFET (Omega MOSFET) characteristics, Device Research Conference, 2003, Salt Lake City, UT, USA,

2003, pp. 33-34.

J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon and P. D.

Ye, First experimental demonstration of gate-all-around IIIV MOSFETs

by top-down approach, Electron Devices Meeting (IEDM), 2011 IEEE

International, Washington,

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Econ F211 1023 PDFDocument2 pagesEcon F211 1023 PDFSaurabh ChaubeyNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument3 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionSaurabh ChaubeyNo ratings yet

- Lecture NotesDocument40 pagesLecture NotesSaurabh ChaubeyNo ratings yet

- Es Precomp TotalDocument21 pagesEs Precomp TotalSaurabh ChaubeyNo ratings yet

- 5164 Final ReportDocument11 pages5164 Final ReportSaurabh ChaubeyNo ratings yet

- HW 7 Grading Breakdown: Part 1 - 14 PointsDocument1 pageHW 7 Grading Breakdown: Part 1 - 14 PointsSaurabh ChaubeyNo ratings yet

- Fourier Transform (FT) Overview: Continuous vs. DiscreteDocument3 pagesFourier Transform (FT) Overview: Continuous vs. DiscreteSaurabh ChaubeyNo ratings yet

- Physics 5001 Syllabus - Fall 2015Document2 pagesPhysics 5001 Syllabus - Fall 2015Saurabh ChaubeyNo ratings yet

- Cadence ManualDocument51 pagesCadence Manualapi-27099960100% (4)

- VerilogA TutDocument47 pagesVerilogA TutSaurabh ChaubeyNo ratings yet

- SimpleScalar GuideDocument4 pagesSimpleScalar GuideSaurabh ChaubeyNo ratings yet

- GATE Study Material, Forum, Downloads, Discussions & More!Document15 pagesGATE Study Material, Forum, Downloads, Discussions & More!himani23No ratings yet

- Roubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Document369 pagesRoubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Maanas Khurana50% (2)

- Basspods P481 Product Manual 29.10.2022Document2 pagesBasspods P481 Product Manual 29.10.2022Gaming with demonNo ratings yet

- DeltaV Controller RedundancyDocument5 pagesDeltaV Controller RedundancyturboedNo ratings yet

- Computernetworks: CRT Technical by Naresh I TechnologiesDocument10 pagesComputernetworks: CRT Technical by Naresh I TechnologiesSantosh SubuddhiNo ratings yet

- Fishman Isys Guitar PreampDocument8 pagesFishman Isys Guitar Preampccfl2No ratings yet

- Performance: Internet Access Modem Telephone Line Internet Service Provider Routed Internet Telephone NetworkDocument8 pagesPerformance: Internet Access Modem Telephone Line Internet Service Provider Routed Internet Telephone NetworkRahul SharmaNo ratings yet

- Operating Manual For ASHIDA Numerical Inverse Time Under Voltage Relay Type: Adr 112ADocument27 pagesOperating Manual For ASHIDA Numerical Inverse Time Under Voltage Relay Type: Adr 112A1981todurkarNo ratings yet

- Processing BJTDocument14 pagesProcessing BJTSnigdha BorahNo ratings yet

- SVG Sinexcel (Ingles)Document19 pagesSVG Sinexcel (Ingles)pablo Quispe EscobarNo ratings yet

- First-Class in Every Sense.: Sound & Vision 2011 - 2012Document27 pagesFirst-Class in Every Sense.: Sound & Vision 2011 - 2012Razvan BaraganNo ratings yet

- Cables, Adapters, Accessories - 1Document8 pagesCables, Adapters, Accessories - 1Nguyen Danh HuyNo ratings yet

- Motorola Power Controller: by Sasi Kumar C Development EngineerDocument68 pagesMotorola Power Controller: by Sasi Kumar C Development EngineerVenkat RaoNo ratings yet

- IFR 6000 ManualDocument265 pagesIFR 6000 ManualHouvenaghelNo ratings yet

- Instrumentation SyllabusDocument31 pagesInstrumentation Syllabusvnktsandeep100% (1)

- Part2 Advanced EMCDocument58 pagesPart2 Advanced EMCili ilievNo ratings yet

- Polyvision TS SeriesDocument2 pagesPolyvision TS SeriesElectronic Whiteboards WarehouseNo ratings yet

- Antenna Theory: Chapter 6.1 - 6.2Document21 pagesAntenna Theory: Chapter 6.1 - 6.2RahulMondolNo ratings yet

- NSN-Flexi Multiradio 10 Base Station System Module DescriptionDocument36 pagesNSN-Flexi Multiradio 10 Base Station System Module DescriptioncarlosNo ratings yet

- Chapter 14, Solution 1.: = ω) (, whereDocument74 pagesChapter 14, Solution 1.: = ω) (, whereJuanFernandoCuadradoNo ratings yet

- Digital Timer: Easy To Use and Easy To ReadDocument32 pagesDigital Timer: Easy To Use and Easy To ReadAlvin NguyenNo ratings yet

- GbatekDocument1,426 pagesGbatekWen HuaNo ratings yet

- MSP430 Update PresentationDocument118 pagesMSP430 Update PresentationNguyên ThảoNo ratings yet

- 9.1.3 Packet Tracer - Identify MAC and IP AddressesDocument3 pages9.1.3 Packet Tracer - Identify MAC and IP Addresseskds20850No ratings yet

- Thinkpad T14 Gen 2 (Intel) : PsrefDocument9 pagesThinkpad T14 Gen 2 (Intel) : PsrefElmer AdedoyaNo ratings yet

- Assignment 1Document4 pagesAssignment 1Walid Aribi AlatreshNo ratings yet

- Allen-Bradley Guardshield 450L-B Safety Light CurtainDocument2 pagesAllen-Bradley Guardshield 450L-B Safety Light Curtainrabt1No ratings yet

- A Tri-Band Wilkinson Power Divider Using Step-Impedance ResonatorDocument4 pagesA Tri-Band Wilkinson Power Divider Using Step-Impedance ResonatorDiya NoorNo ratings yet

- High Power Factor Power DesignDocument8 pagesHigh Power Factor Power DesignnutwutNo ratings yet

- WP - Driving The Costs Out of IPTVDocument26 pagesWP - Driving The Costs Out of IPTVshiuli1288No ratings yet

- Pioneer DDJ-1000SRT - W RRV4695Document99 pagesPioneer DDJ-1000SRT - W RRV469544g6psdxtpNo ratings yet