Professional Documents

Culture Documents

High Resolution 12 Bit Segmented Capacitor DAC in Successive Approximation ADC

Uploaded by

bhasin_hemantCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

High Resolution 12 Bit Segmented Capacitor DAC in Successive Approximation ADC

Uploaded by

bhasin_hemantCopyright:

Available Formats

World Academy of Science, Engineering and Technology

International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering Vol:6, No:12, 2012

High-Resolution 12-Bit Segmented Capacitor

DAC in Successive Approximation ADC

Wee Leong Son, Hasmayadi Abdul Majid, and Rohana Musa

differential. Single-ended circuit is shown for simplicity.

International Science Index, Electronics and Communication Engineering Vol:6, No:12, 2012 waset.org/Publication/5640

AbstractThis paper study the segmented split capacitor

Digital-to-Analog Converter (DAC) implemented in a differentialtype 12-bit Successive Approximation Analog-to-Digital Converter

(SA-ADC). The series capacitance split array method employed as it

reduced the total area of the capacitors required for high resolution

DACs. A 12-bit regular binary array structure requires 2049 unit

capacitors (Cs) while the split array needs 127 unit Cs. These results

in the reduction of the total capacitance and power consumption of

the series split array architectures as to regular binary-weighted

structures. The paper will show the 12-bit DAC series split capacitor

with 4-bit thermometer coded DAC architectures as well as the

simulation and measured results.

KeywordsSuccessive Approximation Register

Digital Converter, SAR ADC, Low voltage ADC.

Fig. 1(a) A conventional 12-bit binary weighted capacitor DAC

Analog-to-

I. INTRODUCTION

UCCESSIVE Approximation Analog-to-Digital Converter

(SA-ADC) with charge redistribution based architectures

has the advantage of low power operation [1]-[4]. However, as

the number of bit increases, input load capacitance and area of

binary-weighted capacitor DAC (Digital-to-Analog Converter)

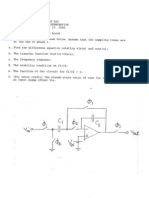

too increase exponentially [5]. Fig. 1(a) shows a 12-bit binary

weighted capacitor DAC example. Fig. 1(b) and Fig. 1(c) are

two split capacitor DAC solutions to reduce both input

capacitance and area for binary weighted DAC.

In Fig. 1(b), fractional value bridge capacitor is

implemented, so that the two capacitor arrays have the same

scaling. In the charge redistribution, the total weight of the left

array is equal to the total weight of the lowest bit in the right

array. However fractional value for the bridge capacitor causes

poor matching with other capacitors. In Fig. 1(c), a unit

bridge capacitor is implemented and the dummy capacitor

Cdummy is removed. Thus, the total weight of the left array

achieves the same weight as the lowest bit in the right array.

However, 1LSB gain error is caused. Both the above

implementations are vulnerable to parasitic capacitance in

Node A and between Node A and Node B, which causes

mismatch between the left and right arrays.

Fig. 1(d) proposes a unit bridge capacitor with 4-bit

thermometer coded DAC scheme to improve the linearity

performance. As shown in Fig. 1(d), 4 MSB bits on the

capacitor array were implemented using the thermometer

coded scheme. The proposed DAC are implemented fully

Fig. 1(b) 12-bit DAC with fractional value bridge capacitor

Fig. 1(c) 12-bit DAC with unit value bridge capacitor

Fig. 1(d) 12-bit with 4-bit thermometer coded DAC

Wee Leong Son, Hasmayadi Abdul Majid and Rohana Musa are with the

Integrated Circuit Development Department, Malaysia Institute of

Microelectronic Systems (MIMOS), Technology Park Malaysia, 57000 Kuala

Lumpur, Malaysia. (Phone: +603-89955000 ext: 55796; fax: +603-89914234;

(e-mail: weeleong@mimos.my, yadi@mimos.my, rohana@mimos.my).

International Scholarly and Scientific Research & Innovation 6(12) 2012

1383

scholar.waset.org/1999.5/5640

World Academy of Science, Engineering and Technology

International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering Vol:6, No:12, 2012

II. OVERALL SARADC OPERATION

International Science Index, Electronics and Communication Engineering Vol:6, No:12, 2012 waset.org/Publication/5640

The architecture of a SAR ADC is shown in Fig. 2,

consisting of a series structure of a capacitive DAC, a

comparator and successive approximation (SA) control logic

[6]. The SA control logic includes shift registers and switch

drivers which control the DAC operation by performing the

binary-scaled feedback during the successive approximation.

The DAC capacitor array is the basic structure of the SAR

ADC and it serves both to sample the input signal and as a

DAC for creating and subtracting the reference voltage.

Fig. 3(b) Single-ended DAC

Fig. 2 Architecture of a SAR ADC

III. IMPLEMENTATION

A. Capacitor Structure Design

Fig. 3(a) A fully differential DAC

International Scholarly and Scientific Research & Innovation 6(12) 2012

The fully differential DAC consists of two arrays of unit

bridge capacitor banks, a fully differential buffer and a4-to-15

decoder where thermometer code are employed as shown in

Fig. 3(a). Single-ended circuit is shown for simplicity in Fig.

3(b). The 12-bit DAC was designed with split unit bridge

capacitor to help reduce the size of the capacitors required,

eventually minimizes the current required to charge up the

capacitor array. Combination of sub-DAC and thermometer

coding employed to improve linearity especially when major

bit transition concerned.

B. Comparator

The comparator circuit comprises of pre-amplifier and

latch, shown in Fig. 4(a) . It represents an important part of the

SAR ADC since it has to be accurate to the value of the Least

Significant Bit (LSB) of an N-bit DAC. For a 12-bit ADC

with the reference voltages of +/-1V, the LSB value is

approximately 488uV. Therefore, the comparator designed has

to resolve a minimum of 488uV difference between the inputs.

However, to design such a high performance comparator

would require more resources that lead to higher current and

power consumption. In this design, a single stage preamplifier was used to boost the input voltage before the

comparator input. This method relaxes the performance

required from the comparator and hence, reduces the current

consumed. The comparator used in this design has a latch with

minimum-sized devices.

The latch is a regenerative latch Fig. 4(b) , with three

distinct phases: PHI1, PHI2 and RESET, where PHI1 and

PHI2 are non-overlapping clocks with RESET happening just

before PHI1. The latch is simulated across Monte Carlo

variation and the maximum offset is 150mV as shown in Fig.

4(c). Thus, the previous stage pre-amplifier has a requirement

to amplify the smallest resolvable signal to at least 150mV to

the latch input.

The required gain is therefore:

Gain required = 150mV/488uV = 307.4 = 49dB

The simulated gain of the pre-amp is 77B, which is well over

the gain requirement.

1384

scholar.waset.org/1999.5/5640

International Science Index, Electronics and Communication Engineering Vol:6, No:12, 2012 waset.org/Publication/5640

World Academy of Science, Engineering and Technology

International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering Vol:6, No:12, 2012

Fig. 4(a) Comparator circuuit

Fig. 4(d) Pree-amplifier circu

uit

Fig. 5(a) shoows the layoout implemenntation of thee DAC

whhile Fig. 5(b)) shows full implementattion of 12-bitt SAR

AD

DC.

Fig. 4(b) Latch circuit

Fig. 5 (a) Layout impplementation of the DAC

Fig. 4(c) Monte Carloo simulation on Latch circuit

The pre-ampplifier is designned to work at

a down to 1.4V, with

a folded-cascoode configuraation, Fig. 4(d). Folded-ccascode

arrchitecture waas chosen due to the limitedd headroom avvailable

att a minimum VDD

V

of 1.4V for the 0.18um Silterra pro

ocess. It

allso provides a better gainn performancce compared to the

coonventional single-stage am

mplifier.

International Scholarly and Scientific Research & Innovation 6(12) 2012

Fig. 5(b) Fuull layout implementation of th

he 12-bit SAR ADC

A

1385

scholar.waset.org/1999.5/5640

World Academy of Science, Engineering and Technology

International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering Vol:6, No:12, 2012

IV. RESULT

International Science Index, Electronics and Communication Engineering Vol:6, No:12, 2012 waset.org/Publication/5640

Fig. 6(a) shows schematic simulation and Fig. 6(b) shows

post layout simulation during input linearity ramping.

Ramping up and ramping down methods is used to test the

DACs linearity. The output for the first ramp up signal shows

non-linear at MSB due to the initial common mode value.

Subsequent ramp up shows that the output signal is actually

linear.

Fig. 7 (b) Measured INL

Fig. 6 (a) Schematic simulation

INL and DNL plot shows that the error is more than

LSB. This may be due to extra parasitic added during layout

implementation. This was not captured during post layout

simulation since the simulation concentrate more towards

major code transition. Fig. 7 (a) and 7(b) are measured DNL

and INL plot respectively.

V. CONCLUSION

A segmented split capacitor Digital-to-Analog Converter

(DAC) had been implemented in a differential 12-bit

Successive Approximation Analog-to-Digital Converter.

Measurement result shows high INL and DNL error due to

added parasitic effect during layout. Better layout matching

and shielding method should be implemented to further

improve the performance.

REFERENCES

[1]

[2]

Fig. 6 (b) Post layout simulation

[3]

[4]

[5]

[6]

[7]

[8]

S. Long, J. Wu, X. Xia, L, Shi, A1.8V 3.1mW

SuccessiveApproximation ADC in Systemon-Chip, Springer Science

+Business Media, LLC 2008.

A. Basu, V. Lee, A. Ma, A 10-bit 10MS/sSuccessive Approximation

A/D Converter in0.35um CMOS, University of Michigan, 2002.H. Poor,

An Introduction to Signal Detection and Estimation.

New York:

Springer-Verlag, 1985, ch. 4.

D. Draxelmayr, A 6b 600MHz 10mW ADC Array in Digital 90nm

CMOS, ISSCCDig. Tech. Papers, pp. 264-265, Feb. 2004.

N. Verma and A. Chandrakasan, An Ultra Low Energy 12-bit RateResolution ScalableSAR ADC for Wireless Sensor Nodes, IEEE J.

Solid-State Circuits, vol. 42, no. 6, pp.1196--1205, Jun. 2007.

R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout

and Simulation.New York: IEEE Press, 1998.

Ji-Yong Um, Digital-domain calibration of split-capacitor DAC with no

extra calibration DAC for a differential-type SAR ADCSolid State

Circuits Conference (A-SSCC), 2011 IEEE Asian.

Ikeda Y, A 14-bit 100-MS/s digitally calibrated binary-weighted currentsteering CMOS DAC without calibration ADC, Solid-State Circuits

Conference, 2007. ASSCC '07. IEEE Asian.

YanfeiChen, Split capacitor DAC mismatch calibration in successive

approximation ADC, Custom Integrated Circuits Conference, 2009.

CICC '09. IEEE.

Fig. 7 (a) Measured DNL

International Scholarly and Scientific Research & Innovation 6(12) 2012

1386

scholar.waset.org/1999.5/5640

You might also like

- c-2c DAC Architecture PDFDocument3 pagesc-2c DAC Architecture PDFshobhit960No ratings yet

- Design and Implementation of A 10 Bit SAR ADCDocument4 pagesDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanNo ratings yet

- D 59 542 548 PDFDocument7 pagesD 59 542 548 PDFlambanaveenNo ratings yet

- Optimizing The Number of Bits/Stage in 10-Bit, 50Ms/Sec Pipelined A/D Converter Considering Area, Speed, Power and LinearityDocument7 pagesOptimizing The Number of Bits/Stage in 10-Bit, 50Ms/Sec Pipelined A/D Converter Considering Area, Speed, Power and LinearityronaldomponteNo ratings yet

- Design of 12-Bit Adc: End-Term Project, 6.775Document21 pagesDesign of 12-Bit Adc: End-Term Project, 6.775dhineshpNo ratings yet

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDocument4 pagesDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyNo ratings yet

- A Digital Background Technique For Pipelined Analog-to-Digital ConvertersDocument5 pagesA Digital Background Technique For Pipelined Analog-to-Digital ConverterskennyNo ratings yet

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDocument9 pagesSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantNo ratings yet

- Low-Power CMOS Image Sensor Based On Column-Parallel Single-Slope/SAR Quantization SchemeDocument6 pagesLow-Power CMOS Image Sensor Based On Column-Parallel Single-Slope/SAR Quantization SchemeRaghul RamasamyNo ratings yet

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADocument22 pagesDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsNo ratings yet

- A 10-Bit 5 Msample/s ADC: Two-Step FlashDocument9 pagesA 10-Bit 5 Msample/s ADC: Two-Step FlashRaghav ChaudharyNo ratings yet

- 1Document4 pages1Yogesh Gujjar C JNo ratings yet

- A 10-Bit 500-MSs 55-mW CMOS ADCDocument12 pagesA 10-Bit 500-MSs 55-mW CMOS ADCSoodeh MiraslaniNo ratings yet

- A 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodDocument4 pagesA 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodSunil PandeyNo ratings yet

- A New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D ConverterDocument6 pagesA New, Low-Cost, Sampled-Data, 10-Bit CMOS A/D Converteralgnben1746No ratings yet

- Moin-10 1109@EIConRus 2019 8657039Document3 pagesMoin-10 1109@EIConRus 2019 8657039Moin SadiNo ratings yet

- A 12-Bit 40 MS/s Pipelined ADC With Over 80 DB SFDR: Wei Qi, Yin Xiumei, Han Dandan, and Yang HuazhongDocument5 pagesA 12-Bit 40 MS/s Pipelined ADC With Over 80 DB SFDR: Wei Qi, Yin Xiumei, Han Dandan, and Yang HuazhongfirpealNo ratings yet

- IEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFDocument3 pagesIEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFQuoc Thang TranNo ratings yet

- 07 - Chapter 4Document45 pages07 - Chapter 4SriramNo ratings yet

- Flash ADC Design in ElectricDocument22 pagesFlash ADC Design in ElectricNagaraj HegdeNo ratings yet

- Laboratory Experiment 6 - Analog To DigitalDocument4 pagesLaboratory Experiment 6 - Analog To DigitalyellowsubmirNo ratings yet

- Oregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonDocument4 pagesOregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonAlex WongNo ratings yet

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDocument4 pagesA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyNo ratings yet

- Microelectronics Journal: Shuo Yang, Jun Cheng, Pei WangDocument8 pagesMicroelectronics Journal: Shuo Yang, Jun Cheng, Pei WangShylu SamNo ratings yet

- A 15-b - Msample/s Digitally Self-Calibrated Pipeline ADC: Hae-Seung Lee, andDocument9 pagesA 15-b - Msample/s Digitally Self-Calibrated Pipeline ADC: Hae-Seung Lee, andSilpa VelagaletiNo ratings yet

- Design and Simulation of DAC On The Basis of Capacitor ArrayDocument4 pagesDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitNo ratings yet

- Pipelined AdcDocument26 pagesPipelined AdcKausar Fathima100% (1)

- Differential Analog Data Path DC Offset Calibration MethodsDocument7 pagesDifferential Analog Data Path DC Offset Calibration MethodsLincoln RibeiroNo ratings yet

- TOPIC 6 - (Converter)Document45 pagesTOPIC 6 - (Converter)Zulkiffli Mohd YusoffNo ratings yet

- A 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error CompensationDocument3 pagesA 10b 100MS S 1.13mW SAR ADC With Binary-Scaled Error Compensation陳昀顥No ratings yet

- Layout Tips For 12-Bit A/D Converter Application: Getting A Good StartDocument7 pagesLayout Tips For 12-Bit A/D Converter Application: Getting A Good StartRoberto MejiaNo ratings yet

- Transactions Briefs: A Single Channel Split Adc Structure For Digital Background Calibration in Pipelined AdcsDocument5 pagesTransactions Briefs: A Single Channel Split Adc Structure For Digital Background Calibration in Pipelined AdcsRahul ShandilyaNo ratings yet

- Low-Pass Filter Control Memory HeadphoneDocument6 pagesLow-Pass Filter Control Memory HeadphonematanveerNo ratings yet

- Camera Ready Reconfigurable ADCDocument20 pagesCamera Ready Reconfigurable ADCjayamala adsulNo ratings yet

- DAC ConverterDocument10 pagesDAC ConverterAmarnath M DamodaranNo ratings yet

- 10 - A TFT-LCD Source-Driver IC With Charge-Recycling TechniqueDocument11 pages10 - A TFT-LCD Source-Driver IC With Charge-Recycling Techniquematwan29No ratings yet

- Charge-Scaling DAC Design and OperationDocument7 pagesCharge-Scaling DAC Design and Operationmilostar6No ratings yet

- TVLSI_paper13Document12 pagesTVLSI_paper13djstubbornkingNo ratings yet

- 12-Bit Low-Power Fully Differential Switched Capacitor Noncalibrating Successive Approximation ADC With 1 MSsDocument6 pages12-Bit Low-Power Fully Differential Switched Capacitor Noncalibrating Successive Approximation ADC With 1 MSsThanos van RamNo ratings yet

- A 10-Bit Low-Power 10MSs Differential Successive Approximation ...Document6 pagesA 10-Bit Low-Power 10MSs Differential Successive Approximation ...zigbee1976No ratings yet

- REPORTFINALDocument21 pagesREPORTFINALReal HumanityNo ratings yet

- Design of A 12-Bit SAR ADC With DigitalDocument4 pagesDesign of A 12-Bit SAR ADC With DigitalY chenNo ratings yet

- A 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSDocument4 pagesA 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSThanos van RamNo ratings yet

- Dec Exp 7 Student ManualDocument4 pagesDec Exp 7 Student ManualAntarldNo ratings yet

- 2010SOVC A 1V 11fJ-Conversion-Step 10bit 10MS-s A Synchronous SAR ADC in 0.18um CMOSDocument2 pages2010SOVC A 1V 11fJ-Conversion-Step 10bit 10MS-s A Synchronous SAR ADC in 0.18um CMOSDivya SivaNo ratings yet

- A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesDocument9 pagesA 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesAshish JoshiNo ratings yet

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDocument12 pagesAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaNo ratings yet

- Designing Loop AntennasDocument18 pagesDesigning Loop AntennasCesar AvilaNo ratings yet

- R - KZ I: A 12-Bit ADC Successive-Approximation-Type With Digital Error CorrectionDocument10 pagesR - KZ I: A 12-Bit ADC Successive-Approximation-Type With Digital Error CorrectionMiguel BrunoNo ratings yet

- ADC DAC Loopback LinearityDocument15 pagesADC DAC Loopback LinearityparrotpanduNo ratings yet

- Design of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalDocument5 pagesDesign of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalSunil KumarNo ratings yet

- A 9-Bit 1.8 GS/s 44 MW Pipelined ADC Using Linearized Open-Loop AmplifiersDocument12 pagesA 9-Bit 1.8 GS/s 44 MW Pipelined ADC Using Linearized Open-Loop AmplifiersDilek METİNNo ratings yet

- 一种用于SAR ADC开关电容比较器的失调消除技术Document5 pages一种用于SAR ADC开关电容比较器的失调消除技术prachanyouetcNo ratings yet

- Behavioral Model of Pipeline Adc by Using SimulinkrDocument5 pagesBehavioral Model of Pipeline Adc by Using SimulinkrSounakDuttaNo ratings yet

- Ultra-Low: Power Silicon-on-Sapphire Energy-ScavengingDocument4 pagesUltra-Low: Power Silicon-on-Sapphire Energy-ScavengingGurkaranjot SinghNo ratings yet

- Modified Low-Power and Area-Efficient Carry Select Adder Using D-LatchDocument8 pagesModified Low-Power and Area-Efficient Carry Select Adder Using D-LatchhemanthbbcNo ratings yet

- ISCAS 2000 - Efficient Error-Cancelling Algorithmic ADCDocument4 pagesISCAS 2000 - Efficient Error-Cancelling Algorithmic ADCAlex WongNo ratings yet

- A Study of Folding and Interpolating ADCDocument7 pagesA Study of Folding and Interpolating ADCअमरेश झाNo ratings yet

- A 10-Bit 50-MS Per S SAR ADC With A Monotonic Capacitor Switching ProcedureDocument10 pagesA 10-Bit 50-MS Per S SAR ADC With A Monotonic Capacitor Switching ProcedureVũNguyễnNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- CTSDM JitterDocument10 pagesCTSDM Jitterbhasin_hemantNo ratings yet

- RNMCDocument4 pagesRNMCbhasin_hemantNo ratings yet

- L14 2 f09Document34 pagesL14 2 f09Hari BabuNo ratings yet

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDocument9 pagesSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantNo ratings yet

- Good DocumentDocument3 pagesGood Documentbhasin_hemantNo ratings yet

- Lect22 IV MixersDocument50 pagesLect22 IV Mixersbhasin_hemantNo ratings yet

- Capless LDO DESIGNDocument6 pagesCapless LDO DESIGNbhasin_hemantNo ratings yet

- Time Interleaved AdcDocument11 pagesTime Interleaved Adcbhasin_hemantNo ratings yet

- Iscas06 LCDocument4 pagesIscas06 LCbhasin_hemantNo ratings yet

- Thermal Noise in SC CircuitsDocument22 pagesThermal Noise in SC Circuitsbhasin_hemantNo ratings yet

- Midterm 2005Document3 pagesMidterm 2005bhasin_hemantNo ratings yet

- Midterm 2013Document3 pagesMidterm 2013bhasin_hemantNo ratings yet

- ThesisDocument157 pagesThesisbhasin_hemantNo ratings yet

- Analysis of Charge-Pump Phase-Locked LoopsDocument10 pagesAnalysis of Charge-Pump Phase-Locked Loopsbhasin_hemantNo ratings yet

- Pipeline Adc ThesisDocument177 pagesPipeline Adc Thesisbhasin_hemant100% (1)

- HW03 Solutions BoserDocument20 pagesHW03 Solutions Boserbhasin_hemantNo ratings yet

- Midterm 2011Document3 pagesMidterm 2011bhasin_hemantNo ratings yet

- Jitter RingDocument15 pagesJitter RingJiaxiang LiuNo ratings yet

- Circuits and Algorithms for Pipelined ADCs in Scaled CMOS TechnologiesDocument184 pagesCircuits and Algorithms for Pipelined ADCs in Scaled CMOS Technologiesbhasin_hemantNo ratings yet

- Good DocumentDocument3 pagesGood Documentbhasin_hemantNo ratings yet

- ThesisDocument157 pagesThesisbhasin_hemantNo ratings yet

- Midterm 2009Document4 pagesMidterm 2009bhasin_hemantNo ratings yet

- 2012 Zhang MascDocument77 pages2012 Zhang Mascbhasin_hemantNo ratings yet

- Jitter RingDocument15 pagesJitter RingJiaxiang LiuNo ratings yet

- PHDDocument184 pagesPHDbhasin_hemantNo ratings yet

- Accuracy Limitations of Pipelined Adcs: Clk2, C V V DV V V V V V V C CDocument4 pagesAccuracy Limitations of Pipelined Adcs: Clk2, C V V DV V V V V V V C Cbhasin_hemantNo ratings yet

- Semiconductor Device CalculationsDocument37 pagesSemiconductor Device Calculationsbhasin_hemantNo ratings yet

- Maneatis 93 BDocument10 pagesManeatis 93 Bbhasin_hemantNo ratings yet

- ON ADC'sDocument24 pagesON ADC'sRavi BellubbiNo ratings yet

- DAC Resistive Divider Circuit ExplainedDocument50 pagesDAC Resistive Divider Circuit ExplainedGohgulan Murugan100% (2)

- Data Converter Book Index F PDFDocument54 pagesData Converter Book Index F PDFhenkpiepNo ratings yet

- Digital To Analog and Analog To Digital Conversion: D/A or DAC and A/D or AdcDocument50 pagesDigital To Analog and Analog To Digital Conversion: D/A or DAC and A/D or AdcsomosreeNo ratings yet

- Printed ReportDocument64 pagesPrinted ReportChethan GowdaNo ratings yet

- Study of Various ADCs and Compare Their Performance and ParametersDocument12 pagesStudy of Various ADCs and Compare Their Performance and ParametersijaertNo ratings yet

- Adc F10Document44 pagesAdc F10Vigneshwari KuthalingamNo ratings yet

- Experiment No. 4 ADC PDFDocument16 pagesExperiment No. 4 ADC PDFRia Cordova0% (1)

- SAR Cyclic and Integrating ADCsDocument50 pagesSAR Cyclic and Integrating ADCsAlberto DanNo ratings yet

- Circuit To Increase Input Range-Sbaa244Document6 pagesCircuit To Increase Input Range-Sbaa244EdsonNo ratings yet

- Analog-To-Digital (A/D) and Digital-To-Analog (D/A) ConversionDocument15 pagesAnalog-To-Digital (A/D) and Digital-To-Analog (D/A) ConversionproteuscarrillusNo ratings yet

- Opamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreDocument35 pagesOpamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreSatya Prasad AkkinaNo ratings yet

- ADCDACDocument180 pagesADCDACKireetiNo ratings yet

- Sar AdcDocument40 pagesSar AdcNivedini KuttiNo ratings yet

- An5250 PDFDocument20 pagesAn5250 PDFAENo ratings yet

- Vlsi Lab Manua2Document75 pagesVlsi Lab Manua2Nandan Bm100% (1)

- Analog To Digital ConverterDocument5 pagesAnalog To Digital ConverterAnonymous j0aO95fgNo ratings yet

- Chapter 3 - Signal Conversion and ProcessingDocument64 pagesChapter 3 - Signal Conversion and Processingنوار السيلاويNo ratings yet

- Ee101 Dac 1Document159 pagesEe101 Dac 1Piyush KabraNo ratings yet

- Question Bank, 2 Marks With AnswersDocument24 pagesQuestion Bank, 2 Marks With AnswersLohanathan VkNo ratings yet

- Digital-to-Analog and Analog-to-Digital Conversion MethodsDocument32 pagesDigital-to-Analog and Analog-to-Digital Conversion MethodsAzliana Mohd Taib100% (1)

- Chapter 6Document42 pagesChapter 6Henry MaedaNo ratings yet

- Applied ElectronicsDocument37 pagesApplied ElectronicsGuruKPO100% (2)

- ADC Guide: Analog-to-Digital Conversion BasicsDocument30 pagesADC Guide: Analog-to-Digital Conversion BasicsBenedict JoNo ratings yet

- Microprocessor System Design QuestionsDocument87 pagesMicroprocessor System Design QuestionskushalNo ratings yet

- Data Converters Successive Approximation ADC Professor Y. Chiu EECT 7327 Fall 2014Document13 pagesData Converters Successive Approximation ADC Professor Y. Chiu EECT 7327 Fall 2014kaart_3000No ratings yet

- Digital Signal Conditioning (ADCDocument74 pagesDigital Signal Conditioning (ADCMohd Fazli50% (2)

- VLSI LAB MANUAL (10ECL77Document67 pagesVLSI LAB MANUAL (10ECL77raghvendrmNo ratings yet

- Data ConvertersDocument37 pagesData ConvertersAshif MahbubNo ratings yet