Professional Documents

Culture Documents

4ME1010lab07RFOscillatorDesign-v1 02

Uploaded by

Thanhha NguyenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4ME1010lab07RFOscillatorDesign-v1 02

Uploaded by

Thanhha NguyenCopyright:

Available Formats

http://dreamcatcher.

asia/cw

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7

RF Oscillator Design

This courseware product contains scholarly and technical information and is protected by copyright laws

and international treaties. No part of this publication may be reproduced by any means, be it transmitted,

transcribed, photocopied, stored in a retrieval system, or translated into any language in any form, without

the prior written permission of Acehub Vista Sdn. Bhd. or their respective copyright owners.

The use of the courseware product and all other products developed and/or distributed by Acehub Vista

Sdn. Bhd. are subject to the applicable License Agreement.

For further information, see the Courseware Product License Agreement.

Objectives

i)

To design a fixed frequency oscillator circuit based on negative resistance approach

ii)

To perform small-signal verification of the oscillator circuit in frequency domain

iii)

To perform large-signal computer simulation of the oscillator circuit in time and frequency

domains

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 1/14

http://dreamcatcher.asia/cw

1.

Background

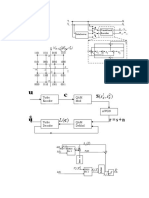

In this lab we will be designing a single transistor fixed frequency oscillator at 470 MHz. We will use an

approach known as negative-resistance oscillator (NRO) method. Please refer to the lecture slides of

ME1000 for detailed theoretical treatment on this subject. Here we will split the transistor oscillator circuit

into a destabilized amplifier and a resonator portion, as shown in Figure 1. We need to come up with a

small-signal amplifier circuit with the impedance looking towards the input given by Z1=R1+jX1 at

fo= 470 MHz. Positive feedback is applied to the amplifier circuit, destabilizing it such that R1 is negative

at fo, hence the name NRO. We then proceed to design a reactive circuit, called the resonator. The

resistance and reactance of the resonator must be such that R1+Rres < 0 and X1 + Xres = 0 at f o. In this

way when the resonator is connected to the destabilized amplifier input, the circuit will (note: not all the

time, see discussion in notes) begin to oscillate near fo when power is supplied to the circuit. Tuning of the

resonator component will bring the oscillation frequency to f o. A large-signal analysis using Harmonic

Balanced method can then be applied to check the steady-state oscillator waveforms, frequency stability,

phase noise, load and supply pulling characteristics and harmonics.

Z1 = R1 + jX1

Resonator

Destabilized

amplifier

Load

Necessary small-signal

conditions for oscillation:

R1 + Rres < 0 at fo

X1 + Xres = 0 at fo

Zres = Rres + jXres

Figure 1 Block Diagram of Negative Resistance Oscillator

The transistor we will be using for this lab is BFR92A, a wideband NPN transistor from NXP

Semiconductors with nominal fT of 5 GHz. This will be more than sufficient for oscillation in the vicinity of

500 MHz.

NOTE: In this lab we will assume that you are already familiar with Genesys user interface, so we will not

show the procedures explicitly as in previous labs but will only show the required schematics and other

windows.

Visit the following YouTube video link to learn more about Genesys:

http://www.youtube.com/user/AgilentEEsof#g/c/20B8D0B20980AA06

Recommended videos for this lab:

1. Genesys Cayenne Nonlinear Time-Domain Transient Circuit Simulator

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 2/14

http://dreamcatcher.asia/cw

2.

RF Oscillator

2.1 DC Biasing Circuit Design for the Destabilized Amplifier

1. As usual run Genesys from Windows desktop.

2. Create a new workspace, add a schematic and insert the transistor BFR92A. Use the Part

Selector A window to find the transistor as shown in Figure 2.

3. Complete the schematic; here we are using a degenerated common-emitter topology for the

transistor. The complete schematic is illustrated in

Figure 3. Use a

supply voltage of 3.3 V. Save the schematic giving it a meaningful name, say Amp_DC.

4. Add a DC analysis into your Workspace (use all the default settings in the DC analysis). Run it

and the DC voltages and current will be displayed in the voltage test points and current probe in

the schematic. Verify that the transistor Q1 is in the active region. See

Figure 3 for the sample results.

Figure 2 Searching and Inserting a Commercial Spice Model (BFR92A)

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 3/14

http://dreamcatcher.asia/cw

SG1

VDC=3.3V

You can also use the DC

voltage source from Part

Selector A

LC

L=220nH

Current probe

IC

IDC=3.665e-3A

RB1

R=47000

VC

VDC=3.3V

VB

VDC=1.165V

Voltage test

point

Q1 {BFR92A@Philips_Wideband}

RE

R=220

Figure 3 The DC Bias Circuit

2.2 Destabilized Amplifier Circuit and AC Analysis

1. Modify your DC biasing schematic as shown in Figure 4. Here series-shunt feedback is used to

make the amplifier unstable. Save your new schematic as DestabAmp_AC.

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 4/14

http://dreamcatcher.asia/cw

Tune these

Standard

Input Port

Load

resistor

Z1 = R1 + jX1

Figure 4 Destabilized Amplifier Circuit and the Linear Analysis Settings

2. Insert a Linear Analysis (or small-signal AC analysis) into your design and refer it to the

DestabAmp_AC schematic. The settings are shown in Figure 4. Lets call this Linear 1.

3. Now run the Linear Analysis. Our aim is to examine the input impedance as a function of

frequency. Open the simulated data for Linear Analysis, insert the necessary plots to show real

and imaginary parts of Z1 (see Figure 5 and Figure 6).

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 5/14

http://dreamcatcher.asia/cw

Plot real and

imaginary parts of Zin

Figure 5 Plotting R1 and X1 Versus Frequency

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 6/14

http://dreamcatcher.asia/cw

ZIN1

100

40

-20

-80

470 MHz, -115.241

re(ZIN1)

-140

-200

-260

-320

-380

-440

-500

100

290

480

670

860

1050

Frequency (MHz)

1240

1430

1620

1810

2000

1240

1430

1620

1810

2000

re(ZIN1)

ZIN1

470 MHz, -98.232

-150

-300

-450

im(ZIN1)

-600

-750

-900

-1050

-1200

-1350

-1500

100

290

480

670

860

1050

Frequency (MHz)

im(ZIN1)

Figure 6 Results of Linear Analysis

4. You need to make sure R1 is negative at 470 MHz. Try tuning capacitors C 1 and C2, and inductor

LC. This will change R1 and X1. Of course, changing the biasing Q1 and loading will have the same

effect. Experiment on your own and refer to the lecture notes and other literature for the details

and mathematical analysis. Typically R1 of 15 or smaller is sufficient to ensure oscillation start up

in the real physical circuit. See lecture notes or books on the effect of R 1 on the steady-state

waveforms.

5. Put a marker at 470 MHz to read out R1 and X1 at 470 MHz. Here R1@470 MHz = 115.24 and X1@470

MHz = 98.23. You need to scale the X and Y axis of the graph to see the waveform as shown in

Figure 6.

2.3 Resonator Design and Time-Domain Verification

1. From the results of last section (2.2), the resonator needs to produce a reactance X res of +98.23 in

order for the final oscillator circuit to oscillate near 470 MHz. This can be realized by an inductor

with inductance of 33 nH. The complete oscillator circuit is shown in Figure 7. Save this

schematic as Osc_Tran. Rres is to model the loss in the inductor by deliberate addition of series

resistor.

2. In order to start-up the oscillation process, a seed signal is needed. In real life this seed signal is

provided by the noise signal in the circuit or transient when we power up the oscillator circuit. This

being a virtual model, we need to artificially provide the seed signal. This is done using a pulse as

shown in Figure 7, connected in series with the DC voltage source. The position of the pulse

source is not crucial. Note that the source frequency is almost zero. This means that within our

normal duration of analysis, we only see a pulse at the start of simulation. After that, this source is

effectively shorted (V = 0).

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 7/14

http://dreamcatcher.asia/cw

VS1

V1=0V

V2=0.1V

TD=0ns

TR=1ns

PW=1ns

TF=1ns

F0=0.00001MHz

SG1

VDC=3.3V

To inject artificial

transient into the

circuit to start the

oscillation process

LC

L=220nH

RB1

R=47000

Resonator

VC

VDC=3.3V

VB

VDC=1.481V

Cc1

C=47pF

Rres

R=5

VL

VDC=0V

Cc2

C=47pF

Destabilized

Amplifier

RL

R=50

Q1 {BFR92A@Philips_Wideband}

C1

C=4.7pF

RE

R=220

Lres

L=33nH

C2

C=6.8pF

Figure 7 Complete Oscillator Circuit

3. Insert a Transient Analysis module with the settings as shown in Figure 8.

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 8/14

http://dreamcatcher.asia/cw

Figure 8 Transient Analysis Settings

4. Now run the Transient Analysis. Plot the voltage at the transistors Collector and Load of the

oscillator. The results are shown in Figure 9. Try changing the value of Rres and see how it affects

the duration of start-up and the steady-state waveforms. Also change L res value and see its effect

on the steady-state oscillation frequency (you can work out the frequency from the voltage

waveforms by first finding the period).

5. Is the steady-state oscillation frequency fosc 470 MHz? Tune Lres so that foscillation is within

0.2 MHz of 470 MHz.

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 9/14

http://dreamcatcher.asia/cw

Voltage

3.2

2.4

1.6

Start-up

Steady-state

V8, V13 (V)

0.8

-0.8

-1.6

-2.4

-3.2

-4

0

10

20

30

40

50

Time (ns)

V8

60

70

80

V13

90

100 of

Note the

number

each connection or net

Figure 9 Voltage Waveforms at Collector and Load from Transient Analysis

2.4 Frequency-Domain Verification

1. We can also perform a frequency domain analysis of the steady-state response of the oscillator

using Harmonic Balance (HB) method. Read up on this by referring to sources from books and

the Internet. Unlike the Transient Analysis which provides the start-up and steady-state view

information, the HB analysis uses optimization method to predict the steady-state voltages and

currents in the circuit. It does this by estimating the magnitude and phase (e.g., the phasor) of

each Fourier component of the voltages and currents.

2. Oscillator analysis using HB approach needs to know the approximate steady-state frequency,

and also whether the circuit is stable or not (if the circuit is not stable, then it wont oscillate and

HB analysis will fail). This is achieved by performing a small-signal or linear analysis of the circuit,

basically a reverse of the procedures that we use in Section 2.2 (note that there are many

approaches to analyse stability of a system). The small-signal analysis will tell the HB analysis

engine the estimated oscillation frequency, and the HB engine will use this information to predict

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 10/14

http://dreamcatcher.asia/cw

the large-signal (or steady-state) voltage and current phasors. The small-signal analysis is done

automatically in Genesys, in the form of Oscillator Port. Modify the Osc_Tran schematic of

Section 2.3 to the circuit shown in Figure 10. Save this as Osc_HB.

Initially use

information from

Section 2.2

SG1

VDC=3.3V

LC

L=220nH

OSCPORT_OSCPORT_1

FOSC=470MHz

VPROBE=0V

Cc2

C=47pF

RB1

R=47000

VC

VDC=3.3V

VB

VDC=1.481V

Cc1

C=47pF

R1

R=10

RL

R=50

Q1 {BFR92A@Philips_Wideband}

C1

C=4.7pF

RE

R=220

L1

L=33nH

C2

C=6.8pF

Figure 10 The Schematic for Harmonic Balance (HB) Analysis of Oscillator

3. Insert a Harmonic Balance Oscillator Analysis module into your Workspace, call this HBOSC1.

Set it as shown in Figure 11. Run the analysis.

4. Open the data from HBOSC1. You can see a variety of data, those that show the voltage or

current phasors and the time-domain waveforms. See Figure 12. The time-domain waveforms are

obtained by performing summing of all the Fourier components of a voltage or current. For

instance, the voltage at transistors Collector terminal in time and frequency domain is shown in

Figure 12. Observe the voltage phasor at the load. Tune the components in the circuit to see if

you can reduce the harmonics at the load.

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 11/14

http://dreamcatcher.asia/cw

The highest Fourier

component to consider

(The larger the more

accurate but takes more

computational time)

Figure 11 Settings for HB Analysis of Oscillator

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 12/14

http://dreamcatcher.asia/cw

This is frequency domain data,

e.g., voltage phasor.

W indicates time-domain, e.g.,

waveform. You can also see the

time-domain waveform of other

voltages and currents. Explore for

yourself or seek out Genesyss

help to see how this is done.

W_VVC

3.7

VVC

3.58

3.46

3.34

VVC (V)

W_VVC (V)

3.22

3.1

2.98

2.86

0.1

2.74

2.62

2.5

0

0.431

0.861

1.292

1.723

2.153

Time (ns)

2.584

3.014

3.445

3.876

4.306

240

480

720

960

W_VVC

1200

Frequency (MHz)

1440

1680

1920

2160

2400

VVC

Figure 12 The Results of HB Analysis

3.

Review Questions

1. If we require that the oscillation frequency be 500 MHz instead of 470 MHz, should we increase

or decrease the inductance of L1?

2. What will happen if the capacitance CC1 is too small?

3. Modify your schematicby replacing L1 with a series LC network, with the C tunableinto a

variable frequency oscillator. Suggest an approach to implement a voltage-controlled variable

capacitor, and with this, modify your circuit into a voltage-controlled oscillator (VCO).

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 13/14

http://dreamcatcher.asia/cw

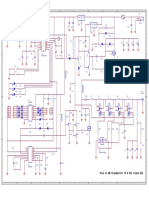

Appendix Screenshot of the Complete Workspace

ME1010 RF Circuit Design (Agilent Genesys)

Lab 7 - 14/14

You might also like

- Integrators, Differentiators, and Simple Filters: 6. PrelabDocument15 pagesIntegrators, Differentiators, and Simple Filters: 6. PrelabMIn LeNo ratings yet

- Elvis and Bode PlotsDocument7 pagesElvis and Bode PlotsKashif AmjadNo ratings yet

- AnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar SurarapuDocument80 pagesAnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar Surarapuprabhu4scribdNo ratings yet

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDocument8 pagesRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiNo ratings yet

- Aim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpDocument8 pagesAim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpAvinash Nandakumar100% (1)

- Function Generator Op-Amp Summing Circuits Pulse Width Modulation LM311 ComparatorDocument7 pagesFunction Generator Op-Amp Summing Circuits Pulse Width Modulation LM311 ComparatorMuhammad JunaidNo ratings yet

- That You Read All The Background Information of This Laboratory BEFORE Proceding With The ExperimentDocument14 pagesThat You Read All The Background Information of This Laboratory BEFORE Proceding With The ExperimentRajith MohananNo ratings yet

- Equency Response of A Common-Emitter BJT AmplifierDocument5 pagesEquency Response of A Common-Emitter BJT AmplifierThomas SmithNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- Experiment 6: Oscillator Circuits and CharacteristicsDocument24 pagesExperiment 6: Oscillator Circuits and CharacteristicsSittie Ainna A. UnteNo ratings yet

- Laboratory 4 - Feedback and CompensationDocument6 pagesLaboratory 4 - Feedback and CompensationbaymanNo ratings yet

- Lab 1-Bjt AmplifierDocument8 pagesLab 1-Bjt Amplifierhasnain3257100% (1)

- RC OscillatorDocument8 pagesRC OscillatorRavi TejaNo ratings yet

- LABreportcommsDocument5 pagesLABreportcommsNoriel MendozaNo ratings yet

- Eca Lab-Min PDFDocument87 pagesEca Lab-Min PDFAkashita SharmaNo ratings yet

- EC1 Lab Exp3 PDFDocument2 pagesEC1 Lab Exp3 PDFRitu RoyNo ratings yet

- Integrator Circuits: 7.0.1 ReadingDocument5 pagesIntegrator Circuits: 7.0.1 Readingnaveenkv10_105528408No ratings yet

- 2018 Ee 69Document19 pages2018 Ee 69Ali MohsinNo ratings yet

- Laboratory Manual: Unified Electronics Laboratory-IiDocument28 pagesLaboratory Manual: Unified Electronics Laboratory-IiAtul SainiNo ratings yet

- RC Phase Shift Oscillator Circuit AnalysisDocument3 pagesRC Phase Shift Oscillator Circuit Analysisskmrajkumar100% (2)

- Procedure - AC Circuits and Signal Modulation - W20Document6 pagesProcedure - AC Circuits and Signal Modulation - W20ChocoNo ratings yet

- Low - Pass FilterDocument8 pagesLow - Pass FilterSaurabh BhiseNo ratings yet

- EC Lab ManualsDocument53 pagesEC Lab ManualsArish AliNo ratings yet

- Texas A&M VCO Lab: CMOS LC Oscillator Analysis & SimulationDocument8 pagesTexas A&M VCO Lab: CMOS LC Oscillator Analysis & SimulationRekha YadavNo ratings yet

- AEC LabManualDocument30 pagesAEC LabManualPrateek PaliwalNo ratings yet

- U17EC017 Lab8Document6 pagesU17EC017 Lab8rosestrikesNo ratings yet

- Experiment 9: Inductor Circuit AnalysisDocument5 pagesExperiment 9: Inductor Circuit AnalysisGlenn VirreyNo ratings yet

- Eee334 Lab#1 Ltspice and Lab Orientation - Instruments and MeasurementsDocument9 pagesEee334 Lab#1 Ltspice and Lab Orientation - Instruments and Measurementsplaystation0% (1)

- Lab 1 Report: Ho Nguyen Bao Tran Le Huynh Minh NguyetDocument20 pagesLab 1 Report: Ho Nguyen Bao Tran Le Huynh Minh NguyetBin BinNo ratings yet

- Emitter Transistor Amplifier VjezbaDocument4 pagesEmitter Transistor Amplifier VjezbaNeda SpasojevićNo ratings yet

- Design A RC Coupled CE Transistor AmplifierDocument7 pagesDesign A RC Coupled CE Transistor AmplifierSudeep Nayak100% (1)

- Electronic Circuits & Logic Design Lab ManualDocument83 pagesElectronic Circuits & Logic Design Lab ManualsunandaalurNo ratings yet

- Laboratory Report on Integrator and Differentiator CircuitDocument22 pagesLaboratory Report on Integrator and Differentiator CircuitHrivu Dasmunshi (RA1911004010566)No ratings yet

- Two StageDocument6 pagesTwo StageSiphosethuSidloyiNo ratings yet

- Paper English Laporan Kerja PraktekDocument4 pagesPaper English Laporan Kerja PraktekKelik Fazar Hadi SaputroNo ratings yet

- Lica Lab ManualDocument53 pagesLica Lab ManualGowtham KannegantiNo ratings yet

- "How To Design RF Circuits" - OscillatorsDocument7 pages"How To Design RF Circuits" - OscillatorsAbbas Bagherifar100% (8)

- Function GeneratorDocument13 pagesFunction GeneratorDilJalaayNo ratings yet

- Common Base Amplifier Circuit AnalysisDocument3 pagesCommon Base Amplifier Circuit AnalysisHatem DheerNo ratings yet

- Lab 5 & 6Document9 pagesLab 5 & 6Nadim Al DroubiNo ratings yet

- Experiment 2 Basic Operational Amplifier CircuitsDocument7 pagesExperiment 2 Basic Operational Amplifier CircuitsVasursharpNo ratings yet

- Ring OscillatorDocument12 pagesRing OscillatorCmeLiv InmyHart NpaynoRentNo ratings yet

- L.C Oscillator Tutorial: 1 AbstractDocument18 pagesL.C Oscillator Tutorial: 1 AbstractChi PhamNo ratings yet

- ECA ManualDocument62 pagesECA ManualAnonymous gP8ivl7fNo ratings yet

- Behaviour of Second Order SystemsDocument2 pagesBehaviour of Second Order SystemsGokul Potdar0% (1)

- Wein Bridge Oscillator: f =1/2π√R1C1R2C2Document11 pagesWein Bridge Oscillator: f =1/2π√R1C1R2C2krishna goggiNo ratings yet

- EE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentDocument7 pagesEE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentTanmay JainNo ratings yet

- Circuits Docs Labs Lab3 First and Second Order ResponsesDocument8 pagesCircuits Docs Labs Lab3 First and Second Order ResponsesCesar Santiago Bolaño SalazarNo ratings yet

- RC CoupledDocument3 pagesRC CoupledRavi TejaNo ratings yet

- Sharmi ECE a-D-Circuits Lab ManualDocument74 pagesSharmi ECE a-D-Circuits Lab ManualSharmila83No ratings yet

- Eca Lab Manual PDFDocument56 pagesEca Lab Manual PDFrppvch100% (5)

- Experiment 10 Lab ActivityDocument4 pagesExperiment 10 Lab ActivityGlenn VirreyNo ratings yet

- Ec6411 EC II Lab Manual 2013Document89 pagesEc6411 EC II Lab Manual 2013Karthik SingaramNo ratings yet

- RC Phase Shift Oscillator PDFDocument9 pagesRC Phase Shift Oscillator PDFA B ShindeNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Operational Amplifier Circuits: Analysis and DesignFrom EverandOperational Amplifier Circuits: Analysis and DesignRating: 4.5 out of 5 stars4.5/5 (2)

- Analog Filters Using MATLABDocument14 pagesAnalog Filters Using MATLABThanhha NguyenNo ratings yet

- 13 Commsys Rev5 Lab5Document22 pages13 Commsys Rev5 Lab5Thanhha NguyenNo ratings yet

- 1I308A_1I308B_1I308V_1I308G_1I308D_1I308E_1I308ZH_1I308I_1I308KDocument1 page1I308A_1I308B_1I308V_1I308G_1I308D_1I308E_1I308ZH_1I308I_1I308KThanhha NguyenNo ratings yet

- Sga 6589Document4 pagesSga 6589Thanhha NguyenNo ratings yet

- Microwaves101 - Spectrum AnalyzerDocument9 pagesMicrowaves101 - Spectrum AnalyzerThanhha NguyenNo ratings yet

- Gain Characterization of The RF Measurement Path: J. Wayde AllenDocument20 pagesGain Characterization of The RF Measurement Path: J. Wayde AllenThanhha NguyenNo ratings yet

- Схема Блока Питания ТрансивераDocument17 pagesСхема Блока Питания ТрансивераThanhha NguyenNo ratings yet

- Programming a PSoC Microcontroller to Control Temperature Using C and PSoC DesignerDocument12 pagesProgramming a PSoC Microcontroller to Control Temperature Using C and PSoC DesignerThanhha NguyenNo ratings yet

- My C NotesDocument30 pagesMy C NotesBrijendra Mohan GuptaNo ratings yet

- H 11 Aa 1Document7 pagesH 11 Aa 1Josetheking CrackedsoftwaresNo ratings yet

- V An Innovative Magnetic Field Sweep Unit: of of of ofDocument20 pagesV An Innovative Magnetic Field Sweep Unit: of of of ofBerthaFloresNo ratings yet

- Scanner: Monitor. Protect. Control. Visualize. CommunicateDocument2 pagesScanner: Monitor. Protect. Control. Visualize. CommunicateThanhha NguyenNo ratings yet

- Us 7088830Document9 pagesUs 7088830Thanhha NguyenNo ratings yet

- 307RF Rudra38Document6 pages307RF Rudra38Thanhha NguyenNo ratings yet

- 0632 Hf/uhf Field Radio EquipmentDocument166 pages0632 Hf/uhf Field Radio EquipmentRamon C. Pastores100% (2)

- Osciladores Simplificados Con Proyectos by EnigmaelectronicaDocument261 pagesOsciladores Simplificados Con Proyectos by EnigmaelectronicaCarlos RamirezNo ratings yet

- Serial DDS Controller: Dave Ek, NK0E George Heron, N2APBDocument1 pageSerial DDS Controller: Dave Ek, NK0E George Heron, N2APBThanhha Nguyen100% (1)

- FM Digital Tuner FM 数字调谐器Document4 pagesFM Digital Tuner FM 数字调谐器Thanhha NguyenNo ratings yet

- Wireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF Modules - Embedded LabDocument12 pagesWireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF Modules - Embedded Labmoonaliawan100% (3)

- FM Digital Tuner FM 数字调谐器Document4 pagesFM Digital Tuner FM 数字调谐器Thanhha NguyenNo ratings yet

- Bai BaoDocument1 pageBai BaoThanhha NguyenNo ratings yet

- 7 PLL Synthesizer 4 55Document55 pages7 PLL Synthesizer 4 55Thanhha NguyenNo ratings yet

- ME1010 RF Circuit Design (Agilent Genesys) Lab 7 RF Oscillator DesignDocument14 pagesME1010 RF Circuit Design (Agilent Genesys) Lab 7 RF Oscillator DesignThanhha NguyenNo ratings yet

- Koch 2016Document331 pagesKoch 2016Thanhha NguyenNo ratings yet

- Pira - CZ AM Transmitter 25 W PLL Class D/E: VIN VoutDocument1 pagePira - CZ AM Transmitter 25 W PLL Class D/E: VIN VoutThanhha NguyenNo ratings yet

- Schottky Barrier Diodes: Lead (PB) - FreeDocument2 pagesSchottky Barrier Diodes: Lead (PB) - FreeDario G. MartinezNo ratings yet

- 7 PLL Synthesizer 4 55Document55 pages7 PLL Synthesizer 4 55Thanhha NguyenNo ratings yet

- 93071ADocument10 pages93071AThanhha NguyenNo ratings yet

- Wireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF Modules - Embedded LabDocument12 pagesWireless Data Transmission Between Two PIC Microcontrollers Using Low-Cost RF Modules - Embedded Labmoonaliawan100% (3)

- ET Tut5 Aut2014Document3 pagesET Tut5 Aut2014SaumoPal0% (1)

- RCF MB15H401Document2 pagesRCF MB15H401Domnu_BibiNo ratings yet

- Basic Electronic Troubleshooting For Biomedical Technicians 2edDocument239 pagesBasic Electronic Troubleshooting For Biomedical Technicians 2edClovis Justiniano100% (22)

- Solar Tracker Using LDRDocument3 pagesSolar Tracker Using LDRIJRASETPublicationsNo ratings yet

- Introduction To Electronics, Familiarization With Basic Electronic Components and Measuring Instruments.Document66 pagesIntroduction To Electronics, Familiarization With Basic Electronic Components and Measuring Instruments.Dogra100% (1)

- PV Cell ModelingDocument12 pagesPV Cell Modelingtran duyNo ratings yet

- Manual de Servicio 4540cDocument1,515 pagesManual de Servicio 4540cxephah stradaNo ratings yet

- Agency Product List: Basler Part Number Description Rohs2-2015 Reach RegulationDocument4 pagesAgency Product List: Basler Part Number Description Rohs2-2015 Reach RegulationAnonymous 1AAjd0No ratings yet

- Case Expansion Measurements: Configuration and Verification ManualDocument44 pagesCase Expansion Measurements: Configuration and Verification ManualRabah AmidiNo ratings yet

- Mechatronic Trade - Professional Practice Judgment 2017 Ver. 1.4Document12 pagesMechatronic Trade - Professional Practice Judgment 2017 Ver. 1.4Daniel Ernesto EspitiaNo ratings yet

- 14 XS DLX 15 - 11039691Document22 pages14 XS DLX 15 - 11039691Ramdek Ramdek100% (1)

- ET Quiz3Document11 pagesET Quiz3Pradeep Kumar BowmarajuNo ratings yet

- Datalogic Safety Light Curtains - Advanced Series, Hand-SafeDocument17 pagesDatalogic Safety Light Curtains - Advanced Series, Hand-SafeNoe CastroNo ratings yet

- Ohm's Law electrical concepts quiz answers and explanationsDocument14 pagesOhm's Law electrical concepts quiz answers and explanationsDerlyn FernandezNo ratings yet

- Capacitor Uf - NF - PF Conversion Chart PDFDocument4 pagesCapacitor Uf - NF - PF Conversion Chart PDFRachel RowlandNo ratings yet

- Trafo Erection and MAINTENANCEDocument23 pagesTrafo Erection and MAINTENANCEgm29No ratings yet

- A WC 708 Lite User ManualDocument12 pagesA WC 708 Lite User ManualFernando ZaiaNo ratings yet

- Schematic P185WJD PDFDocument7 pagesSchematic P185WJD PDFFelipe Infante LeónNo ratings yet

- Gujarat Technological University: Page 1 of 4Document4 pagesGujarat Technological University: Page 1 of 4Darshit KotadiyaNo ratings yet

- Copper WeightDocument4 pagesCopper Weightmajid_20100% (1)

- Freja RTS21DDocument8 pagesFreja RTS21DrohitduraiNo ratings yet

- So Do Dien D7RDocument2 pagesSo Do Dien D7RVinh Trinhvinhub50% (2)

- PHYSICS FORM 5 CHAPTER 1 WAVES AND ELECTRICITYDocument4 pagesPHYSICS FORM 5 CHAPTER 1 WAVES AND ELECTRICITYsyeddnNo ratings yet

- Importance of Electricity in the Modern AgeDocument2 pagesImportance of Electricity in the Modern AgeMT RANo ratings yet

- InverterDocument71 pagesInverterAlade Victor100% (14)

- ACTURA Durus 48350 BrochureDocument2 pagesACTURA Durus 48350 BrochurePowerstorm0% (1)

- Active Barrier RN221NDocument8 pagesActive Barrier RN221NOleg SidNo ratings yet

- DSR-200 - 200P No SchemDocument215 pagesDSR-200 - 200P No SchemКонстантин ЯминскийNo ratings yet

- Proprietary Electronics For Reactor Safety and ControlsDocument13 pagesProprietary Electronics For Reactor Safety and ControlsVarshaNo ratings yet

- Conductors and Electric Field in Static EquilibriumDocument1 pageConductors and Electric Field in Static Equilibriumfrance villNo ratings yet