Professional Documents

Culture Documents

Chap 4 Les Circuits Sequentiels

Uploaded by

Kycelle MbouzekoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chap 4 Les Circuits Sequentiels

Uploaded by

Kycelle MbouzekoCopyright:

Available Formats

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

1. INTRODUCTION

Un circuit combinatoire est un circuit numrique dont les sorties dpendent uniquement des

entres: = ( ).

Ltat du systme ne dpend pas de ltat interne du systme ; Pas de mmoration de ltat du

systme.

Les circuits logiques combinatoires ne suffisent pas eux seuls la manipulation de

linformation comme cela se fait dans les systmes numriques modernes. Le caractre fig des

circuits combinatoires, que traduit la correspondance stricte entre les entres et les sorties, limite

considrablement le champ de leurs applications. Cest l que les circuits squentiels prennent

toute leur importance. Ces derniers permettent la mise au point de systmes dont le

fonctionnement dpend non plus seulement des entres reues, mais galement des informations

traites prcdemment dans le cours de leur fonctionnement.

2. LES CIRCUITS SEQUENTIELS

Un circuit logique squentiel est un circuit logique possdant des entres et des sorties et

prsentant un comportement o les sorties ne dpendent pas seulement des entres, mais

galement des squences des entres passes.

Figure 4.1 : Circuit logique squentiel

Ltat linstant t+1 est une fonction des entres en mme instant t+1 et de ltat prcdente du

systme (linstant t) :

= ( , )

3. SYSTEME SYNCHRONE ET ASYNCHRONES (notion de lhorloge)

Une horloge est une variable logique qui passe successivement de 0 1 et de 1 0 dune faon

priodique. Cette variable est utilise souvent comme une entre des circuits squentiels : le

circuit est dit synchrone.

Lhorloge est note par h ou clk (clock).

Figure 4.2 : Circuit squentiel synchrone

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 30

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Lhorloge

Figure 4. 3 : Exemple de signal dhorloge

Les systmes Asynchrones

Lorsquun circuit squentiel na pas dhorloge comme variable dentre ou si le circuit

fonctionne indpendamment de cette horloge alors ce circuit est asynchrone.

Figure 4. 4 : Circuit squentiel asynchrone

4. LES BASCULES (flip-flops)

Les bascules sont les circuits de bases de la logique squentiel ; elles peuvent possder une

horloge (synchrone) ou non (asynchrone). Chaque bascule possde des entres et deux sorties :

et .Une bascule possde la fonction de mmoration et de basculement.

Figure 4. 5 : symbole dune Bascule

Il existe plusieurs types de bascules :T ,RS, RST ,D ,JK

4.1.Bascule RS (Reset, Set)

Le circuit bistable RS est un circuit logique rtroaction simple permettant denregistrer un

bit. Le nom SR vient du fait que la bistable possde deux entres, S et R, renvoyant

respectivement Set et Reset. Lorsque lentre S est 1, le circuit enregistre un 1 sa sortie Q.

Lorsque lentre R passe 1, le circuit est rinitialis et il enregistre 0 sa sortie Q. Cela nest

possible que si S et R ne valent pas 1 en mme temps. Si S et R valent tous deux 0, le systme est

stable et mmorise la dernire valeur enregistre.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 31

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

b) CIRCUIT INTERNE

a) SYMBOLE

c) TABLE DE VERITE

S

0

0

0

0

1

1

1

1

R

0

0

1

1

0

0

1

1

Qt

0

1

0

1

0

1

0

1

Q+

S

0

0

1

1

R

0

1

0

1

Q+

mmorisation

Mise 0

Mise 1

Interdit

d) DIAGRAMME TEMPOREL

4.2.Bascule RS synchrone

La bascule RSH est une bascule RS synchronise par un signal dhorloge H. Lorsque H

est au niveau bas, la bascule fonctionne comme une mmoire, et lorsque H est au niveau haut, la

bascule fonctionne comme une bascule RS classique, et conserve donc les tats interdits pour

R=S=1.

a) Symbole

S

X

0

0

1

1

b) Table de vrit

R

H

X

0

0

1

1

1

0

1

1

X

Qt+1

Exemple

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 32

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

4.3.Bascule JK

Les bascules JK sont des bascules matre-esclave fonctionnant seulement en mode synchrone.

Elles sont plus polyvalentes que les basculent RS, car elles nont pas dtat ambigu. Sachant que

les sorties sont toujours complmentaires, leur rebouclage sur les entres limine ltat interdit. Il

ny a pas dinconvnient ce rebouclage car les sorties de lesclave ne change dtat que lorsque

le matre est bloqu. Les bascules JK sont trs courantes dans les systmes numriques.

a) Symbol

b) Table de vrit

4.4.Bascule D

La bascule D est une bascule matre-esclave conue sur le mme principe que la JK. La bascule

D est une bascule nayant quune seule entre nomme D.

a) Symbole

b) Table de vrit

5. LES REGISTRES

5.1.Dfinition

Un registre est un circuit constitu de n bascules synchronises permettant de stocker

temporairement un mot binaire de n bits en vue de son transfert dans un autre circuit (pour

traitement, affichage, mmorisation, etc.).

5.2. Registre de mmorisation : criture et lecture parallles

Tous les bits du mot traiter sont crits (entre criture E=1), ou lus, (entre lecture

L=1), simultanment.

Figure 4.6: stockage en parallle et transfert en parallle dun mot de 4 bits

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 33

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

5.3.Registres dcalage

Comme son nom lindique, un registre dcalage consiste dcaler bit par bit un mot

binaire soit vers la gauche, soit vers la droite. Le registre dcalage peut tre criture et

lecture srie ou parallle.

5.3.1. Registre criture srie et lecture srie

Aprs 4 pulsations de CLK, les 4 bits sont entrs dans le registre. Aprs 4 autres cycles

dhorloge, les 4 bits sont dplacs vers la sortie. Leur application est essentiellement le calcul

arithmtique binaire. CLK est alors lentre de dcalage.

5.3.2. Registre criture srie et lecture parallle

Lorsque lentre est stocke, chaque bit apparat simultanment sur les lignes de sortie. Le

registre dcalage est utilis comme convertisseur srie parallle. Il est ncessaire la rception

lors dune transmission srie.

5.3.3. Registre criture parallle et lecture srie

Utilis comme convertisseur parallle-srie, il est ncessaire lmission lors dune transmission

srie.

Figure 4.7: Registre criture parallle et lecture srie

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 34

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

5.4.Registre universel

Le registre universel permet quatre modes de fonctionnement commands par deux

variables S1 et S2.

a) Table de fonctionnement

b)

Circuit intgr

6. LES COMPTEURS

Un compteur est un circuit squentiel comportant n bascules dcrivant au rythme dune

horloge un cycle de comptage rgulier ou quelconque dun maximum de 2 combinaisons.

La combinaison de sortie dun compteur est appel tat, et le nombre dtats possibles

dun compteur est appel modulo.

6.1.Compteur asynchrone ( propagation)

En cascadant des bascules JK montes en diviseurs de frquence, on peut donc raliser un

compteur dont le modulo dpendra du nombre de bascules.

6.1.1. Compteur asynchrone cycle rgulier

Exemple dun Compteur asynchrone 4 bits (compte de 0 15)

La sortie de chaque bascule agit comme le signal dhorloge de la suivante.

a. Fonctionnement

J=K=1 ; toutes les bascules commutent sur des fronts descendants ;

la bascule A commute chaque front descendant du signal dhorloge ;

la sortie de la bascule 1 sert dhorloge pour la bascule 2 B commute chaque fois que A

passe de 1 0 ;

de la mme manire, C commute lorsque B passe de 1 0, et D commute lorsque C passe de 1

0.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 35

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

b. Table dimplication squentielle

Si on imagine que DCBA reprsente un nombre binaire, le

compteur ralise la suite des nombres binaires allant de 0000

1111(soit de 0 15). Aprs la 15me impulsion, les bascules

sont dans la condition 1111. Quand la 16me impulsion

arrive, le compteur affiche 0000 : un nouveau cycle

commence.

c. Chronogrammes

Remarque : chaque bascule divise par deux la frquence dhorloge qui alimente son entre CLK :

=

Exemple dapplication 1: Concevez un compteur asynchrone modulo 8.calculez la frquence

la sortie de la dernire bascule si la frquence du signal dhorloge est de 3kHz. Faite les

chronogrammes du compteur.

6.1.2. Dcompteurs asynchrones

Il suffit de piloter chaque entre CLK des bascules au moyen de la sortie complmente de la

bascule prcdente.

Exemple : dcompteur modulo 8

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 36

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Chronogramme

6.1.3. Compteur asynchrone modulo

<

( cycle rgulier)

Pour raliser un compteur ou un dcompteur dont le cycle nest pas une puissance de

2, la seule solution est dagir sur lentre Clear lorsque la combinaison correspondant au

modulo du compteur se produit sur les sorties de celui-ci. Ainsi, pour2

< < 2 , on ralise

un compteur modulo 2n (avec n bascules), puis on raccourcit le cycle en jouant sur les entres

RAZ des bascules.

Exemple : Compteur asynchrone modulo 6 :2 < 6 < 2

on ralise un compteur modulo 3 avec 3 bascules, et on ramne le compteur 000 ds que

= 110

ds que la sortie de la porte NAND passe 0, les bascules sont forces 0 : le compteur se

remet compter partir de 0.

le compteur ralis compte de 000 101 (de 0 5) puis recommence un nouveau cycle

Exemple dapplication 2: Concevez un compteur asynchrone dcimal. Calculez la frquence

la sortie de la dernire bascule si la frquence du signal dhorloge est de 3kHz. Faite les

chronogrammes du compteur.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 37

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

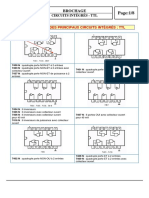

6.1.4. Exemple de CI

Il existe de nombreuses puces en technologies TTL et CMOS. Parmi les plus populaires

on trouve en TTL le 7493 qui est un compteur 4 bits, et en CMOS le 4024 qui est un compteur 7

bits.

MR Master Reset.

6.2.Compteur Synchrone (parallle)

Toutes les bascules sont dclenches en mme temps par le mme signal dhorloge. Ceci

vite le problme du retard de propagation.

6.2.1. Table de transition dune bascule JK

On connait les valeurs des sorties, comment dterminer les valeurs des entres JK ?

Q

0

0

1

1

Q+

0

1

0

1

6.2.2. Etude des compteurs synchrones modulo

Exemple1 : ralisation dun compteur modulo 8 (bascule JK) : n=3 ; toutes les bascules

possdent la mme horloge. Pour raliser le compteur, il faut dterminer les quations des Ji et

Ki ?

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 38

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Daprs la table de vrit on trouve :

J0=K0=1 , J1=K1=Q0 , J2=K2=Q0.Q1

Exemple2 : ralisation compteur modulo 8 (bascule D) :

Q2

Q1

Q0

Q2+

Q1+

Q0+

D2

D1

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

D0

Page 39

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Exemple dapplication 3: Concevez un compteur synchrone dcimal bascules JK.

6.2.3. Compteur synchrone cycle quelconque

Soit le compteur ayant le cycle suivant

Pour forcer le compteur dun tat un autre il faut agir sur les entres synchrones Ji et

Ki ;Pour les tats qui nappartiennent pas au cycle du compteur, il faut les considrer comme

tant des tats indtermins ( Ji=X et Ki=X).

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 40

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Exemple dapplication 4 : Concevez un compteur dcompteur pair synchrone modulo 16

bascule JK.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 41

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

7. EXERCICE

Exercice 1 :

Soit le montage de la figure 1

a) Donnez sa table de vrit.

b) Quel circuit logique reconnaissez-vous ?

c) Remplissez le chronogramme suivant :

Figure 1

Exercice 2 :

2.1. Supposez que Q=0 au dbut. Appliquez les formes donde x et y de la figure 2 au entres A

et B dune mmoire en PORTES NON-ET (figure 1) et dterminez les formes donde de

2.2. Intervertissez les formes dondes de la figure 2, puis appliquez les aux entres R et S dune

mmoire en PORTES NI ; dterminez les formes donde de . Supposez que Q=0 au

dpart.

2.3. Les formes dondes de la figure 2 sont appliques au circuit de la figure 3. Supposez que

Q=0 au dpart ; dterminez les formes donde de .

Figure 2

Figure 3

Exercice 3 :

3.1. Une bascule de commutation na quune entre et sa sortie change dtat chaque fois

quune impulsion arrive sur son entre. Il est possible de cbler une bascule S-C synchrone pour

quelle fonctionne en mode de commutation, voir figure 4. La forme donde applique lentre

CLK est celle dune onde carre de 1Khz.

a) Assurez-vous que ce montage fonctionne comme une bascule de commutation, puis

tracez la forme donde de la sortie Q. Supposez que Q=0 au dpart.

b) Montrez comment il est possible dutiliser une Bascule J-K comme bascule de

commutation. Appliquez une onde carre de 10Khz lentre et tracez la forme donde de sortie.

c) Connectez la sortie Q de cette bascule (de commutation JK) lentre CLK dune

seconde bascule ayant galement J=K=1. Trouvez la frquence de la forme donde de sortie de

cette bascule.

3.2. Soit les deux bascules JK ci-dessous :

Figure 4

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 42

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

a) Rappelez la table de vrit dune bascule JK synchronise sur front montant.

b) Remplissez le chronogramme suivant :

3.3. Soit le montage ci-dessous :

Remplissez le chronogramme suivant :

Exercice 4 :

4.1. Dessinez le schma dun circuit qui assure le transfert parallle synchrone des donnes entre

un registre de 3 bits et une autre form de bascules J-K.

4.2. a) Indiquez combien il faut de bascules pour construire un compteur binaire dont lintervalle

de comptage va de 0 1023

b) Calculez la frquence du signal de sortie de la dernire bascule de ce compteur si la

frquence du signal dentre est 2Mhz.

c) Dites quel est le modulo de ce compteur.

d) Si le compteur est zro au dbut, quel nombre contient-il aprs 2060 impulsions

4.3. Un compteur est synchronis un signal dhorloge de 256Khz ; la frquence de la sortie de

la dernire bascule est de 2Khz.

a) Trouvez le modulo

b) Indiquez lintervalle de comptage

Exercice 5 :

5.1. Une onde carre de 8Mhz synchronise un compteur propagation de 5bits.

a) Quel est la frquence du signal la dernire bascule ?

b) supposant que ce compteur a comme tat initial 00000, quel sera son contenu aprs l44

impulsions dentre

5.2. Ralisez un compteur asynchrone modulo 24 bascule J-K et tracez les chronogrammes des

sorties.

5.3. a) Dessinez le schma dun dcompteur MODULO 16

b) Construisez le graphe des tats.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 43

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

c) Si le nombre initial du compteur est ltat du compteur 0110, quel est ltat du compteur

aprs la 37 impulsions ?

Exercice 6 :

6.1. Tracez le schma du circuit dun compteur parallle Modulo-64

6.2. La figure 5 reproduit un compteur parallle de 4 bits conu de faons ne pas passer toute la

suite des 16 tats binaires possibles. Analysez son fonctionnement en traant les formes dondes

pour chaque sortie des bascules. Ensuite, dterminez la suite des nombres de ce compteur.

Toutes les bascules sont zro au dpart.

Figure 5

Exercice 7 :

On souhaite raliser, en un seul circuit, un compteur/dcompteur asynchrone modulo 16.

Ce montage devra possder deux modes de fonctionnement : un mode compteur et un mode

dcompteur. La slection du mode seffectuera l'aide d'une entre S qui respectera les

conditions suivantes :

S = 0 mode compteur ;

S = 1 mode dcompteur.

Vous avez votre disposition quatre bascules JK et toutes les portes logiques ncessaires. Les

bascules sont synchronises sur front montant et possdent une entre de reset asynchrone active

ltat haut.

a). Donnez le schma de cblage du compteur/dcompteur.

b). Ajoutez un interrupteur automatique de remise zro lallumage.

c). Ajoutez un interrupteur manuel de remise zro.

d). Que suffit-il de faire pour remplacer les bascules JK par des bascules D ?

Exercice 8 :

La figure 6 montre comment un dcompteur prrglable peut tre utilis comme minuterie

programmable. La frquence du signal dhorloge est prcisment 1Hz ; cette frquence est

drive de la frquence de 60 Hz du secteur quon divise par 60. Les interrupteurs S1 S4

servent installer dans le compteur un nombre de dpart voulu lorsquune impulsion

momentane est applique

. Le fonctionnement de la minuterie est lanc en appuyant sur

linterrupteur bouton poussoir Start. La bascule Z sert liminer les rebonds de linterrupteur

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 44

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

Start. Le monostable produit une impulsion trs troite appliqu lentre . La sortie de la

bascule X est une forme donde qui reste 1 durant un nombre de secondes gal au nombre

install par les interrupteurs.

a). Supposez que toutes les bascules et que le compteur sont 0. Analyser et expliquer le

fonctionnement du circuit, si ncessaire au moyen de formes dondes, pour le cas S1 et S4 = 0 et

S2 et S3 = 1. Assurez-vous de bien expliquez le rle de la bascule X.

b). Dites pourquoi la sortie de la minuterie ne peut tre prleve la sortie

.

c). Dites pourquoi on ne peut utiliser linterrupteur Start pour dclencher directement le

monostable.

d). Dites ce qui ce passe si linterrupteur Start est enfonc trop longtemps. Ajoutez les

circuits logiques ncessaires qui font en sorte que linterrupteur Start enfonc trop longtemps na

plus deffet sur la minuterie.

Figure 6

Exercice 9 :

Soit le montage ci-dessous :

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 45

CHAPITRE IV : CIRCUITS LOGIQUES SEQENTIELS

a). Remplissez le chronogramme suivant si lentre E vaut zro :

b). Que ralise ce montage ?

Exercice 10 :

a) Remplissez la table des transitions dune bascule JK.

Dans un premier temps, on dsire raliser un compteur synchrone modulo 7 laide de bascules

JK synchronises sur front montant.

b) laide de la table des transitions, remplissez le tableau ci-dessous :

c) Donnez les quations des entres J0, K0, J1, K1, J2et K2.

d) Dessinez le schma de cblage.

On dsire maintenant raliser un compteur synchrone, modulo 8 en code Gray, laide de

bascules JK synchronises sur front descendant.

e) Remplissez le tableau ci-dessous :

f) Donnez les quations des entres J0, K0, J1, K1, J2et K2.

BY PaTRICK JUVeT gNeTCHeJO: P.L.e.T IN eLeCTRONICS

Page 46

You might also like

- Compte Rendu PLL2 PDFDocument4 pagesCompte Rendu PLL2 PDFSafouane ElNo ratings yet

- TP1Document5 pagesTP1Mohamed ZarboubiNo ratings yet

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabFrom EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabNo ratings yet

- Manuel Utilisateur Maxi MiniDocument123 pagesManuel Utilisateur Maxi MinicherifNo ratings yet

- Chapitre I Microprocesseur 6809 GSEA12013Document56 pagesChapitre I Microprocesseur 6809 GSEA12013xanafahd78% (9)

- Les CompteursDocument7 pagesLes CompteursSoufiane AggourNo ratings yet

- Exercices d'optique et d'électromagnétismeFrom EverandExercices d'optique et d'électromagnétismeRating: 5 out of 5 stars5/5 (1)

- Cours - Composants Logiques Programmables Et VHDLDocument141 pagesCours - Composants Logiques Programmables Et VHDLYoussef Elalaoui0% (1)

- Les Bascules BistablesDocument8 pagesLes Bascules BistablesTopina Rahim100% (1)

- M18 - Logique Combinatoire GE-ESADocument136 pagesM18 - Logique Combinatoire GE-ESAMohammed Amine Kened50% (4)

- A22-Opérations D'arithmétique Binaire - v19 - 2Document6 pagesA22-Opérations D'arithmétique Binaire - v19 - 2Rafik Ben AmorNo ratings yet

- TP2 MicroprocesseurDocument14 pagesTP2 MicroprocesseurAdem AounNo ratings yet

- Les Compteurs Et Decompteurs PDFDocument11 pagesLes Compteurs Et Decompteurs PDFbakkari MNo ratings yet

- Chapitre Circuit Logique EleveDocument31 pagesChapitre Circuit Logique EleveNourallah Aouina100% (2)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- Logique CombinatoireDocument11 pagesLogique CombinatoireAnseea Popescu100% (1)

- EMD0203Document11 pagesEMD0203FouadHbNo ratings yet

- Chapitre 4 SLDocument12 pagesChapitre 4 SLHENSCHEL ShadracNo ratings yet

- TP1 LogiqueDocument5 pagesTP1 LogiqueasmaNo ratings yet

- Cours RegistresDocument8 pagesCours RegistresAnais Nour GhellamNo ratings yet

- Serie Exo AutomatismesDocument8 pagesSerie Exo AutomatismesSalimMalekNo ratings yet

- Brochage Des Principaux CI-TTL PDFDocument8 pagesBrochage Des Principaux CI-TTL PDFFerjani Mohamed100% (1)

- Bascules Exos PDFDocument2 pagesBascules Exos PDFbenhasamNo ratings yet

- Logique Combinatoire PDFDocument7 pagesLogique Combinatoire PDFAmatou ArrahmenNo ratings yet

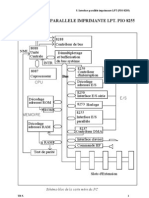

- Port Parallèle Pia 8255Document11 pagesPort Parallèle Pia 8255alex bbapNo ratings yet

- ch4 CircuitscombinatoiresDocument8 pagesch4 CircuitscombinatoiresKais BouzraraNo ratings yet

- Compteur SYN A2-2 2020Document8 pagesCompteur SYN A2-2 2020basmaNo ratings yet

- Exercice de Logique Sequentielle PDFDocument30 pagesExercice de Logique Sequentielle PDFmohcenNo ratings yet

- TD Maintenance Idustrielle Electronique 2Document1 pageTD Maintenance Idustrielle Electronique 2Fth Walter100% (1)

- Circuits Combinatoires Et SéquentielsDocument38 pagesCircuits Combinatoires Et SéquentielsHicham Wayne100% (3)

- TD CodeurDocument4 pagesTD CodeurMüheb BoudhraaNo ratings yet

- Les Comparateurs NumeriquesDocument4 pagesLes Comparateurs NumeriquesAbdelhadi EnnajihNo ratings yet

- Affichage MultiplexéDocument9 pagesAffichage Multiplexémustapha3100% (1)

- A2-2 UalDocument3 pagesA2-2 UalLabossef LabossefchedlyNo ratings yet

- Circuit IntegresDocument7 pagesCircuit IntegresAbd OUNo ratings yet

- Grafcet LaderDocument10 pagesGrafcet Laderhicham raghaiNo ratings yet

- Circuits Combinatoires EssentielsDocument7 pagesCircuits Combinatoires EssentielsBah KhalilNo ratings yet

- Ado 1ap 21-22 TD4Document2 pagesAdo 1ap 21-22 TD4Hamza BoutlihNo ratings yet

- Final Ele1300 h2008Document11 pagesFinal Ele1300 h2008Youssef YoussefNo ratings yet

- Bascules SynchronesDocument7 pagesBascules SynchronesMohamed Ben FredjNo ratings yet

- Compteurs / Décompteurs Asynchrones: Exercice 1Document2 pagesCompteurs / Décompteurs Asynchrones: Exercice 1Willy JossNo ratings yet

- Pic 16 F 877Document10 pagesPic 16 F 877Youssef Boughallad100% (1)

- TD Partie1Document6 pagesTD Partie1Maestri MaestroNo ratings yet

- 09 C5 RR-Les BasculesDocument14 pages09 C5 RR-Les BasculesRida LaglilNo ratings yet

- Programmation de L'interface ParallèleDocument10 pagesProgrammation de L'interface ParallèleAbdeltif BelquorchiNo ratings yet

- Add SOUSDocument9 pagesAdd SOUSNabil KhNo ratings yet

- Mini ProjetDocument2 pagesMini ProjetPretty Bea100% (1)

- Chap 3-MicrocontroleurDocument35 pagesChap 3-MicrocontroleurYosra rhim YosraNo ratings yet

- td5 Sur Chapitre 3. Automate ProgrammableDocument9 pagestd5 Sur Chapitre 3. Automate ProgrammableJean Louis KouassiNo ratings yet

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesFrom EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesNo ratings yet

- Récupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriqueFrom EverandRécupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriqueNo ratings yet

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesFrom EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesNo ratings yet

- Nez Électronique: Un appareil innovant fournit aux humains un odorat puissantFrom EverandNez Électronique: Un appareil innovant fournit aux humains un odorat puissantNo ratings yet

- GTEE Partie 2Document22 pagesGTEE Partie 2Les trucs qui marchent vraiment 2020No ratings yet

- TP 2 AutomatismeDocument14 pagesTP 2 AutomatismeAmine MalihNo ratings yet

- Cours Circuit SéquentielDocument22 pagesCours Circuit SéquentielMelina AggarNo ratings yet

- Esa Api29 ElkhalidyDocument144 pagesEsa Api29 ElkhalidyAZZ. ED DAHRAOUINo ratings yet

- Compteur Energie A1500Document88 pagesCompteur Energie A1500schumacher144100% (1)

- SysLog1 05 CompteursRegistresDocument19 pagesSysLog1 05 CompteursRegistresJunior DADJINNo ratings yet

- TIMER0Document78 pagesTIMER0Brahim Attia100% (1)

- Abel Jedec Proteus PDFDocument4 pagesAbel Jedec Proteus PDFbenoit lemayNo ratings yet

- Ace 6000 MTDocument3 pagesAce 6000 MTZellagui Energy100% (1)

- HEI3 TC Automatique 2001 DS2000-2001-HEI-GRAFCETDocument8 pagesHEI3 TC Automatique 2001 DS2000-2001-HEI-GRAFCETHaithem AmineNo ratings yet

- Codeur IncrémentalDocument23 pagesCodeur IncrémentalNejib Ben Nasr100% (1)

- CmosDocument32 pagesCmosDhekra JbeliNo ratings yet

- Série TDDocument2 pagesSérie TDBrahim OurraisNo ratings yet

- Technique CDocument8 pagesTechnique CChaker ChaoualNo ratings yet

- Exercices AssembleurDocument8 pagesExercices Assembleurarthurrimbaudoo0% (1)

- Modules VHDLDocument109 pagesModules VHDLSidali Zelazel100% (1)

- Chapitre 2Document25 pagesChapitre 2Md Idir HocineNo ratings yet

- KASTO VERTO-A2 - 03835154 - FDocument32 pagesKASTO VERTO-A2 - 03835154 - FPatrickNo ratings yet

- GRAFCET 1 Couleur 1 3Document106 pagesGRAFCET 1 Couleur 1 3Chaimaa GhazzaouiNo ratings yet

- Compte RenduDocument21 pagesCompte RenduYoussef BTS SENo ratings yet

- C4 SequentielleDocument82 pagesC4 SequentielleOumar MandodjoNo ratings yet

- L3 Biochimie 19-20 Belhattab R L3 Bioch Tech Anal Bioch II Chapitres II Et IIIDocument10 pagesL3 Biochimie 19-20 Belhattab R L3 Bioch Tech Anal Bioch II Chapitres II Et IIIEngwataNo ratings yet

- Le201td 2011Document23 pagesLe201td 2011Ghazi Ben HmidaNo ratings yet

- Circuits Intégrés Logiques C.MOSDocument21 pagesCircuits Intégrés Logiques C.MOSHamami AymenNo ratings yet

- Les Registres UsthbDocument45 pagesLes Registres Usthbzgaren amineNo ratings yet

- Manuel ProfesseurDocument17 pagesManuel Professeurnouredine akliNo ratings yet

- Compteurs Horaires 21Document1 pageCompteurs Horaires 21ArmelNo ratings yet

- UntitledDocument64 pagesUntitledRedouane ChihabeNo ratings yet